Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Active                                                                           |

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 40 MIPs                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                            |

| Number of I/O              | 21                                                                               |

| Program Memory Size        | 9КВ (3К х 24)                                                                    |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 1K x 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 8x10b; D/A 2x10b                                                             |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 36-VFTLA Exposed Pad                                                             |

| Supplier Device Package    | 36-VTLA (5x5)                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj09gs302t-i-tl |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

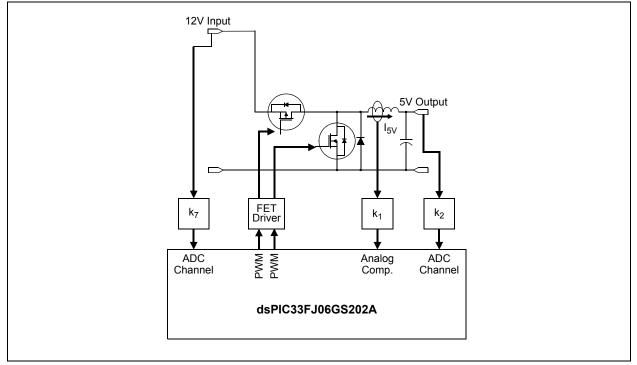

### FIGURE 2-6: SINGLE-PHASE SYNCHRONOUS BUCK CONVERTER

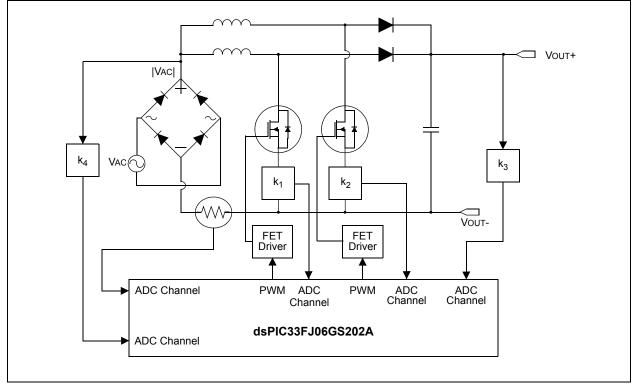

### FIGURE 2-7: INTERLEAVED PFC

### TABLE 4-1: CPU CORE REGISTER MAP (CONTINUED)

| SFR Name | SFR<br>Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12   | Bit 11 | Bit 10                                          | Bit 9      | Bit 8         | Bit 7    | Bit 6 | Bit 5   | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|----------|-------------|--------|--------|--------|----------|--------|-------------------------------------------------|------------|---------------|----------|-------|---------|-------|-------|-------|-------|-------|---------------|

| CORCON   | 0044        | —      | _      | _      | US       | EDT    | EDT DL<2:0> SATA SATB SATDW ACCSAT IPL3 PSV RND |            |               |          |       |         | IF    | 0020  |       |       |       |               |

| MODCON   | 0046        | XMODEN | YMODEN | _      | _        |        | BWM                                             | <3:0>      |               |          | ΥW    | /M<3:0> |       |       | XWM   | <3:0> |       | 0000          |

| XMODSRT  | 0048        |        |        |        |          |        | Х                                               | S<15:1>    |               |          |       |         |       |       |       |       | 0     | XXXX          |

| XMODEND  | 004A        |        |        |        |          |        | Х                                               | E<15:1>    |               |          |       |         |       |       |       |       | 1     | XXXX          |

| YMODSRT  | 004C        |        |        |        |          |        | Y                                               | S<15:1>    |               |          |       |         |       |       |       |       | 0     | XXXX          |

| YMODEND  | 004E        |        |        |        |          |        | Y                                               | E<15:1>    |               |          |       |         |       |       |       |       | 1     | XXXX          |

| XBREV    | 0050        | BREN   |        |        | XB<14:0> |        |                                                 |            |               |          |       |         | XXXX  |       |       |       |       |               |

| DISICNT  | 0052        | _      | _      |        |          |        |                                                 | Disable In | terrupts Cour | nter Reg | ister |         |       |       |       |       |       | XXXX          |

Legend:

x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

### TABLE 4-24: PERIPHERAL PIN SELECT INPUT REGISTER MAP FOR dsPIC33FJ06GS001

| SFR Name | SFR<br>Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11  | Bit 10 | Bit 9 | Bit 8 | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3  | Bit 2  | Bit 1 | Bit 0 | All<br>Resets |

|----------|-------------|--------|--------|--------|--------|---------|--------|-------|-------|-------|-------|-------|-------|--------|--------|-------|-------|---------------|

| RPINR0   | 0680        | —      | —      |        |        | INT1R<5 | 5:0>   |       |       | —     | —     | —     | —     | —      | —      | _     | —     | 3F00          |

| RPINR1   | 0682        | _      | —      | _      | —      | _       |        | —     | _     | —     | _     |       |       | INT2R  | <5:0>  |       |       | 003F          |

| RPINR2   | 0684        | _      | —      |        |        | T1CKR<  | 5:0>   |       |       | —     | _     | _     | _     | —      | _      | _     | _     | 3F00          |

| RPINR3   | 0686        | _      | _      |        | —      | —       |        | —     | _     | _     |       |       |       | T2CKR  | <5:0>  |       |       | 003F          |

| RPINR29  | 06BA        | _      | _      |        |        | FLT1R<5 | 5:0>   | •     |       | _     |       | _     | _     | _      | _      | _     |       | 3F00          |

| RPINR30  | 06BC        | _      | _      |        |        | FLT3R<5 | 5:0>   |       |       | _     |       |       |       | FLT2R  | <5:0>  |       |       | 3F3F          |

| RPINR31  | 06BE        | _      | _      |        |        | FLT5R<5 | 5:0>   |       |       | _     |       |       |       | FLT4R  | <5:0>  |       |       | 3F3F          |

| RPINR32  | 06C0        | _      | _      |        |        | FLT7R<5 | 5:0>   |       |       | _     |       |       |       | FLT6R  | <5:0>  |       |       | 3F3F          |

| RPINR33  | 06C2        | _      | _      |        |        | SYNCI1R | <5:0>  |       |       | _     | _     |       |       | FLT8R  | <5:0>  |       |       | 3F3F          |

| RPINR34  | 06C4        | _      | _      | _      | —      | —       | _      | —     | _     | _     | _     |       |       | SYNCI2 | R<5:0> |       |       | 003F          |

Legend: x = unknown value on Reset, - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

### TABLE 4-25: PERIPHERAL PIN SELECT INPUT REGISTER MAP FOR dsPIC33FJ06GS101A AND dsPIC33FJ06GS102A

| SFR Name | SFR<br>Addr | Bit 15    | Bit 14   | Bit 13       | Bit 12      | Bit 11        | Bit 10      | Bit 9    | Bit 8      | Bit 7   | Bit 6 | Bit 5 | Bit 4 | Bit 3  | Bit 2  | Bit 1 | Bit 0 | All<br>Resets |

|----------|-------------|-----------|----------|--------------|-------------|---------------|-------------|----------|------------|---------|-------|-------|-------|--------|--------|-------|-------|---------------|

| RPINR0   | 0680        | —         | —        |              |             | INT1R<5       | 5:0>        |          |            | —       | —     | _     | —     | —      | —      | -     | —     | 3F00          |

| RPINR1   | 0682        | —         | —        | _            | _           | _             |             | —        | —          | _       | _     |       |       | INT2R  | <5:0>  |       |       | 003F          |

| RPINR2   | 0684        | _         | _        |              |             | T1CKR<        | 5:0>        |          |            | _       | _     |       | _     | _      | _      | _     | _     | 3F00          |

| RPINR3   | 0686        | _         | _        | _            | —           | —             |             | —        | _          | _       | _     |       |       | T2CKR  | <5:0>  |       | •     | 003F          |

| RPINR11  | 0696        | _         | _        | -            | _           | _             |             | _        | _          | _       | _     |       |       | OCFAF  | <5:0>  |       |       | 003F          |

| RPINR18  | 06A4        | _         | _        |              | •           | U1CTSR<       | <5:0>       | •        | •          |         | _     |       |       | U1RXF  | <5:0>  |       |       | 3F3F          |

| RPINR20  | 06A8        | _         | _        |              |             | SCK1R<        | 5:0>        |          |            |         | _     |       |       | SDI1R  | <5:0>  |       |       | 3F3F          |

| RPINR21  | 06AA        | _         | _        | _            | —           | —             |             | —        | _          | _       | _     |       |       | SS1R·  | <5:0>  |       |       | 003F          |

| RPINR29  | 06BA        | _         | _        |              | •           | FLT1R<        | 5:0>        | •        | •          | _       | _     | _     |       | _      | _      | _     |       | 3F00          |

| RPINR30  | 06BC        | —         | —        |              |             | FLT3R<        | 5:0>        |          |            | _       | _     |       |       | FLT2R  | <5:0>  |       |       | 3F3F          |

| RPINR31  | 06BE        | _         | _        |              |             | FLT5R<5       | 5:0>        |          |            | _       | _     |       |       | FLT4R  | <5:0>  |       |       | 3F3F          |

| RPINR32  | 06C0        | _         | _        |              |             | FLT7R<        | 5:0>        |          |            | _       | _     |       |       | FLT6R  | <5:0>  |       |       | 3F3F          |

| RPINR33  | 06C2        | _         | _        |              |             | SYNCI1R       | <5:0>       |          |            |         | _     |       |       | FLT8R  | <5:0>  |       |       | 3F3F          |

| RPINR34  | 06C4        | _         | _        | _            | _           | _             |             | —        | _          | _       | _     |       |       | SYNCI2 | R<5:0> |       |       | 003F          |

| Legend:  | x = unkn    | own value | on Reset | , — = unimpl | emented, re | ad as '0'. Re | eset values | are show | n in hexad | ecimal. | •     |       |       |        |        |       |       | *             |

dsPIC33FJ06GS001/101A/102A/202A and dsPIC33FJ09GS302

# FIGURE 7-1: dsPIC33FJ06GS001/101A/102A/202A and dsPIC33FJ09GS302 INTERRUPT VECTOR TABLE

| 1                                 | Depet como Instruction            |                   |                                                        |

|-----------------------------------|-----------------------------------|-------------------|--------------------------------------------------------|

|                                   | Reset - GOTO Instruction          | 0x000000          |                                                        |

|                                   | Reset – GOTO Address              | 0x000002          |                                                        |

|                                   | Reserved                          | 0x000004          |                                                        |

|                                   | Oscillator Fail Trap Vector       | _                 |                                                        |

|                                   | Address Error Trap Vector         | _                 |                                                        |

|                                   | Stack Error Trap Vector           |                   |                                                        |

|                                   | Math Error Trap Vector            | _                 |                                                        |

|                                   | Reserved                          |                   |                                                        |

|                                   | Reserved                          |                   |                                                        |

|                                   | Reserved                          |                   |                                                        |

|                                   | Interrupt Vector 0                | 0x000014          |                                                        |

|                                   | Interrupt Vector 1                |                   |                                                        |

|                                   | ~                                 | _                 |                                                        |

|                                   | ~                                 | _                 |                                                        |

|                                   | ~                                 |                   |                                                        |

|                                   | Interrupt Vector 52               | 0x00007C          | Interrupt Vector Table (IVT) <sup>(1)</sup>            |

| >                                 | Interrupt Vector 53               | 0x00007E          | ,                                                      |

| brit                              | Interrupt Vector 54               | 0x000080          |                                                        |

| L re                              | ~                                 | _                 |                                                        |

| er                                | ~                                 | -                 |                                                        |

| Drd                               | Interrupt Vector 116              | 0x0000FC          |                                                        |

| Decreasing Natural Order Priority | Interrupt Vector 117              | 0x0000FC          |                                                        |

| fr                                |                                   | 0x000100          |                                                        |

| Za                                | Reserved<br>Reserved              | 0x000100          |                                                        |

| bu                                | Reserved                          | 0x000102          |                                                        |

| asi                               | Oscillator Fail Trap Vector       | _                 |                                                        |

| e c                               | Address Error Trap Vector         |                   |                                                        |

| De                                | Stack Error Trap Vector           |                   |                                                        |

| _                                 | Math Error Trap Vector            |                   |                                                        |

|                                   | Reserved                          | _                 |                                                        |

|                                   | Reserved                          |                   |                                                        |

|                                   | Reserved                          | -                 |                                                        |

|                                   | Interrupt Vector 0                | 0x000114          |                                                        |

|                                   | Interrupt Vector 1                |                   |                                                        |

|                                   | ~                                 |                   |                                                        |

|                                   | ~                                 | 1                 |                                                        |

|                                   | ~                                 | 1                 | Alternate Interrupt Vector Table (AIVT) <sup>(1)</sup> |

|                                   | Interrupt Vector 52               | 0x00017C          | ,                                                      |

|                                   | Interrupt Vector 53               | 0x00017E          |                                                        |

|                                   | Interrupt Vector 54               | 0x000180          |                                                        |

|                                   | ~                                 |                   |                                                        |

|                                   | ~                                 |                   |                                                        |

|                                   | ~                                 | ]                 |                                                        |

|                                   | Interrupt Vector 116              |                   |                                                        |

| ↓ J                               | Interrupt Vector 117              | 0x0001FE          |                                                        |

| V                                 | Start of Code                     | 0x000200          |                                                        |

|                                   |                                   |                   |                                                        |

|                                   |                                   |                   |                                                        |

| Note de O                         | Table 7 4 families list of image  |                   |                                                        |

| Note 1: See                       | Table 7-1 for the list of impleme | ented interrupt v | ectors.                                                |

|                                   |                                   |                   |                                                        |

| U-0           | R/W-1                 | R/W-0                                              | R/W-0      | U-0              | R/W-1            | R/W-0           | R/W-0 |

|---------------|-----------------------|----------------------------------------------------|------------|------------------|------------------|-----------------|-------|

| _             |                       | ADCP1IP<2:0>                                       | >          | —                |                  | ADCP0IP<2:0>    |       |

| bit 15        |                       |                                                    |            |                  | •                |                 | bit 8 |

| U-0           | U-0                   | U-0                                                | U-0        | U-0              | U-0              | U-0             | U-0   |

|               |                       |                                                    | _          | _                | _                |                 | _     |

| bit 7         |                       |                                                    |            |                  |                  |                 | bit 0 |

| Legend:       |                       |                                                    |            |                  |                  |                 |       |

| R = Readabl   | le bit                | W = Writable                                       | bit        | U = Unimpler     | mented bit, read | 1 as '0'        |       |

| -n = Value at | t POR                 | '1' = Bit is set                                   |            | '0' = Bit is cle | eared            | x = Bit is unkr | nown  |

|               | •<br>•<br>001 = Inter | rupt is Priority 7 (<br>rupt is Priority 1         |            | ty interrupt)    |                  |                 |       |

| bit 11        |                       | rupt source is dis<br>ented: Read as '             |            |                  |                  |                 |       |

| bit 10-8      | ADCP0IP<              | <b>2:0&gt;:</b> ADC Pair 0<br>rupt is Priority 7 ( | Conversion |                  | Priority bits    |                 |       |

|               |                       | rupt is Priority 1<br>rupt source is dis           | abled      |                  |                  |                 |       |

### 10.6 Peripheral Pin Select (PPS)

Peripheral Pin Select configuration enables peripheral set selection and placement on a wide range of I/O pins. By increasing the pinout options available on a particular device, programmers can better tailor the microcontroller to their entire application, rather than trimming the application to fit the device.

The Peripheral Pin Select configuration feature operates over a fixed subset of digital I/O pins. Programmers can independently map the input and/or output of most digital peripherals to any one of these I/O pins. Peripheral Pin Select is performed in software and generally does not require the device to be reprogrammed. Hardware safeguards are included that prevent accidental or spurious changes to the peripheral mapping once it has been established.

### 10.6.1 AVAILABLE PINS

The Peripheral Pin Select feature is used with a range of up to 16 pins. The number of available pins depends on the particular device and its pin count. Pins that support the Peripheral Pin Select feature include the designation, "RPn", in their full pin designation, where "RP" designates a remappable peripheral and "n" is the remappable pin number.

### 10.6.2 CONTROLLING PERIPHERAL PIN SELECT

Peripheral Pin Select features are controlled through two sets of Special Function Registers: one to map peripheral inputs and one to map outputs. Because they are separately controlled, a particular peripheral's input and output (if the peripheral has both) can be placed on any selectable function pin without constraint.

The association of a peripheral to a peripheral selectable pin is handled in two different ways, depending on whether an input or output is being mapped.

### 10.6.2.1 Input Mapping

The inputs of the Peripheral Pin Select options are mapped on the basis of the peripheral. A control register associated with a peripheral dictates the pin it will be mapped to. The RPINRx registers are used to configure peripheral input mapping (see Register 10-1 through Register 10-15). Each register contains sets of 6-bit fields, with each set associated with one of the remappable peripherals. Programming a given peripheral's bit field with an appropriate 6-bit value maps the RPn pin with that value to that peripheral. For any given device, the valid range of values for any bit field corresponds to the maximum number of Peripheral Pin Selections supported by the device.

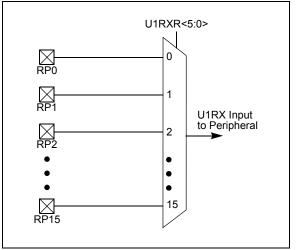

Figure 10-2 illustrates the remappable pin selection for the U1RX input.

Note: For input mapping only, the Peripheral Pin Select (PPS) functionality does not have priority over the TRISx settings. Therefore, when configuring the RPx pin for input, the corresponding bit in the TRISx register must also be configured for input (i.e., set to '1').

### FIGURE 10-2: REMAPPABLE MUX INPUT FOR U1RX

| U-0           | U-0                 | R/W-1             | R/W-1          | R/W-1            | R/W-1                 | R/W-1                      | R/W-1 |

|---------------|---------------------|-------------------|----------------|------------------|-----------------------|----------------------------|-------|

| —             | —                   |                   |                | SCK1F            | R<5:0> <sup>(1)</sup> |                            |       |

| bit 15        |                     |                   |                |                  |                       |                            | bit 8 |

|               |                     |                   |                |                  |                       |                            |       |

| U-0           | U-0                 | R/W-1             | R/W-1          | R/W-1            | R/W-1                 | R/W-1                      | R/W-1 |

|               |                     |                   |                | SDI1R            | <5:0> <sup>(1)</sup>  |                            |       |

| bit 7         |                     |                   |                |                  |                       |                            | bit ( |

|               |                     |                   |                |                  |                       |                            |       |

| Legend:       |                     |                   |                |                  |                       |                            |       |

| R = Readabl   |                     | W = Writable      |                | •                | mented bit, read      | d as '0'                   |       |

| -n = Value at | t POR               | '1' = Bit is set  |                | '0' = Bit is cle | ared                  | x = Bit is unkr            | nown  |

| L:1 4 5 4 4   |                     | ta da Da a da a ( | ~ '            |                  |                       |                            |       |

| bit 15-14     | -                   | ted: Read as '    |                |                  |                       | (4)                        |       |

| bit 13-8      | SCK1R<5:0>          | : Assign SPI1     | Clock Input (S | CK1) to the Co   | prresponding R        | Pn Pin bits <sup>(1)</sup> |       |

|               | 111111 <b>= Inp</b> |                   |                |                  |                       |                            |       |

|               |                     | out tied to RP3   |                |                  |                       |                            |       |

|               |                     | out tied to RP34  |                |                  |                       |                            |       |

|               |                     | out tied to RP3   |                |                  |                       |                            |       |

|               |                     | out tied to RP32  | 2              |                  |                       |                            |       |

|               | •                   |                   |                |                  |                       |                            |       |

|               | •                   |                   |                |                  |                       |                            |       |

|               | 00000 <b>= Inpu</b> | t tied to RP0     |                |                  |                       |                            |       |

| bit 7-6       |                     | ted: Read as '    | 0'             |                  |                       |                            |       |

| bit 5-0       | -                   |                   |                | 11) to the Corre | esponding RPn         | Pin bits <sup>(1)</sup>    |       |

|               | 111111 = Inp        |                   |                |                  | sepending rain        |                            |       |

|               |                     | out tied to RP3   | 5              |                  |                       |                            |       |

|               |                     | out tied to RP34  |                |                  |                       |                            |       |

|               |                     | out tied to RP33  |                |                  |                       |                            |       |

|               |                     | out tied to RP32  |                |                  |                       |                            |       |

|               | •                   |                   |                |                  |                       |                            |       |

|               | •                   |                   |                |                  |                       |                            |       |

|               | •                   |                   |                |                  |                       |                            |       |

|               | 00000 <b>= Inpu</b> | t tied to RPO     |                |                  |                       |                            |       |

|               | 00000 <b>– mpu</b>  |                   |                |                  |                       |                            |       |

### REGISTER 10-8: RPINR20: PERIPHERAL PIN SELECT INPUT REGISTER 20

**Note 1:** These bits are not implemented in the dsPIC33FJ06GS001 device.

| U-0           | U-0                 | U-0                                  | U-0           | U-0                                | U-0                  | U-0                          | U-0   |  |  |

|---------------|---------------------|--------------------------------------|---------------|------------------------------------|----------------------|------------------------------|-------|--|--|

| —             | —                   | —                                    | _             | —                                  | _                    |                              |       |  |  |

| bit 15        |                     |                                      |               |                                    |                      |                              | bit 8 |  |  |

|               |                     |                                      |               |                                    |                      |                              |       |  |  |

| U-0           | U-0                 | R/W-1                                | R/W-1         | R/W-1                              | R/W-1                | R/W-1                        | R/W-1 |  |  |

|               |                     |                                      |               | SS1R                               | <5:0> <sup>(1)</sup> |                              |       |  |  |

| bit 7         |                     |                                      |               |                                    |                      |                              | bit 0 |  |  |

|               |                     |                                      |               |                                    |                      |                              |       |  |  |

| Legend:       |                     |                                      |               |                                    |                      |                              |       |  |  |

| R = Readabl   | le bit              | W = Writable                         | bit           | U = Unimplemented bit, read as '0' |                      |                              |       |  |  |

| -n = Value at | t POR               | '1' = Bit is set                     |               | '0' = Bit is cle                   | ared                 | x = Bit is unknown           |       |  |  |

|               |                     |                                      |               |                                    |                      |                              |       |  |  |

| bit 15-6      | Unimplemen          | ted: Read as '                       | כי            |                                    |                      |                              |       |  |  |

| bit 5-0       | SS1R<5:0>: /        | Assign SPI1 Sla                      | ave Select In | put (SS1) to the                   | e Corresponding      | g RPn Pin bits <sup>(1</sup> | 1)    |  |  |

|               | 111111 <b>= Inp</b> |                                      |               |                                    |                      |                              |       |  |  |

|               |                     | out tied to RP35                     |               |                                    |                      |                              |       |  |  |

|               |                     | out tied to RP34                     |               |                                    |                      |                              |       |  |  |

|               |                     | out tied to RP33<br>out tied to RP32 |               |                                    |                      |                              |       |  |  |

|               | •                   |                                      | -             |                                    |                      |                              |       |  |  |

|               | •                   |                                      |               |                                    |                      |                              |       |  |  |

|               | •                   |                                      |               |                                    |                      |                              |       |  |  |

|               | 00000 <b>= Inpu</b> | t tied to RP0                        |               |                                    |                      |                              |       |  |  |

|               |                     |                                      |               |                                    |                      |                              |       |  |  |

### REGISTER 10-9: RPINR21: PERIPHERAL PIN SELECT INPUT REGISTER 21

**Note 1:** These bits are not implemented in the dsPIC33FJ06GS001 device.

| U-0                | U-0                                                                                                                       | R/W-1                                                                                                                                                                      | R/W-1                              | R/W-1                       | R/W-1            | R/W-1           | R/W-1 |

|--------------------|---------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|-----------------------------|------------------|-----------------|-------|

| _                  | —                                                                                                                         |                                                                                                                                                                            |                                    | FLT7                        | R<5:0>           |                 |       |

| bit 15             |                                                                                                                           |                                                                                                                                                                            |                                    |                             |                  |                 | bit 8 |

|                    |                                                                                                                           |                                                                                                                                                                            |                                    |                             |                  |                 |       |

| U-0                | U-0                                                                                                                       | R/W-1                                                                                                                                                                      | R/W-1                              | R/W-1                       | R/W-1            | R/W-1           | R/W-1 |

| _                  | —                                                                                                                         |                                                                                                                                                                            |                                    | FLT6                        | R<5:0>           |                 |       |

| bit 7              |                                                                                                                           |                                                                                                                                                                            |                                    |                             |                  |                 | bit ( |

| Legend:            |                                                                                                                           |                                                                                                                                                                            |                                    |                             |                  |                 |       |

| R = Readab         | le bit                                                                                                                    | W = Writable I                                                                                                                                                             | oit                                | U = Unimplen                | nented bit, read | d as '0'        |       |

| -n = Value a       | t POR                                                                                                                     | '1' = Bit is set                                                                                                                                                           |                                    | '0' = Bit is clea           |                  | x = Bit is unkr | nown  |

|                    |                                                                                                                           |                                                                                                                                                                            |                                    |                             |                  |                 |       |

| bit 15-14          | Unimpleme                                                                                                                 | nted: Read as '(                                                                                                                                                           | )'                                 |                             |                  |                 |       |

| bit 13-8           | •                                                                                                                         | : Assign PWM F                                                                                                                                                             |                                    | =I T7) to the Co            | orresponding R   | Pn Pin hits     |       |

|                    |                                                                                                                           | put tied to Vss                                                                                                                                                            |                                    |                             | incoponding is   |                 |       |

|                    |                                                                                                                           | put tied to RP35                                                                                                                                                           |                                    |                             |                  |                 |       |

|                    |                                                                                                                           |                                                                                                                                                                            |                                    |                             |                  |                 |       |

|                    | 100010 <b>= ln</b>                                                                                                        | put tied to RP34                                                                                                                                                           |                                    |                             |                  |                 |       |

|                    |                                                                                                                           | put tied to RP34<br>put tied to RP33                                                                                                                                       |                                    |                             |                  |                 |       |

|                    | 100001 <b>= In</b>                                                                                                        |                                                                                                                                                                            | 1                                  |                             |                  |                 |       |

|                    | 100001 <b>= In</b>                                                                                                        | put tied to RP33                                                                                                                                                           | 1                                  |                             |                  |                 |       |

|                    | 100001 <b>= In</b>                                                                                                        | put tied to RP33                                                                                                                                                           | 1                                  |                             |                  |                 |       |

|                    | 100001 <b>= In</b>                                                                                                        | put tied to RP33                                                                                                                                                           | 1                                  |                             |                  |                 |       |

|                    | 100001 = In<br>100000 = In<br>•                                                                                           | put tied to RP33<br>put tied to RP32                                                                                                                                       | 1                                  |                             |                  |                 |       |

| bit 7-6            | 100001 = In<br>100000 = In<br>•<br>•<br>•<br>00000 = Inp                                                                  | put tied to RP33<br>put tied to RP32<br>ut tied to RP0                                                                                                                     |                                    |                             |                  |                 |       |

| bit 7-6            | 100001 = In<br>100000 = In<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>• | put tied to RP33<br>put tied to RP32<br>ut tied to RP0<br>nted: Read as '0                                                                                                 | ;<br>;<br>;                        | ELT6) to the Co             | prresponding P   | PDn Din hite    |       |

| bit 7-6<br>bit 5-0 | 100001 = In<br>100000 = In<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>• | put tied to RP33<br>put tied to RP32<br>ut tied to RP0<br><b>nted:</b> Read as '0<br>:: Assign PWM F                                                                       | ;<br>;<br>;                        | FLT6) to the Co             | prresponding R   | Pn Pin bits     |       |

|                    | 100001 = In<br>100000 = In<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>• | put tied to RP33<br>put tied to RP32<br>ut tied to RP0<br>nted: Read as '0<br>: Assign PWM F<br>put tied to Vss                                                            | <sub>)</sub> ,<br>Fault Input 6 (I | FLT6) to the Co             | prresponding R   | Pn Pin bits     |       |

|                    | 100001 = In<br>100000 = In<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>• | put tied to RP33<br>put tied to RP32<br>ut tied to RP0<br>nted: Read as '0<br>: Assign PWM F<br>put tied to Vss<br>put tied to RP35                                        | ) <sup>)</sup><br>Fault Input 6 (I | FLT6) to the Co             | prresponding R   | Pn Pin bits     |       |

|                    | 100001 = In<br>100000 = In<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>• | ut tied to RP33<br>put tied to RP32<br>ut tied to RP0<br>nted: Read as '0<br>: Assign PWM F<br>put tied to Vss<br>put tied to RP35<br>put tied to RP34                     | ) <sup>)</sup><br>Fault Input 6 (I | <sup>-</sup> LT6) to the Co | prresponding R   | Pn Pin bits     |       |

|                    | 100001 = In<br>100000 = In<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>• | ut tied to RP33<br>put tied to RP32<br>ut tied to RP0<br>nted: Read as '0<br>: Assign PWM F<br>put tied to Vss<br>put tied to RP35<br>put tied to RP34<br>put tied to RP33 | o'<br>Fault Input 6 (I             | <sup>-</sup> LT6) to the Co | prresponding R   | Pn Pin bits     |       |

|                    | 100001 = In<br>100000 = In<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>• | ut tied to RP33<br>put tied to RP32<br>ut tied to RP0<br>nted: Read as '0<br>: Assign PWM F<br>put tied to Vss<br>put tied to RP35<br>put tied to RP34                     | o'<br>Fault Input 6 (I             | <sup>-</sup> LT6) to the Co | prresponding R   | Pn Pin bits     |       |

|                    | 100001 = In<br>100000 = In<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>• | ut tied to RP33<br>put tied to RP32<br>ut tied to RP0<br>nted: Read as '0<br>: Assign PWM F<br>put tied to Vss<br>put tied to RP35<br>put tied to RP34<br>put tied to RP33 | o'<br>Fault Input 6 (I             | <sup>-</sup> LT6) to the Co | prresponding R   | Pn Pin bits     |       |

|                    | 100001 = In<br>100000 = In<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>• | ut tied to RP33<br>put tied to RP32<br>ut tied to RP0<br>nted: Read as '0<br>: Assign PWM F<br>put tied to Vss<br>put tied to RP35<br>put tied to RP34<br>put tied to RP33 | o'<br>Fault Input 6 (I             | FLT6) to the Co             | prresponding R   | Pn Pin bits     |       |

|                    | 100001 = In<br>100000 = In<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>• | ut tied to RP33<br>put tied to RP32<br>ut tied to RP0<br>nted: Read as '0<br>: Assign PWM F<br>put tied to Vss<br>put tied to RP35<br>put tied to RP34<br>put tied to RP33 | o'<br>Fault Input 6 (I             | <sup>=</sup> LT6) to the Co | prresponding R   | Pn Pin bits     |       |

### REGISTER 10-13: RPINR32: PERIPHERAL PIN SELECT INPUT REGISTER 32

| R/W-0                 | U-0                        | R/W-0                                   | HS/HC-0                | R/W-0                     | R/W-0               | R/W-0                   | R/W-0                 |

|-----------------------|----------------------------|-----------------------------------------|------------------------|---------------------------|---------------------|-------------------------|-----------------------|

| PTEN                  | _                          | PTSIDL                                  | SESTAT                 | SEIEN                     | EIPU <sup>(1)</sup> | SYNCPOL <sup>(1)</sup>  | SYNCOEN <sup>(1</sup> |

| bit 15                |                            |                                         |                        |                           |                     |                         | bit 8                 |

|                       |                            |                                         |                        |                           |                     |                         |                       |

| R/W-0                 | U-0                        | R/W-0                                   | R/W-0                  | R/W-0                     | R/W-0               | R/W-0                   | R/W-0                 |

| SYNCEN <sup>(1)</sup> | —                          | SYNCSF                                  | RC<1:0> <sup>(1)</sup> |                           | SEV                 | [PS<3:0> <sup>(1)</sup> |                       |

| bit 7                 |                            |                                         |                        |                           |                     |                         | bit (                 |

| Legend:               |                            | HC = Hardware                           | e Clearable bit        | HS = Hardv                | vare Settable       | bit                     |                       |

| R = Readable          | bit                        | W = Writable b                          | it                     | U = Unimpl                | lemented bit,       | read as '0'             |                       |

| -n = Value at F       | POR                        | '1' = Bit is set                        |                        | '0' = Bit is c            | cleared             | x = Bit is unkr         | lown                  |

| bit 15                | PTFN: PWM                  | Module Enable                           | bit                    |                           |                     |                         |                       |

|                       |                            | dule is enabled                         |                        |                           |                     |                         |                       |

|                       | 0 = PWM mod                | dule is disabled                        |                        |                           |                     |                         |                       |

| bit 14                |                            | ted: Read as '0                         |                        |                           |                     |                         |                       |

| bit 13                |                            | V Time Base Sto                         | •                      | bit                       |                     |                         |                       |

|                       |                            | e base halts in C                       |                        |                           |                     |                         |                       |

| bit 12                |                            | e base runs in C<br>cial Event Interr   |                        |                           |                     |                         |                       |

| DIT 12                |                            | /ent interrupt is                       | •                      |                           |                     |                         |                       |

|                       | •                          | /ent interrupt is                       | •                      |                           |                     |                         |                       |

| bit 11                | SEIEN: Speci               | al Event Interrup                       | ot Enable bit          |                           |                     |                         |                       |

|                       | •                          | ent interrupt is                        |                        |                           |                     |                         |                       |

|                       | -                          | /ent interrupt is                       |                        | n                         |                     |                         |                       |

| bit 10                |                            | Immediate Peri                          | •                      |                           |                     |                         |                       |

|                       |                            | riod register is u<br>riod register upd |                        |                           | oundaries           |                         |                       |

| bit 9                 |                            | ynchronization I                        |                        |                           | Janaanee            |                         |                       |

|                       |                            | nd SYNCO1 po                            |                        | •                         |                     |                         |                       |

|                       |                            | nd SYNCO1 are                           | -                      |                           |                     |                         |                       |

| bit 8                 |                            | rimary Time Ba                          |                        | bit <sup>(1)</sup>        |                     |                         |                       |

|                       |                            | output is enable                        |                        |                           |                     |                         |                       |

| hit 7                 |                            | output is disable<br>ternal Time Base   |                        | n Enchla hit              | (1)                 |                         |                       |

| bit 7                 |                            | synchronization                         | •                      |                           |                     |                         |                       |

|                       |                            | synchronization                         |                        |                           |                     |                         |                       |

| bit 6                 |                            | ted: Read as '0'                        |                        |                           |                     |                         |                       |

| bit 5-4               |                            | :0>: Synchrono                          |                        | ction bits <sup>(1)</sup> |                     |                         |                       |

|                       | 11 = Reserve               | d                                       |                        |                           |                     |                         |                       |

|                       | 10 = Reserve               |                                         |                        |                           |                     |                         |                       |

|                       | 01 = SYNCI2<br>00 = SYNCI1 |                                         |                        |                           |                     |                         |                       |

| bit 3-0               |                            | >: PWM Special                          | Event Trigger (        | Jutnut Posts              | caler Select I      | <sub>Dits</sub> (1)     |                       |

|                       |                            | Postscaler genera                       |                        |                           |                     |                         | atch event            |

|                       | •                          | 3                                       | -1                     | 55 0                      | . ,                 |                         |                       |

|                       | •                          |                                         |                        |                           |                     |                         |                       |

|                       | •<br>0001 = 1·2 Pr         | ostscaler genera                        | ites a Special Fi      | vent Trigger (            | nn everv sec        | ond compare m           | atch event            |

|                       |                            | ostscaler genera                        |                        |                           |                     |                         |                       |

|                       |                            | -                                       | -                      |                           |                     |                         |                       |

|                       |                            | be changed only                         |                        |                           |                     |                         |                       |

|                       |                            | ogram the Peric                         |                        |                           | signuy large        | er man me expe          | scied period of       |

### REGISTER 15-1: PTCON: PWM TIME BASE CONTROL REGISTER

the external synchronization input signal.

### REGISTER 15-19: PWMCAPx: PRIMARY PWMx TIME BASE CAPTURE REGISTER

| R-0              | R-0 | R-0                        | R-0   | R-0                      | R-0              | R-0             | R-0   |

|------------------|-----|----------------------------|-------|--------------------------|------------------|-----------------|-------|

|                  |     |                            | PWMCA | P<15:8> <sup>(1,2)</sup> |                  |                 |       |

| bit 15           |     |                            |       |                          |                  |                 | bit 8 |

|                  |     |                            |       |                          |                  |                 |       |

| R-0              | R-0 | R-0                        | R-0   | R-0                      | U-0              | U-0             | U-0   |

|                  | PW  | /MCAP<7:3> <sup>(1,;</sup> | 2)    |                          | —                | —               | —     |

| bit 7            |     |                            |       |                          |                  |                 | bit 0 |

|                  |     |                            |       |                          |                  |                 |       |

| Legend:          |     |                            |       |                          |                  |                 |       |

| R = Readable bi  | t   | W = Writable               | bit   | U = Unimpler             | mented bit, read | d as '0'        |       |

| -n = Value at PO | R   | '1' = Bit is set           |       | '0' = Bit is cle         | ared             | x = Bit is unkr | nown  |

bit 15-3

PWMCAP<15:3>: Captured PWM Time Base Value bits<sup>(1,2)</sup>

The value in this register represents the captured PWM time base value when a leading edge is detected on the current-limit input.

bit 2-0

Unimplemented: Read as '0'

- **Note 1:** The capture feature is only available on primary output (PWMxH).

- 2: This feature is active only after LEB processing on the current-limit input signal is complete.

### REGISTER 15-20: CHOP: PWM CHOP CLOCK GENERATOR REGISTER

| R/W-0           | U-0        | U-0                                | U-0             | U-0              | U-0                               | R/W-0              | R/W-0        |  |

|-----------------|------------|------------------------------------|-----------------|------------------|-----------------------------------|--------------------|--------------|--|

| CHPCLKEN        | —          | —                                  | —               | —                | —                                 | CHOPC              | LK<6:5>      |  |

| bit 15          |            |                                    |                 |                  | •                                 |                    | bit 8        |  |

|                 |            |                                    |                 |                  |                                   |                    |              |  |

| R/W-0           | R/W-0      | R/W-0                              | R/W-0           | R/W-0            | U-0                               | U-0                | U-0          |  |

|                 | CI         | HOPCLK<4:0>                        |                 |                  | —                                 | —                  | _            |  |

| bit 7           |            |                                    |                 |                  |                                   |                    | bit 0        |  |

|                 |            |                                    |                 |                  |                                   |                    |              |  |

| Legend:         |            |                                    |                 |                  |                                   |                    |              |  |

| R = Readable    | bit        | W = Writable                       | bit             | U = Unimple      | mented bit, read                  | as '0'             |              |  |

| -n = Value at P | POR        | '1' = Bit is set                   |                 | '0' = Bit is cle | eared                             | x = Bit is unknown |              |  |

|                 |            |                                    |                 |                  |                                   |                    |              |  |

| bit 15          | CHPCLKEN:  | Enable Chop                        | Clock Generat   | tor bit          |                                   |                    |              |  |

|                 | •          | ck generator is<br>ck generator is |                 |                  |                                   |                    |              |  |

| bit 14-10       | •          | ited: Read as '                    |                 |                  |                                   |                    |              |  |

|                 | -          |                                    |                 |                  |                                   |                    |              |  |

| bit 9-3         | CHOPCLK<6  | 5:0>: Chop Clo                     | ck Divider bits | 5                |                                   |                    |              |  |

|                 |            |                                    |                 |                  | ollowing expressionary Master PWN |                    | CLKDIV<2:0>) |  |

| bit 2-0         | Unimplemen | ted: Read as '                     | 0'              |                  |                                   |                    |              |  |

|                 | -          |                                    |                 |                  |                                   |                    |              |  |

NOTES:

## REGISTER 18-1: U1MODE: UART1 MODE REGISTER (CONTINUED)

| bit 4   | URXINV: Receive Polarity Inversion bit <sup>(3)</sup>                                                                                                                              |

|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | 1 = U1RX Idle state is '0'                                                                                                                                                         |

|         | 0 = U1RX Idle state is '1'                                                                                                                                                         |

| bit 3   | BRGH: High Baud Rate Enable bit <sup>(3)</sup>                                                                                                                                     |

|         | <ul> <li>1 = BRG generates 4 clocks per bit period (4x baud clock, High-Speed mode)</li> <li>0 = BRG generates 16 clocks per bit period (16x baud clock, Standard mode)</li> </ul> |

| bit 2-1 | PDSEL<1:0>: Parity and Data Selection bits <sup>(3)</sup>                                                                                                                          |

|         | 11 = 9-bit data, no parity                                                                                                                                                         |

|         | 10 = 8-bit data, odd parity                                                                                                                                                        |

|         | 01 = 8-bit data, even parity<br>00 = 8-bit data, no parity                                                                                                                         |

|         |                                                                                                                                                                                    |

| bit 0   | STSEL: Stop Bit Selection bit <sup>(3)</sup>                                                                                                                                       |

|         | 1 = Two Stop bits                                                                                                                                                                  |

|         | 0 = One Stop bit                                                                                                                                                                   |

|         |                                                                                                                                                                                    |

- **Note 1:** Refer to **Section 17. "UART**" (DS70188) in the *"dsPIC33F/PIC24H Family Reference Manual"* for information on enabling the UART module for receive or transmit operation.

- **2:** This feature is only available for the 16x BRG mode (BRGH = 0).

- 3: This bit is not available in the dsPIC33FJ06GS001 device.

### 20.3 Module Applications

This module provides a means for the SMPS dsPIC DSC devices to monitor voltage and currents in a power conversion application. The ability to detect transient conditions and stimulate the dsPIC DSC processor and/or peripherals, without requiring the processor and ADC to constantly monitor voltages or currents, frees the dsPIC DSC to perform other tasks.

The comparator module has a high-speed comparator, an associated 10-bit DAC and a DAC output amplifier that provide a programmable reference voltage to the inverting input of the comparator. The polarity of the comparator output is user-programmable. The output of the module can be used in the following modes:

- · Generate an Interrupt

- Trigger an ADC Sample and Convert Process

- · Truncate the PWM Signal (current limit)

- Truncate the PWM Period (current minimum)

- Disable the PWM Outputs (Fault latch)

The output of the comparator module may be used in multiple modes at the same time, such as: 1) generate an interrupt, 2) have the ADC take a sample and convert it, and 3) truncate the PWM output in response to a voltage being detected beyond its expected value.

The comparator module can also be used to wake-up the system from Sleep or Idle mode when the analog input voltage exceeds the programmed threshold voltage.

### 20.4 DAC

The range of the DAC is controlled via an analog multiplexer that selects either AVDD/2, an internal reference source, INTREF, or an external reference source, EXTREF. The full range of the DAC (AVDD/2) will typically be used when the chosen input source pin is shared with the ADC. The reduced range option (INTREF) will likely be used when monitoring current levels using a current sense resistor. Usually, the measured voltages in such applications are small (<1.25V); therefore, the option of using a reduced reference range for the comparator extends the available DAC resolution in these applications. The use of an external reference enables the user to connect to a reference that better suits their application.

DACOUT, shown in Figure 20-1, can only be associated with a single comparator at a given time.

| Note: | It should be ensured in software that     |

|-------|-------------------------------------------|

|       | multiple DACOE bits are not set. The      |

|       | output on the DACOUT pin will be indeter- |

|       | minate if multiple comparators enable the |

|       | DAC output.                               |

### 20.5 DAC Buffer Gain

The output of the DAC is buffered/amplified via the DAC buffer. The block functions as a 1x gain amplifier or as a 1.8x gain amplifier. The gain selection is controlled via the HGAIN bit in the CMPCONx register. Using the 1.8x gain option will raise the reference voltage to the analog comparator to a maximum of 2.8V. Using a higher reference voltage for the analog comparator can improve the signal-to-noise ratio in an application.

### 20.6 Comparator Input Range

The comparator has an input voltage range from -0.2V to AVDD + 0.2V, making it a rail-to-rail input.

### 20.7 Digital Logic

The CMPCONx register (see Register 20-1) provides the control logic that configures the High-Speed Analog Comparator module. The digital logic provides a pulse stretcher. The analog comparator can respond to very fast transient signals. After the comparator output is given the desired polarity, the signal is passed to this pulse stretching circuit. The pulse stretching circuit has an asynchronous set function and a delay circuit that insure the minimum pulse width is three system clock cycles wide so that the attached circuitry can properly respond.

The stretch circuit is followed by a digital filter. The digital filter is enabled via the FLTREN bit in the CMPCONx register. The digital filter operates with the clock specified via the FCLKSEL bit in the CMPCONx register. The comparator signal must be stable in a high or low state for at least three of the selected clock cycles for it to pass through the digital filter.

During Sleep mode, the clock signal inputs to the module are disabled. However, the module's analog components may continue to function in a reduced power manner to allow the user to wake-up the device when a signal is applied to a comparator input.

In Sleep mode, the clocks are stopped; however, the analog comparator signal has an asynchronous connection across the filter that allows interrupts to be generated regardless of the stopped clocks.

The comparator can be disabled while in Idle mode if the CMPSIDL bit is set. If a device has multiple comparators, and any CMPSIDL bit is set, the entire group of comparators will be disabled while in Idle mode. The advantage is reduced power consumption. Moreover, this behavior reduces complexity in the design of the clock control logic for this module.

| U-0                                           | U-0        | U-0              | U-0          | U-0                                | U-0            | R/W-0                     | R/W-0       |  |

|-----------------------------------------------|------------|------------------|--------------|------------------------------------|----------------|---------------------------|-------------|--|

| _                                             | —          | —                | _            |                                    | —              | CMREF<9:8> <sup>(1)</sup> |             |  |

| bit 15                                        |            |                  |              |                                    |                |                           | bit 8       |  |

|                                               |            |                  |              |                                    |                |                           |             |  |

| R/W-0                                         | R/W-0      | R/W-0            | R/W-0        | R/W-0                              | R/W-0          | R/W-0                     | R/W-0       |  |

| CMREF<7:0> <sup>(1)</sup>                     |            |                  |              |                                    |                |                           |             |  |

| bit 7                                         |            |                  |              |                                    |                |                           | bit 0       |  |

|                                               |            |                  |              |                                    |                |                           |             |  |