Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                         |

| Core Processor             | F <sup>2</sup> MC-16LX                                                           |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 24MHz                                                                            |

| Connectivity               | CANbus, EBI/EMI, I <sup>2</sup> C, LINbus, UART/USART                            |

| Peripherals                | DMA, LVD, POR, WDT                                                               |

| Number of I/O              | 51                                                                               |

| Program Memory Size        | 128KB (128K x 8)                                                                 |

| Program Memory Type        | Mask ROM                                                                         |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 4K x 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 3.5V ~ 5.5V                                                                      |

| Data Converters            | A/D 15x8/10b                                                                     |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 64-LQFP                                                                          |

| Supplier Device Package    | 64-LQFP (12x12)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/mb90352espmc-gs-162e1 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 1. Product Lineup1 (Without Clock supervisor function)

#### Flash memory products

| Part Number                                     | MB90F351E                                                  | MB90F351TE                                                                                                                                                                           | MB90F351ES                                     | MB90F351TES |  |  |  |  |  |

|-------------------------------------------------|------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------|-------------|--|--|--|--|--|

| Parameter                                       | MB90F352E                                                  | MB90F352TE                                                                                                                                                                           | MB90F352ES                                     | MB90F352TES |  |  |  |  |  |

| Туре                                            |                                                            | Flash memo                                                                                                                                                                           | ory products                                   |             |  |  |  |  |  |

| CPU                                             |                                                            | F <sup>2</sup> MC-16LX CPU                                                                                                                                                           |                                                |             |  |  |  |  |  |

| System clock                                    | Minimum instruction execut                                 | LL clock multiplication circuit (× 1, × 2, × 3, × 4, × 6, 1/2 when PLL stops) linimum instruction execution time : 42 ns (oscillation clock 4 MHz, PLL × 6)                          |                                                |             |  |  |  |  |  |

| ROM                                             | 128 Kbytes Dual operation                                  | 4 Kbytes Flash memory : MB90F351E(S), MB90F351TE(S)<br>28 Kbytes Dual operation Flash memory (Erase/write and read can be operated at the same time) :<br>B90F352E(S), MB90F352TE(S) |                                                |             |  |  |  |  |  |

| RAM                                             |                                                            | 4 Kb                                                                                                                                                                                 | oytes                                          |             |  |  |  |  |  |

| Emulator-specific power supply*                 |                                                            | -                                                                                                                                                                                    | -                                              |             |  |  |  |  |  |

| Sub clock pin<br>(X0A, X1A)<br>(Max 100 kHz)    | Y                                                          | es                                                                                                                                                                                   | Ν                                              | 0           |  |  |  |  |  |

| Clock supervisor                                |                                                            | N                                                                                                                                                                                    | lo                                             |             |  |  |  |  |  |

| Low voltage/CPU<br>operation detection<br>reset | No                                                         | Yes                                                                                                                                                                                  | No                                             | Yes         |  |  |  |  |  |

| Operating voltage                               |                                                            | perating (not using A/D conv<br>) converter/Flash programm<br>ernal bus                                                                                                              |                                                |             |  |  |  |  |  |

| Operating<br>temperature                        |                                                            | -40°C to                                                                                                                                                                             | o +125°C                                       |             |  |  |  |  |  |

| Package                                         |                                                            | LQF                                                                                                                                                                                  | P-64                                           |             |  |  |  |  |  |

|                                                 |                                                            | 2 cha                                                                                                                                                                                | nnels                                          |             |  |  |  |  |  |

| LIN-UART                                        | Special synchronous option                                 | ttings using a dedicated bau<br>ns for adapting to different sy<br>ther as master or slave LIN o                                                                                     | •                                              | er)         |  |  |  |  |  |

| I <sup>2</sup> C (400 kbps)                     |                                                            | 1 cha                                                                                                                                                                                | annel                                          |             |  |  |  |  |  |

|                                                 |                                                            | 15 cha                                                                                                                                                                               | annels                                         |             |  |  |  |  |  |

| A/D converter                                   | •                                                          | includes sample time (per c                                                                                                                                                          | ,                                              |             |  |  |  |  |  |

| 16-bit reload timer<br>(2 channels)             | Operation clock frequency<br>Supports External Event Co    |                                                                                                                                                                                      | ys = Machine clock frequenc                    | cy)         |  |  |  |  |  |

|                                                 | Free-run Timer 0 (clock inp<br>Free-run Timer 1 (clock inp | ut FRCK0) corresponds to I0<br>ut FRCK1) corresponds to I0                                                                                                                           | CU0/1.<br>CU4/5/6/7, OCU4/5/6/7.               |             |  |  |  |  |  |

| 16-bit Free-run timer<br>(2 channels)           | Signals an interrupt when overhowing.                      |                                                                                                                                                                                      |                                                |             |  |  |  |  |  |

| 16-bit output                                   |                                                            | 4 cha                                                                                                                                                                                | nnels                                          |             |  |  |  |  |  |

| compare                                         |                                                            | 6-bit free-run Timer matches<br>can be used to generate an                                                                                                                           | s with output compare registent output signal. | ers.        |  |  |  |  |  |

| Pin No.  | Pin name                                     | I/O<br>Circuit<br>type* | Function                                                                                                                                                                                                                                                                   |

|----------|----------------------------------------------|-------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 39       | P17                                          | G                       | General purpose I/O port. The register can be set to select whether to use a pull-up resistor. This function is enabled in single-chip mode.                                                                                                                               |

| 39       | AD15                                         |                         | Input/output pin for external bus address data bus bit 15.<br>This function is enabled when external bus is enabled.                                                                                                                                                       |

|          | P20 to P23                                   |                         | General purpose I/O ports. The register can be set to select whether to use a pull-up resistor.<br>In external bus mode, the pins are enabled as a general-<br>purpose I/O port when the corresponding bit in the external address output control register<br>(HACR) is 1. |

| 40 to 43 | A16 to A19                                   | G                       | Output pins for A16 to A19 of the external address data bus.<br>When the corresponding bit in the external address output control register (HACR) is 0, the pins<br>are enabled as high address output pins A16 to A19.                                                    |

|          | PPG9 (8)<br>PPGB (A)<br>PPGD (C)<br>PPGF (E) |                         | Output pins for PPGs                                                                                                                                                                                                                                                       |

|          | P24                                          |                         | General purpose I/O port. The register can be set to select whether to use a pull-up resistor. In external bus mode, the pin is enabled as a general-<br>purpose I/O port when the corresponding bit in the external address output control register (HACR) is 1.          |

| 44       | A20                                          | G                       | Output pin for A20 of the external address data bus. When the corresponding bit in the external address output control register (HACR) is 0, the pin is enabled as high address output pin A20.                                                                            |

|          | IN0                                          |                         | Data sample input pin for input capture ICU0                                                                                                                                                                                                                               |

|          | P25                                          |                         | General purpose I/O port. The register can be set to select whether to use a pull-up resistor. In external bus mode, the pin is enabled as a general-<br>purpose I/O port when the corresponding bit in the external address output control register (HACR) is 1.          |

| 51       | A21                                          | G                       | Output pin for A21 of the external address data bus. When the corresponding bit in the external address output control register (HACR) is 0, the pin is enabled as high address output pin A21.                                                                            |

|          | IN1                                          |                         | Data sample input pin for input capture ICU1                                                                                                                                                                                                                               |

|          | ADTG                                         |                         | Trigger input pin for A/D converter                                                                                                                                                                                                                                        |

|          | P44                                          |                         | General purpose I/O port                                                                                                                                                                                                                                                   |

| 52       | 52 SDA0                                      |                         | Serial data I/O pin for I <sup>2</sup> C 0                                                                                                                                                                                                                                 |

|          | FRCK0                                        |                         | Input pin for the 16-bit Free-run Timer 0                                                                                                                                                                                                                                  |

|          | P45                                          |                         | General purpose I/O port                                                                                                                                                                                                                                                   |

| 53       | SCL0                                         | н                       | Serial clock I/O pin for I <sup>2</sup> C 0                                                                                                                                                                                                                                |

|          | FRCK1                                        |                         | Input pin for the 16-bit Free-run Timer 1                                                                                                                                                                                                                                  |

| Pin No. | Pin name | I/O<br>Circuit<br>type* | Function                                                                                                                                                                                                                                                                           |

|---------|----------|-------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | P30      |                         | General purpose I/O port. The register can be set to select whether to use a pull-up resistor. This function is enabled in single-chip mode.                                                                                                                                       |

| 54      | ALE      | G                       | Address latch enable output pin. This function is enabled when external bus is enabled.                                                                                                                                                                                            |

|         | IN4      |                         | Data sample input pin for input capture ICU4                                                                                                                                                                                                                                       |

|         | P31      |                         | General purpose I/O port. The register can be set to select whether to use a pull-up resistor. This function is enabled in single-chip mode.                                                                                                                                       |

| 55      | RD       | G                       | Read strobe output pin for data bus. This function is enabled when external bus is enabled.                                                                                                                                                                                        |

|         | IN5      |                         | Data sample input pin for input capture ICU5                                                                                                                                                                                                                                       |

|         | P32      |                         | General purpose I/O port. The register can be set to select wh <u>ether to u</u> se a pull-up resistor. This function is enabled either in single-chip mode or with the WR/WRL pin output disabled.                                                                                |

| 56      | WR/WRL   | G                       | Write strobe output pin for the data bus. This function is enabled when both the external bus and the WR/WRL pin output are enabled. WRL is used to write-strobe 8 lower bits of the data bus in 16-bit access. WR is used to write-strobe 8 bits of the data bus in 8-bit access. |

|         | INT10R   |                         | External interrupt request input pin for INT10                                                                                                                                                                                                                                     |

| 57      | P33      | G                       | General purpose I/O port. The register can be set to select whether to use a pull-up resistor. This function is enabled either in single-chip mode, in external bus 8-bit mode or with the WRH pin output disabled.                                                                |

| 57      | WRH      | G                       | Write strobe output pin for the 8 higher bits of the data bus. This function is enabled when the external bus is enabled, when the external bus 16-bit mode is selected, and when the $\overline{WRH}$ output pin is enabled.                                                      |

|         | P34      |                         | General purpose I/O port. The register can be set to select whether to use a pull-up resistor. This function is enabled either in single-chip mode or with the hold function disabled.                                                                                             |

| 58      | HRQ G    |                         | Hold request input pin. This function is enabled when both the external bus and the hold func-<br>tion are enabled.                                                                                                                                                                |

|         | OUT4     |                         | Wave form output pin for output compare OCU4                                                                                                                                                                                                                                       |

|         | P35      |                         | General purpose I/O port. The register can be set to select whether to use a pull-up resistor. This function is enabled either in single-chip mode or with the hold function disabled.                                                                                             |

| 59      | HAK      | G                       | Hold acknowledge output pin. This function is enabled when both the external bus and the hold function are enabled.                                                                                                                                                                |

|         | OUT5     |                         | Wave form output pin for output compare OCU5                                                                                                                                                                                                                                       |

|         | P36      |                         | General purpose I/O port. The register can be set to select whether to use a pull-up resistor. This function is enabled either in single-chip mode or with the external ready function disabled.                                                                                   |

| 60      | RDY      | G                       | Ready input pin. This function is enabled when both the external bus and the external ready function are enabled.                                                                                                                                                                  |

|         | OUT6     |                         | Wave form output pin for output compare OCU6                                                                                                                                                                                                                                       |

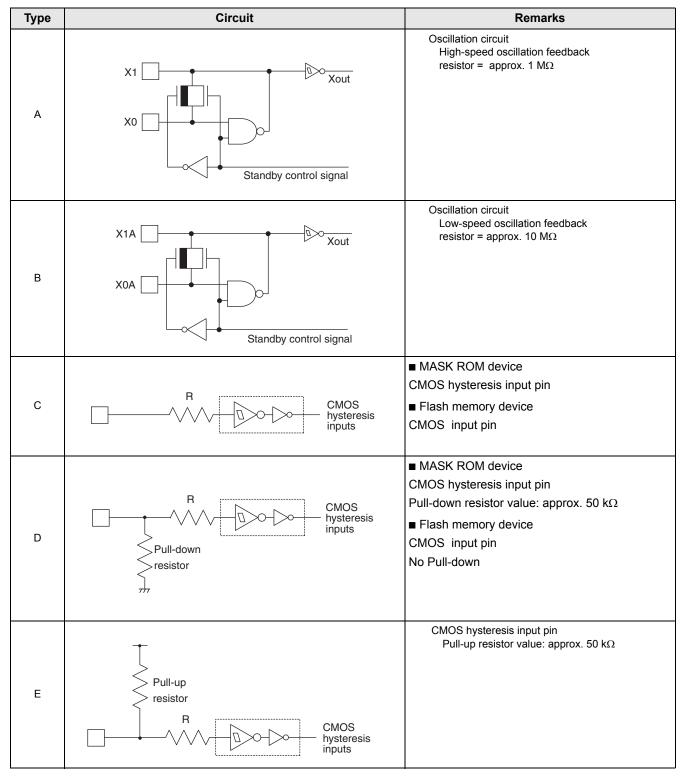

# 6. I/O Circuit Type

Please ask each crystal maker to evaluate the oscillational characteristics of the crystal and this device.

#### Turning-on sequence of power supply to A/D converter and analog inputs 9.

Make sure to turn on the A/D converter power supply (AV<sub>CC</sub>, AVRH) and analog inputs (AN0 to AN14) after turning-on the digital power supply ( $V_{CC}$ ). Turn-off the digital power after turning off the A/D converter power

supply and analog inputs. In this case, make sure that the power supply voltage does not exceed the rated voltage of the A/D converter (turning on/of the analog and digital power supplies simultaneously is acceptable).

#### 10. Connection of unused pins of A/D converter if A/D converter is not used

Connect unused pins of A/D converter to  $AV_{CC} = V_{CC}$ ,  $AV_{SS} = AVRH = V_{SS}$ .

#### 11. Notes on energization

To prevent the internal regulator circuit from malfunctioning, set the voltage rise time during energization at 50  $\mu$ s or more (0.2 V to 2.7 V).

#### 12. Stabilization of power supply voltage

A sudden change in the supply voltage may cause the device to malfunction even within the V<sub>CC</sub> supply voltage operating range. Therefore, the V<sub>CC</sub> supply voltage should be stabilized. For reference, the supply voltage should be controlled so that V<sub>CC</sub> ripple variations (peak- to-peak values) at commercial frequencies (50 MHz/ 60 MHz) fall below 10% of the standard V<sub>CC</sub> supply voltage and the coefficient of fluctuation does not exceed 0.1 V/ms at instanta-

neous power switching.

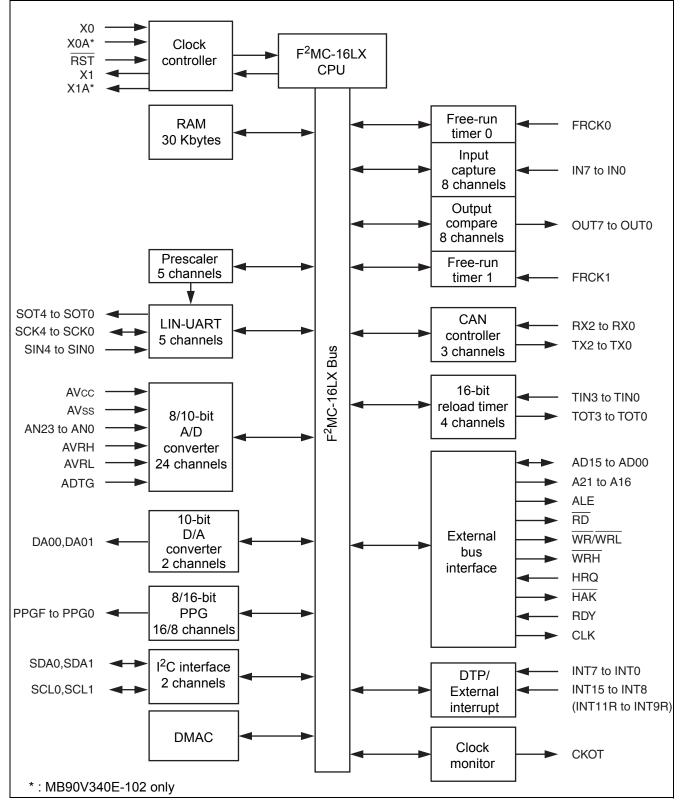

# 8. Block Diagrams

### MB90V340E-101/102

# 10. I/O Map

| Address                                       | Register                            | Abbreviation | Access | Resource name | Initial value         |

|-----------------------------------------------|-------------------------------------|--------------|--------|---------------|-----------------------|

| 000000 <sub>H</sub>                           | Port 0 Data Register                | PDR0         | R/W    | Port 0        | XXXXXXXXAB            |

| 000001 <sub>H</sub>                           | Port 1 Data Register                | PDR1         | R/W    | Port 1        | XXXXXXXXAB            |

| 000002 <sub>H</sub>                           | Port 2 Data Register                | PDR2         | R/W    | Port 2        | XXXXXXXXB             |

| 000003 <sub>H</sub>                           | Port 3 Data Register                | PDR3         | R/W    | Port 3        | XXXXXXXXAB            |

| 000004 <sub>H</sub>                           | Port 4 Data Register                | PDR4         | R/W    | Port 4        | XXXXXXXXAB            |

| 000005 <sub>H</sub>                           | Port 5 Data Register                | PDR5         | R/W    | Port 5        | XXXXXXXXB             |

| 000006 <sub>H</sub>                           | Port 6 Data Register                | PDR6         | R/W    | Port 6        | XXXXXXXX <sub>B</sub> |

| 000007 <sub>H</sub> to<br>00000A <sub>H</sub> |                                     | Reserve      | d      |               |                       |

| 00000B <sub>H</sub>                           | Port 5 Analog Input Enable Register | ADER5        | R/W    | Port 5, A/D   | 11111111 <sub>B</sub> |

| 00000C <sub>H</sub>                           | Port 6 Analog Input Enable Register | ADER6        | R/W    | Port 6, A/D   | 11111111 <sub>B</sub> |

| 00000D <sub>H</sub>                           |                                     | Reserve      | d      |               |                       |

| 00000E <sub>H</sub>                           | Input Level Select Register 0       | ILSR0        | R/W    | Ports         | 00000000 <sub>B</sub> |

| 00000F <sub>H</sub>                           | Input Level Select Register 1       | ILSR1        | R/W    | Ports         | 00000000 <sub>B</sub> |

| 000010 <sub>H</sub>                           | Port 0 Direction Register           | DDR0         | R/W    | Port 0        | 00000000 <sub>B</sub> |

| 000011 <sub>H</sub>                           | Port 1 Direction Register           | DDR1         | R/W    | Port 1        | 00000000 <sub>B</sub> |

| 000012 <sub>H</sub>                           | Port 2 Direction Register           | DDR2         | R/W    | Port 2        | XX000000 <sub>B</sub> |

| 000013 <sub>H</sub>                           | Port 3 Direction Register           | DDR3         | R/W    | Port 3        | 00000000 <sub>B</sub> |

| 000014 <sub>H</sub>                           | Port 4 Direction Register           | DDR4         | R/W    | Port 4        | XX000000 <sub>B</sub> |

| 000015 <sub>H</sub>                           | Port 5 Direction Register           | DDR5         | R/W    | Port 5        | X0000000 <sub>B</sub> |

| 000016 <sub>H</sub>                           | Port 6 Direction Register           | DDR6         | R/W    | Port 6        | 00000000 <sub>B</sub> |

| 000017 <sub>H</sub> to<br>000019 <sub>H</sub> |                                     | Reserve      | d      |               |                       |

| 00001A <sub>H</sub>                           | SIN input Level Setting Register    | DDRA         | W      | UART2, UART3  | X00XXXXX <sub>B</sub> |

| 00001B <sub>H</sub>                           |                                     | Reserve      | d      |               |                       |

| 00001C <sub>H</sub>                           | Port 0 Pull-up Control Register     | PUCR0        | R/W    | Port 0        | 00000000 <sub>B</sub> |

| 00001D <sub>H</sub>                           | Port 1 Pull-up Control Register     | PUCR1        | R/W    | Port 1        | 00000000 <sub>B</sub> |

| 00001E <sub>H</sub>                           | Port 2 Pull-up Control Register     | PUCR2        | R/W    | Port 2        | 00000000 <sub>B</sub> |

| 00001F <sub>H</sub>                           | Port 3 Pull-up Control Register     | PUCR3        | R/W    | Port 3        | 00000000 <sub>B</sub> |

| 000020 <sub>H</sub> to<br>000037 <sub>H</sub> |                                     | Reserve      | d      |               |                       |

| Address                                      | Register                                     | Abbreviation | Access | Resource name                              | Initial value         |

|----------------------------------------------|----------------------------------------------|--------------|--------|--------------------------------------------|-----------------------|

| 000038 <sub>H</sub>                          | PPG 4 Operation Mode Control Register        | PPGC4        | W, R/W |                                            | 0X000XX1 <sub>B</sub> |

| 000039 <sub>H</sub>                          | PPG 5 Operation Mode Control Register        | PPGC5        | W, R/W | 16-bit Programmable Pulse<br>Generator 4/5 | 0X000001 <sub>B</sub> |

| 00003A <sub>H</sub>                          | PPG 4/5 Count Clock Select Register          | PPG45        | R/W    |                                            | 000000X0 <sub>B</sub> |

| 00003B <sub>H</sub>                          | Address Detect Control Register 1            | PACSR1       | R/W    | Address Match<br>Detection 1               | 00000000 <sub>B</sub> |

| 00003C <sub>H</sub>                          | PPG 6 Operation Mode Control Register        | PPGC6        | W, R/W |                                            | 0X000XX1 <sub>B</sub> |

| 00003D <sub>H</sub>                          | PPG 7 Operation Mode Control Register        | PPGC7        | W, R/W | 16-bit Programmable Pulse<br>Generator 6/7 | 0X000001 <sub>B</sub> |

| 00003E <sub>H</sub>                          | PPG 6/7 Count Clock Select Register          | PPG67        | R/W    |                                            | 000000X0 <sub>B</sub> |

| 00003F <sub>H</sub>                          |                                              | Reserved     |        |                                            |                       |

| 000040 <sub>H</sub>                          | PPG 8 Operation Mode Control Register        | PPGC8        | W, R/W |                                            | 0X000XX1 <sub>B</sub> |

| 000041 <sub>H</sub>                          | PPG 9 Operation Mode Control Register        | PPGC9        | W, R/W | 16-bit Programmable Pulse<br>Generator 8/9 | 0X000001 <sub>B</sub> |

| 000042 <sub>H</sub>                          | PPG 8/9 Count Clock Select Register          | PPG89        | R/W    |                                            | 000000X0 <sub>B</sub> |

| 000043 <sub>H</sub>                          |                                              | Reserved     |        |                                            |                       |

| 000044 <sub>H</sub>                          | PPG A Operation Mode Control Register        | PPGCA        | W, R/W |                                            | 0X000XX1 <sub>B</sub> |

| 000045 <sub>H</sub>                          | PPG B Operation Mode Control Register        | PPGCB        | W, R/W | 16-bit Programmable Pulse<br>Generator A/B | 0X000001 <sub>B</sub> |

| 000046 <sub>H</sub>                          | PPG A/B Count Clock Select Register          | PPGAB        | R/W    |                                            | 000000X0 <sub>B</sub> |

| 000047 <sub>H</sub>                          |                                              | Reserved     | •      |                                            |                       |

| 000048 <sub>H</sub>                          | PPG C Operation Mode Control Register        | PPGCC        | W,R/W  |                                            | 0X000XX1 <sub>B</sub> |

| 000049 <sub>H</sub>                          | PPG D Operation Mode Control Register        | PPGCD        | W,R/W  | 16-bit Programmable Pulse<br>Generator C/D | 0X000001 <sub>B</sub> |

| 00004A <sub>H</sub>                          | PPG C/D Count Clock Select Register          | PPGCD        | R/W    |                                            | 000000X0 <sub>B</sub> |

| 00004B <sub>H</sub>                          |                                              | Reserved     |        | ·                                          |                       |

| 00004C <sub>H</sub>                          | PPG E Operation Mode Control Register        | PPGCE        | W,R/W  |                                            | 0X000XX1 <sub>B</sub> |

| 00004D <sub>H</sub>                          | PPG F Operation Mode Control Register        | PPGCF        | W,R/W  | 16-bit Programmable Pulse<br>Generator E/F | 0X000001 <sub>B</sub> |

| 00004E <sub>H</sub>                          | PPG E/F Count Clock Select Register          | PPGEF        | R/W    |                                            | 000000X0 <sub>B</sub> |

| 00004F <sub>H</sub>                          |                                              | Reserved     |        | ·                                          |                       |

| 000050 <sub>H</sub>                          | Input Capture Control Status<br>Register 0/1 | ICS01        | R/W    | Input Capture 0/1                          | 00000000 <sub>B</sub> |

| 000051 <sub>H</sub>                          | Input Capture Edge Register 0/1              | ICE01        | R/W, R |                                            | XXX0X0XX <sub>B</sub> |

| 000052 <sub>H</sub> ,<br>000053 <sub>H</sub> |                                              | Reserved     |        |                                            |                       |

| 000054 <sub>H</sub>                          | Input Capture Control Status<br>Register 4/5 | ICS45        | R/W    | Input Capture 4/5                          | 00000000 <sub>B</sub> |

| 000055 <sub>H</sub>                          | Input Capture Edge Register 4/5              | ICE45        | R      |                                            | XXXXXXXAB             |

| 000056 <sub>H</sub>                          | Input Capture Control Status<br>Register 6/7 | ICS67        | R/W    | Input Capture 6/7                          | 00000000 <sub>B</sub> |

| 000057 <sub>H</sub>                          | Input Capture Edge Register 6/7              | ICE67        | R/W, R |                                            | XXX000XX <sub>B</sub> |

| Address                                          | Register                                                      | Abbreviation | Access | Resource name                                | Initial value         |  |

|--------------------------------------------------|---------------------------------------------------------------|--------------|--------|----------------------------------------------|-----------------------|--|

| 000058 <sub>H</sub><br>to<br>00005B <sub>H</sub> |                                                               | Reserved     |        |                                              |                       |  |

| 00005C <sub>H</sub>                              | Output Compare Control Status<br>Register 4                   | OCS4         | R/W    | Output Compare 4/5                           | 0000XX00 <sub>B</sub> |  |

| 00005D <sub>H</sub>                              | Output Compare Control Status<br>Register 5                   | OCS5         | R/W    | Output Compare 4/5                           | 0XX00000 <sub>B</sub> |  |

| 00005E <sub>H</sub>                              | Output Compare Control Status<br>Register 6                   | OCS6         | R/W    | Output Company 6/7                           | 0000XX00 <sub>B</sub> |  |

| 00005F <sub>H</sub>                              | Output Compare Control Status<br>Register 7                   | OCS7         | R/W    | Output Compare 6/7                           | 0XX00000 <sub>B</sub> |  |

| 000060 <sub>H</sub>                              | Timer Control Status Register 0                               | TMCSR0       | R/W    | 40 bit Dalaget Timer 0                       | 00000000 <sub>B</sub> |  |

| 000061 <sub>H</sub>                              | Timer Control Status Register 0                               | TMCSR0       | R/W    | 16-bit Reload Timer 0                        | XXXX0000 <sub>B</sub> |  |

| 000062 <sub>H</sub>                              | Timer Control Status Register 1                               | TMCSR1       | R/W    | 16 hit Delead Timer 1                        | 00000000 <sub>B</sub> |  |

| 000063 <sub>H</sub>                              | Timer Control Status Register 1                               | TMCSR1       | R/W    | 16-bit Reload Timer 1                        | XXXX0000 <sub>B</sub> |  |

| 000064 <sub>H</sub>                              | Timer Control Status Register 2                               | TMCSR2       | R/W    | 40 kit Dala ad Tim an 0                      | 00000000 <sub>B</sub> |  |

| 000065 <sub>H</sub>                              | Timer Control Status Register 2                               | TMCSR2       | R/W    | 16-bit Reload Timer 2                        | XXXX0000 <sub>B</sub> |  |

| 000066 <sub>H</sub>                              | Timer Control Status Register 3                               | TMCSR3       | R/W    | 40 bit Dalaged Timer 2                       | 00000000 <sub>B</sub> |  |

| 000067 <sub>H</sub>                              | Timer Control Status Register 3                               | TMCSR3       | R/W    | 16-bit Reload Timer 3                        | XXXX0000 <sub>B</sub> |  |

| 000068 <sub>H</sub>                              | A/D Control Status Register 0                                 | ADCS0        | R/W    |                                              | 000XXXX0 <sub>B</sub> |  |

| 000069 <sub>H</sub>                              | A/D Control Status Register 1                                 | ADCS1        | R/W    |                                              | 0000000X <sub>B</sub> |  |

| 00006A <sub>H</sub>                              | A/D Data Register 0                                           | ADCR0        | R      | A/D Oceanity                                 | 00000000 <sub>B</sub> |  |

| 00006B <sub>H</sub>                              | A/D Data Register 1                                           | ADCR1        | R      | A/D Converter                                | XXXXXX00 <sub>B</sub> |  |

| 00006C <sub>H</sub>                              | ADC Setting Register 0                                        | ADSR0        | R/W    |                                              | 00000000 <sub>B</sub> |  |

| 00006D <sub>H</sub>                              | ADC Setting Register 1                                        | ADSR1        | R/W    |                                              | 00000000 <sub>B</sub> |  |

| 00006E <sub>H</sub>                              | Low Voltage/CPU Operation Detection Reset<br>Control Register | LVRC         | R/W, W | Low Voltage/CPU<br>Operation Detection Reset | 00111000 <sub>B</sub> |  |

| 00006F <sub>H</sub>                              | ROM Mirror Function Select Register                           | ROMM         | W      | ROM Mirror                                   | XXXXXXX1 <sub>B</sub> |  |

| 000070 <sub>H</sub><br>to<br>00007F <sub>H</sub> |                                                               | Reserved     |        | ·                                            |                       |  |

| 000080 <sub>H</sub><br>to<br>00008F <sub>H</sub> | Reserved for CAN controller 1. Refer to "CAN C                | ontrollers"  |        |                                              |                       |  |

| 000090 <sub>H</sub><br>to<br>00009A <sub>H</sub> | Reserved                                                      |              |        |                                              |                       |  |

| Address                                      | Register                                                                     | Abbreviation | Access | Resource name                               | Initial value         |

|----------------------------------------------|------------------------------------------------------------------------------|--------------|--------|---------------------------------------------|-----------------------|

| 00009B <sub>H</sub>                          | DMA Descriptor Channel Specification Register                                | DCSR         | R/W    |                                             | 00000000 <sub>B</sub> |

| 00009C <sub>H</sub>                          | DMA Status Register L Register                                               | DSRL         | R/W    | DMA                                         | 00000000 <sub>B</sub> |

| 00009D <sub>H</sub>                          | DMA Status Register H Register                                               | DSRH         | R/W    |                                             | 00000000 <sub>B</sub> |

| 00009E <sub>H</sub>                          | Address Detect Control Register 0                                            | PACSR0       | R/W    | Address Match<br>Detection 0                | 00000000 <sub>B</sub> |

| 00009F <sub>H</sub>                          | Delayed Interrupt/Release Register                                           | DIRR         | R/W    | Delayed Interrupt                           | XXXXXXX0 <sub>B</sub> |

| 0000A0 <sub>H</sub>                          | Low-power Consumption Mode<br>Control Register                               | LPMCR        | W,R/W  | Low Power<br>Consumption<br>Control Circuit | 00011000 <sub>B</sub> |

| 0000A1 <sub>H</sub>                          | Clock Selection Register                                                     | CKSCR        | R,R/W  | Low Power<br>Consumption<br>Control Circuit | 11111100 <sub>B</sub> |

| 0000A2 <sub>H</sub> ,<br>0000A3 <sub>H</sub> |                                                                              | Reserved     |        |                                             |                       |

| 0000A4 <sub>H</sub>                          | DMA Stop Status Register                                                     | DSSR         | R/W    | DMA                                         | 00000000 <sub>B</sub> |

| 0000A5 <sub>H</sub>                          | Automatic Ready Function Selection<br>Register                               | ARSR         | W      | External Memory                             | 0011XX00 <sub>B</sub> |

| 0000A6 <sub>H</sub>                          | External Address Output Control Register                                     | HACR         | W      | Access                                      | 00000000 <sub>B</sub> |

| 0000A7 <sub>H</sub>                          | Bus Control Signal Selection Register                                        | ECSR         | W      |                                             | 0000000X <sub>B</sub> |

| 0000A8 <sub>H</sub>                          | Watchdog Control Register                                                    | WDTC         | R,W    | Watchdog Timer                              | XXXXX111 <sub>B</sub> |

| 0000A9 <sub>H</sub>                          | Timebase Timer Control Register                                              | TBTC         | W,R/W  | Timebase timer                              | 1XX00100 <sub>B</sub> |

| 0000AA <sub>H</sub>                          | Watch Timer Control Register                                                 | WTC          | R,R/W  | Watch Timer                                 | 1X001000 <sub>B</sub> |

| 0000AB <sub>H</sub>                          |                                                                              | Reserved     |        |                                             |                       |

| 0000AC <sub>H</sub>                          | DMA Enable Register L Register                                               | DERL         | R/W    | DMA                                         | 00000000 <sub>B</sub> |

| 0000AD <sub>H</sub>                          | DMA Enable Register H Register                                               | DERH         | R/W    | DIVIA                                       | 00000000 <sub>B</sub> |

| 0000AE <sub>H</sub>                          | Flash Control Status Register<br>(Flash Devices only. Otherwise<br>reserved) | FMCS         | R,R/W  | Flash memory                                | 000X0000 <sub>B</sub> |

| 0000AF <sub>H</sub>                          |                                                                              | Reserved     | 1      |                                             |                       |

| 0000B0 <sub>H</sub>                          | Interrupt Control Register 00                                                | ICR00        | W,R/W  |                                             | 00000111 <sub>B</sub> |

| 0000B1 <sub>H</sub>                          | Interrupt Control Register 01                                                | ICR01        | W,R/W  |                                             | 00000111 <sub>B</sub> |

| 0000B2 <sub>H</sub>                          | Interrupt Control Register 02                                                | ICR02        | W,R/W  |                                             | 00000111 <sub>B</sub> |

| 0000B3 <sub>H</sub>                          | Interrupt Control Register 03                                                | ICR03        | W,R/W  |                                             | 00000111 <sub>B</sub> |

| 0000B4 <sub>H</sub>                          | Interrupt Control Register 04                                                | ICR04        | W,R/W  | Interrupt Control                           | 00000111 <sub>B</sub> |

| 0000B5 <sub>H</sub>                          | Interrupt Control Register 05                                                | ICR05        | W,R/W  |                                             | 00000111 <sub>B</sub> |

| 0000B6 <sub>H</sub>                          | Interrupt Control Register 06                                                | ICR06        | W,R/W  |                                             | 00000111 <sub>B</sub> |

| 0000B7 <sub>H</sub>                          | Interrupt Control Register 07                                                | ICR07        | W,R/W  |                                             | 00000111 <sub>B</sub> |

| 0000B8 <sub>H</sub>                          | Interrupt Control Register 08                                                | ICR08        | W,R/W  |                                             | 00000111 <sub>B</sub> |

| Address                                                                    | Register                                                              | Abbreviation | Access | Resource name                | Initial value         |  |

|----------------------------------------------------------------------------|-----------------------------------------------------------------------|--------------|--------|------------------------------|-----------------------|--|

| 0079C3 <sub>H</sub> to<br>0079DF <sub>H</sub>                              |                                                                       | Reserve      | d      |                              |                       |  |

| 0079E0 <sub>H</sub>                                                        | Detect Address Setting Register 0                                     | PADR0        | R/W    |                              | XXXXXXXXAB            |  |

| 0079E1 <sub>H</sub>                                                        | Detect Address Setting Register 0                                     | PADR0        | R/W    |                              | XXXXXXXX <sub>B</sub> |  |

| 0079E2 <sub>H</sub>                                                        | Detect Address Setting Register 0                                     | PADR0        | R/W    |                              | XXXXXXXX <sub>B</sub> |  |

| 0079E3 <sub>H</sub>                                                        | Detect Address Setting Register 1                                     | PADR1        | R/W    |                              | XXXXXXXX <sub>B</sub> |  |

| 0079E4 <sub>H</sub>                                                        | Detect Address Setting Register 1                                     | PADR1        | R/W    | Address Match<br>Detection 0 | XXXXXXXX <sub>B</sub> |  |

| 0079E5 <sub>H</sub>                                                        | Detect Address Setting Register 1                                     | PADR1        | R/W    | Botootion o                  | XXXXXXXX <sub>B</sub> |  |

| 0079E6 <sub>H</sub>                                                        | Detect Address Setting Register 2                                     | PADR2        | R/W    |                              | XXXXXXXX <sub>B</sub> |  |

| 0079E7 <sub>H</sub>                                                        | Detect Address Setting Register 2                                     | PADR2        | R/W    |                              | XXXXXXXXB             |  |

| 0079E8 <sub>H</sub>                                                        | Detect Address Setting Register 2                                     | PADR2        | R/W    |                              | XXXXXXXX <sub>B</sub> |  |

| 0079E9 <sub>H</sub><br>to<br>0079EF <sub>H</sub>                           |                                                                       | Reserve      | d      |                              |                       |  |

| 0079F0 <sub>H</sub>                                                        | Detect Address Setting Register 3                                     | PADR3        | R/W    |                              | XXXXXXXX <sub>B</sub> |  |

| 0079F1 <sub>H</sub>                                                        | Detect Address Setting Register 3                                     | PADR3        | R/W    |                              | XXXXXXXXB             |  |

| 0079F2 <sub>H</sub>                                                        | Detect Address Setting Register 3                                     | PADR3        | R/W    |                              | XXXXXXXAB             |  |

| 0079F3 <sub>H</sub>                                                        | Detect Address Setting Register 4                                     | PADR4        | R/W    |                              | XXXXXXXX <sub>B</sub> |  |

| 0079F4 <sub>H</sub>                                                        | Detect Address Setting Register 4                                     | PADR4        | R/W    | Address Match<br>Detection 1 | XXXXXXXXB             |  |

| 0079F5 <sub>H</sub>                                                        | Detect Address Setting Register 4                                     | PADR4        | R/W    | Botootion                    | XXXXXXXXB             |  |

| 0079F6 <sub>H</sub>                                                        | Detect Address Setting Register 5                                     | PADR5        | R/W    |                              | XXXXXXXX <sub>B</sub> |  |

| 0079F7 <sub>H</sub>                                                        | Detect Address Setting Register 5                                     | PADR5        | R/W    |                              | XXXXXXXXB             |  |

| 0079F8 <sub>H</sub>                                                        | Detect Address Setting Register 5                                     | PADR5        | R/W    |                              | XXXXXXXXB             |  |

| 0079F9 <sub>H</sub><br>to<br>007BFF <sub>H</sub><br>007C00 <sub>H</sub> to | Reserved f                                                            | Reserve      | -      | Controllers"                 |                       |  |

| 007DFF <sub>H</sub><br>007E00 <sub>H</sub><br>to 007FFF <sub>H</sub>       | Reserved for CAN controller 1. Refer to "CAN Controllers"<br>Reserved |              |        |                              |                       |  |

Notes : " Initial value of "X" represents unknown value.

" Any write access to reserved addresses in I/O map should not be performed. A read access to reserved addresses results reading unknown value.

### **11. CAN Controllers**

- Compliant with CAN standard Version2.0 Part A and Part B

Supports tr12ansmission/reception in standard frame and extended frame formats

- Supports transmitting of data frames by receiving remote frames

- 16 transmitting/receiving message buffers

- 29-bit ID and 8-byte data

- Multi-level message buffer configuration

- Provides full-bit comparison, full-bit mask, acceptance register 0/acceptance register 1 for each message buffer as ID acceptance mask

- Two acceptance mask registers in either standard frame format or extended frame formats

- Bit rate programmable from 10 kbps to 2 Mbps (when input clock is at 16 MHz)

| Address             | Register       | Abbreviation | Access | Initial Value         |  |

|---------------------|----------------|--------------|--------|-----------------------|--|

| CAN1                |                |              | A00633 |                       |  |

| 007C40 <sub>H</sub> |                |              |        | XXXXXXXX <sub>B</sub> |  |

| 007C41 <sub>H</sub> | ID register 9  | IDR8         | R/W    | XXXXXXXAB             |  |

| 007C42 <sub>H</sub> | ID register 8  | IDRO         |        | XXXXXXXX <sub>B</sub> |  |

| 007C43 <sub>H</sub> |                |              |        | XXXXXXXAB             |  |

| 007C44 <sub>H</sub> |                |              |        | XXXXXXXX <sub>B</sub> |  |

| 007C45 <sub>H</sub> | ID register 0  | IDR9         | R/W    | XXXXXXXAB             |  |

| 007C46 <sub>H</sub> | ID register 9  | IDR9         | R/W    | XXXXXXXX <sub>B</sub> |  |

| 007C47 <sub>H</sub> |                |              |        | XXXXXXXAB             |  |

| 007C48 <sub>H</sub> |                |              |        | XXXXXXXX <sub>B</sub> |  |

| 007C49 <sub>H</sub> | ID register 10 | IDR10        | D/A/   | XXXXXXXXB             |  |

| 007C4A <sub>H</sub> | ID register 10 |              | R/W —  | XXXXXXXX <sub>B</sub> |  |

| 007C4B <sub>H</sub> |                |              |        | XXXXXXXXB             |  |

| 007C4C <sub>H</sub> |                |              |        | XXXXXXXXB             |  |

| 007C4D <sub>H</sub> | ID register 11 | IDR11        | R/W -  | XXXXXXXXB             |  |

| 007C4E <sub>H</sub> | ID register 11 |              |        | XXXXXXXX <sub>B</sub> |  |

| 007C4F <sub>H</sub> |                |              |        | XXXXXXXXB             |  |

| 007C50 <sub>H</sub> |                |              |        | XXXXXXXX <sub>B</sub> |  |

| 007C51 <sub>H</sub> | ID register 42 |              | DAA    | XXXXXXXXB             |  |

| 007C52 <sub>H</sub> | ID register 12 | IDR12        | R/W    | XXXXXXXX <sub>B</sub> |  |

| 007C53 <sub>H</sub> |                |              |        | XXXXXXXXB             |  |

| 007C54 <sub>H</sub> |                |              |        | XXXXXXXXB             |  |

| 007C55 <sub>H</sub> | ID register 10 |              |        | XXXXXXXXB             |  |

| 007C56 <sub>H</sub> | ID register 13 | IDR13        | R/W    | XXXXXXXXB             |  |

| 007C57 <sub>H</sub> |                |              |        | XXXXXXXXB             |  |

| 007C58 <sub>H</sub> |                |              |        | XXXXXXXXB             |  |

| 007C59 <sub>H</sub> | ID register 14 |              |        | XXXXXXXXB             |  |

| 007C5A <sub>H</sub> | ID register 14 | IDR14        | R/W    | XXXXXXXXB             |  |

| 007C5B <sub>H</sub> |                |              |        | XXXXXXXXB             |  |

| 007C5C <sub>H</sub> |                |              |        | XXXXXXXXB             |  |

| 007C5D <sub>H</sub> | ID register 45 |              |        | XXXXXXXXB             |  |

| 007C5E <sub>H</sub> | ID register 15 | IDR15        | R/W —  | XXXXXXXXB             |  |

| 007C5F <sub>H</sub> |                |              |        | XXXXXXXXB             |  |

| Interrupt cause   | El <sup>2</sup> OS | DMA ch Interrupt vector Interrupt contro<br>number |        | Interrupt vector    |        | -                   |

|-------------------|--------------------|----------------------------------------------------|--------|---------------------|--------|---------------------|

|                   | corresponding      | number                                             | Number | Address             | Number | Address             |

| UART 2 RX         | Y2                 | 14                                                 | #39    | FFFF60 <sub>H</sub> | ICR14  | 0000BE <sub>H</sub> |

| UART 2 TX         | Y1                 | 15                                                 | #40    | FFFF5C <sub>H</sub> | 10K14  |                     |

| Flash Memory      | Ν                  | -                                                  | #41    | FFFF58 <sub>H</sub> | ICR15  | 000005              |

| Delayed Interrupt | Ν                  | _                                                  | #42    | FFFF54 <sub>H</sub> | ICK15  | 0000BF <sub>H</sub> |

Y1 : Usable

Y2 : Usable, with El<sup>2</sup>OS stop function

N : Unusable

Notes : •The peripheral resources sharing the ICR register have the same interrupt level.

•When the peripheral resources sharing the ICR register use extended intelligent I/O service, only one can use EI<sup>2</sup>OS at a time.

•When either of the two peripheral resources sharing the ICR register specifies El<sup>2</sup>OS, the other one cannot use interrupts.

# 13. Electrical Characteristics

### 13.1 Absolute Maximum Ratings

| Parameter                                | Symbol               | Ra                    | ting                  | Unit | Remarks                              |

|------------------------------------------|----------------------|-----------------------|-----------------------|------|--------------------------------------|

| Farameter                                | Symbol               | Min                   | Max                   |      | Reliaiks                             |

|                                          | V <sub>CC</sub>      | $V_{SS} - 0.3$        | V <sub>SS</sub> + 6.0 | V    |                                      |

| Power supply voltage*1                   | AV <sub>CC</sub>     | $V_{SS} - 0.3$        | V <sub>SS</sub> + 6.0 | V    | $V_{CC} = AV_{CC}^{*2}$              |

|                                          | AVRH                 | V <sub>SS</sub> - 0.3 | V <sub>SS</sub> + 6.0 | V    | AV <sub>CC</sub> ≥AVRH* <sup>2</sup> |

| Input voltage*1                          | VI                   | V <sub>SS</sub> - 0.3 | V <sub>SS</sub> + 6.0 | V    | *3                                   |

| Output voltage*1                         | Vo                   | V <sub>SS</sub> - 0.3 | V <sub>SS</sub> + 6.0 | V    | *3                                   |

| Maximum Clamp Current                    | I <sub>CLAMP</sub>   | -4.0                  | +4.0                  | mA   | *5                                   |

| Total Maximum Clamp Current              | $\Sigma  I_{CLAMP} $ | _                     | 40                    | mA   | *5                                   |

| "L" level maximum output current         | I <sub>OL</sub>      | _                     | 15                    | mA   | *4                                   |

| "L" level average output current         | I <sub>OLAV</sub>    | _                     | 4                     | mA   | *4                                   |

| "L" level maximum overall output current | Σl <sub>OL</sub>     | _                     | 100                   | mA   | *4                                   |

| "L" level average overall output current | $\Sigma I_{OLAV}$    | _                     | 50                    | mA   | *4                                   |

| "H" level maximum output current         | I <sub>OH</sub>      | —                     | -15                   | mA   | *4                                   |

| "H" level average output current         | I <sub>OHAV</sub>    | _                     | -4                    | mA   | *4                                   |

| "H" level maximum overall output current | Σl <sub>OH</sub>     | _                     | -100                  | mA   | *4                                   |

| "H" level average overall output current | ΣΙ <sub>ΟΗΑV</sub>   | —                     | -50                   | mA   | *4                                   |

| Power consumption                        | PD                   | _                     | 454                   | mW   |                                      |

| Operating temperature                    | т                    | -40                   | +105                  | °C   |                                      |

| Operating temperature                    | Τ <sub>Α</sub>       | -40                   | +125                  | °C   | *6                                   |

| Storage temperature                      | T <sub>STG</sub>     | -55                   | +150                  | °C   |                                      |

### **13.2 Recommended Operating Conditions**

$(V_{SS} = AV_{SS} = 0 V)$

| Parameter             | Symbol                                | Value |     |      | Unit | Remarks                                                                                                                                                |

|-----------------------|---------------------------------------|-------|-----|------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------|

| Falameter             | Symbol                                | Min   | Тур | Max  | Unit | Remarks                                                                                                                                                |

|                       | V <sub>CC</sub> ,<br>AV <sub>CC</sub> | 4.0   | 5.0 | 5.5  | V    | Under normal operation                                                                                                                                 |

| Power supply voltage  |                                       | 3.5   | 5.0 | 5.5  | V    | Under normal operation, when not using the A/D con-<br>verter and not Flash programming.                                                               |

|                       |                                       | 4.5   | 5.0 | 5.5  | V    | When External bus is used.                                                                                                                             |

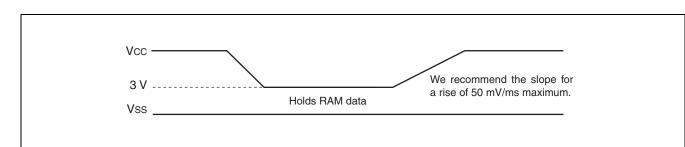

|                       |                                       | 3.0   | -   | 5.5  | V    | Maintains RAM data in stop mode                                                                                                                        |

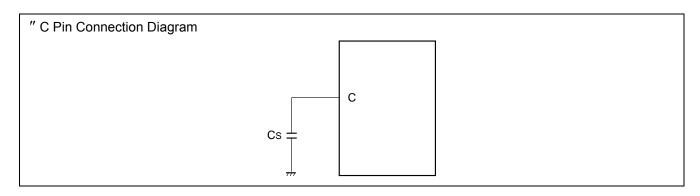

| Smoothing capacitor   | Cs                                    | 0.1   | _   | 1.0  | μF   | Use a ceramic capacitor or comparable capacitor of the AC characteristics. Bypass capacitor at the $V_{CC}$ pin should be greater than this capacitor. |

| Operating temperature | Τ <sub>Α</sub>                        | -40   | —   | +125 | °C   | *                                                                                                                                                      |

\* : If used exceeding  $T_A = +105^{\circ}C$ , be sure to contact Cypress for reliability limitations.

WARNING: The recommended operating conditions are required in order to ensure the normal operation of the semiconductor device. All of the device's electrical characteristics are warranted when the device is operated within these ranges.

Always use semiconductor devices within their recommended operating condition ranges. Operation outside these ranges may adversely affect reliability and could result in device failure. No warranty is made with respect to uses, operating conditions, or combinations not represented on the data sheet. Users considering application outside the listed conditions are advised to contact their representatives beforehand.

# 13.3 DC Characteristics

| Damamadan                        | Ourseland        | Dim                              | Condition                                             | Value                 |                       |                       |                                                          | Dementer                                                                                            |  |

|----------------------------------|------------------|----------------------------------|-------------------------------------------------------|-----------------------|-----------------------|-----------------------|----------------------------------------------------------|-----------------------------------------------------------------------------------------------------|--|

| Parameter                        | Symbol           | Pin                              | Condition                                             | Min                   | Тур                   | Max                   | Unit                                                     | Remarks                                                                                             |  |

| V <sub>IHS</sub> –               | V <sub>IHS</sub> | _                                | _                                                     | 0.8 V <sub>CC</sub>   | _                     | V <sub>CC</sub> + 0.3 | V                                                        | Pin inputs if CMOS<br>hysteresis input levels are se-<br>lected (except P12, P15, P44,<br>P45, P50) |  |

|                                  | _                | _                                | 0.8 V <sub>CC</sub>                                   | _                     | V <sub>CC</sub> + 0.3 | V                     | Pin inputs if<br>Automotive input<br>levels are selected |                                                                                                     |  |

| input<br>voltage                 | V <sub>IHT</sub> | _                                | _                                                     | 2.0                   | _                     | V <sub>CC</sub> + 0.3 | V                                                        | Pin inputs if TTL input levels are selected                                                         |  |

| (At V <sub>CC</sub> = 5 V ± 10%) | V <sub>IHS</sub> | _                                | _                                                     | 0.7 V <sub>CC</sub>   | _                     | V <sub>CC</sub> + 0.3 | V                                                        | P12, P15, P50 inputs if CMOS input levels are selected                                              |  |

|                                  | V <sub>IHI</sub> | _                                | -                                                     | 0.7 V <sub>CC</sub>   | _                     | V <sub>CC</sub> + 0.3 | V                                                        | P44, P45 inputs if CMOS hys-<br>teresis input levels are selected                                   |  |

|                                  | V <sub>IHR</sub> | _                                | _                                                     | 0.8 V <sub>CC</sub>   | _                     | V <sub>CC</sub> + 0.3 | V                                                        | RST input pin (CMOS hystere-<br>sis)                                                                |  |

|                                  | V <sub>IHM</sub> | -                                | _                                                     | V <sub>CC</sub> - 0.3 | _                     | V <sub>CC</sub> + 0.3 | V                                                        | MD input pin                                                                                        |  |

|                                  | V <sub>ILS</sub> | _                                | _                                                     | V <sub>SS</sub> – 0.3 | _                     | 0.2 V <sub>CC</sub>   | V                                                        | Pin inputs if CMOS<br>hysteresis input levels are se-<br>lected (except P12, P15, P44,<br>P45, P50) |  |

| "L" level                        | V <sub>ILA</sub> | _                                | _                                                     | V <sub>SS</sub> - 0.3 | _                     | 0.5 V <sub>CC</sub>   | V                                                        | Pin inputs if<br>Automotive input<br>levels are selected                                            |  |

| input<br>voltage                 | V <sub>ILT</sub> | -                                | _                                                     | V <sub>SS</sub> - 0.3 | _                     | 0.8                   | V                                                        | Pin inputs if TTL input levels are selected                                                         |  |

| (At V <sub>CC</sub> = 5 V ± 10%) | V <sub>ILS</sub> | -                                | _                                                     | V <sub>SS</sub> - 0.3 | _                     | 0.3 V <sub>CC</sub>   | V                                                        | P12, P15, P50 inputs if CMOS input levels are selected                                              |  |

|                                  | V <sub>ILI</sub> | -                                | _                                                     | V <sub>SS</sub> - 0.3 | _                     | 0.3 V <sub>CC</sub>   | V                                                        | P44, P45 inputs if CMOS hys-<br>teresis input levels are selected                                   |  |

|                                  | V <sub>ILR</sub> | -                                | _                                                     | V <sub>SS</sub> - 0.3 | _                     | 0.2 V <sub>CC</sub>   | V                                                        | RST input pin (CMOS hystere-<br>sis)                                                                |  |

|                                  | V <sub>ILM</sub> | -                                | -                                                     | V <sub>SS</sub> - 0.3 | _                     | V <sub>SS</sub> + 0.3 | V                                                        | MD input pin                                                                                        |  |

| Output "H"<br>voltage            | V <sub>OH</sub>  | Normal out-<br>puts              | $V_{CC} = 4.5 V,$<br>$I_{OH} = -4.0 mA$               | V <sub>CC</sub> - 0.5 | _                     | -                     | V                                                        |                                                                                                     |  |

| Output "H"<br>voltage            | V <sub>OHI</sub> | I <sup>2</sup> C current outputs | V <sub>CC</sub> = 4.5 V,<br>I <sub>OH</sub> = -3.0 mA | $V_{CC} - 0.5$        | _                     | _                     | V                                                        |                                                                                                     |  |

# (T\_A = -40°C to +125°C, V\_{CC} = 5.0 V $\pm$ 10%, f\_{CP} $\leq$ 24 MHz, V\_{SS} = AV\_{SS} = 0 V)