Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                         |

| Core Processor             | F <sup>2</sup> MC-16LX                                                           |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 24MHz                                                                            |

| Connectivity               | CANbus, EBI/EMI, I <sup>2</sup> C, LINbus, UART/USART                            |

| Peripherals                | DMA, LVD, POR, WDT                                                               |

| Number of I/O              | 51                                                                               |

| Program Memory Size        | 128KB (128K x 8)                                                                 |

| Program Memory Type        | Mask ROM                                                                         |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 4K x 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 3.5V ~ 5.5V                                                                      |

| Data Converters            | A/D 15x8/10b                                                                     |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 64-LQFP                                                                          |

| Supplier Device Package    | 64-LQFP (12x12)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/mb90352espmc-gs-172e1 |

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Part Number<br>Parameter                      | MB90351E<br>MB90352E                                                                                                                                                                                                                                                                    | MB90351TE<br>MB90352TE                                                                                                    | MB90351ES<br>MB90352ES                                                           | MB90351TES<br>MB90352TES                      | MB90V340E-1<br>01                                                                                                                                                                 | MB90V340E-1<br>02 |  |

|-----------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|-----------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|--|

|                                               |                                                                                                                                                                                                                                                                                         | 4 cha                                                                                                                     | Innels                                                                           |                                               | 8 channels                                                                                                                                                                        |                   |  |

| 16-bit output compare                         |                                                                                                                                                                                                                                                                                         | pt when 16-bit free<br>registers can be u                                                                                 | s output compare re<br>output signal.                                            | egisters.                                     |                                                                                                                                                                                   |                   |  |

| 40 bit in a to a three                        |                                                                                                                                                                                                                                                                                         | 6 cha                                                                                                                     | innels                                                                           |                                               | 8 cha                                                                                                                                                                             | annels            |  |

| 16-bit input capture                          | Retains 16-bit free                                                                                                                                                                                                                                                                     | e-run timer value by                                                                                                      | / (rising edge, fallin                                                           | ig edge, or the both                          | edges), signals ar                                                                                                                                                                | n interrupt.      |  |

| 8/16-bit<br>programmable pulse gen-<br>erator | 8-<br>8-                                                                                                                                                                                                                                                                                | 8-bit reload of bit reload registers bit reload registers                                                                 | /10 channels (8-bit<br>counters × 12<br>for L pulse width×<br>for H pulse width× | 12                                            | 8 channels (16-bit)/<br>16 channels (8-bit)<br>8-bit reload counters × 16<br>8-bit reload registers for<br>L pulse width × 16<br>8-bit reload registers for<br>H pulse width × 16 |                   |  |

|                                               | A pair of 8-bit relo<br>8-bit prescaler + 8<br>Operation clock fro                                                                                                                                                                                                                      | -bit reload counter<br>equency : fsys, fsys                                                                               | e configured as one                                                              | 2 <sup>3</sup> , fsys/2 <sup>4</sup> or 128 μ |                                                                                                                                                                                   |                   |  |

|                                               |                                                                                                                                                                                                                                                                                         | 1 cha                                                                                                                     | 3 cha                                                                            | annels                                        |                                                                                                                                                                                   |                   |  |

| CAN interface                                 | Automatic re-trans<br>Automatic transmi<br>16 prioritized mes<br>Supports multiple<br>Flexible configurat                                                                                                                                                                               | smission in case of<br>ssion responding t<br>sage buffers for da<br>messages.<br>tion of acceptance<br>/Full bit mask/Two | o Remote Frame<br>ta and ID<br>filtering :                                       | art B.                                        |                                                                                                                                                                                   |                   |  |

|                                               |                                                                                                                                                                                                                                                                                         | 8 cha                                                                                                                     | innels                                                                           |                                               | 16 ch                                                                                                                                                                             | annels            |  |

| External interrupt                            | Can be used rising extended intelliger                                                                                                                                                                                                                                                  | g edge, falling edge<br>nt I/O services (El <sup>2</sup>                                                                  | e, starting up by "H<br>OS) and DMA.                                             | "/"L" level input, ext                        | ternal interrupt,                                                                                                                                                                 |                   |  |

| D/A converter                                 |                                                                                                                                                                                                                                                                                         | -                                                                                                                         | _                                                                                |                                               | 2 cha                                                                                                                                                                             | annels            |  |

| I/O ports                                     | Virtually all external pins can be used as general purpose I/O port.<br>All push-pull outputs<br>Bit-wise settable as input/output or peripheral signal<br>Settable as CMOS schmitt trigger/ automotive inputs<br>TTL input level settable for external bus (only for external bus pin) |                                                                                                                           |                                                                                  |                                               |                                                                                                                                                                                   |                   |  |

| Flash memory                                  |                                                                                                                                                                                                                                                                                         |                                                                                                                           | -                                                                                | _                                             |                                                                                                                                                                                   |                   |  |

| Corresponding<br>evaluation name              | MB90V3                                                                                                                                                                                                                                                                                  | 40E-102                                                                                                                   | MB90V3                                                                           | 340E-101                                      | -                                                                                                                                                                                 | _                 |  |

\*: It is setting of Jumper switch (TOOL VCC) when Emulator (MB2147-01) is used. Please refer to the Emulator hardware manual about details.

| Part Number<br>Parameter            | MB90356E<br>MB90357E                                                                                                                                                                                                                                                                                                                                                                                         | MB90356TE<br>MB90357TE                                   | MB90356ES<br>MB90357ES                                                           | MB90356TES<br>MB90357TES              | MB90V340E-1<br>03                                                                                                                                                           | MB90V340E-1<br>04 |  |

|-------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|----------------------------------------------------------------------------------|---------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|--|

| 16 bit output                       |                                                                                                                                                                                                                                                                                                                                                                                                              | 4 cha                                                    | annels                                                                           |                                       | 8 cha                                                                                                                                                                       | annels            |  |

| 16-bit output<br>compare            |                                                                                                                                                                                                                                                                                                                                                                                                              |                                                          | -run Timer matches<br>sed to generate an                                         | s with output compa<br>output signal. | are registers.                                                                                                                                                              |                   |  |

|                                     |                                                                                                                                                                                                                                                                                                                                                                                                              | 6 cha                                                    | annels                                                                           |                                       | 8 cha                                                                                                                                                                       | annels            |  |

| 16-bit input capture                | Retains 16-bit free signals an interrup                                                                                                                                                                                                                                                                                                                                                                      |                                                          | y (rising edge, fallir                                                           | ng edge or rising &                   | falling edge),                                                                                                                                                              |                   |  |

| 8/16-bit<br>programmable pulse gen- | 8-t                                                                                                                                                                                                                                                                                                                                                                                                          | 8-bit reload                                             | /10 channels (8-bit<br>counters×12<br>for L pulse width ×<br>for H pulse width × | 12                                    | 8 channels (16-bit)/<br>16 channels (8-bit)<br>8-bit reload counters×16<br>8-bit reload registers for<br>L pulse width×16<br>8-bit reload registers for<br>H pulse width×16 |                   |  |

| erator                              | Supports 8-bit and 16-bit operation modes.<br>A pair of 8-bit reload counters can be configured as one 16-bit reload counter or as<br>8-bit prescaler + 8-bit reload counter.<br>Operation clock frequency : fsys, fsys/2 <sup>1</sup> , fsys/2 <sup>2</sup> , fsys/2 <sup>3</sup> , fsys/2 <sup>4</sup> or 128 $\mu$ s@fosc = 4 MHz<br>(fsys = Machine clock frequency, fosc = Oscillation clock frequency) |                                                          |                                                                                  |                                       |                                                                                                                                                                             |                   |  |

|                                     |                                                                                                                                                                                                                                                                                                                                                                                                              | 1 ch                                                     | 3 channels                                                                       |                                       |                                                                                                                                                                             |                   |  |

| CAN interface                       | Conforms to CAN Specification Version 2.0 Part A and B.<br>Automatic re-transmission in case of error<br>Automatic transmission responding to Remote Frame<br>Prioritized 16 message buffers for data and ID<br>Supports multiple messages.<br>Flexible configuration of acceptance filtering :<br>Full bit compare/Full bit mask/Two partial bit masks<br>Supports up to 1 Mbps.                            |                                                          |                                                                                  |                                       |                                                                                                                                                                             |                   |  |

|                                     |                                                                                                                                                                                                                                                                                                                                                                                                              | 8 cha                                                    | annels                                                                           |                                       | 16 ch                                                                                                                                                                       | annels            |  |

| External interrupt                  |                                                                                                                                                                                                                                                                                                                                                                                                              | g edge, falling edge<br>nt I/O services (El <sup>2</sup> |                                                                                  | L level input, exterr                 | nal interrupt,                                                                                                                                                              |                   |  |

| D/A converter                       |                                                                                                                                                                                                                                                                                                                                                                                                              | -                                                        | _                                                                                |                                       | 2 cha                                                                                                                                                                       | annels            |  |

| I/O ports                           | Virtually all external pins can be used as general purpose I/O port.<br>All push-pull outputs<br>Bit-wise settable as input/output or peripheral module signal<br>Settable as CMOS schmitt trigger/ automotive inputs<br>TTL input level settable for external bus (only for external bus pin)                                                                                                               |                                                          |                                                                                  |                                       |                                                                                                                                                                             |                   |  |

| Flash memory                        |                                                                                                                                                                                                                                                                                                                                                                                                              |                                                          | -                                                                                | _                                     |                                                                                                                                                                             |                   |  |

| Corresponding EVA name              | MB90V3                                                                                                                                                                                                                                                                                                                                                                                                       | 40E-104                                                  | MB90V3                                                                           | 340E-103                              | -                                                                                                                                                                           | _                 |  |

|                                     |                                                                                                                                                                                                                                                                                                                                                                                                              |                                                          |                                                                                  |                                       |                                                                                                                                                                             |                   |  |

\*: It is setting of Jumper switch (TOOL VCC) when Emulator (MB2147-01) is used. Please refer to the Emulator hardware manual about details.

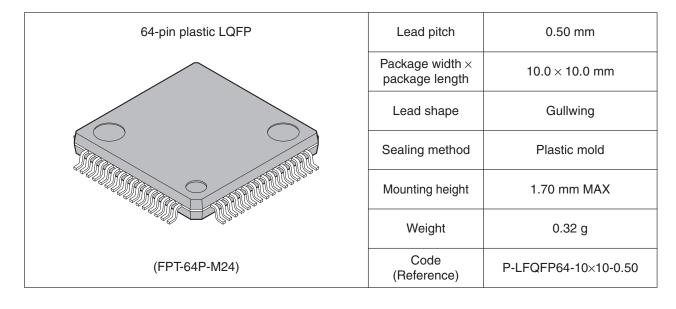

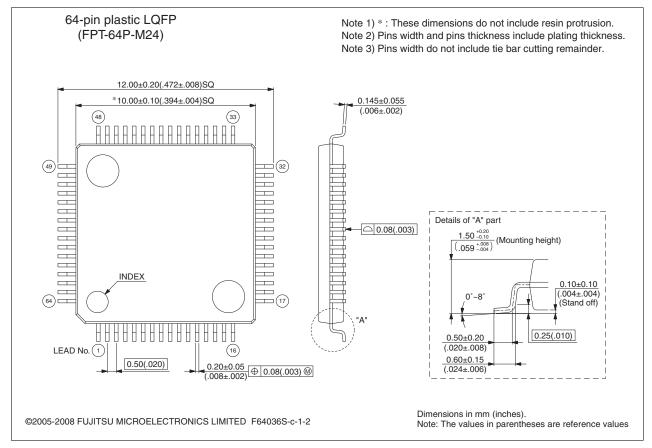

# 3. Packages and Product Correspondence

| Package                                   | MB90V340E-101<br>MB90V340E-102<br>MB90V340E-103<br>MB90V340E-104 | MB90351E (S), MB90351TE (S)<br>MB90F351E (S), MB90F351TE (S)<br>MB90352E (S), MB90352TE (S)<br>MB90F352E (S), MB90F352TE (S)<br>MB90356E (S), MB90356TE (S)<br>MB90F356E (S), MB90F356TE (S)<br>MB90357E (S), MB905357TE (S) |

|-------------------------------------------|------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PGA-299C-A01                              | $\bigcirc$                                                       | ×                                                                                                                                                                                                                            |

| FPT-64P-M23<br>(12.0 mm, 0.65 mm pitch)   | ×                                                                | 0                                                                                                                                                                                                                            |

| FPT-64P-M24<br>(10.0 mm ], 0.50 mm pitch) | ×                                                                | 0                                                                                                                                                                                                                            |

$\bigcirc$  : Yes,  $\times$  : No

Note : Refer to "Package Dimensions" for detail of each package.

| 24 to 31     P00 to P07     Finis function is enabled in single-chip mode.       24 to 31     AD00 to AD07     Finis function is enabled in single-chip mode.       1NT8 to INT15     Input/output pins of external address data bus lower 8 bits. This function is enabled when the external bus is enabled.       32     AD008     Fernal interrupt request input pins for INT8 to INT15       33     AD08     General purpose I/O port. The register can be set to select whether to use a pull-up resistor. This function is enabled in single-chip mode.       33     AD09     General purpose I/O port. The register can be set to select whether to use a pull-up resistor. This function is enabled in single-chip mode.       33     AD09     General purpose I/O port. The register can be set to select whether to use a pull-up resistor.       34     AD09     General purpose I/O port. The register can be set to select whether to use a pull-up resistor.       34     AD10     N     Input/output pin for external bus address data bus bit 9. This function is enabled when external bus is enabled.       35     AD10     N     General purpose I/O port. The register can be set to select whether to use a pull-up resistor. This function is enabled in single-chip mode.       35     AD11     Fetternal interrupt request input pin for INT11       36     AD11     Seretil data output pin for                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Pin No.  | Pin name      | I/O<br>Circuit<br>type* | Function                                                |  |  |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|---------------|-------------------------|---------------------------------------------------------|--|--|--|

| AD00 to AD07     external bus is enabled.       INT8 to INT15     External interrupt request input pins for INT8 to INT15       32     AD08     General purpose I/0 port. The register can be set to select whether to use a pull-up resistor.<br>This function is enabled in single-chip mode.       33     AD09     Input/output pin for relead timer1       33     AD09     General purpose I/0 port. The register can be set to select whether to use a pull-up resistor.<br>This function is enabled in single-chip mode.       33     AD09     General purpose I/0 port. The register can be set to select whether to use a pull-up resistor.<br>This function is enabled in single-chip mode.       34     AD09     General purpose I/0 port. The register can be set to select whether to use a pull-up resistor.<br>This function is enabled in single-chip mode.       34     AD10     N     General purpose I/0 port. The register can be set to select whether to use a pull-up resistor.<br>This function is enabled in single-chip mode.       35     AD10     N     Input/output pin for LART3       35     AD11     General purpose I/0 port. The register can be set to select whether to use a pull-up resistor.<br>This function is enabled in single-chip mode.       36     AD11     General purpose I/0 port. The register can be set to select whether to use a pull-up resistor.<br>This function is enabled when external bus is datress data bus bit 11.<br>This function is enabled when e                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |          | P00 to P07    |                         |                                                         |  |  |  |

| 32     P10     General purpose I/O port. The register can be set to select whether to use a pull-up resistor.<br>This function is enabled when external bus address data bus bit 8.<br>This function is enabled when external bus is enabled.       33     AD09     General purpose I/O port. The register can be set to select whether to use a pull-up resistor.<br>This function is enabled when external bus is enabled.       33     AD09     General purpose I/O port. The register can be set to select whether to use a<br>pull-up resistor. This function is enabled in single-chip mode.       34     P11     General purpose I/O port. The register can be set to select whether to use a<br>pull-up resistor. This function is enabled in single-chip mode.       34     AD09     General purpose I/O port. The register can be set to select whether to use a pull-up resistor.<br>This function is enabled use address data bus bit 9. This function is<br>enabled when external bus address data bus bit 10. This function is enabled when exter-<br>nal bus is enabled.       34     AD10     N     Input/output pin for external bus address data bus bit 10. This function is enabled when exter-<br>nal bus is enabled.       35     AD11     Ceneral purpose I/O port. The register can be set to select whether to use a pull-up resistor.<br>This function is enabled in single-chip mode.       36     AD11     General purpose I/O port. The register can be set to select whether to use a pull-up resistor.<br>This function is enabled when external bus address data bus bit 11.<br>This function is enabled when external bus address data bus bit                                                                                                                                                                                                                                                                                                                                                                                                    | 24 to 31 | AD00 to AD07  | G                       |                                                         |  |  |  |

| AD08     Fits     This function is enabled in single-chip mode.       32     AD08     G     Input/output pin for external bus address data bus bit 8.<br>This function is enabled when external bus is enabled.       33     AD09     G     General purpose I/O port. The register can be set to select whether to use a pull-up resistor. This function is enabled when external bus is enabled.       33     AD09     G     Input/output pin for external bus address data bus bit 9.<br>Input/output pin for external bus is enabled.       34     AD10     Input/output pin for external bus address data bus bit 9. This function is enabled when external bus is enabled.       34     AD10     N     General purpose I/O port. The register can be set to select whether to use a pull-up resistor. This function is enabled in single-chip mode.       35     AD10     N     General purpose I/O port. The register can be set to select whether to use a pull-up resistor. This function is enabled.       35     AD11     Research purpose I/O port. The register can be set to select whether to use a pull-up resistor. This function is enabled in single-chip mode.       36     AD11     G     Input/output pin for external bus address data bus bit 11.<br>This function is enabled when external bus is enabled.       36     AD11     G     Input/output pin for UART3       37     AD12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |          | INT8 to INT15 |                         | External interrupt request input pins for INT8 to INT15 |  |  |  |

| AD06     This function is enabled when external bus is enabled.       33     F11     Event input pin for reload timer1       33     AD09     G     General purpose I/O port. The register can be set to select whether to use a pull-up resistor. This function is enabled in single-chip mode.       34     AD09     F12     Input/output pin for reload timer1       34     P12     General purpose I/O port. The register can be set to select whether to use a pull-up resistor. This function is enabled.       34     AD10     N     General purpose I/O port. The register can be set to select whether to use a pull-up resistor. This function is enabled in single-chip mode.       34     AD10     N     Serial data input pin for UART3       35     AD11     General purpose I/O port. The register can be set to select whether to use a pull-up resistor. This function is enabled in single-chip mode.       35     AD11     General purpose I/O port. The register can be set to select whether to use a pull-up resistor. This function is enabled in single-chip mode.       36     AD11     General purpose I/O port. The register can be set to select whether to use a pull-up resistor. This function is enabled in single-chip mode.       36     AD11     General purpose I/O port. The register can be set to select whether to use a pull-up resistor. This function is enabled in single-chip mode. <tr< td=""><td></td><td>P10</td><td></td><td></td></tr<>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |          | P10           |                         |                                                         |  |  |  |

| P11General purpose I/O port. The register can be set to select whether to use a<br>pull-up resistor. This function is enabled in single-chip mode.33AD09GInput/output pin for external bus address data bus bit 9. This function is<br>enabled when external bus is enabled.34AD10NGeneral purpose I/O port. The register can be set to select whether to use a pull-up resistor.<br>This function is enabled in single-chip mode.34AD10NGeneral purpose I/O port. The register can be set to select whether to use a pull-up resistor.<br>This function is enabled in single-chip mode.34AD10NInput/output pin for external bus address data bus bit 10. This function is enabled when external<br>hal bus is enabled.35AD11NExternal interrupt request input pin for INT1135AD11GInput/output pin for caternal bus address data bus bit 11.<br>This function is enabled in single-chip mode.36AD11GInput/output pin for UART336AD12GInput/output pin for UART337P14General purpose I/O port. The register can be set to select whether to use a pull-up resistor.<br>This function is enabled in single-chip mode.37AD12GInput/output pin for UART337P15NGeneral purpose I/O port. The register can be set to select whether to use a pull-up resistor.<br>This function is enabled in single-chip mode.38P16GGeneral purpose I/O port. The register can be set to select whether to use a pull-up resistor.<br>This function is enabled in single-chip mode.38P16GGeneral purpose I/O por                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 32       | AD08          | G                       |                                                         |  |  |  |

| 33AD09<br>AD09G<br>Input/output pin for external bus address data bus bit 9. This function is<br>enabled when external bus is enabled.<br>Output pin for relead timer134AD10<br>SIN3NGeneral purpose I/O port. The register can be set to select whether to use a pull-up resistor.<br>This function is enabled in single-chip mode.34AD10<br>SIN3NInput/output pin for external bus address data bus bit 10. This function is enabled when external<br>hal bus is enabled.34AD10<br>SIN3NInput/output pin for external bus address data bus bit 10. This function is enabled when external<br>hal bus is enabled.35AD11<br>SOT3P13<br>P13General purpose I/O port. The register can be set to select whether to use a pull-up resistor.<br>This function is enabled in single-chip mode.36AD11<br>SOT3General purpose I/O port. The register can be set to select whether to use a pull-up resistor.<br>This function is enabled in single-chip mode.36AD11<br>SOT3General purpose I/O port. The register can be set to select whether to use a pull-up resistor.<br>This function is enabled when external bus is enabled.36AD12<br>SOT3General purpose I/O port. The register can be set to select whether to use a pull-up resistor.<br>This function is enabled in single-chip mode.37P14<br>AD12General purpose I/O port. The register can be set to select whether to use a pull-up resistor.<br>This function is enabled in single-chip mode.37P15<br>AD13NInput/output pin for UART3<br>Clock input/output pin for UART3<br>This function is enabled when external bus is enabled.38P16<br>AD13General purpose I/O port. The register                                                                                                                                                                                                                                                                                                                                                                                                                                     |          | TIN1          |                         | Event input pin for reload timer1                       |  |  |  |

| AD09   enabled when external bus is enabled.     TOT1   Output pin for reload timer1     0utput pin for reload timer1   General purpose I/O port. The register can be set to select whether to use a pull-up resistor. This function is enabled in single-chip mode.     34   AD10   N     35   AD10   N     36   P13   Serial data input pin for UART3     37   P13   General purpose I/O port. The register can be set to select whether to use a pull-up resistor. This function is enabled.     36   AD11   General purpose I/O port. The register can be set to select whether to use a pull-up resistor. This function is enabled.     36   AD11   General purpose I/O port. The register can be set to select whether to use a pull-up resistor. This function is enabled in single-chip mode.     36   AD11   General purpose I/O port. The register can be set to select whether to use a pull-up resistor. This function is enabled in single-chip mode.     37   P14   General purpose I/O port. The register can be set to select whether to use a pull-up resistor. This function is enabled in single-chip mode.     37   P15   Referent purpose I/O port. The register can be set to select whether to use a pull-up resistor. This function is enabled in single-chip mode.     38   P16   General purpose I/O port. The register can be set to select whether to use a pull-up resistor. Th                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |          | P11           |                         |                                                         |  |  |  |

| 34   P12   General purpose I/O port. The register can be set to select whether to use a pull-up resistor. This function is enabled in single-chip mode.     34   AD10   N   Input/output pin for external bus address data bus bit 10. This function is enabled when external bus is enabled.     31   SIN3   Serial data input pin for UART3     35   AD11   General purpose I/O port. The register can be set to select whether to use a pull-up resistor. This function is enabled in single-chip mode.     35   AD11   General purpose I/O port. The register can be set to select whether to use a pull-up resistor. This function is enabled in single-chip mode.     36   AD11   General purpose I/O port. The register can be set to select whether to use a pull-up resistor. This function is enabled when external bus is enabled.     36   SOT3   General purpose I/O port. The register can be set to select whether to use a pull-up resistor. This function is enabled in single-chip mode.     36   AD12   General purpose I/O port. The register can be set to select whether to use a pull-up resistor. This function is enabled in single-chip mode.     37   P14   General purpose I/O port. The register can be set to select whether to use a pull-up resistor. This function is enabled when external bus is enabled.     37   P15   General purpose I/O port. The register can be set to select whether to use a pull-up resistor. This function is enabled in single-chip mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 33       | AD09          | G                       |                                                         |  |  |  |

| 34   AD10   N   This function is enabled in single-chip mode.     34   AD10   N   Input/output pin for external bus address data bus bit 10. This function is enabled when external bus is enabled.     31   SIN3   Serial data input pin for UART3   External interrupt request input pin for INT11     35   AD11   General purpose I/O port. The register can be set to select whether to use a pull-up resistor. This function is enabled in single-chip mode.     35   AD11   General purpose I/O port. The register can be set to select whether to use a pull-up resistor. This function is enabled in single-chip mode.     36   AD11   General purpose I/O port. The register can be set to select whether to use a pull-up resistor. This function is enabled in single-chip mode.     36   AD12   General purpose I/O port. The register can be set to select whether to use a pull-up resistor. This function is enabled in single-chip mode.     36   AD12   General purpose I/O port. The register can be set to select whether to use a pull-up resistor. This function is enabled in single-chip mode.     37   P14   General purpose I/O port. The register can be set to select whether to use a pull-up resistor. This function is enabled in single-chip mode.     37   P15   N   General purpose I/O port. The register can be set to select whether to use a pull-up resistor. This function is enabled when external bus is enabled.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |          | TOT1          |                         | Output pin for reload timer1                            |  |  |  |

| 34AD10N<br>nal bus is enabled.SIN3Sin3Serial data input pin for UART3INT11RExternal interrupt request input pin for INT1135AD11GAD11GInput/output pin for external bus address data bus bit 11.<br>This function is enabled when external bus is enabled.36AD11G36AD12General purpose I/O port. The register can be set to select whether to use a pull-up resistor.<br>This function is enabled when external bus is enabled.36AD12General purpose I/O port. The register can be set to select whether to use a pull-up resistor.<br>This function is enabled in single-chip mode.36AD12General purpose I/O port. The register can be set to select whether to use a pull-up resistor.<br>This function is enabled in single-chip mode.36AD12General purpose I/O port. The register can be set to select whether to use a pull-up resistor.<br>This function is enabled when external bus is enabled.37P14General purpose I/O port. The register can be set to select whether to use a pull-up resistor.<br>This function is enabled when external bus is enabled.37P15N<br>Input/output pin for external bus address data bus bit 13.<br>This function is enabled in single-chip mode.38P16General purpose I/O port. The register can be set to select whether to use a pull-up resistor.<br>This function is enabled when external bus is enabled.38P16General purpose I/O port. The register can be set to select whether to use a pull-up resistor.<br>This function is enabled when external bus is enabled.38P16General purpose I/O port. The register can                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |          | P12           |                         |                                                         |  |  |  |

| INT11R     External interrupt request input pin for INT11       35     P13     General purpose I/O port. The register can be set to select whether to use a pull-up resistor. This function is enabled in single-chip mode.       35     AD11     General purpose I/O port. The register can be set to select whether to use a pull-up resistor. This function is enabled when external bus address data bus bit 11. This function is enabled when external bus is enabled.       36     AD12     General purpose I/O port. The register can be set to select whether to use a pull-up resistor. This function is enabled in single-chip mode.       36     AD12     General purpose I/O port. The register can be set to select whether to use a pull-up resistor. This function is enabled in single-chip mode.       36     AD12     General purpose I/O port. The register can be set to select whether to use a pull-up resistor. This function is enabled when external bus address data bus bit 12. This function is enabled when external bus is enabled.       37     P15     General purpose I/O port. The register can be set to select whether to use a pull-up resistor. This function is enabled in single-chip mode.       38     P16     General purpose I/O port. The register can be set to select whether to use a pull-up resistor. This function is enabled when external bus address data bus bit 13. This function is enabled when external bus address data bus bit 13. This function is enabled when external bus is enabled.       38     P16     General purpose I/O port. The register can be                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 34       | 54            |                         |                                                         |  |  |  |

| 35   P13   General purpose I/O port. The register can be set to select whether to use a pull-up resistor. This function is enabled in single-chip mode.     35   AD11   General purpose I/O port. The register can be set to select whether to use a pull-up resistor. This function is enabled when external bus is enabled.     36   AD12   Fital data output pin for UART3     36   AD12   General purpose I/O port. The register can be set to select whether to use a pull-up resistor. This function is enabled in single-chip mode.     36   AD12   General purpose I/O port. The register can be set to select whether to use a pull-up resistor. This function is enabled in single-chip mode.     36   AD12   General purpose I/O port. The register can be set to select whether to use a pull-up resistor. This function is enabled in single-chip mode.     37   P14   General purpose I/O port. The register can be set to select whether to use a pull-up resistor. This function is enabled when external bus address data bus bit 12. This function is enabled when external bus is enabled.     37   P15   Reneral purpose I/O port. The register can be set to select whether to use a pull-up resistor. This function is enabled in single-chip mode.     38   P16   General purpose I/O port. The register can be set to select whether to use a pull-up resistor. This function is enabled when external bus is enabled.     38   P16   General purpose I/O port. The register can be set to select whether to use a pu                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |          |               |                         | Serial data input pin for UART3                         |  |  |  |

| 35AD11<br>AD11GThis function is enabled in single-chip mode.35AD11GInput/output pin for external bus address data bus bit 11.<br>This function is enabled when external bus is enabled.36P14General purpose I/O port. The register can be set to select whether to use a pull-up resistor.<br>This function is enabled in single-chip mode.36AD12GGeneral purpose I/O port. The register can be set to select whether to use a pull-up resistor.<br>This function is enabled when external bus address data bus bit 12.<br>This function is enabled when external bus address data bus bit 12.<br>This function is enabled when external bus is enabled.36AD12GGeneral purpose I/O port. The register can be set to select whether to use a pull-up resistor.<br>This function is enabled when external bus is enabled.37P15NGeneral purpose I/O port. The register can be set to select whether to use a pull-up resistor.<br>This function is enabled when external bus address data bus bit 13.<br>This function is enabled in single-chip mode.37P16General purpose I/O port. The register can be set to select whether to use a pull-up resistor.<br>This function is enabled when external bus address data bus bit 13.<br>This function is enabled when external bus is enabled.38P16General purpose I/O port. The register can be set to select whether to use a pull-up resistor.<br>This function is enabled when external bus is enabled.38P16General purpose I/O port. The register can be set to select whether to use a pull-up resistor.<br>This function is enabled in single-chip mode.38P16Input/output pin for external bus address data bus bit 14. <td></td> <td>INT11R</td> <td></td> <td>External interrupt request input pin for INT11</td>                                                                                                                                                                                                                                                                                                                |          | INT11R        |                         | External interrupt request input pin for INT11          |  |  |  |

| AD11This function is enabled when external bus is enabled.SOT3Serial data output pin for UART3AD12P14General purpose I/O port. The register can be set to select whether to use a pull-up resistor.<br>This function is enabled in single-chip mode.36AD12GInput/output pin for external bus address data bus bit 12.<br>This function is enabled when external bus is enabled.36Clock input/output pin for UART337P15NAD13General purpose I/O port. The register can be set to select whether to use a pull-up resistor.<br>This function is enabled in single-chip mode.38P16General purpose I/O port. The register can be set to select whether to use a pull-up resistor.<br>This function is enabled in single-chip mode.38P16General purpose I/O port. The register can be set to select whether to use a pull-up resistor.<br>This function is enabled when external bus is enabled.38P16General purpose I/O port. The register can be set to select whether to use a pull-up resistor.<br>This function is enabled when external bus is enabled.38P16General purpose I/O port. The register can be set to select whether to use a pull-up resistor.<br>This function is enabled in single-chip mode.<br>Input/output pin for external bus address data bus bit 13.<br>This function is enabled in single-chip mode.38P16General purpose I/O port. The register can be set to select whether to use a pull-up resistor.<br>This function is enabled in single-chip mode.38Input/output pin for external bus address data bus bit 14.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |          | P13           |                         |                                                         |  |  |  |

| 36   P14   General purpose I/O port. The register can be set to select whether to use a pull-up resistor. This function is enabled in single-chip mode.     36   AD12   General purpose I/O port. The register can be set to select whether to use a pull-up resistor. This function is enabled in single-chip mode.     36   AD12   General purpose I/O port. The register can be set to select whether to use a pull-up resistor. This function is enabled when external bus is enabled.     37   P15   Clock input/output pin for UART3     37   P15   N     AD13   N   General purpose I/O port. The register can be set to select whether to use a pull-up resistor. This function is enabled in single-chip mode.     38   P16   General purpose I/O port. The register can be set to select whether to use a pull-up resistor. This function is enabled when external bus address data bus bit 13. This function is enabled when external bus is enabled.     38   P16   General purpose I/O port. The register can be set to select whether to use a pull-up resistor. This function is enabled in single-chip mode.     38   P16   General purpose I/O port. The register can be set to select whether to use a pull-up resistor. This function is enabled in single-chip mode.     38   P16   Input/output pin for external bus address data bus bit 14.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 35       | AD11 C        |                         |                                                         |  |  |  |

| 36   Image: Pi4 definition of the sector o |          | SOT3          |                         | Serial data output pin for UART3                        |  |  |  |

| AD12   This function is enabled when external bus is enabled.     SCK3   Clock input/output pin for UART3     37   P15   AD13     AD13   N   General purpose I/O port. The register can be set to select whether to use a pull-up resistor.<br>This function is enabled in single-chip mode.     38   P16   General purpose I/O port. The register can be set to select whether to use a pull-up resistor.<br>This function is enabled when external bus address data bus bit 13.<br>This function is enabled when external bus is enabled.     38   P16   General purpose I/O port. The register can be set to select whether to use a pull-up resistor.<br>This function is enabled in single-chip mode.     38   P16   General purpose I/O port. The register can be set to select whether to use a pull-up resistor.<br>This function is enabled in single-chip mode.     38   P16   Input/output pin for external bus address data bus bit 14.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |          | P14           |                         |                                                         |  |  |  |

| 37   P15   N   General purpose I/O port. The register can be set to select whether to use a pull-up resistor. This function is enabled in single-chip mode.     37   AD13   Input/output pin for external bus address data bus bit 13. This function is enabled when external bus is enabled.     38   P16   General purpose I/O port. The register can be set to select whether to use a pull-up resistor. This function is enabled when external bus is enabled.     38   P16   General purpose I/O port. The register can be set to select whether to use a pull-up resistor. This function is enabled in single-chip mode.     38   P16   General purpose I/O port. The register can be set to select whether to use a pull-up resistor. This function is enabled in single-chip mode.     38   Input/output pin for external bus address data bus bit 14.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 36       | AD12          | G                       |                                                         |  |  |  |

| 37   P15   N   This function is enabled in single-chip mode.     37   AD13   Input/output pin for external bus address data bus bit 13.<br>This function is enabled when external bus is enabled.     38   P16   General purpose I/O port. The register can be set to select whether to use a pull-up resistor.<br>This function is enabled in single-chip mode.     38   AD14   General purpose I/O port. The register can be set to select whether to use a pull-up resistor.<br>This function is enabled in single-chip mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |          | SCK3          |                         | Clock input/output pin for UART3                        |  |  |  |

| AD13   Input/output pin for external bus address data bus bit 13.<br>This function is enabled when external bus is enabled.     38   P16   General purpose I/O port. The register can be set to select whether to use a pull-up resistor.<br>This function is enabled in single-chip mode.     38   AD14   General purpose I/O port. The register can be set to select whether to use a pull-up resistor.<br>This function is enabled in single-chip mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 27       | P15           | N                       |                                                         |  |  |  |

| 38 G This function is enabled in single-chip mode.<br>Input/output pin for external bus address data bus bit 14.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 37       |               |                         |                                                         |  |  |  |