Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                         |

| Core Processor             | F <sup>2</sup> MC-16LX                                                           |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 24MHz                                                                            |

| Connectivity               | CANbus, EBI/EMI, I <sup>2</sup> C, LINbus, UART/USART                            |

| Peripherals                | DMA, LVD, POR, WDT                                                               |

| Number of I/O              | 51                                                                               |

| Program Memory Size        | 128KB (128K x 8)                                                                 |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 4K x 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 3.5V ~ 5.5V                                                                      |

| Data Converters            | A/D 15x8/10b                                                                     |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 64-LQFP                                                                          |

| Supplier Device Package    | 64-LQFP (12x12)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/mb90f352espmc1-g-spe1 |

# 1. Product Lineup1 (Without Clock supervisor function)

■ Flash memory products

| Part Number                                  | MB90F351E                                                                                                                                                                                                                                                                                                                          | MB90F351TE                                                                                                                                                                                              | MB90F351ES                       | MB90F351TES        |  |  |  |  |

|----------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|--------------------|--|--|--|--|

|                                              | MB90F352E                                                                                                                                                                                                                                                                                                                          | MB90F352TE                                                                                                                                                                                              | MB90F352ES                       | MB90F351TES        |  |  |  |  |

| Parameter                                    |                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                         |                                  |                    |  |  |  |  |

| Туре                                         |                                                                                                                                                                                                                                                                                                                                    | Flash memo                                                                                                                                                                                              |                                  |                    |  |  |  |  |

| CPU                                          |                                                                                                                                                                                                                                                                                                                                    | F <sup>2</sup> MC-16                                                                                                                                                                                    | SLX CPU                          |                    |  |  |  |  |

| System clock                                 | Minimum instruction execut                                                                                                                                                                                                                                                                                                         | PLL clock multiplication circuit ( $\times$ 1, $\times$ 2, $\times$ 3, $\times$ 4, $\times$ 6, 1/2 when PLL stops)  Minimum instruction execution time: 42 ns (oscillation clock 4 MHz, PLL $\times$ 6) |                                  |                    |  |  |  |  |

| ROM                                          |                                                                                                                                                                                                                                                                                                                                    | MB90F351E(S), MB90F352<br>Flash memory (Erase/write a<br>2TE(S)                                                                                                                                         |                                  | at the same time): |  |  |  |  |

| RAM                                          |                                                                                                                                                                                                                                                                                                                                    | 4 Kb                                                                                                                                                                                                    | ytes                             |                    |  |  |  |  |

| Emulator-specific power supply*              |                                                                                                                                                                                                                                                                                                                                    | -                                                                                                                                                                                                       | -                                |                    |  |  |  |  |

| Sub clock pin<br>(X0A, X1A)<br>(Max 100 kHz) | Ye                                                                                                                                                                                                                                                                                                                                 | es                                                                                                                                                                                                      | ı                                | No                 |  |  |  |  |

| Clock supervisor                             |                                                                                                                                                                                                                                                                                                                                    | N                                                                                                                                                                                                       | 0                                |                    |  |  |  |  |

| Low voltage/CPU operation detection reset    | No                                                                                                                                                                                                                                                                                                                                 | Yes                                                                                                                                                                                                     | No                               | Yes                |  |  |  |  |

| Operating voltage                            |                                                                                                                                                                                                                                                                                                                                    | perating (not using A/D conv<br>converter/Flash programmi<br>ernal bus                                                                                                                                  |                                  |                    |  |  |  |  |

| Operating temperature                        |                                                                                                                                                                                                                                                                                                                                    | –40°C to                                                                                                                                                                                                | +125°C                           |                    |  |  |  |  |

| Package                                      |                                                                                                                                                                                                                                                                                                                                    | LQFI                                                                                                                                                                                                    | P-64                             |                    |  |  |  |  |

|                                              |                                                                                                                                                                                                                                                                                                                                    | 2 cha                                                                                                                                                                                                   | nnels                            |                    |  |  |  |  |

| LIN-UART                                     | Special synchronous option                                                                                                                                                                                                                                                                                                         | ttings using a dedicated bau<br>is for adapting to different sy<br>ther as master or slave LIN o                                                                                                        | nchronous serial protocols       | ner)               |  |  |  |  |

| I <sup>2</sup> C (400 kbps)                  |                                                                                                                                                                                                                                                                                                                                    | 1 cha                                                                                                                                                                                                   | annel                            |                    |  |  |  |  |

|                                              |                                                                                                                                                                                                                                                                                                                                    | 15 cha                                                                                                                                                                                                  | annels                           |                    |  |  |  |  |

| A/D converter                                | 10-bit or 8-bit resolution<br>Conversion time : Min 3 μs                                                                                                                                                                                                                                                                           | includes sample time (per c                                                                                                                                                                             | one channel)                     |                    |  |  |  |  |

| 16-bit reload timer<br>(2 channels)          | Operation clock frequency :<br>Supports External Event Co                                                                                                                                                                                                                                                                          | fsys/ $2^1$ , fsys/ $2^3$ , fsys/ $2^5$ (fsyout function.                                                                                                                                               | ys = Machine clock frequen       | icy)               |  |  |  |  |

| 40 hit Farance "                             | Free-run Timer 0 (clock inputere-run Timer 1 (clock inputere-run Timer 1)                                                                                                                                                                                                                                                          | ut FRCK0) corresponds to I0<br>ut FRCK1) corresponds to I0                                                                                                                                              | CU0/1.<br>CU4/5/6/7, OCU4/5/6/7. |                    |  |  |  |  |

| 16-bit Free-run timer<br>(2 channels)        | Signals an interrupt when overflowing. Supports Timer Clear when it matches Output Compare (ch.0, ch.4). Operation clock frequency: fsys, fsys/2 <sup>1</sup> , fsys/2 <sup>2</sup> , fsys/2 <sup>3</sup> , fsys/2 <sup>4</sup> , fsys/2 <sup>5</sup> , fsys/2 <sup>6</sup> , fsys/2 <sup>7</sup> (fsys = Machine clock frequency) |                                                                                                                                                                                                         |                                  |                    |  |  |  |  |

| 16 hit output                                |                                                                                                                                                                                                                                                                                                                                    | 4 cha                                                                                                                                                                                                   | nnels                            |                    |  |  |  |  |

| 16-bit output compare                        | Signals an interrupt when 16-bit free-run Timer matches with output compare registers.  A pair of compare registers can be used to generate an output signal.                                                                                                                                                                      |                                                                                                                                                                                                         |                                  |                    |  |  |  |  |

■ MASK ROM products/Evaluation products

| Part Number Parameter                        | MB90351E<br>MB90352E                                                                                                                                                | MB90351TE<br>MB90352TE                                                                                                                                                                                                                                                                                                             | MB90351ES<br>MB90352ES                        | MB90351TES<br>MB90352TES                             | MB90V340E-1<br>01                                                                                               | MB90V340E-1 |

|----------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|-------------|

| Туре                                         |                                                                                                                                                                     | MASK RO                                                                                                                                                                                                                                                                                                                            | M products                                    |                                                      | Evaluation                                                                                                      | n products  |

| CPU                                          |                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                    | F <sup>2</sup> MC-1                           | 6LX CPU                                              |                                                                                                                 |             |

| System clock                                 | ·                                                                                                                                                                   | •                                                                                                                                                                                                                                                                                                                                  | 2, ×3, ×4, ×6, 1/2 v<br>42 ns (oscillation of | when PLL stops)<br>clock 4 MHz, PLL ×                | 6)                                                                                                              |             |

| ROM                                          | ,                                                                                                                                                                   | B90351E(S), MB90<br>B90352E(S), MB90                                                                                                                                                                                                                                                                                               | ` '                                           |                                                      | Exte                                                                                                            | ernal       |

| RAM                                          |                                                                                                                                                                     | 4 Kt                                                                                                                                                                                                                                                                                                                               | oytes                                         |                                                      | 30 K                                                                                                            | bytes       |

| Emulator-specific power supply*              |                                                                                                                                                                     | -                                                                                                                                                                                                                                                                                                                                  | _                                             |                                                      | Y                                                                                                               | es          |

| Sub clock pin<br>(X0A, X1A)<br>(Max 100 kHz) | Ye                                                                                                                                                                  | es                                                                                                                                                                                                                                                                                                                                 | N                                             | No                                                   | No                                                                                                              | Yes         |

| Clock supervisor                             |                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                    | N                                             | lo                                                   | •                                                                                                               | 1           |

| Low voltage/CPU operation detection reset    | No                                                                                                                                                                  | Yes                                                                                                                                                                                                                                                                                                                                | No                                            | Yes                                                  | N                                                                                                               | lo          |

| Operating voltage range                      | 4.0 V to 5.5 V : at                                                                                                                                                 | 3.5 V to 5.5 V : at normal operating (not using A/D converter) 4.0 V to 5.5 V : at using A/D converter 4.5 V to 5.5 V : at using external bus                                                                                                                                                                                      |                                               |                                                      | 5 V ± 10%                                                                                                       |             |

| Operating temperature range                  |                                                                                                                                                                     | −40°C to                                                                                                                                                                                                                                                                                                                           | +125°C                                        |                                                      | _                                                                                                               |             |

| Package                                      |                                                                                                                                                                     | LQF                                                                                                                                                                                                                                                                                                                                | P-64                                          |                                                      | PGA-299                                                                                                         |             |

|                                              |                                                                                                                                                                     | 2 cha                                                                                                                                                                                                                                                                                                                              | innels                                        |                                                      | 5 cha                                                                                                           | nnels       |

| LIN-UART                                     | Special synchrono                                                                                                                                                   | ous options for ada                                                                                                                                                                                                                                                                                                                |                                               | d rate generator (re<br>nchronous serial p<br>device |                                                                                                                 |             |

| I <sup>2</sup> C (400 kbps)                  |                                                                                                                                                                     | 1 cha                                                                                                                                                                                                                                                                                                                              | annel                                         |                                                      | 2 channels                                                                                                      |             |

|                                              |                                                                                                                                                                     | 15 ch                                                                                                                                                                                                                                                                                                                              | annels                                        |                                                      | 24 ch                                                                                                           | annels      |

| A/D converter                                | 10-bit or 8-bit reso<br>Conversion time :                                                                                                                           |                                                                                                                                                                                                                                                                                                                                    | sample time (per c                            | one channel)                                         |                                                                                                                 |             |

|                                              |                                                                                                                                                                     | 2 cha                                                                                                                                                                                                                                                                                                                              | innels                                        |                                                      | 4 cha                                                                                                           | nnels       |

| 16-bit reload timer                          | Operation clock frequency: fsys/2 <sup>1</sup> , fsys/2 <sup>3</sup> , fsys/2 <sup>5</sup> (fsys = Machine clock frequency) Supports External Event Count function. |                                                                                                                                                                                                                                                                                                                                    |                                               |                                                      |                                                                                                                 |             |

| 16-bit free-run timer<br>(2 channels)        | Free-run Timer 0 (clock input FRCK0) corresponds to ICU0/1. Free-run Timer 1 (clock input FRCK1) corresponds to ICU4/5/6/7, OCU4/5/6/7.                             |                                                                                                                                                                                                                                                                                                                                    |                                               |                                                      | Free-run Timer 0 corresponds to ICU0/1/2/3, OCU0/1/2/3. Free-run Timer 1 corresponds to ICU4/5/6/7, OCU4/5/6/7. |             |

| •                                            | Supports Timer Ci<br>Operation clock from                                                                                                                           | Signals an interrupt when overflowing. Supports Timer Clear when it matches Output Compare (ch.0, ch.4). Operation clock frequency: fsys, fsys/2 <sup>1</sup> , fsys/2 <sup>2</sup> , fsys/2 <sup>3</sup> , fsys/2 <sup>4</sup> , fsys/2 <sup>5</sup> , fsys/2 <sup>6</sup> , fsys/2 <sup>7</sup> (fsys = Machine clock frequency) |                                               |                                                      |                                                                                                                 |             |

| Part Number Parameter                         | MB90351E<br>MB90352E                                                                                                                                                                                                                                                                                                                                                                         | MB90351TE<br>MB90352TE                                                                | MB90351ES<br>MB90352ES                                                                                                                                          | MB90351TES<br>MB90352TES | MB90V340E-1<br>01    | MB90V340E-1<br>02 |  |

|-----------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|----------------------|-------------------|--|

|                                               |                                                                                                                                                                                                                                                                                                                                                                                              | 4 cha                                                                                 | ınnels                                                                                                                                                          |                          | 8 channels           |                   |  |

| 16-bit output compare                         |                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                       | -run Timer matches<br>sed to generate an                                                                                                                        |                          | egisters.            |                   |  |

| 40 hit is not a set of                        |                                                                                                                                                                                                                                                                                                                                                                                              | 6 cha                                                                                 | innels                                                                                                                                                          |                          | 8 cha                | annels            |  |

| 16-bit input capture                          | Retains 16-bit free                                                                                                                                                                                                                                                                                                                                                                          | e-run timer value by                                                                  | / (rising edge, fallin                                                                                                                                          | ig edge, or the both     | n edges), signals ar | n interrupt.      |  |

| 8/16-bit<br>programmable pulse gen-<br>erator | 8-                                                                                                                                                                                                                                                                                                                                                                                           | 6 channels (16-bit)<br>8-bit reload o<br>bit reload registers<br>bit reload registers | 8 channels (16-bit)/ 16 channels (8-bit) 8-bit reload counters × 16 8-bit reload registers for L pulse width × 16 8-bit reload registers for H pulse width × 16 |                          |                      |                   |  |

| erator                                        | Supports 8-bit and 16-bit operation modes.  A pair of 8-bit reload counters can be configured as one 16-bit reload counter or as 8-bit prescaler + 8-bit reload counter.  Operation clock frequency: fsys, fsys/2 <sup>1</sup> , fsys/2 <sup>2</sup> , fsys/2 <sup>3</sup> , fsys/2 <sup>4</sup> or 128 μs@fosc = 4 MHz (fsys = Machine clock frequency, fosc = Oscillation clock frequency) |                                                                                       |                                                                                                                                                                 |                          |                      |                   |  |

|                                               |                                                                                                                                                                                                                                                                                                                                                                                              | 1 ch                                                                                  | 3 cha                                                                                                                                                           | annels                   |                      |                   |  |

| CAN interface                                 | Compliant with CAN standard Version 2.0 Part A and Part B. Automatic re-transmission in case of error Automatic transmission responding to Remote Frame 16 prioritized message buffers for data and ID Supports multiple messages. Flexible configuration of acceptance filtering: Full bit compare/Full bit mask/Two partial bit masks Supports up to 1 Mbps.                               |                                                                                       |                                                                                                                                                                 |                          |                      |                   |  |

|                                               |                                                                                                                                                                                                                                                                                                                                                                                              | 8 cha                                                                                 | innels                                                                                                                                                          |                          | 16 ch                | annels            |  |

| External interrupt                            | Can be used rising extended intelliger                                                                                                                                                                                                                                                                                                                                                       | g edge, falling edge<br>nt I/O services (El <sup>2</sup>                              | e, starting up by "H<br>OS) and DMA.                                                                                                                            | "/"L" level input, ex    | ternal interrupt,    |                   |  |

| D/A converter                                 |                                                                                                                                                                                                                                                                                                                                                                                              | -                                                                                     |                                                                                                                                                                 |                          | 2 cha                | annels            |  |

| I/O ports                                     | Virtually all external pins can be used as general purpose I/O port. All push-pull outputs Bit-wise settable as input/output or peripheral signal Settable as CMOS schmitt trigger/ automotive inputs TTL input level settable for external bus (only for external bus pin)                                                                                                                  |                                                                                       |                                                                                                                                                                 |                          |                      |                   |  |

| Flash memory                                  |                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                       | -                                                                                                                                                               |                          |                      |                   |  |

| Corresponding evaluation name                 | MB90V3                                                                                                                                                                                                                                                                                                                                                                                       | 40E-102                                                                               | MB90V3                                                                                                                                                          | 340E-101                 | -                    |                   |  |

<sup>\*:</sup> It is setting of Jumper switch (TOOL VCC) when Emulator (MB2147-01) is used. Please refer to the Emulator hardware manual about details.

■ MASK ROM products/Evaluation products

| Part Number                               |                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                        |                                                                     |                                                                                                          |                                  |                   |

|-------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|----------------------------------|-------------------|

|                                           | MB90356E<br>MB90357E                                                                                                                       | MB90356TE<br>MB90357TE                                                                                                                                                                                                                                                                                                                 | MB90356ES<br>MB90357ES                                              | MB90356TES<br>MB90357TES                                                                                 | MB90V340E-1<br>03                | MB90V340E-1<br>04 |

| Parameter                                 |                                                                                                                                            | 111111111111111111111111111111111111111                                                                                                                                                                                                                                                                                                | 11120000720                                                         |                                                                                                          |                                  | <b>V</b> 4        |

| CPU                                       |                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                        | F <sup>2</sup> MC-16                                                | SLX CPU                                                                                                  |                                  |                   |

| System clock                              |                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                        | $\times$ 3, $\times$ 4, $\times$ 6, 1/2 who 42 ns (oscillation of   | . ,                                                                                                      | 6)                               |                   |

| ROM                                       | ,                                                                                                                                          | B90356E(S), MB90<br>B90357E(S), MB90                                                                                                                                                                                                                                                                                                   | ` '                                                                 |                                                                                                          | Exte                             | ernal             |

| RAM                                       |                                                                                                                                            | 4 Kb                                                                                                                                                                                                                                                                                                                                   | ytes                                                                |                                                                                                          | 30 K                             | bytes             |

| Emulator-specific power supply*           |                                                                                                                                            | -                                                                                                                                                                                                                                                                                                                                      | =                                                                   |                                                                                                          | Y                                | es                |

| Sub clock pin<br>(X0A, X1A)               | Ye                                                                                                                                         | es                                                                                                                                                                                                                                                                                                                                     | N                                                                   | lo                                                                                                       | No                               | Yes               |

| Clock supervisor                          |                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                        | Y                                                                   | es                                                                                                       | •                                |                   |

| Low voltage/CPU operation detection reset | No                                                                                                                                         | Yes                                                                                                                                                                                                                                                                                                                                    | No                                                                  | Yes                                                                                                      | N                                | lo                |

| Operating voltage range                   | 4.0 V to 5.5 V : at                                                                                                                        | normal operating (using A/D converteusing external bus                                                                                                                                                                                                                                                                                 | not using A/D conver                                                | erter)                                                                                                   | 5 V ± 10%                        |                   |

| Operating temperature range               |                                                                                                                                            | −40°C to                                                                                                                                                                                                                                                                                                                               | ) +125°C                                                            |                                                                                                          | _                                |                   |

| Package                                   |                                                                                                                                            | LQF                                                                                                                                                                                                                                                                                                                                    | P-64                                                                |                                                                                                          | PGA-299                          |                   |

|                                           |                                                                                                                                            | 2 cha                                                                                                                                                                                                                                                                                                                                  | nnels                                                               |                                                                                                          | 5 channels                       |                   |

| LIN-UART                                  | Special synchrono                                                                                                                          | ous options for ada                                                                                                                                                                                                                                                                                                                    | ng a dedicated bau<br>pting to different sy<br>aster or slave LIN o | nchronous serial p                                                                                       |                                  |                   |

| I <sup>2</sup> C (400 kbps)               |                                                                                                                                            | 1 cha                                                                                                                                                                                                                                                                                                                                  | annel                                                               |                                                                                                          | 2 cha                            | nnels             |

|                                           |                                                                                                                                            | 15 cha                                                                                                                                                                                                                                                                                                                                 | annels                                                              |                                                                                                          | 24 ch                            | annels            |

| A/D converter                             | 10-bit or 8-bit reso<br>Conversion time :                                                                                                  |                                                                                                                                                                                                                                                                                                                                        | sample time (per o                                                  | ne channel)                                                                                              |                                  |                   |

| 16-bit reload timer<br>(4 channels)       | Operation clock from Supports External                                                                                                     | equency : fsys/2 <sup>1</sup> , t<br>Event Count funct                                                                                                                                                                                                                                                                                 | fsys/ $2^3$ , fsys/ $2^5$ (fsyion.                                  | ys = Machine clock                                                                                       | frequency)                       |                   |

| 16-bit free-run timer<br>(2 channels)     | Free-run Timer 0 (clock input FRCK0) corresponds to ICU 0/1. Free-run Timer 1 (clock input FRCK1) corresponds to ICU 4/5/6/7, OCU 4/5/6/7. |                                                                                                                                                                                                                                                                                                                                        |                                                                     | Free-run Timer 0<br>corresponds to<br>OCU 0/1/2/3.<br>Free-run Timer 1<br>corresponds to<br>OCU 4/5/6/7. | o ICU 0/1/2/3,<br>o ICU 4/5/6/7, |                   |

| ,                                         | Supports Timer Cl<br>Operation clock from                                                                                                  | Signals an interrupt when overflowing. Supports Timer Clear when a match with Output Compare (Channel 0, 4). Operation clock frequency: fsys, fsys/2 <sup>1</sup> , fsys/2 <sup>2</sup> , fsys/2 <sup>3</sup> , fsys/2 <sup>4</sup> , fsys/2 <sup>5</sup> , fsys/2 <sup>6</sup> , fsys/2 <sup>7</sup> (fsys = Machine clock frequency) |                                                                     |                                                                                                          |                                  |                   |

| Pin No. | Pin name        | I/O<br>Circuit<br>type* | Function                                                                                                                                                                                                                                                                           |

|---------|-----------------|-------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | P30             | _                       | General purpose I/O port. The register can be set to select whether to use a pull-up resistor. This function is enabled in single-chip mode.                                                                                                                                       |

| 54      | ALE             | G                       | Address latch enable output pin. This function is enabled when external bus is enabled.                                                                                                                                                                                            |

|         | IN4             |                         | Data sample input pin for input capture ICU4                                                                                                                                                                                                                                       |

|         | P31             |                         | General purpose I/O port. The register can be set to select whether to use a pull-up resistor. This function is enabled in single-chip mode.                                                                                                                                       |

| 55      | RD              | G                       | Read strobe output pin for data bus. This function is enabled when external bus is enabled.                                                                                                                                                                                        |

|         | IN5             |                         | Data sample input pin for input capture ICU5                                                                                                                                                                                                                                       |

|         | P32             |                         | General purpose I/O port. The register can be set to select whether to use a pull-up resistor. This function is enabled either in single-chip mode or with the WR/WRL pin output disabled.                                                                                         |

| 56      | WR/WRL          | G                       | Write strobe output pin for the data bus. This function is enabled when both the external bus and the WR/WRL pin output are enabled. WRL is used to write-strobe 8 lower bits of the data bus in 16-bit access. WR is used to write-strobe 8 bits of the data bus in 8-bit access. |

|         | INT10R          |                         | External interrupt request input pin for INT10                                                                                                                                                                                                                                     |

| 57      | P33<br>7<br>WRH | G                       | General purpose I/O port. The register can be set to select whether to use a pull-up resistor. This function is enabled either in single-chip mode, in external bus 8-bit mode or with the WRH pin output disabled.                                                                |

| 57      |                 |                         | Write strobe output pin for the 8 higher bits of the data bus. This function is enabled when the external bus is enabled, when the external bus 16-bit mode is selected, and when the WRH output pin is enabled.                                                                   |

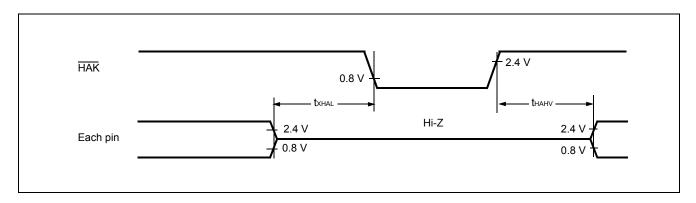

|         | P34             |                         | General purpose I/O port. The register can be set to select whether to use a pull-up resistor. This function is enabled either in single-chip mode or with the hold function disabled.                                                                                             |

| 58      | HRQ             | G                       | Hold request input pin. This function is enabled when both the external bus and the hold function are enabled.                                                                                                                                                                     |

|         | OUT4            |                         | Wave form output pin for output compare OCU4                                                                                                                                                                                                                                       |

|         | P35             |                         | General purpose I/O port. The register can be set to select whether to use a pull-up resistor. This function is enabled either in single-chip mode or with the hold function disabled.                                                                                             |

| 59      | 59 HAK          |                         | Hold acknowledge output pin. This function is enabled when both the external bus and the hold function are enabled.                                                                                                                                                                |

|         | OUT5            |                         | Wave form output pin for output compare OCU5                                                                                                                                                                                                                                       |

|         | P36             |                         | General purpose I/O port. The register can be set to select whether to use a pull-up resistor. This function is enabled either in single-chip mode or with the external ready function disabled.                                                                                   |

| 60      | RDY             | G                       | Ready input pin. This function is enabled when both the external bus and the external ready function are enabled.                                                                                                                                                                  |

|         | OUT6            |                         | Wave form output pin for output compare OCU6                                                                                                                                                                                                                                       |

| Туре | Circuit                                                                                                | Remarks                                                                                                                                                                                                                                                                                         |

|------|--------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| I    | P-ch Nout  R CMOS hysteresis inputs  Automotive input Standby control for input shutdown  Analog input | <ul> <li>■ CMOS level output (I<sub>OL</sub> = 4 mA, I<sub>OH</sub> = -4 mA)</li> <li>■ CMOS hysteresis inputs (With the standby-time input shutdown function)</li> <li>■ Automotive input (With the standby-time input shutdown function)</li> <li>■ Analog input for A/D converter</li> </ul> |

| К    | P-ch<br>N-ch                                                                                           | Protection circuit for power supply input                                                                                                                                                                                                                                                       |

| L    | ANE P-ch AVR ANE ANE                                                                                   | <ul> <li>With the protection circuit of A/D converter reference voltage power input pin</li> <li>Flash memory devices do not have a protection circuit against V<sub>CC</sub> for pin AVRH.</li> </ul>                                                                                          |

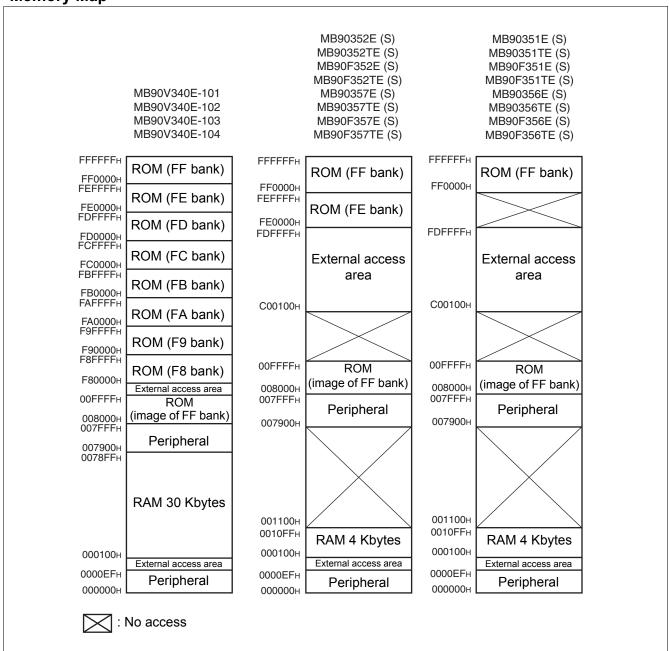

## 9. Memory Map

Note: The high-order portion of bank 00 gives the image of the FF bank ROM to make the small model of the C compiler effective. Since the low-order 16 bits are the same, the table in ROM can be referenced without using the far specification in the pointer declaration.

For example, an attempt to access  $00C000_H$  practically accesses the value at FFC000<sub>H</sub> in ROM.

The ROM area in bank FF exceeds 32 Kbytes, and its entire image cannot be shown in bank 00.

The image between  $FF8000_H$  and  $FFFFF_H$  is visible in bank 00, while the image between  $FF0000_H$  and  $FF7FFF_H$  is visible only in bank FF.

# 10. I/O Map

| Address                                       | Register                            | Abbreviation | Access | Resource name | Initial value         |

|-----------------------------------------------|-------------------------------------|--------------|--------|---------------|-----------------------|

| 000000 <sub>H</sub>                           | Port 0 Data Register                | PDR0         | R/W    | Port 0        | XXXXXXXX <sub>B</sub> |

| 000001 <sub>H</sub>                           | Port 1 Data Register                | PDR1         | R/W    | Port 1        | XXXXXXXX <sub>B</sub> |

| 000002 <sub>H</sub>                           | Port 2 Data Register                | PDR2         | R/W    | Port 2        | XXXXXXXX <sub>B</sub> |

| 000003 <sub>H</sub>                           | Port 3 Data Register                | PDR3         | R/W    | Port 3        | XXXXXXXX              |

| 000004 <sub>H</sub>                           | Port 4 Data Register                | PDR4         | R/W    | Port 4        | XXXXXXXX              |

| 000005 <sub>H</sub>                           | Port 5 Data Register                | PDR5         | R/W    | Port 5        | XXXXXXXX <sub>B</sub> |

| 000006 <sub>H</sub>                           | Port 6 Data Register                | PDR6         | R/W    | Port 6        | XXXXXXXX              |

| 000007 <sub>H</sub> to<br>00000A <sub>H</sub> |                                     | Reserve      | d      |               |                       |

| 00000B <sub>H</sub>                           | Port 5 Analog Input Enable Register | ADER5        | R/W    | Port 5, A/D   | 11111111 <sub>B</sub> |

| 00000C <sub>H</sub>                           | Port 6 Analog Input Enable Register | ADER6        | R/W    | Port 6, A/D   | 11111111 <sub>B</sub> |