Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                                |

|----------------------------|--------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                       |

| Core Processor             | F <sup>2</sup> MC-16LX                                                         |

| Core Size                  | 16-Bit                                                                         |

| Speed                      | 24MHz                                                                          |

| Connectivity               | CANbus, EBI/EMI, I <sup>2</sup> C, LINbus, UART/USART                          |

| Peripherals                | DMA, LVD, POR, WDT                                                             |

| Number of I/O              | 51                                                                             |

| Program Memory Size        | 128KB (128K x 8)                                                               |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | -                                                                              |

| RAM Size                   | 4K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 3.5V ~ 5.5V                                                                    |

| Data Converters            | A/D 15x8/10b                                                                   |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                             |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 64-LQFP                                                                        |

| Supplier Device Package    | 64-LQFP (12x12)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/mb90f352espmc1-gse2 |

# MB90350E Series

## Contents

| Product Lineup1 (Without Clock supervisor fund   | tion) 4 |

|--------------------------------------------------|---------|

| Product Lineup 2 (With Clock supervisor function | n)7     |

| Packages and Product Correspondence              | 12      |

| Pin Assignments                                  | 13      |

| Pin Description                                  | 14      |

| I/O Circuit Type                                 |         |

| Handling Devices                                 | 22      |

| Block Diagrams                                   | 27      |

| Memory Map                                       | 33      |

| I/O Map                                          | 34      |

| CAN Controllers                                  | 42      |

| Interrupt Factors, Interrupt Vectors, Interrupt  |         |

| Control Register                                 | 50      |

| Electrical Characteristics                       | 51      |

| Absolute Maximum Ratings                         | 51      |

| Recommended Operating Conditions                 | 53      |

| DC Characteristics                               |         |

| AC Characteristics                               | 59      |

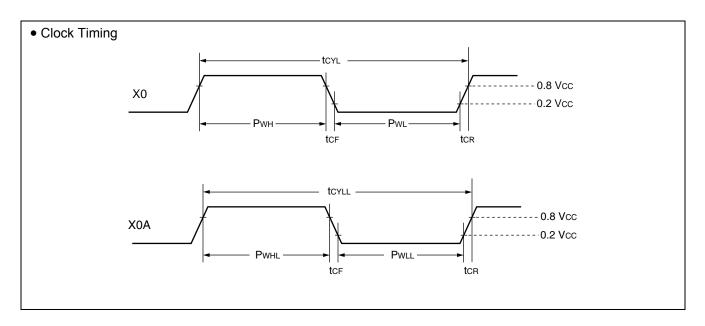

| Clock Timing                                     | 59      |

| Reset Standby Input                        | 62 |

|--------------------------------------------|----|

| Power On Reset                             | 63 |

| Clock Output Timing                        | 63 |

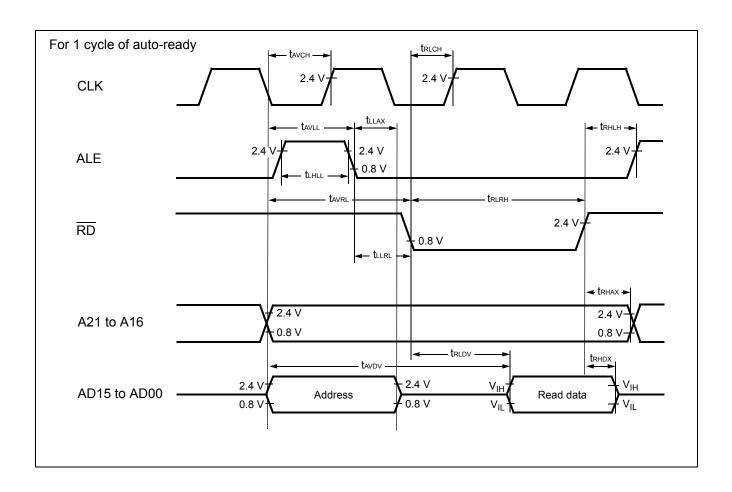

| Bus Timing (Read)                          |    |

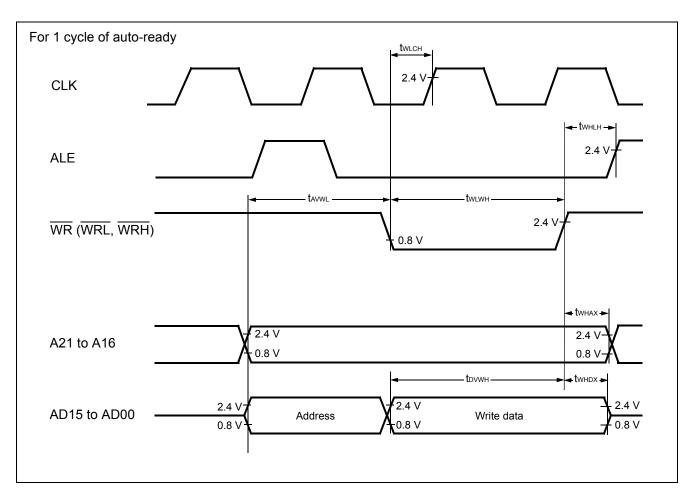

| Bus Timing (Write)                         | 66 |

| Ready Input Timing                         | 67 |

| Hold Timing                                | 68 |

| LIN-UART2/3                                | 69 |

| Trigger Input Timing                       | 73 |

| Timer Related Resource Input Timing        |    |

| Timer Related Resource Output Timing       | 74 |

| I2C Timing                                 | 75 |

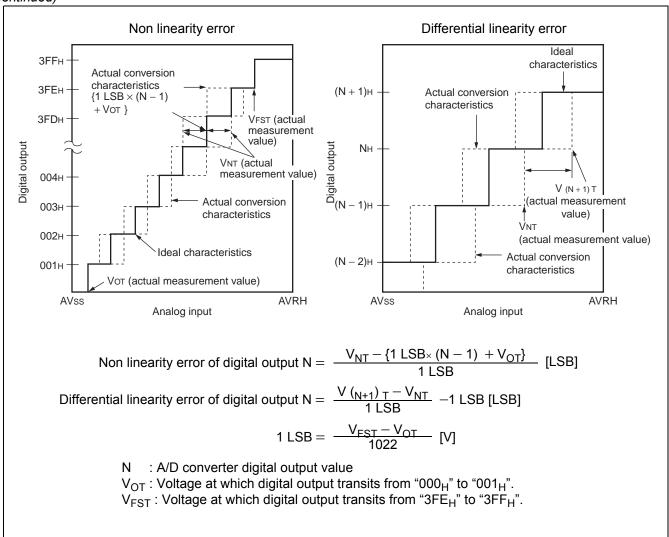

| A/D Converter                              | 76 |

| Definition of A/D Converter Terms          | 80 |

| Flash Memory Program/Erase Characteristics | 82 |

| Ordering Information                       | 83 |

| Package Dimensions                         | 85 |

| Major Changes                              | 87 |

|                                            |    |

| Part Number Parameter         | MB90F351E<br>MB90F352E                                                                                                                                                                                                                                                                                                                                                                                                              | MB90F351TE<br>MB90F352TE                                                                                                                                                                                                                                                                                                                                                                      | MB90F351ES<br>MB90F352ES         | MB90F351TES<br>MB90F352TES |  |  |  |  |  |

|-------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|----------------------------|--|--|--|--|--|

| 16-bit Input capture          |                                                                                                                                                                                                                                                                                                                                                                                                                                     | 6 cha                                                                                                                                                                                                                                                                                                                                                                                         |                                  |                            |  |  |  |  |  |

|                               |                                                                                                                                                                                                                                                                                                                                                                                                                                     | er value by (rising edge, fallin                                                                                                                                                                                                                                                                                                                                                              | ig edge or rising & falling ed   | ge), signals an interrupt. |  |  |  |  |  |

|                               |                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                               |                                  |                            |  |  |  |  |  |

| programmable pulse generator  | A pair of 8-bit reload count<br>8-bit prescaler + 8-bit reloa<br>Operation clock frequency                                                                                                                                                                                                                                                                                                                                          | Supports 8-bit and 16-bit operation modes.  A pair of 8-bit reload counters can be configured as one 16-bit reload counter or as 8-bit prescaler + 8-bit reload counter.  Operation clock frequency: fsys, fsys/2 <sup>1</sup> , fsys/2 <sup>2</sup> , fsys/2 <sup>3</sup> , fsys/2 <sup>4</sup> or 128 µs@fosc = 4 MHz  (fsys = Machine clock frequency, fosc = Oscillation clock frequency) |                                  |                            |  |  |  |  |  |

|                               |                                                                                                                                                                                                                                                                                                                                                                                                                                     | 1 cha                                                                                                                                                                                                                                                                                                                                                                                         | annel                            |                            |  |  |  |  |  |

| CAN interface                 | Compliant with CAN standard Version2.0 Part A and Part B. Automatic re-transmission in case of error Automatic transmission responding to Remote Frame 16 prioritized message buffers for data and ID Supports multiple messages. Flexible configuration of acceptance filtering: Full bit compare/Full bit mask/Two partial bit masks Supports up to 1 Mbps.                                                                       |                                                                                                                                                                                                                                                                                                                                                                                               |                                  |                            |  |  |  |  |  |

|                               |                                                                                                                                                                                                                                                                                                                                                                                                                                     | 8 cha                                                                                                                                                                                                                                                                                                                                                                                         | nnels                            |                            |  |  |  |  |  |

| External interrupt            | Can be used rising edge, fa extended intelligent I/O ser                                                                                                                                                                                                                                                                                                                                                                            | alling edge, starting up by "H<br>vices (El <sup>2</sup> OS) and DMA.                                                                                                                                                                                                                                                                                                                         | "/"L" level input, external into | errupt,                    |  |  |  |  |  |

| D/A converter                 |                                                                                                                                                                                                                                                                                                                                                                                                                                     | _                                                                                                                                                                                                                                                                                                                                                                                             | _                                |                            |  |  |  |  |  |

| I/O ports                     | Virtually all external pins can be used as general purpose I/O port. All push-pull outputs Bit-wise settable as input/output or peripheral signal Settable as CMOS schmitt trigger/ automotive inputs TTL input level settable for external bus (only for external bus pin)                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                               |                                  |                            |  |  |  |  |  |

| Flash memory                  | Supports automatic programming, Embedded Algorithm Write/Erase/Erase-Suspend/Resume commands A flag indicating completion of the algorithm Number of erase cycles: 10000 times Data retention time: 20 years Boot block configuration Erase can be performed on each block. Block protection with external programming voltage Flash Security Feature for protecting the content of the Flash (MB90F352E(S) and MB90F352TE(S) only) |                                                                                                                                                                                                                                                                                                                                                                                               |                                  |                            |  |  |  |  |  |

| Corresponding evaluation name | MB90V340E-102  MB90V340E-101  MB90V340E-101                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                               |                                  |                            |  |  |  |  |  |

<sup>\*:</sup> It is setting of Jumper switch (TOOL VCC) when Emulator (MB2147-01) is used. Please refer to the Emulator hardware manual about details.

■ MASK ROM products/Evaluation products

| Part Number                               |                                                                                      |                                                                                                                                                     |                                                                                                          |                                                                                    |                                           |                   |  |  |  |

|-------------------------------------------|--------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------|-------------------------------------------|-------------------|--|--|--|

|                                           | MB90356E<br>MB90357E                                                                 | MB90356TE<br>MB90357TE                                                                                                                              | MB90356ES<br>MB90357ES                                                                                   | MB90356TES<br>MB90357TES                                                           | MB90V340E-1<br>03                         | MB90V340E-1<br>04 |  |  |  |

| Parameter                                 |                                                                                      | 111111111111111111111111111111111111111                                                                                                             | III.DOGGGT EG                                                                                            | 1111200007 120                                                                     |                                           | <b>V</b> 4        |  |  |  |

| CPU                                       |                                                                                      |                                                                                                                                                     | F <sup>2</sup> MC-16                                                                                     | SLX CPU                                                                            |                                           |                   |  |  |  |

| System clock                              |                                                                                      | On-chip PLL clock multiplier (×1, ×2, ×3, ×4, ×6, 1/2 when PLL stops)  Minimum instruction execution time: 42 ns (oscillation clock 4 MHz, PLL × 6) |                                                                                                          |                                                                                    |                                           |                   |  |  |  |

| ROM                                       | ,                                                                                    | B90356E(S), MB90<br>B90357E(S), MB90                                                                                                                |                                                                                                          | External                                                                           |                                           |                   |  |  |  |

| RAM                                       |                                                                                      | 4 Kb                                                                                                                                                | oytes                                                                                                    |                                                                                    | 30 K                                      | bytes             |  |  |  |

| Emulator-specific power supply*           |                                                                                      | -                                                                                                                                                   |                                                                                                          |                                                                                    | Y                                         | es                |  |  |  |

| Sub clock pin<br>(X0A, X1A)               | Ye                                                                                   | es                                                                                                                                                  | N                                                                                                        | lo                                                                                 | No                                        | Yes               |  |  |  |

| Clock supervisor                          |                                                                                      |                                                                                                                                                     | Y                                                                                                        | es                                                                                 |                                           |                   |  |  |  |

| Low voltage/CPU operation detection reset | No                                                                                   | No Yes No Yes                                                                                                                                       |                                                                                                          |                                                                                    |                                           | lo                |  |  |  |

| Operating voltage range                   | 4.0 V to 5.5 V : at                                                                  | normal operating (using A/D converteusing external bus                                                                                              | 5 V ± 10%                                                                                                |                                                                                    |                                           |                   |  |  |  |

| Operating temperature range               |                                                                                      | −40°C to                                                                                                                                            | _                                                                                                        |                                                                                    |                                           |                   |  |  |  |

| Package                                   |                                                                                      | LQF                                                                                                                                                 | P-64                                                                                                     |                                                                                    | PGA-299                                   |                   |  |  |  |

|                                           |                                                                                      | 2 cha                                                                                                                                               | innels                                                                                                   |                                                                                    | 5 cha                                     | innels            |  |  |  |

| LIN-UART                                  | Special synchrono                                                                    | ous options for ada                                                                                                                                 | ng a dedicated bau<br>pting to different sy<br>aster or slave LIN c                                      | nchronous serial p                                                                 |                                           |                   |  |  |  |

| I <sup>2</sup> C (400 kbps)               |                                                                                      | 1 cha                                                                                                                                               | annel                                                                                                    |                                                                                    | 2 cha                                     | innels            |  |  |  |

|                                           |                                                                                      | 15 cha                                                                                                                                              | annels                                                                                                   |                                                                                    | 24 ch                                     | annels            |  |  |  |

| A/D converter                             |                                                                                      | 10-bit or 8-bit resolution Conversion time : Min 3 μs includes sample time (per one channel)                                                        |                                                                                                          |                                                                                    |                                           |                   |  |  |  |

| 16-bit reload timer<br>(4 channels)       | Operation clock from Supports External                                               | equency : fsys/2 <sup>1</sup> , t<br>Event Count funct                                                                                              | fsys/ $2^3$ , fsys/ $2^5$ (fsyion.                                                                       | ys = Machine clock                                                                 | frequency)                                |                   |  |  |  |

| 16-bit free-run timer<br>(2 channels)     | ·                                                                                    | (clock input FRCK0                                                                                                                                  | Free-run Timer 0<br>corresponds to<br>OCU 0/1/2/3.<br>Free-run Timer 1<br>corresponds to<br>OCU 4/5/6/7. | o ICU 0/1/2/3,<br>o ICU 4/5/6/7,                                                   |                                           |                   |  |  |  |

| ,                                         | Signals an interrup<br>Supports Timer Cl<br>Operation clock fr<br>(fsys = Machine cl | ot when overflowing<br>lear when a match<br>equency : fsys, fsys<br>ock frequency)                                                                  | g.<br>with Output Compa<br>s/2 <sup>1</sup> , fsys/2 <sup>2</sup> , fsys/2                               | are (Channel 0, 4) .<br><sup>3</sup> , fsys/2 <sup>4</sup> , fsys/2 <sup>5</sup> , | fsys/2 <sup>6</sup> , fsys/2 <sup>7</sup> | (Oa na            |  |  |  |

| Part Number Parameter               | MB90356E<br>MB90357E                                                                                                                                                               | MB90356TE<br>MB90357TE                                                                                              | MB90356ES<br>MB90357ES                                                 | MB90356TES<br>MB90357TES                                                                                                                                  | MB90V340E-1<br>03 | MB90V340E-1<br>04 |  |

|-------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|-------------------|--|

| 16-bit output                       |                                                                                                                                                                                    | 4 cha                                                                                                               | nnels                                                                  |                                                                                                                                                           | 8 channels        |                   |  |

| compare                             | Signals an interrupt<br>A pair of compare r                                                                                                                                        |                                                                                                                     |                                                                        | are registers.                                                                                                                                            |                   |                   |  |

|                                     |                                                                                                                                                                                    | 6 cha                                                                                                               | annels                                                                 |                                                                                                                                                           | 8 cha             | nnels             |  |

| 16-bit input capture                | Retains 16-bit free-<br>signals an interrupt                                                                                                                                       |                                                                                                                     | y (rising edge, fallir                                                 | g edge or rising &                                                                                                                                        | falling edge),    |                   |  |

| 8/16-bit<br>programmable pulse gen- | 8-bi                                                                                                                                                                               | channels (16-bit)<br>8-bit reload<br>t reload registers<br>t reload registers                                       | 12                                                                     | 8 channels (16-bit)/ 16 channels (8-bit) 8-bit reload counters×16 8-bit reload registers for L pulse width×16 8-bit reload registers for H pulse width×16 |                   |                   |  |

| erator                              | Supports 8-bit and<br>A pair of 8-bit reload<br>8-bit prescaler + 8-bit<br>Operation clock fred<br>(fsys = Machine clo                                                             | d counters can be<br>oit reload counter<br>quency : fsys, fsy                                                       | e configured as one<br>s/2 <sup>1</sup> , fsys/2 <sup>2</sup> , fsys/2 | e <sup>3</sup> , fsys/2 <sup>4</sup> or 128 μ                                                                                                             |                   |                   |  |

|                                     |                                                                                                                                                                                    | 1 cha                                                                                                               | annel                                                                  |                                                                                                                                                           | 3 cha             | nnels             |  |

| CAN interface                       | Conforms to CAN S<br>Automatic re-transm<br>Automatic transmis<br>Prioritized 16 mess<br>Supports multiple m<br>Flexible configuratic<br>Full bit compare/F<br>Supports up to 1 Mi | nission in case of<br>sion responding t<br>age buffers for da<br>nessages.<br>on of acceptance<br>-ull bit mask/Two | error o Remote Frame ata and ID                                        | В.                                                                                                                                                        |                   |                   |  |

|                                     |                                                                                                                                                                                    | 8 cha                                                                                                               | nnels                                                                  |                                                                                                                                                           | 16 ch             | annels            |  |

| External interrupt                  | Can be used rising extended intelligent                                                                                                                                            | edge, falling edge<br>I/O services (El <sup>2</sup>                                                                 | e, starting up by H/<br>OS) and DMA.                                   | L level input, exterr                                                                                                                                     | nal interrupt,    |                   |  |

|                                     | - 2 channels                                                                                                                                                                       |                                                                                                                     |                                                                        |                                                                                                                                                           |                   |                   |  |

| D/A converter                       |                                                                                                                                                                                    | -                                                                                                                   | _                                                                      |                                                                                                                                                           | 2 cha             | nnels             |  |

| D/A converter  I/O ports            | Virtually all external<br>All push-pull output<br>Bit-wise settable as<br>Settable as CMOS<br>TTL input level sett                                                                 | s<br>input/output or p<br>schmitt trigger/ au                                                                       | eripheral module s<br>utomotive inputs                                 | gnal                                                                                                                                                      | 2 cha             | nnels             |  |

|                                     | All push-pull output<br>Bit-wise settable as<br>Settable as CMOS                                                                                                                   | s<br>input/output or p<br>schmitt trigger/ au                                                                       | eripheral module s<br>utomotive inputs                                 | gnal                                                                                                                                                      | 2 cha             | nnels             |  |

<sup>\*:</sup> It is setting of Jumper switch (TOOL VCC) when Emulator (MB2147-01) is used. Please refer to the Emulator hardware manual about details.

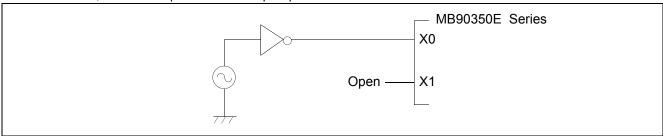

### 3. Using external clock

To use external clock, drive the X0 pin and leave X1 pin open.

### 4. Precautions for when not using a sub clock signal

X0A and X1A are oscillation pins for sub clock. If you do not connect pins X0A and X1A to an oscillator, use pull-down handling on the X0A pin, and leave the X1A pin open.

### 5. Notes on during operation of PLL clock mode

On this microcontroller, if in case the crystal oscillator breaks off or an external reference clock input stops while the PLL clock mode is selected, a self-oscillator circuit contained in the PLL may continue its operation at its self-running frequency. However, Cypress will not guarantee results of operations if such failure occurs.

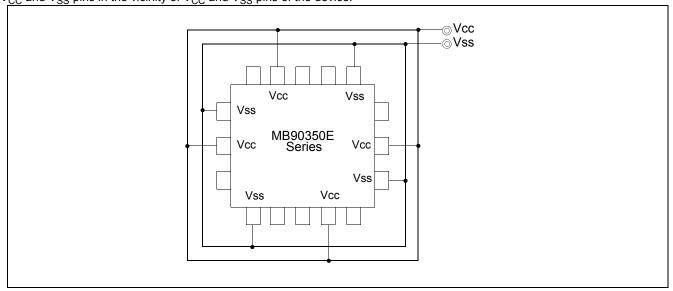

## 6. Treatment of Power Supply Pins (V<sub>CC</sub>/V<sub>SS</sub>)

■ If there are multiple V<sub>CC</sub> and V<sub>SS</sub> pins, from the point of view of device design, pins to be of the same potential are connected inside of the device to prevent malfunction such as latch-up.

To reduce unnecessary radiation, prevent malfunctioning of the strobe signal due to the rise of ground level, and observe the standard for total output current, be sure to connect the  $V_{CC}$  and  $V_{SS}$  pins to the power supply and ground externally. Connect  $V_{CC}$  and  $V_{SS}$  pins to the device from the current supply source at a possibly low impedance.

As a measure against power supply noise, it is recommended to connect a capacitor of about 0.1 μF as a bypass capacitor between V<sub>CC</sub> and V<sub>SS</sub> pins in the vicinity of V<sub>CC</sub> and V<sub>SS</sub> pins of the device.

### 7. Pull-up/down resistors

The MB90350E series does not support internal pull-up/down resistors (Port 0 to Port 3: built-in pull-up resistors). Use external components where needed.

### 8. Crystal oscillator circuit

Noise around the X0/X1, or X0A/X1A pins may cause this device to operate abnormally. In the interest of stable operation it is strongly recommended that printed circuit artwork places ground bypass capacitors as close as possible to the X0/X1, X0A/X1A and crystal oscillator (or ceramic oscillator) and that oscillator lines do not cross the lines of other circuits.

#### 13. Serial Communication

There is a possibility to receive wrong data due to the noise or other causes on the serial communication. Therefore, design a printed circuit board so as to avoid noise.

Retransmit the data if an error occurs because of applying the checksum to the last data in consideration of receiving wrong data due to the noise.

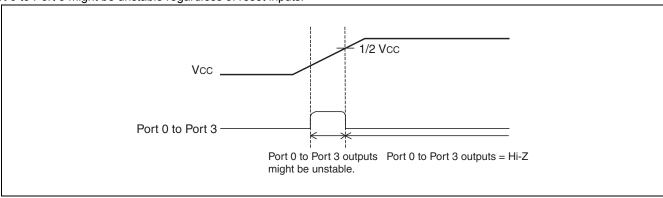

### 14. Port 0 to port 3 output during power-on (External-bus mode)

As shown below, when power is turned on in external-bus mode, there is a possibility that output signal of Port 0 to Port 3 might be unstable regardless of reset inputs.

### 15. Setting using CAN function

To use CAN function, please set "1" to DIRECT bit of CAN direct mode register (CDMR).

#### 16. Flash security function

The security byte is located in the area of the Flash memory. If protection code 01<sub>H</sub> is written in the security byte, the Flash memory is in the protected state by security.

Therefore please do not write 01<sub>H</sub> in this address if you do not use the security function.

Please refer to following table for the address of the security byte.

| Product name                                                   | Flash memory size            | Address for security bit |

|----------------------------------------------------------------|------------------------------|--------------------------|

| MB90F352E(S)<br>MB90F352TE(S)<br>MB90F357E(S)<br>MB90F357TE(S) | Embedded 1 Mbit Flash memory | FE0001 <sub>H</sub>      |

### 17. Operation with $T_A = +105$ °C or more

If used exceeding  $T_A = +105$ °C, please contact Cypress sales representatives for reliability limitations.

### 18. Low voltage/CPU operation reset circuit

The low voltage detection reset circuit is a function that monitors power supply voltage in order to detect when a voltage drops below a given voltage level. When a low voltage condition is detected, an internal reset signal is generated.

The CPU operation detection reset circuit is a 20-bit counter that uses oscillation as a count clock and generates an internal reset signal if not cleared within a given time after startup.

#### (1) Low voltage detection reset circuit

| Detection voltage          |

|----------------------------|

| $4.0~{ m V}\pm 0.3~{ m V}$ |

When a low voltage condition is detected, the low voltage detection flag (LVRC: LVRF) is set to "1" and an internal reset signal is output.

Because the low voltage detection reset circuit continues to operate even in stop mode, detection of a low voltage condition generates an internal reset and releases stop mode.

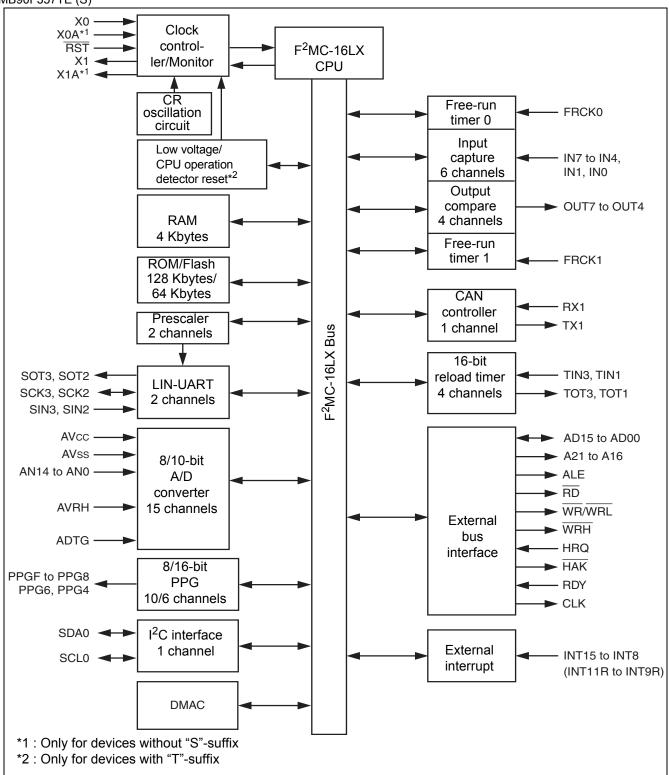

## 8. Block Diagrams

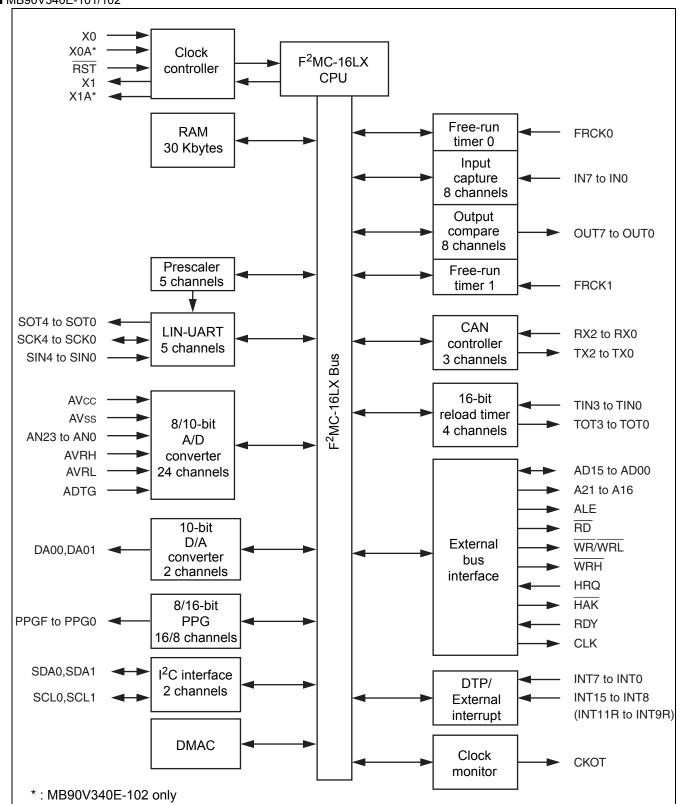

### ■ MB90V340E-101/102

■ MB90356E (S), MB90356TE (S), MB90F356E (S), MB90F356TE (S), MB90357TE (S), MB90357TE (S), MB90F357TE (S)

| Address                                       | Register                                     | Abbreviation | Access      | Resource name        | Initial value         |

|-----------------------------------------------|----------------------------------------------|--------------|-------------|----------------------|-----------------------|

| 0000B9 <sub>H</sub>                           | Interrupt Control Register 09                | ICR09        | W,R/W       |                      | 00000111 <sub>B</sub> |

| 0000BA <sub>H</sub>                           | Interrupt Control Register 10                | ICR10        | W,R/W       |                      | 00000111 <sub>B</sub> |

| 0000BB <sub>H</sub>                           | Interrupt Control Register 11                | ICR11        | W,R/W       |                      | 00000111 <sub>B</sub> |

| 0000BC <sub>H</sub>                           | Interrupt Control Register 12                | ICR12        | W,R/W       | Interrupt Control    | 00000111 <sub>B</sub> |

| 0000BD <sub>H</sub>                           | Interrupt Control Register 13                | ICR13        | W,R/W       |                      | 00000111 <sub>B</sub> |

| 0000BE <sub>H</sub>                           | Interrupt Control Register 14                | ICR14        | W,R/W       |                      | 00000111 <sub>B</sub> |

| 0000BF <sub>H</sub>                           | Interrupt Control Register 15                | ICR15        | W,R/W       |                      | 00000111 <sub>B</sub> |

| 0000C0 <sub>H</sub><br>to 0000C9 <sub>H</sub> |                                              | Reserved     |             |                      |                       |

| 0000CA <sub>H</sub>                           | External Interrupt Enable Register 1         | ENIR1        | R/W         |                      | 00000000 <sub>B</sub> |

| 0000CB <sub>H</sub>                           | External Interrupt Source Register 1         | EIRR1        | R/W         |                      | XXXXXXXX <sub>B</sub> |

| 0000CC <sub>H</sub>                           | External Interrupt Level Register 1          | ELVR1        | R/W         | External Interrupt 1 | 00000000 <sub>B</sub> |

| 0000CD <sub>H</sub>                           | External Interrupt Level Register 1          | ELVR1        | R/W         | External interrupt 1 | 00000000 <sub>B</sub> |

| 0000CE <sub>H</sub>                           | External Interrupt Source Select<br>Register | EISSR        | R/W         |                      | 00000000 <sub>B</sub> |

| 0000CF <sub>H</sub>                           | PLL/Sub clock Control register               | PSCCR        | W           | PLL                  | XXXX0000 <sub>B</sub> |

| 0000D0 <sub>H</sub>                           | DMA Buffer Address Pointer L<br>Register     | BAPL         | R/W         |                      | XXXXXXXX <sub>B</sub> |

| 0000D1 <sub>H</sub>                           | DMA Buffer Address Pointer M<br>Register     | ВАРМ         | R/W         |                      | XXXXXXXX <sub>B</sub> |

| 0000D2 <sub>H</sub>                           | DMA Buffer Address Pointer H<br>Register     | ВАРН         | R/W         |                      | XXXXXXXX <sub>B</sub> |

| 0000D3 <sub>H</sub>                           | DMA Control Register                         | DMACS        | R/W         | DMA                  | XXXXXXXX <sub>B</sub> |

| 0000D4 <sub>H</sub>                           | I/O Register Address Pointer L<br>Register   | IOAL         | R/W         |                      | XXXXXXXX <sub>B</sub> |

| 0000D5 <sub>H</sub>                           | I/O Register Address Pointer H<br>Register   | IOAH         | R/W         |                      | XXXXXXXX <sub>B</sub> |

| 0000D6 <sub>H</sub>                           | Data Counter L Register                      | DCTL         | R/W         |                      | XXXXXXXX              |

| 0000D7 <sub>H</sub>                           | Data Counter H Register                      | DCTH         | R/W         |                      | XXXXXXXX              |

| 0000D8 <sub>H</sub>                           | Serial Mode Register 2                       | SMR2         | W,R/W       |                      | 00000000 <sub>B</sub> |

| 0000D9 <sub>H</sub>                           | Serial Control Register 2                    | SCR2         | W,R/W       |                      | 00000000 <sub>B</sub> |

| 0000DA <sub>H</sub>                           | Reception/Transmission Data<br>Register 2    | RDR2/TDR2    | R/W         |                      | 00000000 <sub>B</sub> |

| 0000DB <sub>H</sub>                           | Serial Status Register 2                     | SSR2         | R,R/W       | UART2                | 00001000 <sub>B</sub> |

| 0000DC <sub>H</sub>                           | Extended Communication Control Register 2    | ECCR2        | R,W,<br>R/W |                      | 000000XX <sub>B</sub> |

| 0000DD <sub>H</sub>                           | Extended Status/Control Register 2           | ESCR2        | R/W         |                      | 00000100 <sub>B</sub> |

| 0000DE <sub>H</sub>                           | Baud Rate Generator Register 20              | BGR20        | R/W         |                      | 00000000 <sub>B</sub> |

| Address             | Posistor                               | Abbreviation | A00000                | Initial Value         |  |

|---------------------|----------------------------------------|--------------|-----------------------|-----------------------|--|

| CAN1                | Register                               | Appreviation | Access                | Initial Value         |  |

| 007D00 <sub>H</sub> | Control status register                | CSR          | R/W, W                | 0XXXX0X1 <sub>B</sub> |  |

| 007D01 <sub>H</sub> | Control status register                | CSK          | R/W, R                | 00XXX000 <sub>B</sub> |  |

| 007D02 <sub>H</sub> | Last event indicator register LEIR R/W |              | R/W                   | 000X0000 <sub>B</sub> |  |

| 007D03 <sub>H</sub> | Last event indicator register          | LLIIV        | 1000                  | XXXXXXXX <sub>B</sub> |  |

| 007D04 <sub>H</sub> | Receive/transmit error counter         | RTEC         | R                     | 00000000 <sub>B</sub> |  |

| 007D05 <sub>H</sub> | Neceive/transmit error counter         | KILO         | IX.                   | 00000000 <sub>B</sub> |  |

| 007D06 <sub>H</sub> | Bit timing register                    | BTR          | R/W                   | 11111111 <sub>B</sub> |  |

| 007D07 <sub>H</sub> | Dit tilling register                   | BIK          | 1000                  | X1111111 <sub>B</sub> |  |

| 007D08 <sub>H</sub> | IDE register                           | IDER         | R/W                   | $XXXXXXXX_B$          |  |

| 007D09 <sub>H</sub> | IDE register                           | IDEN         | 1000                  | XXXXXXXX <sub>B</sub> |  |

| 007D0A <sub>H</sub> | Transmit RTR register                  | TRTRR        | R/W                   | 00000000 <sub>B</sub> |  |

| 007D0B <sub>H</sub> | Transmit ix ix register                | IIVIIII      | 1000                  | 00000000 <sub>B</sub> |  |

| 007D0C <sub>H</sub> | Remote frame receive waiting           | RFWTR        | R/W                   | XXXXXXXX <sub>B</sub> |  |

| 007D0D <sub>H</sub> | register                               | IXI VVIIX    | 1000                  | XXXXXXXX <sub>B</sub> |  |

| 007D0E <sub>H</sub> | Transmit interrupt                     | TIER         | R/W                   | 00000000 <sub>B</sub> |  |

| 007D0F <sub>H</sub> | enable register                        | TILIX        | 1000                  | 00000000 <sub>B</sub> |  |

| 007D10 <sub>H</sub> |                                        |              |                       | XXXXXXXX <sub>B</sub> |  |

| 007D11 <sub>H</sub> | Acceptance mask                        | AMSR R/W     | XXXXXXXX <sub>B</sub> |                       |  |

| 007D12 <sub>H</sub> | select register                        | AWIOIX       | 1000                  | XXXXXXXX <sub>B</sub> |  |

| 007D13 <sub>H</sub> |                                        |              |                       | XXXXXXXX <sub>B</sub> |  |

| 007D14 <sub>H</sub> |                                        |              |                       | XXXXXXXX <sub>B</sub> |  |

| 007D15 <sub>H</sub> | Acceptance mask register 0             | AMR0         | R/W                   | XXXXXXXX <sub>B</sub> |  |

| 007D16 <sub>H</sub> | Acceptance mask register o             | Alviito      | 1000                  | XXXXXXXX <sub>B</sub> |  |

| 007D17 <sub>H</sub> |                                        |              |                       | XXXXXXXX <sub>B</sub> |  |

| 007D18 <sub>H</sub> |                                        |              |                       | XXXXXXXX <sub>B</sub> |  |

| 007D19 <sub>H</sub> | Acceptance mask register 1             | AMR1         | R/W                   | XXXXXXXX <sub>B</sub> |  |

| 007D1A <sub>H</sub> | Acceptance mask register i             | AIVIRI       | F/VV                  | XXXXXXXX <sub>B</sub> |  |

| 007D1B <sub>H</sub> |                                        |              |                       | $XXXXXXXX_B$          |  |

(T\_A = -40°C to +125°C,

$$V_{CC} = 5.0~V \pm 10\%,\, f_{CP} \le 24~MHz,\, V_{SS} = AV_{SS} = 0~V)$$

| Parameter                     | Cumbal           | Pin  |       | Value |     | Unit  | Remarks               |         |

|-------------------------------|------------------|------|-------|-------|-----|-------|-----------------------|---------|

| Faranietei                    | Symbol           | FIII | Min   | Тур   | Max | Oilit | Oilit                 | Remarks |

| Internal operating clock fre- | f <sub>CP</sub>  | 1    | 1.5   | 1     | 24  | MHz   | When using main clock |         |

| (machine clock)               | $f_{CPL}$        | -    | _     | 8.192 | 50  | kHz   | When using sub clock  |         |

| Internal operating clock cy-  | t <sub>CP</sub>  | Ī    | 41.67 | ı     | 666 | ns    | When using main clock |         |

| cle time<br>(machine clock)   | t <sub>CPL</sub> | _    | 20    | 122.1 | _   | μS    | When using sub clock  |         |

<sup>\*:</sup> The limitation is in the range of the clock frequency when PLL is used. Use within the range in graph of "· PLL guaranteed operation range External clock frequency and internal operation clock frequency".

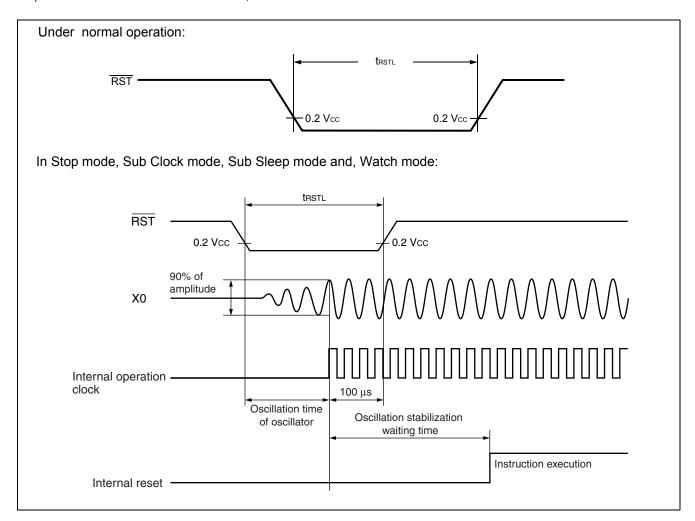

$^{\star}$ : Oscillation time of oscillator is the time that the amplitude reaches 90%. In the crystal oscillator, the oscillation time is between several ms to tens of ms. In ceramic oscillators, the oscillation time is between hundreds of  $\mu$ s to several ms. With an external clock, the oscillation time is 0 ms.

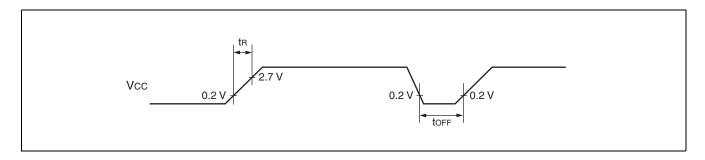

### 13.4.3 Power On Reset

(T\_A = -40 °C to +125 °C, V\_{CC} = 5.0 V

$$\pm$$

10%,  $f_{CP} \leq$  24 MHz,  $V_{SS} = AV_{SS} = 0$  V)

| Parameter          | Symbol           | Pin             | Condition | Va   | lue | Unit  | Remarks                     |

|--------------------|------------------|-----------------|-----------|------|-----|-------|-----------------------------|

| raiailletei        | Syllibol         | FIII            | Condition | Min  | Max | Oilit | Remarks                     |

| Power on rise time | t <sub>R</sub>   | V <sub>CC</sub> | _         | 0.05 | 30  | ms    |                             |

| Power off time     | t <sub>OFF</sub> | V <sub>CC</sub> | _         | 1    | _   | ms    | Waiting time until power-on |

## 13.4.6 Bus Timing (Write)

(T<sub>A</sub> = -40°C to +105°C, V<sub>CC</sub> = 5.0 V  $\pm$  10 %, V<sub>SS</sub> = 0.0 V, f<sub>CP</sub>  $\leq$  24 MHz)

| Parameter                                                           | Symbol            | Pin                             | Condition | Value                        | Unit |       |

|---------------------------------------------------------------------|-------------------|---------------------------------|-----------|------------------------------|------|-------|

| raidilletei                                                         | Symbol            | FIII                            | Condition | Min                          | Max  | Oilit |

| Valid address → $\overline{\text{WR}} \downarrow \text{time}$       | t <sub>AVWL</sub> | A21 to A16, AD15<br>to AD00, WR |           | t <sub>CP</sub> -15          | _    | ns    |

| WR pulse width                                                      | t <sub>WLWH</sub> | WR                              |           | (n*+3/2)t <sub>CP</sub> - 20 | _    | ns    |

| Valid data output $ ightarrow \overline{\mathrm{WR}} \uparrow$ time | t <sub>DVWH</sub> | AD15 to AD00, WR                |           | (n*+3/2)t <sub>CP</sub> - 20 | _    | ns    |

| $\overline{WR} \uparrow \to Data$ hold time                         | t <sub>WHDX</sub> | AD15 to AD00, WR                | _         | 15                           | _    | ns    |

| $\overline{WR} \uparrow \to Address$ valid time                     | t <sub>WHAX</sub> | A21 to A16, WR                  |           | t <sub>CP</sub> /2 - 10      | _    | ns    |

| $\overline{WR} \uparrow \to ALE \uparrow time$                      | t <sub>WHLH</sub> | WR, ALE                         |           | t <sub>CP</sub> /2 - 15      | _    | ns    |

| $\overline{WR} \downarrow \to CLK \uparrow time$                    | t <sub>WLCH</sub> | WR, CLK                         |           | t <sub>CP</sub> /2 - 15      | _    | ns    |

<sup>\*:</sup> Number of ready cycles

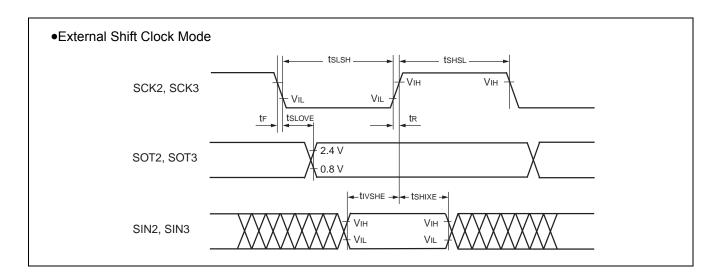

## ■ Bit setting: ESCR:SCES = 1, ECCR:SCDE = 0

(T\_A =  $-40^{\circ}C$  to  $+125^{\circ}C,~V_{CC}=5.0~V\pm10\%,~f_{CP}\leq24$  MHz,  $V_{SS}=0~V)$

| Parameter                                         | Symbol             | Pin                      | Condition                                                           | V                                  | Unit                   |       |  |

|---------------------------------------------------|--------------------|--------------------------|---------------------------------------------------------------------|------------------------------------|------------------------|-------|--|

| Parameter                                         | Зушьог             | PIII                     | Condition                                                           | Min                                | Max                    | Oilit |  |

| Serial clock cycle time                           | tscyc              | SCK2, SCK3               |                                                                     | 5 t <sub>CP</sub>                  | =                      | ns    |  |

| SCK $\uparrow \rightarrow$ SOT delay time         | t <sub>SHOVI</sub> | SCK2, SCK3<br>SOT2, SOT3 | Internal shift clock                                                | -50                                | +50                    | ns    |  |

| Valid SIN → SCK $\downarrow$                      | t <sub>IVSLI</sub> | SCK2, SCK3<br>SIN2, SIN3 | mode output pins are CL = 80 pF + 1 TTL.                            | t <sub>CP</sub> + 80               | -                      | ns    |  |

| $SCK \downarrow \to Valid \; SIN \; hold \; time$ | t <sub>SLIXI</sub> | SCK2, SCK3<br>SIN2, SIN3 |                                                                     | 0                                  | -                      | ns    |  |

| Serial clock "H" pulse width                      | t <sub>SHSL</sub>  | SCK2, SCK3               |                                                                     | 3 t <sub>CP</sub> - t <sub>R</sub> | =                      | ns    |  |

| Serial clock "L" pulse width                      | t <sub>SLSH</sub>  | SCK2, SCK3               |                                                                     | t <sub>CP</sub> + 10               | =                      | ns    |  |

| SCK $\uparrow \rightarrow$ SOT delay time         | t <sub>SHOVE</sub> | SCK2, SCK3<br>SOT2, SOT3 |                                                                     | =                                  | 2 t <sub>CP</sub> + 60 | ns    |  |

| Valid SIN $\rightarrow$ SCK $↓$                   | t <sub>IVSLE</sub> | SCK2, SCK3<br>SIN2, SIN3 | External shift clock<br>mode output pins are<br>CL = 80 pF + 1 TTL. | 30                                 | =                      | ns    |  |

| $SCK \downarrow \to Valid \; SIN \; hold \; time$ | t <sub>SLIXE</sub> | SCK2, SCK3<br>SIN2, SIN3 |                                                                     | t <sub>CP</sub> + 30               | -                      | ns    |  |

| SCK fall time                                     | t <sub>F</sub>     | SCK2, SCK3               | ]                                                                   | -                                  | 10                     | ns    |  |

| SCK rise time                                     | t <sub>R</sub>     | SCK2, SCK3               | ]                                                                   | _                                  | 10                     | ns    |  |

Notes :  $\, \bullet \, C_L$  is load capacity value of pins when testing.

$\bullet$   $t_{\mbox{\footnotesize{CP}}}$  is internal operating clock cycle time (machine clock) . Refer to "Clock Timing".

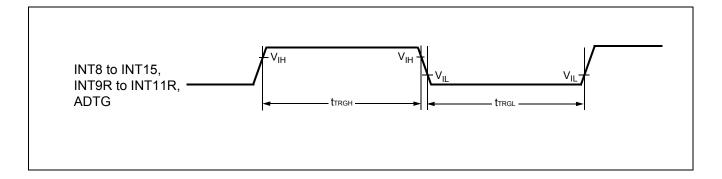

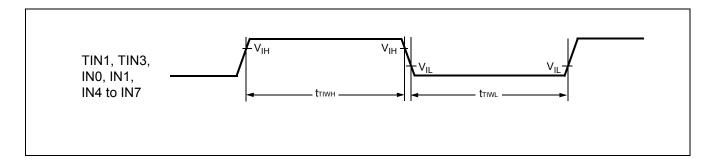

## 13.4.10 Trigger Input Timing

(T\_A = -40 °C to +125 °C, V\_{CC} = 5.0 V  $\pm$  10%, f\_{CP}  $\leq$  24 MHz, V\_{SS} = AV\_{SS} = 0 V)

| Parameter         | Symbol                                 | Pin                                     | Condition | Va                | Unit |     |

|-------------------|----------------------------------------|-----------------------------------------|-----------|-------------------|------|-----|

| raiailletei       | eter Symbol Pili                       |                                         | Condition | Min               |      | Max |

| Input pulse width | t <sub>TRGH</sub><br>t <sub>TRGL</sub> | INT8 to INT15,<br>INT9R to INT11R, ADTG | _         | 5 t <sub>CP</sub> | _    | ns  |

## 13.4.11 Timer Related Resource Input Timing

$(T_A = -40^{\circ}C \text{ to } +125^{\circ}C, V_{CC} = 5.0 \text{ V} \pm 10\%, f_{CP} \le 24 \text{ MHz}, V_{SS} = AV_{SS} = 0 \text{ V})$

|                    |                   | (1A 10 0 0 1 1 1 0 0 ) | 00 -      | · • / •, ·CF = -  |     | 33    | _ |

|--------------------|-------------------|------------------------|-----------|-------------------|-----|-------|---|

| Parameter          | Symbol            | Pin                    | Condition |                   |     | Unit  |   |

| raiailietei        | Symbol            |                        | Condition | Min               | Max | Oilit |   |

| Input pulse width  | t <sub>TIWH</sub> | TIN1, TIN3,IN0, IN1,   | _         | 1 t               | _   | ns    |   |

| input puise wiatii | t <sub>TIWL</sub> | IN4 to IN7             |           | 4 t <sub>CP</sub> |     | 113   |   |

## 13.4.12 Timer Related Resource Output Timing

(T\_A = -40°C to +125°C, V\_{CC} = 5.0 V  $\pm$  10%, f\_{CP}  $\leq$  24 MHz, V\_{SS} = AV\_{SS} = 0 V)

| Parameter                                      | Symbol          | Pin                                     | Condition | Value |     | Unit  |  |

|------------------------------------------------|-----------------|-----------------------------------------|-----------|-------|-----|-------|--|

| raidilietei                                    | Syllibol        | r III                                   | Condition | Min   | Max | Oilit |  |

| $CLK \uparrow \rightarrow T_{OUT}$ change time | t <sub>TO</sub> | TOT1, TOT3, PPG4, PPG6,<br>PPG8 to PPGF | _         | 30    | _   | ns    |  |

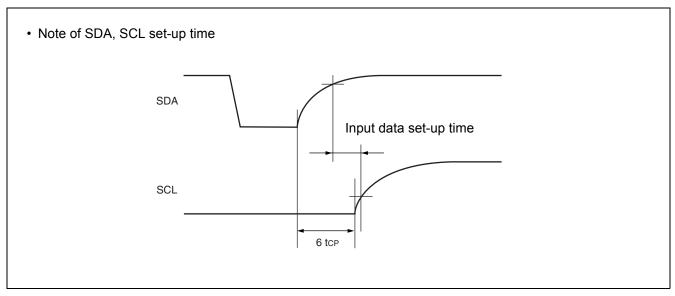

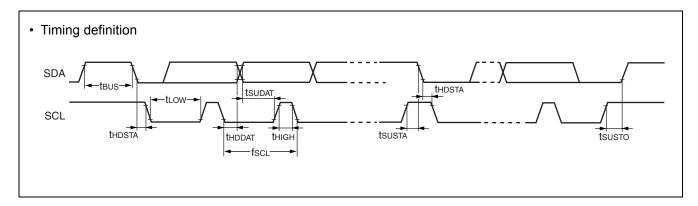

Note: The rating of the input data set-up time in the device connected to the bus cannot be satisfied depending on the load capacitance or pull-up resistor.

Be sure to adjust the pull-up resistor of SDA and SCL if the rating of the input data set-up time cannot be satisfied.

### 13.7 Flash Memory Program/Erase Characteristics

### ■ Dual Operation Flash Memory

| Parameter                               | Conditions              |       | Value |      | Unit  | Remarks                                          |  |

|-----------------------------------------|-------------------------|-------|-------|------|-------|--------------------------------------------------|--|

| Parameter                               | Conditions              | Min   | Тур   | Max  | Ullit | Remarks                                          |  |

| Sector erase time<br>(4 Kbytes sector)  |                         | _     | 0.2   | 0.5  | s     | Excludes programming prior to erasure            |  |

| Sector erase time<br>(16 Kbytes sector) | T <sub>A</sub> = +25°C  | _     | 0.5   | 7.5  | S     | Excludes programming prior to erasure            |  |

| Chip erase time                         | V <sub>CC</sub> = 5.0 V | _     | 4.6   | _    | S     | Excludes programming prior to erasure            |  |

| Word (16-bit width) programming time    |                         | _     | 64    | 3600 | μS    | Except for the overhead time of the system level |  |

| Program/Erase cycle                     | _                       | 10000 | _     | _    | cycle |                                                  |  |

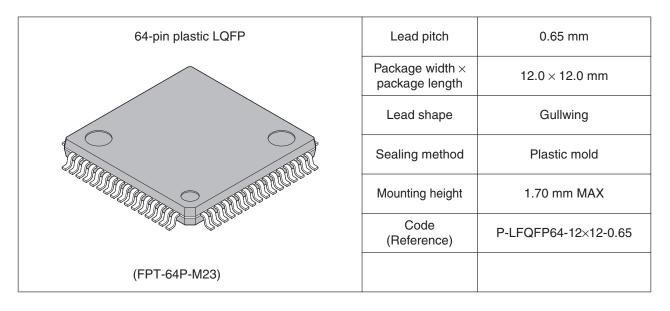

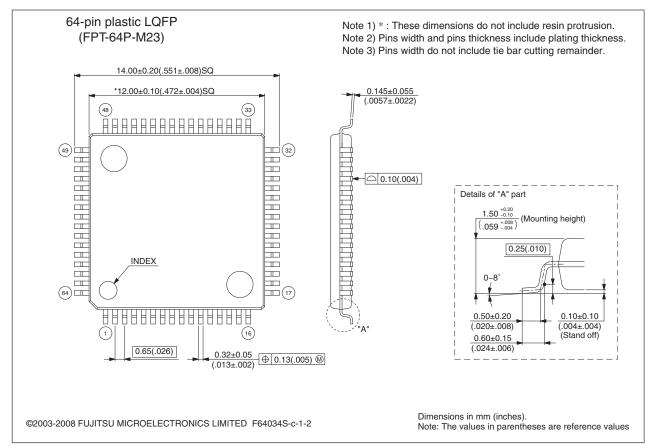

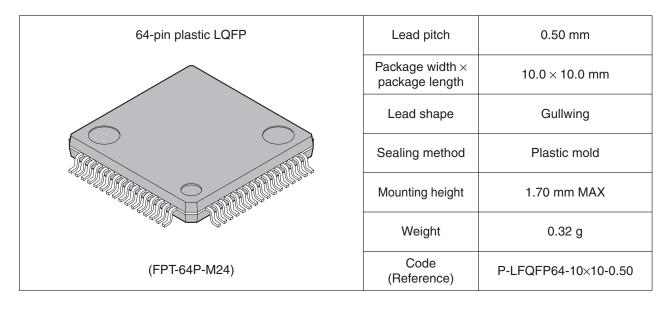

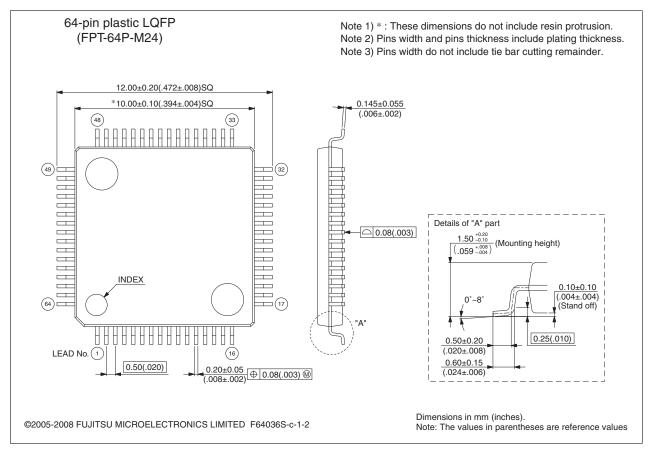

### 14.1 Package Dimensions