Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                       |

|----------------------------|-----------------------------------------------------------------------|

| Product Status             | Obsolete                                                              |

| Core Processor             | ST7                                                                   |

| Core Size                  | 8-Bit                                                                 |

| Speed                      | 8MHz                                                                  |

| Connectivity               | -                                                                     |

| Peripherals                | LVD, POR, PWM, WDT                                                    |

| Number of I/O              | 5                                                                     |

| Program Memory Size        | 1KB (1K x 8)                                                          |

| Program Memory Type        | FLASH                                                                 |

| EEPROM Size                | -                                                                     |

| RAM Size                   | 128 x 8                                                               |

| Voltage - Supply (Vcc/Vdd) | 2.4V ~ 5.5V                                                           |

| Data Converters            | -                                                                     |

| Oscillator Type            | Internal                                                              |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                     |

| Mounting Type              | Through Hole                                                          |

| Package / Case             | 8-DIP (0.300", 7.62mm)                                                |

| Supplier Device Package    | -                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/st7fliteus2b6 |

# **Contents**

| 1     | Intro | luction                                    | 1   |

|-------|-------|--------------------------------------------|-----|

| 2     | Pin d | escription                                 | 2   |

| 3     | Regis | ster and memory map                        | 5   |

| 4     | Flash | program memory1                            | 8   |

|       | 4.1   | Introduction                               | 8   |

|       | 4.2   | Main features                              | 8   |

|       | 4.3   | Programming modes                          | 8   |

|       |       | 4.3.1 In-circuit programming (ICP)         | 8   |

|       |       | 4.3.2 In application programming (IAP)     | 9   |

|       | 4.4   | I <sup>2</sup> C interface                 | 9   |

|       | 4.5   | Memory protection                          | 0   |

|       |       | 4.5.1 Readout protection                   | 0   |

|       |       | 4.5.2Flash Write/Erase protection          | 1:1 |

|       | 4.6   | Related documentation                      | 1   |

|       | 4.7   | Register description                       | 2   |

|       |       | 4.7.1 Flash Control/Status register (FCSR) | 2   |

| 5     | Cent  | ع، processing unit                         | 3   |

|       | 5.0   | Introduction                               |     |

|       | 5.2   | Main features                              |     |

| SO,   | 5.3   | CPU registers                              |     |

| , O   | .0.   | 5.3.1 Accumulator (A)                      |     |

|       | Silv  | 5.3.2 Index registers (X and Y)            |     |

| 1050l |       | 5.3.3 Program counter (PC)                 |     |

| 102   |       | 5.3.4 Condition Code register (CC)         | 4   |

|       |       | 5.3.5 Stack Pointer (SP)                   | :6  |

| 6     | Supp  | ly, reset and clock management2            | 8   |

|       | 6.1   | Main features 2                            | 8   |

|       | 6.2   | Internal RC oscillator adjustment          | 8   |

|      | 6.3    | Register description                                        | 30 |

|------|--------|-------------------------------------------------------------|----|

|      |        | 6.3.1 Main Clock Control/Status register (MCCSR)            | 30 |

|      |        | 6.3.2 RC Control register (RCCR)                            | 31 |

|      |        | 6.3.3 System Integrity (SI) Control/status register (SICSR) | 31 |

|      |        | 6.3.4 AVD Threshold Selection register (AVDTHCR)            | 32 |

|      |        | 6.3.5 Clock Controller Control/Status register (CKCNTCSR)   | 32 |

|      | 6.4    | Reset sequence manager (RSM)                                | 35 |

|      |        | 6.4.1 Introduction                                          | 35 |

|      |        | 6.4.2 Asynchronous external RESET pin                       | 36 |

|      |        | 6.4.3 External Power-on reset                               |    |

|      |        | 6.4.4 Internal low voltage detector (LVD) reset             |    |

|      |        | 6.4.5 Internal watchdog reset                               | 37 |

|      | 6.5    | Register description                                        | 37 |

|      |        | 6.5.1 Multiplexed I/O Reset Control register 1 (MUCCh1)     | 37 |

|      |        | 6.5.2 Multiplexed I/O Reset Control registe: ( (NUXCR0)     | 37 |

| _    |        |                                                             |    |

| 7    | Interr | upts                                                        |    |

|      | 7.1    | Non maskable software interrupt                             | 39 |

|      | 7.2    | External interrupts                                         | 40 |

|      | 7.3    | Peripheral interrupts                                       | 40 |

|      |        | 7.3.1 External Interrupt Control register 1 (EICR1)         | 41 |

|      |        | 7.3.2 External Interrupt Control register 2 (EICR2)         | 42 |

|      | 7.4    | Cystem integrity management (SI)                            | 43 |

|      |        | 7.4.1 Low voltage detector (LVD)                            | 43 |

| 10   |        | 7.4.2 Auxiliary voltage detector (AVD)                      | 45 |

| cO// |        | 7.4.3 Low power modes                                       | 46 |

| 03   |        | 7.4.4 Register description                                  | 46 |

|      | 30     |                                                             |    |

| 8    |        | r saving modes                                              |    |

| 5    | 8.1    | Introduction                                                | 48 |

|      | 8.2    | Slow mode                                                   | 49 |

|      | 8.3    | Wait mode                                                   | 49 |

|      | 8.4    | Active-halt and Halt modes                                  | 50 |

|      |        | 8.4.1 Active-halt mode                                      | 51 |

|      |        | 8.4.2 Halt mode                                             | 52 |

|      | 8.5    | Auto-wakeup from Halt mode                                  | 54 |

|      |        |                                                             |    |

| Instru | ction se                                       | et                                                                                                                                                                                                                                                                                                                                             | . 84                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|--------|------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 11.1   | ST7 add                                        | lressing modes                                                                                                                                                                                                                                                                                                                                 | . 84                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|        | 11.1.1                                         | Inherent mode                                                                                                                                                                                                                                                                                                                                  | 85                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|        | 11.1.2                                         | Immediate                                                                                                                                                                                                                                                                                                                                      | 86                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|        | 11.1.3                                         | Direct                                                                                                                                                                                                                                                                                                                                         | 86                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|        | 11.1.4                                         | Indexed mode (no offset, short, long)                                                                                                                                                                                                                                                                                                          | 86                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|        | 11.1.5                                         | Indirect modes (short, long)                                                                                                                                                                                                                                                                                                                   | 87                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|        | 11.1.6                                         | Indirect indexed modes (short, long)                                                                                                                                                                                                                                                                                                           | 87                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|        | 11.1.7                                         | Relative modes (direct, indirect)                                                                                                                                                                                                                                                                                                              | 88                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 11.2   | Instruction                                    | on groups                                                                                                                                                                                                                                                                                                                                      | 88                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|        | 11.2.1                                         | Illegal opcode reset                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Electr | ical cha                                       | racteristics                                                                                                                                                                                                                                                                                                                                   | . 92                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 12.1   | Paramet                                        | er conditions                                                                                                                                                                                                                                                                                                                                  | . 92                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|        | 12.1.1                                         | Minimum and maximum values                                                                                                                                                                                                                                                                                                                     | 92                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|        | 12.1.2                                         | Typical values                                                                                                                                                                                                                                                                                                                                 | 92                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|        | 12.1.3                                         | Typical curves                                                                                                                                                                                                                                                                                                                                 | 92                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|        | 12.1.4                                         | Loading capacitor                                                                                                                                                                                                                                                                                                                              | 92                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|        | 12.1.5                                         |                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 12.2   | Absolute                                       | e maximົນເຕັງຈາings                                                                                                                                                                                                                                                                                                                            | . 93                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 12.3   | Operatir                                       | ng conditions                                                                                                                                                                                                                                                                                                                                  | . 94                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|        | 12.3.1                                         | General operating conditions                                                                                                                                                                                                                                                                                                                   | 94                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|        | 72.3.2                                         | Operating conditions with low voltage detector (LVD)                                                                                                                                                                                                                                                                                           | 95                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|        | 12.3.3                                         | Auxiliary voltage detector (AVD) thresholds                                                                                                                                                                                                                                                                                                    | 96                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 10     | 12.3.4                                         | Internal RC oscillator                                                                                                                                                                                                                                                                                                                         | 96                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 12.4   | Supply of                                      | current characteristics                                                                                                                                                                                                                                                                                                                        | . 99                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|        | 12.4.1                                         | Supply current                                                                                                                                                                                                                                                                                                                                 | 99                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 94     | 12.4.2                                         | Internal RC oscillator supply current characteristics                                                                                                                                                                                                                                                                                          | . 100                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 3      | 12.4.3                                         | On-chip peripherals                                                                                                                                                                                                                                                                                                                            | . 103                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 12.5   | Clock ar                                       | nd timing characteristics                                                                                                                                                                                                                                                                                                                      | 103                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 12.6   | Memory                                         | characteristics                                                                                                                                                                                                                                                                                                                                | 104                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 12.7   | EMC ch                                         | aracteristics                                                                                                                                                                                                                                                                                                                                  | 105                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|        | 12.7.1                                         | Functional EMS (electromagnetic susceptibility)                                                                                                                                                                                                                                                                                                | . 105                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|        | 12.7.2                                         | Electromagnetic Interference (EMI)                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|        | 12.7.3                                         | Absolute maximum ratings (electrical sensitivity)                                                                                                                                                                                                                                                                                              | . 106                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 12.8   | I/O port                                       | pin characteristics                                                                                                                                                                                                                                                                                                                            | 108                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|        | 11.1<br>11.2<br>Electr<br>12.1<br>12.2<br>12.3 | 11.1 ST7 add 11.1.1 11.1.2 11.1.3 11.1.4 11.1.5 11.1.6 11.1.7 11.2 Instruction 11.2.1  Electrical characteristics 12.1 Parameteristics 12.1.1 12.1.2 12.1.3 12.1.4 12.1.5 12.2 Absolute 12.3 Operation 12.3.1 12.3.2 12.3.3 12.3.4 12.4 Supply of 12.4.1 12.4.2 12.4.3 12.5 Clock ar 12.6 Memory 12.7 EMC characteristics 12.7.1 12.7.2 12.7.3 | 11.1.1 Inherent mode 11.1.2 Immediate 11.1.3 Direct 11.1.4 Indexed mode (no offset, short, long) 11.1.5 Indirect modes (short, long) 11.1.6 Indirect indexed modes (short, long) 11.1.7 Relative modes (direct, indirect) 11.2 Instruction groups 11.2.1 Illegal opcode reset  Electrical characteristics 12.1 Parameter conditions 12.1.1 Minimum and maximum values 12.1.2 Typical values 12.1.3 Typical curves 12.1.4 Loading capacitor 12.1.5 Pin input voltage 12.2 Absolute maxim un ratings 12.3 Operating or of nions 12.3.1 General operating conditions 12.3.2 Operating conditions with low voltage detector (LVD) 12.3.3 Auxiliary voltage detector (AVD) thresholds 12.3.4 Internal RC oscillator 12.4.5 Supply current characteristics 12.4.1 Supply current 12.4.2 Internal RC oscillator supply current characteristics 12.4.3 On-chip peripherals 12.5 Clock and timing characteristics 12.6 Memory characteristics 12.7 EMC characteristics 12.7.1 Functional EMS (electromagnetic susceptibility) 12.7.2 Electromagnetic Interference (EMI) 12.7.3 Absolute maximum ratings (electrical sensitivity) |

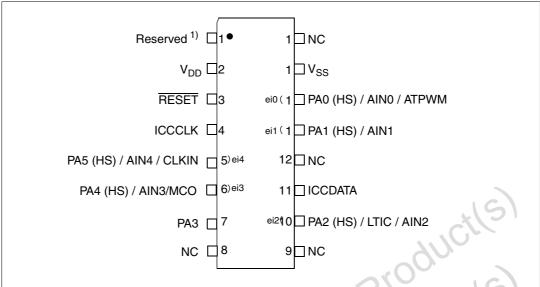

Figure 4. 16-pin package pinout

- Jedon d. alad p. pin. It is not nutiplexed any change on the section A3 functional fire and the section and the section and the section and the section are section as the section are The differences versus the 8-pin packages are listed below:

The IPC signals (ICCCLK and ICCDATA) are mapped on docated pins.

The RESET signal is mapped on a dedicated pin. It is not multiplexed with PA3.

PA3 pin is always configured as output. Any change on additional tiplexed IO reset control registers (MUXCR1 and MUXCR2) will have no effect on PA3 functionality. Refer to Section 6.5: Register description on

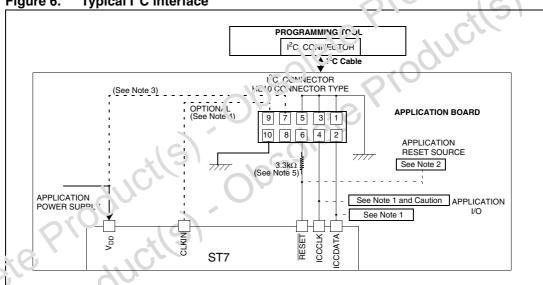

Pin 9 has to be connected to the CLKIN pin of the ST7 when  $I^2C$  mode is selected with option bytes disabled (35-pulse  $I^2C$  entry mode). When option bytes are enabled (38-pulse  $I^2C$  entry mode), the internal RC clock (internal RC or AWU RC) is forced. If internal RC is selected in the option byte, the internal RC is provided. If AWU RC or external clock is selected, the AWU RC oscillator is provided.

A serial resistor must be connected to  $I^2C$  connector pin 6 in order to prevent contention on PA3/RESET pin. Contention may occur if a tool forces a state on RESET pin while PA3 pin forces the opposite state in output mode. The resistor value is defined to limit the current below 2 mA at 5 V. If PA3 is used as output push-pull, then the application must be switched off to allow the tool to take control of the RESET pin (PA3). To allow the programming tool to drive the RESET pin below  $V_{IL}$ , special care must also be taken when a pull-up is placed on PA3 for application reasons.

#### Caution:

During normal operation, ICCCLK pin must be pulled- up, internally or externally (external pull-up of 10 k $\Omega$  mandatory in noisy environment). This is to avoid entering I<sup>2</sup>C mode unexpectedly during a reset. In the application, even if the pin is configured as output, any reset will put it back in input pull-up.

Figure 6. Typical I<sup>2</sup>C interface

# 4.5 Memory protection

There are two different types of memory protection: readout protection and Write/Erase Protection which can be applied individually.

## 4.5.1 Readout protection

Readout protection, when selected provides a protection against program memory content extraction and against write access to Flash memory. Even if no protection can be considered as totally unbreakable, the feature provides a very high level of protection for a general purpose microcontroller. Program memory is protected.

#### Central processing unit 5

#### 5.1 Introduction

This CPU has a full 8-bit architecture and contains six internal registers allowing efficient 8bit data manipulation.

#### 5.2 Main features

- 63 basic instructions

- Fast 8-bit by 8-bit multiply

- 17 main addressing modes

- Two 8-bit index registers

- 16-bit stack pointer

- Low power modes

- Maskable hardware interrupts

- Non-maskable software interrupt

#### 5.3 **CPU** registers

sent in \* The six CPU registers shown in Figu. 9 7 are not present in the memory mapping and are accessed by specific instructions.

#### 5.3.1 Accumulator (A)

The Accumulato: is an S-bit general purpose register used to hold operands and the results of the arithmetic and logic calculations and to manipulate data.

#### 5.3.2 Index registers (X and Y)

in indexed addressing modes, these 8-bit registers are used to create either effective addresses or temporary storage areas for data manipulation. (The cross-assembler generates a precede instruction (PRE) to indicate that the following instruction refers to the Y register.)

The Y register is not affected by the interrupt automatic procedures (not pushed to and popped from the stack).

## **Program counter (PC)**

The program counter is a 16-bit register containing the address of the next instruction to be executed by the CPU. It is made of two 8-bit registers PCL (program counter low which is the LSB) and PCH (program counter high which is the MSB).

## Bit 7:5 Set to '1'

#### Bit 4 H Half carry

This bit is set by hardware when a carry occurs between bits 3 and 4 of the ALU during an ADD or ADC instruction. It is reset by hardware during the same instructions.

0: No half carry has occurred.

1: A half carry has occurred.

This bit is tested using the JRH or JRNH instruction. The H bit is useful in BCD arithmetic subroutines.

#### Bit 3 I Interrupt mask

This bit is set by hardware when entering in interrupt or by software to disable all interrupts except the TRAP software interrupt. This bit is cleared by software.

0: Interrupts are enabled.

1: Interrupts are disabled.

This bit is controlled by the RIM, SIM and IRET instructions and is tested by the JRM and JRNM instructions.

Note: Interrupts requested while I is set are latched and our be processed when I is cleared. By default an interrupt routine is not interruptible because the I bit is set by hardware at the start of the routine and reset by the IRET instruction at the end of the routine. It the I bit is cleared by software in the interrupt routine, pending interrupts are serviced regardless of the priority level of the current interrup, ro nine.

#### Bit 2 N Negative

This bit is set and cleared by nardware. It is representative of the result sign of the last arithmetic, logical or data manipulation. It is a copy of the 7<sup>th</sup> bit of the result.

0: The result of the last operation is positive or null.

1: The result of the last operation is negative

(that is, the most significant bit is a logic 1).

This pit is accessed by the JRMI and JRPL instructions.

### 2 Zero

This bit is set and cleared by hardware. This bit indicates that the result of the last arithmetic, logical or data manipulation is zero.

0: The result of the last operation is different from zero.

1: The result of the last operation is zero.

This bit is accessed by the JREQ and JRNE test instructions.

# Obsolete Pre Paro

This bit is set and cleared by hardware and software. It indicates an overflow or an underflow has occurred during the last arithmetic operation.

0: No overflow or underflow has occurred.

1: An overflow or underflow has occurred.

This bit is driven by the SCF and RCF instructions and tested by the JRC and JRNC instructions. It is also affected by the "bit test and branch", shift and rotate instructions.

This 16-bit register is read/write by software but can be written only once between two reset events. It is cleared by hardware after a reset; When both MUXCR0 and MUXCR1 registers are at 00h, the multiplexed PA3/RESET pin will act as RESET. To configure this pin as output (Port A3), write 55h to MUXCR0 and AAh to MUXCR1.

These registers are one-time writable only.

- To configure PA3 as general purpose output:

After power-on / reset, the application program has to configure the I/O port by writing to these registers as described above. Once the pin is configured as an I/O output, it cannot be changed back to a reset pin by the application code.

- To configure PA3 as RESET:

An internally generated reset (such as POR, LVD, WDG, illegal opcode) will clear the two registers and the pin will act again as a reset function. Otherwise, a power-down is required to put the pin back in reset configuration.

Table 8. Multiplexed IO register map and reset values

| MUXCR0<br>reset<br>value<br>MUXCR1<br>reset<br>value | MIR7<br>0 | MIR6<br>0  | MIR5<br>0  | MIR4<br>0  | MIR3       | MIR2       | MIR1      | MIR0                       |

|------------------------------------------------------|-----------|------------|------------|------------|------------|------------|-----------|----------------------------|

| reset                                                |           |            |            |            | U          | 0          | 0         | 0                          |

|                                                      | 0         | MIR14<br>0 | MIR12<br>0 | мIR12<br>0 | MIR11<br>0 | MIR10<br>0 | MIR9<br>0 | MIR8<br>0                  |

|                                                      | *16       |            |            | 0/8        |            |            |           |                            |

| OGIU                                                 | CIL       | ,          | 2/02       | 7          |            |            |           |                            |

| (U                                                   | cile      |            |            |            |            |            |           |                            |

| LOQIC                                                | <i>r</i>  |            |            |            |            |            |           |                            |

|                                                      |           |            |            |            |            |            |           |                            |

|                                                      |           |            |            |            |            |            |           |                            |

|                                                      |           |            |            |            |            |            |           | coduci(s) obsoler oduci(s) |

# 7 Interrupts

The ST7 core may be interrupted by one of two different methods: Maskable hardware interrupts as listed in the "interrupt mapping" table and a non-maskable software interrupt (TRAP). The Interrupt processing flowchart is shown in *Figure 14*.

The maskable interrupts must be enabled by clearing the I bit in order to be serviced. However, disabled interrupts may be latched and processed when they are enabled (see external interrupts subsection).

Note: After reset, all interrupts are disabled.

When an interrupt has to be serviced:

- Normal processing is suspended at the end of the current instruction execution.

- The PC, X, A and CC registers are saved onto the stack.

- The I bit of the CC register is set to prevent additional interrupts.

- The PC is then loaded with the interrupt vector of the interrupt to service and the first instruction of the interrupt service routine is fetched (refer to the Interrupt Mapping table for vector addresses).

The interrupt service routine should finish with the IRE Transfruction which causes the contents of the saved registers to be recovered from the stack.

Note: As a consequence of the IRET instruction, the I bit is cleared and the main program resumes.

## **Priority management**

By default, a servicing interrupt cannot be interrupted because the I bit is set by hardware entering in interrupt routine

In the case when several interrupts are simultaneously pending, an hardware priority defines which one will be serviced first (see *Table 9: Interrupt mapping*).

## Interrupts and low power mode

All in errupts allow the processor to leave the Wait low power mode. Only external and specifically mentioned interrupts allow the processor to leave the Halt low power mode (refer to the "Exit from Halt" column in *Table 9: Interrupt mapping*).

# 7.1 Non maskable software interrupt

This interrupt is entered when the TRAP instruction is executed regardless of the state of the I bit. It is serviced according to the flowchart in *Figure 14*.

#### Halt mode recommendations

- Make sure that an external event is available to wakeup the microcontroller from Halt mode.

- When using an external interrupt to wakeup the microcontroller, reinitialize the

corresponding I/O as "Input Pull-up with Interrupt" before executing the HALT

instruction. The main reason for this is that the I/O may be wrongly configured due to

external interference or by an unforeseen logical condition.

- For the same reason, reinitialize the level sensitiveness of each external interrupt as a precautionary measure.

- The opcode for the HALT instruction is 0x8E. To avoid an unexpected HALT instruction due to a program counter failure, it is advised to clear all occurrences of the data value 0x8E from memory. For example, avoid defining a constant in ROM with the value 0x8E.

- As the HALT instruction clears the I bit in the CC register to allow interrupts, the user may choose to clear all pending interrupt bits before executing the HALT instruction. This avoids entering other peripheral interrupt routines after executing the external interrupt routine corresponding to the wakeup event (reset or external interrupt).

# 8.5 Auto-wakeup from Halt mode

Auto-wakeup from Halt (AWUFH) mode is similar to Halt mode with the addition of a specific internal RC oscillator for wakeup (Auto-wakeup from Halt oscillator) which replaces the main clock which was active before entering Halt mode. Compared to Active-halt mode, AWUFH has lower power consumption (the main clock is not kept running), but there is no accurate realtime clock available.

It is entered by executing the !ALT instruction when the AWUEN bit in the AWUCSR register has been set.

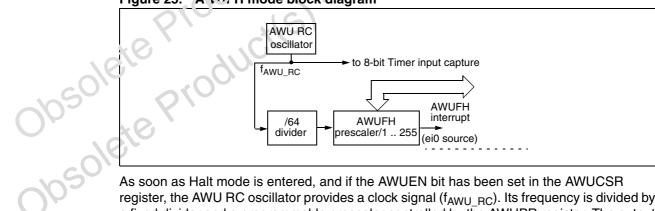

Figure 25. ANUFH mode block diagram

As soon as Halt mode is entered, and if the AWUEN bit has been set in the AWUCSR register, the AWU RC oscillator provides a clock signal ( $f_{AWU\_RC}$ ). Its frequency is divided by a fixed divider and a programmable prescaler controlled by the AWUPR register. The output of this prescaler provides the delay time. When the delay has elapsed, the following actions are performed:

- The AWUF flag is set by hardware,

- An interrupt wakes-up the MCU from Halt mode,

- The main oscillator is immediately turned on and the 64 CPU cycle delay is used to stabilize it.

After this startup delay, the CPU resumes operation by servicing the AWUFH interrupt. The AWU flag and its associated interrupt are cleared by software reading the AWUCSR register.

To compensate for any frequency dispersion of the AWU RC oscillator, it can be calibrated by measuring the clock frequency  $f_{AWU\_RC}$  and then calculating the right prescaler value. Measurement mode is enabled by setting the AWUM bit in the AWUCSR register in Run mode. This connects  $f_{AWU\_RC}$  to the input capture of the 8-bit lite timer, allowing the  $f_{AWU\_RC}$  to be measured using the main oscillator clock as a reference timebase.

### Similarities with Halt mode

The following AWUFH mode behavior is the same as normal Halt mode:

- The MCU can exit AWUFH mode by means of any interrupt with exit from Halt capability or a reset (see Section 8.4: Active-halt and Halt modes).

- When entering AWUFH mode, the I bit in the CC register is forced to 0 to enable interrupts. Therefore, if an interrupt is pending, the MCU wakes up immediately.

- In AWUFH mode, the main oscillator is turned off causing all internal processing to be stopped, including the operation of the on-chip peripherals. Note of the peripherals are clocked except those which get their clock supply from another clock generator (such as an external or auxiliary oscillator like the AWU oscillator).

- The compatibility of watchdog operation with AVULTH mode is configured by the WDGHALT option bit in the option byte. Depending on this setting, the HALT instruction when executed while the watchdog syst in a enabled, can generate a watchdog reset.

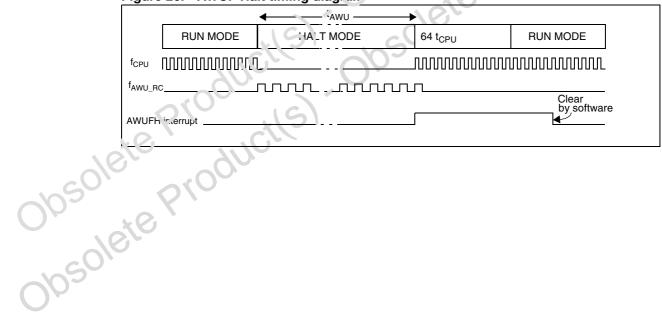

Figure 26. AWUF Halt timing diagram

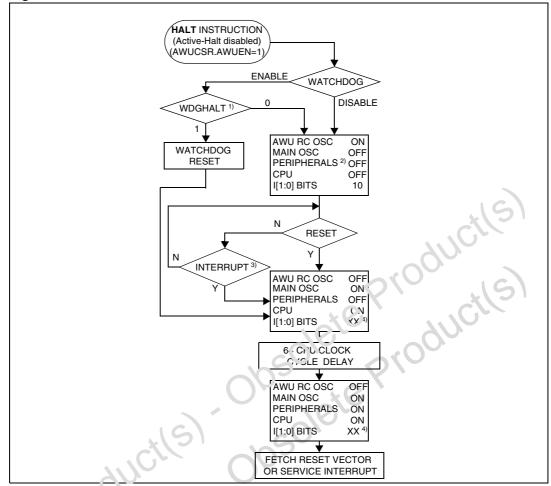

Figure 27. AWUFH mode flowchart

- WDGHALT is an option bit. See option byte section for more details.

- Per pheral clocked with an external clock source can still be active.

- Only an AWUFH interrupt and some specific interrupts can exit the MCU from Halt mode (such as external int errupt). Refer to Table 9: Interrupt mapping for more details.

- Only a.

interrup