Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                         |

|----------------------------|-------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                |

| Core Processor             | ST7                                                                     |

| Core Size                  | 8-Bit                                                                   |

| Speed                      | 8MHz                                                                    |

| Connectivity               | -                                                                       |

| Peripherals                | LVD, POR, PWM, WDT                                                      |

| Number of I/O              | 5                                                                       |

| Program Memory Size        | 1KB (1K x 8)                                                            |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | -                                                                       |

| RAM Size                   | 128 x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 2.4V ~ 5.5V                                                             |

| Data Converters            | -                                                                       |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                      |

| Mounting Type              | Surface Mount                                                           |

| Package / Case             | 8-SOIC (0.154", 3.90mm Width)                                           |

| Supplier Device Package    | 8-SOIC                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/st7fliteus2m3tr |

|      | 6.3    | Register description                                        | 30 |

|------|--------|-------------------------------------------------------------|----|

|      |        | 6.3.1 Main Clock Control/Status register (MCCSR)            | 30 |

|      |        | 6.3.2 RC Control register (RCCR)                            | 31 |

|      |        | 6.3.3 System Integrity (SI) Control/status register (SICSR) | 31 |

|      |        | 6.3.4 AVD Threshold Selection register (AVDTHCR)            | 32 |

|      |        | 6.3.5 Clock Controller Control/Status register (CKCNTCSR)   | 32 |

|      | 6.4    | Reset sequence manager (RSM)                                | 35 |

|      |        | 6.4.1 Introduction                                          | 35 |

|      |        | 6.4.2 Asynchronous external RESET pin                       | 36 |

|      |        | 6.4.3 External Power-on reset                               |    |

|      |        | 6.4.4 Internal low voltage detector (LVD) reset             |    |

|      |        | 6.4.5 Internal watchdog reset                               | 37 |

|      | 6.5    | Register description                                        | 37 |

|      |        | 6.5.1 Multiplexed I/O Reset Control register 1 (MUXCh1)     | 37 |

|      |        | 6.5.2 Multiplexed I/O Reset Control registe: ( (NUXCR0)     | 37 |

| _    |        |                                                             |    |

| 7    | Interr | upts                                                        |    |

|      | 7.1    | Non maskable software interrupt                             | 39 |

|      | 7.2    | External interrupts                                         | 40 |

|      | 7.3    | Peripheral interrupts                                       | 40 |

|      |        | 7.3.1 External Interrupt Control register 1 (EICR1)         | 41 |

|      |        | 7.3.2 External Interrupt Control register 2 (EICR2)         | 42 |

|      | 7.4    | Cystem integrity management (SI)                            | 43 |

|      |        | 7.4.1 Low voltage detector (LVD)                            | 43 |

| 10   |        | 7.4.2 Auxiliary voltage detector (AVD)                      | 45 |

| cO// |        | 7.4.3 Low power modes                                       | 46 |

| 03   |        | 7.4.4 Register description                                  | 46 |

|      | 30     |                                                             |    |

| 8    |        | r saving modes                                              |    |

| 5    | 8.1    | Introduction                                                | 48 |

|      | 8.2    | Slow mode                                                   | 49 |

|      | 8.3    | Wait mode                                                   | 49 |

|      | 8.4    | Active-halt and Halt modes                                  | 50 |

|      |        | 8.4.1 Active-halt mode                                      | 51 |

|      |        | 8.4.2 Halt mode                                             | 52 |

|      | 8.5    | Auto-wakeup from Halt mode                                  | 54 |

|      |        |                                                             |    |

|       |        | 8.5.1           | Register description   | . 57 |

|-------|--------|-----------------|------------------------|------|

| 9     | I/O po | orts            |                        | . 59 |

|       | 9.1    | Introdu         | ction                  | . 59 |

|       | 9.2    | Functio         | nal description        | . 59 |

|       |        | 9.2.1           | Input modes            |      |

|       |        | 9.2.2           | Output modes           |      |

|       |        | 9.2.3           | Alternate functions    | . 61 |

|       | 9.3    | Unused          | d I/O pins             | . 63 |

|       | 9.4    | Low po          | wer modes              | 63   |

|       | 9.5    | Interrup        | ots                    | . 63 |

|       | 9.6    | I/O por         | t implementation       | . 64 |

|       |        |                 | 2100 (6)               |      |

| 10    | On-cl  | hip peri        | pherals                | 65   |

|       | 10.1   | Lite tim        | er (LT)                | . 65 |

|       |        | 10.1.1          | Introduction           | . 65 |

|       |        | 10.1.2          | Main features          | . 65 |

|       |        | 10.1.3          | Functional description |      |

|       |        | 10.1.4          | Low power modes        |      |

|       |        | 10.1.5          | Interrupts             |      |

|       |        | 10.1.6          | Register description   |      |

|       | 10.2   |                 | านาว-reload timer (AT) |      |

|       |        | 10.2.1          | Introduction           |      |

|       | 40,    | 10.2.2          | Main features          |      |

|       | Sir    | 10.2.3          | Functional description | . 71 |

| c0'   |        | 10.2.4          | Low power modes        |      |

| 0     |        | 10.2.5          | Interrupts             |      |

| ,     | 2/6    | 10.2.6          | Register description   |      |

| 10501 | 10.3   | 10-bit <i>A</i> | VD converter (ADC)     |      |

| MS    |        | 10.3.1          | Introduction           |      |

| ) (   |        | 10.3.2          | Main features          |      |

|       |        | 10.3.3          | Functional description |      |

|       |        | 10.3.4          | Low power modes        |      |

|       |        | 10.3.5          | Interrupts             |      |

|       |        | 10.3.6          | Register description   | . 82 |

#### Pin description 2

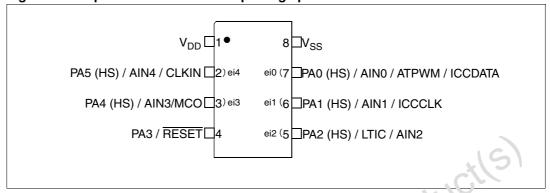

Figure 2. 8-pin SO and Plastic DIP package pinout

- 1. HS: High sink capability.

- 2. eix: associated external interrupt vector

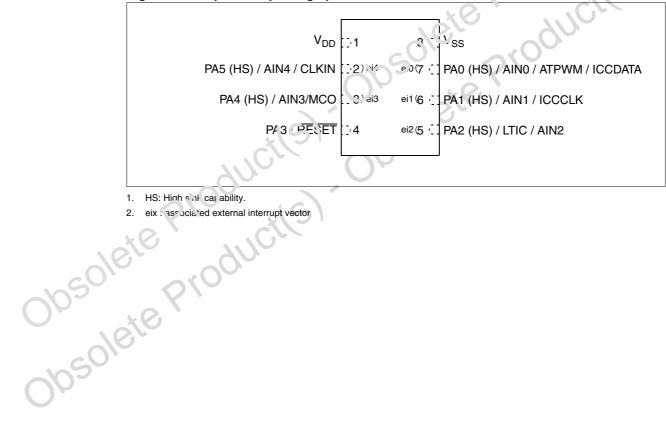

Figure 3. 8-pin DFN package pinout

- eix : จราวต่ะ ed external interrupt vector

Hardware register map (continued)<sup>(1)</sup> Table 3.

| Address                                            | Block             | Register<br>label                                    | Register name                                                                                                                                                | Reset status                           | Remark                          |

|----------------------------------------------------|-------------------|------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|---------------------------------|

| 0049h<br>004Ah                                     | AWU               | AWUPR<br>AWUCSR                                      | AWU Prescaler register AWU Control/Status register                                                                                                           | FFh<br>00h                             | R/W<br>R/W                      |

| 004Bh<br>004Ch<br>004Dh<br>004Eh<br>004Fh<br>0050h | DM <sup>(4)</sup> | DMCR<br>DMSR<br>DMBK1H<br>DMBK1L<br>DMBK2H<br>DMBK2L | DM Control register DM Status register DM Breakpoint register 1 High DM Breakpoint register 1 Low DM Breakpoint register 2 High DM Breakpoint register 2 Low | 00h<br>00h<br>00h<br>00h<br>00h<br>00h | R/W<br>R/W<br>R/W<br>R/W<br>R/W |

| 0051h to<br>007Fh                                  |                   |                                                      | Reserved area (47 bytes)                                                                                                                                     |                                        | 16)                             |

|                                                    |                   |                                                      | i solete                                                                                                                                                     | orodiul                                |                                 |

|                                                    | ete               | Slogn                                                | ct(s) obsolete                                                                                                                                               | Produk                                 |                                 |

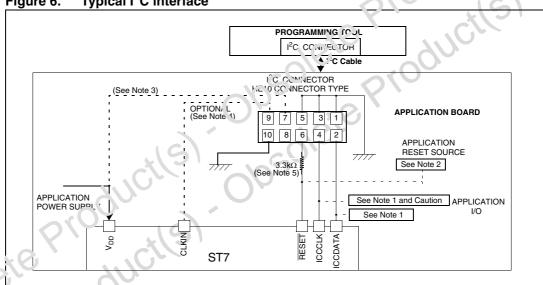

Pin 9 has to be connected to the CLKIN pin of the ST7 when  $I^2C$  mode is selected with option bytes disabled (35-pulse  $I^2C$  entry mode). When option bytes are enabled (38-pulse  $I^2C$  entry mode), the internal RC clock (internal RC or AWU RC) is forced. If internal RC is selected in the option byte, the internal RC is provided. If AWU RC or external clock is selected, the AWU RC oscillator is provided.

A serial resistor must be connected to  $I^2C$  connector pin 6 in order to prevent contention on PA3/RESET pin. Contention may occur if a tool forces a state on RESET pin while PA3 pin forces the opposite state in output mode. The resistor value is defined to limit the current below 2 mA at 5 V. If PA3 is used as output push-pull, then the application must be switched off to allow the tool to take control of the RESET pin (PA3). To allow the programming tool to drive the RESET pin below  $V_{\rm IL}$ , special care must also be taken when a pull-up is placed on PA3 for application reasons.

#### Caution:

During normal operation, ICCCLK pin must be pulled- up, internally or externally (external pull-up of 10 k $\Omega$  mandatory in noisy environment). This is to avoid entering I<sup>2</sup>C mode unexpectedly during a reset. In the application, even if the pin is configured as output, any reset will put it back in input pull-up.

Figure 6. Typical I<sup>2</sup>C interface

# 4.5 Memory protection

There are two different types of memory protection: readout protection and Write/Erase Protection which can be applied individually.

### 4.5.1 Readout protection

Readout protection, when selected provides a protection against program memory content extraction and against write access to Flash memory. Even if no protection can be considered as totally unbreakable, the feature provides a very high level of protection for a general purpose microcontroller. Program memory is protected.

In flash devices, this protection is removed by reprogramming the option. In this case, program memory is automatically erased, and the device can be reprogrammed.

Readout protection selection depends on the device type:

- In Flash devices it is enabled and removed through the FMP R bit in the option byte.

- In ROM devices it is enabled by mask option specified in the option list.

#### 4.5.2 Flash Write/Erase protection

Write/erase protection, when set, makes it impossible to both overwrite and erase program memory. Its purpose is to provide advanced security to applications and prevent any change being made to the memory content.

Once set, Write/erase protection can never be removed. Warning: write-protected flash device is no longer reprogrammable.

Write/erase protection is enabled through the FMP W bit in the oution byte.

and I<sup>2</sup>C protocol, re. / I<sup>2</sup>C protocol reference For details on Flash programming and I<sup>2</sup>C protocol, refer to the ST7 Flash programming reference manual and to the ST7 I<sup>2</sup>C proteon reference manual.

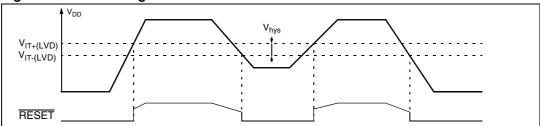

Figure 15. Low voltage detector vs reset

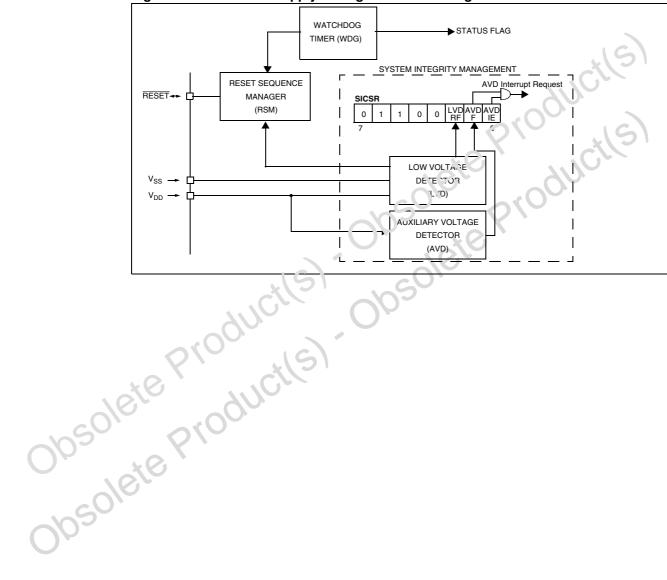

Figure 16. Reset and supply management block diagram

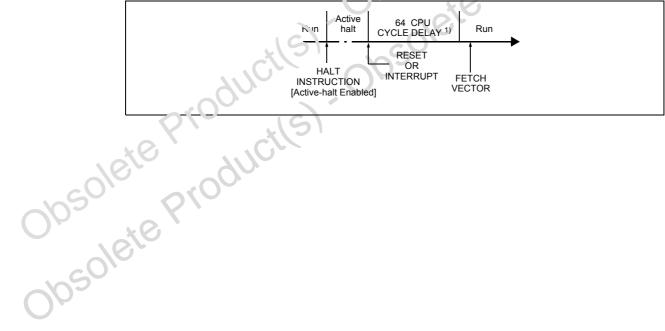

#### 8.4.1 Active-halt mode

Active-halt mode is the lowest power consumption mode of the MCU with a real time clock available. It is entered by executing the 'HALT' instruction when Active-halt mode is enabled.

The MCU can exit Active-halt mode on reception of a Lite Timer / AT Timer interrupt or a reset.

- When exiting Active-halt mode by means of a reset, a 64 CPU cycle delay occurs. After the start up delay, the CPU resumes operation by fetching the reset vector which woke it up (see Figure 22).

- When exiting Active-halt mode by means of an interrupt, the CPU immediately resumes operation by servicing the interrupt vector which woke it up (see *Figure 22*).

When entering Active-halt mode, the I bit in the CC register is cleared to enable interrupts. Therefore, if an interrupt is pending, the MCU wakes up immediately.

In Active-halt mode, only the main oscillator and the selected timer counter ('\_17/^\) are running to keep a wakeup time base. All other peripherals are not clocked except those which get their clock supply from another clock generator (such as extern all or auxiliary oscillator).

#### Caution:

As soon as Active-halt is enabled, executing a HALT instruction while the watchdog is active does not generate a reset if the WDGHALT bit is reset.

This means that the device cannot spend more than a defined delay in this power saving mode.

Figure 21. Active-halt timing over view

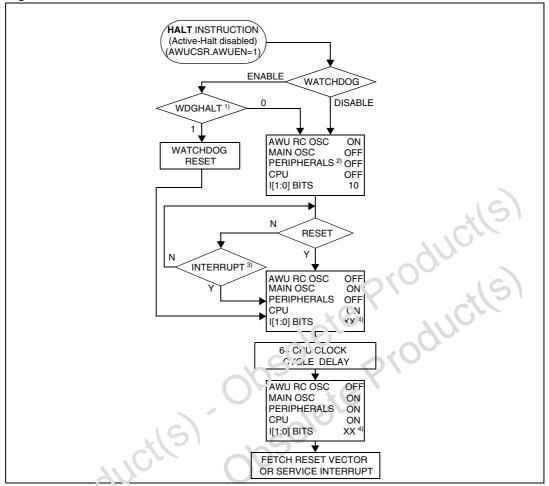

Figure 27. AWUFH mode flowchart

- WDGHALT is an option bit. See option byte section for more details.

- Per pheral clocked with an external clock source can still be active.

- Only an AWUFH interrupt and some specific interrupts can exit the MCU from Halt mode (such as external int errupt). Refer to Table 9: Interrupt mapping for more details.

- Only a.

interrup

4. Before s set to the popped. Before servicing an interrupt, the CC register is pushed on the stack. The I[1:0] bits of the CC register are set to the current software priority level of the interrupt routine and recovered when the CC register is

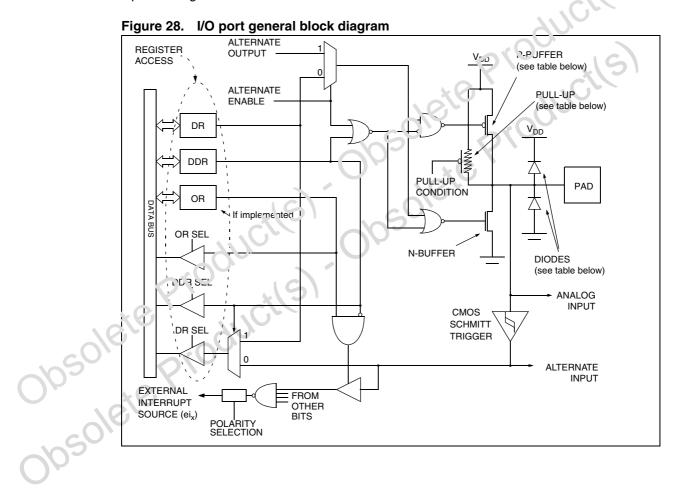

#### 9.2.3 Alternate functions

When an on-chip peripheral is configured to use a pin, the alternate function is automatically selected. This alternate function takes priority over the standard I/O programming under the following conditions:

- When the signal is coming from an on-chip peripheral, the I/O pin is automatically configured in output mode (push-pull or open drain according to the peripheral).

- When the signal is going to an on-chip peripheral, the I/O pin must be configured in floating input mode. In this case, the pin state is also digitally readable by addressing the DR register.

- Note: 1 Input pull-up configuration can cause unexpected value at the input of the alternate peripheral input.

- When an on-chip peripheral use a pin as input and output, this pin has to be configured in input floating mode.

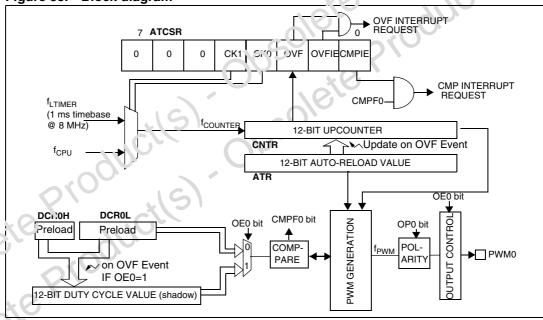

## 10.2 12-bit auto-reload timer (AT)

### 10.2.1 Introduction

The 12-bit auto-reload timer can be used for general-purpose timing functions. It is based on a free-running 12-bit upcounter with a PWM output channel.

#### 10.2.2 Main features

- 12-bit upcounter with 12-bit auto-reload register (ATR)

- Maskable overflow interrupt

- PWM signal generator

- Frequency range 2 kHz 4 MHz (@ 8 MHz f<sub>CPU</sub>)

- Programmable duty-cycle

- Polarity control

- Maskable compare interrupt

- Output compare function

Figure 33. Block diagram

## 10.2.3 Functional description

#### **PWM** mode

This mode allows a pulse width modulated signals to be generated on the PWM0 output pin with minimum core processing overhead. The PWM0 output signal can be enabled or disabled using the OE0 bit in the PWMCR register. When this bit is set the PWM I/O pin is configured as output push-pull alternate function.

Note: CMPF0 is available in PWM mode (see Section : PWM0 control/status register (PWM0CSR)).

#### 10.2.5 Interrupts

Table 28. Interrupt events

| Interrupt event <sup>(1)</sup> | Event<br>flag | Enable<br>control<br>bit | Exit<br>from<br>Wait | Exit<br>from<br>Halt | Exit<br>from<br>Active-halt |

|--------------------------------|---------------|--------------------------|----------------------|----------------------|-----------------------------|

| Overflow event                 | OVF           | OVFIE                    | Yes                  | No                   | Yes <sup>(2)</sup>          |

| CMP event                      | CMPFx         | CMPIE                    | Yes                  | No                   | No                          |

The interrupt events are connected to separate interrupt vectors (see Interrupts chapter). They generate an interrupt if the enable bit is set in the ATCSR register and the interrupt mask in the CC register is reset (RIM instruction).

#### 10.2.6 Register description

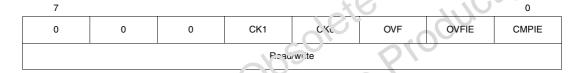

## Timer control status register (ATCSR)

Reset value: 0000 0000 (00h)

Bits 7:5 Reserved, must be kept cleared.

#### Bits 4:3 CK[1:0] Counter Clock Selection.

These bus are set and cleared by software and cleared by hardware after a reset. They select the clock frequency of the counter (see Table 29: Counter clock celection).

### Eit 2 UVF Overflow flag.

This bit is set by hardware and cleared by software by reading the ATCSR register. It indicates the transition of the counter from FFFh to ATR value.

0: No counter overflow occurred

1: Counter overflow occurred

When set, the OVF bit stays high for 1  $f_{COUNTER}$  cycle (up to 1ms depending on the clock selection) after it has been cleared by software.

#### Bit 1 **OVFIE** Overflow interrupt enable.

This bit is read/write by software and cleared by hardware after a reset.

0: OVF interrupt disabled

1: OVF interrupt enabled

# Obsolete Pro Bit 0 CMPIE Compare interrupt enable.

This bit is read/write by software and clear by hardware after a reset. It allows to mask the interrupt generation when CMPF bit is set.

0: CMPF interrupt disabled

1: CMPF interrupt enabled

<sup>2.</sup> Only if CK0=1 and CK1=0

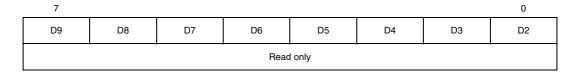

## ADC data register high (ADCDRH)

Reset value: 0000 0000 (00h)

Bits 7:0 D[9:2] MSB of Analog Converted value

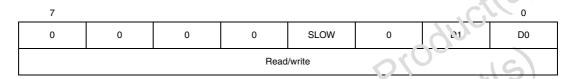

## ADC control/data register Low (ADCDRL)

Reset value: 0000 0000 (00h)

Bits 7:4 Reserved. Forced by hardware to 0.

Bit 3 SLOW Slow mode

This bit is set and cleared by software. It is used together with the SPEED bit to configure the ADC clock speed as shown on the table below (see Table 33: Configuring the ADC c ock spiced).

Bit 2 Reserved. Forced by hardware to 0.

Bits 1:0 D[1:0] LSB or Analog Converted value

Table 33. Configuring the ADC clock speed

| f <sub>ADC</sub>     | SLOW | SPEED |

|----------------------|------|-------|

| f <sub>CPU</sub> /^- | 0    | 0     |

| f <sub>CP-1</sub>    | 0    | 1     |

| i <sub>CPU</sub> /4  | 1    | Х     |

ADC register map and reset values

| f <sub>CPU</sub> /? | 10                                   | 16                                                                                                                  |                                                                                                                                            |                                                                                                                         |                                              | (                                             | )                                             | 0                                             |                                               |                                               |

|---------------------|--------------------------------------|---------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|-----------------------------------------------|-----------------------------------------------|-----------------------------------------------|-----------------------------------------------|-----------------------------------------------|

| forg                | . (                                  | )                                                                                                                   | 1                                                                                                                                          |                                                                                                                         |                                              |                                               |                                               |                                               |                                               |                                               |

| /4                  | AU.                                  |                                                                                                                     |                                                                                                                                            |                                                                                                                         |                                              | 1                                             |                                               | х                                             |                                               |                                               |

| Table 34.           | ADC regis                            | ster ma <sub>l</sub>                                                                                                | and res                                                                                                                                    | set value                                                                                                               | es                                           |                                               |                                               |                                               |                                               |                                               |

| Address<br>(Hex.)   | Register<br>label                    | 7                                                                                                                   | 6                                                                                                                                          | 5                                                                                                                       | 4                                            | 3                                             | 2                                             | 1                                             | 0                                             |                                               |

| 0034h               | ADCCSR<br>Reset value                | EOC<br>0                                                                                                            | SPEED<br>0                                                                                                                                 | ADON<br>0                                                                                                               | 0<br>0                                       | 0<br>0                                        | CH2<br>0                                      | CH1<br>0                                      | CH0<br>0                                      |                                               |

| 0035h               | ADCDRH<br>Reset value                | D9<br>0                                                                                                             | D8<br>0                                                                                                                                    | D7<br>0                                                                                                                 | D6<br>0                                      | D5<br>0                                       | D4<br>0                                       | D3<br>0                                       | D2<br>0                                       |                                               |

| 0036h               | ADCDRL<br>Reset value                | 0<br>0                                                                                                              | 0                                                                                                                                          | 0                                                                                                                       | 0<br>0                                       | SLOW<br>0                                     | 0                                             | D1<br>0                                       | D0<br>0                                       |                                               |

|                     | Table 34. Address (Hex.) 0034h 0035h | Table 34. ADC regis Address (Hex.) Register label  0034h ADCCSR Reset value  0035h ADCDRH Reset value  0036h ADCDRL | Table 34. ADC register map  Address (Hex.) Register label 7  0034h ADCCSR Reset value 0  0035h ADCDRH D9 Reset value 0  ADCDRL 0  ADCDRL 0 | Table 34.   ADC register map and resemble 34.   ADC register map and resemble 34.   Address (Hex.)   Register label   7 | Table 34.   ADC register map and reset value | Table 34.   ADC register map and reset values | Table 34.   ADC register map and reset values | Table 34.   ADC register map and reset values | Table 34.   ADC register map and reset values | Table 34.   ADC register map and reset values |

Table 39. Instructions supporting direct, indexed, indirect and indirect indexed addressing modes (continued)

| Instructions            | Function                     |  |  |  |

|-------------------------|------------------------------|--|--|--|

| CPL, NEG                | 1 or 2 complement            |  |  |  |

| BSET, BRES              | Bit operations               |  |  |  |

| BTJT, BTJF              | Bit test and jump operations |  |  |  |

| SLL, SRL, SRA, RLC, RRC | Shift and rotate operations  |  |  |  |

| SWAP                    | Swap nibbles                 |  |  |  |

| CALL, JP                | Call or jump subroutine      |  |  |  |

## 11.1.7 Relative modes (direct, indirect)

This addressing mode is used to modify the PC register value by adding an  $\ell$ -bit signed offset to it.

Table 40. Instructions supporting relative modes

| Available relative direct/indirect instructions | Function         |

|-------------------------------------------------|------------------|

| JRxx                                            | Conditional jump |

| CALLR                                           | Call relative    |

The relative addressing mode consis's or two submodes:

## **Relative mode (Direct)**

The offset follows the opcode

## Relative mode ('ndirect)

The offset is defined in memory, of which the address follows the opcode.

# 11.2 instruction groups

The ST7 family devices use an Instruction Set consisting of 63 instructions. The instructions may be subdivided into 13 main groups as illustrated in the following table:

Table 41. ST7 instruction set

| Load and Transfer               | LD   | CLR  |     |     |     |  |  |

|---------------------------------|------|------|-----|-----|-----|--|--|

| Stack operation                 | PUSH | POP  | RSP |     |     |  |  |

| Increment/Decrement             | INC  | DEC  |     |     |     |  |  |

| Compare and tests               | CP   | TNZ  | ВСР |     |     |  |  |

| Logical operations              | AND  | OR   | XOR | CPL | NEG |  |  |

| Bit operation                   | BSET | BRES |     |     |     |  |  |

| Conditional bit test and branch | BTJT | BTJF |     |     |     |  |  |

| Arithmetic operations           | ADC  | ADD  | SUB | SBC | MUL |  |  |

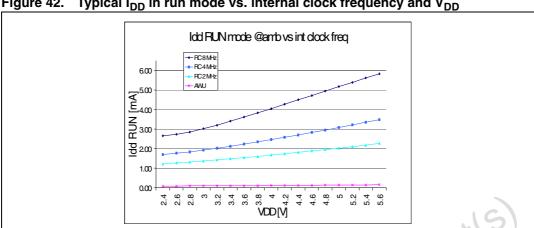

Figure 42. Typical  $I_{DD}$  in run mode vs. internal clock frequency and  $V_{DD}$

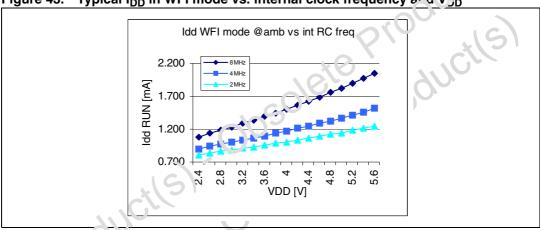

Figure 44. Typical  $I_{DD}$  in Slow, Slow-wait and Active-halt mode vs  $V_{DD}$  & int RC = 8 MHz

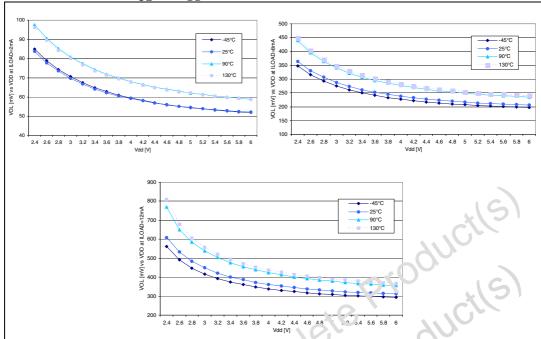

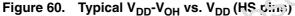

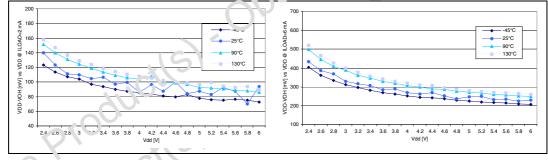

Figure 59. Typical V<sub>OL</sub> vs. V<sub>DD</sub> (HS pins)

# 12.9 Control pin characteristics

The reset network protects the device against parasitic resets.

The output of the external reset circuit must have an open-drain output to drive the ST7 reset pad. Otherwise the device can be damaged when the ST7 generates an internal reset (LVD or watchdog).

Whatever the reset source is (internal or external), the user must ensure that the level on the  $\overline{\text{RESET}}$  pin can go below the  $V_{IL}$  max. level specified in *Table 65*. Otherwise the reset will not be taken into account internally.

Because the reset circuit is designed to allow the internal reset to be output in the  $\overline{\text{RESET}}$  pin, the user must ensure that the current sunk on the  $\overline{\text{RESET}}$  pin is less than the absolute maximum value specified for  $I_{\text{INJ}(\text{RESET})}$  in *Table 44*.

Refer to *Figure 61* and *Figure 62* for a description of the RESET pin protection circuit with LVD enabled and disabled.

#### Device configuration and ordering information 14

Each device is available for production in user programmable versions (FLASH) as well as in factory coded versions (FASTROM). Refer to Table 79 for the full list of supported part

- ST7FLITEUSA2xx and ST7FLITEUSA5xx XFlash devices are shipped to customers with a default program memory content (FFh).

- Factory Advanced Service Technique ROM (FASTROM) versions are also available: they are factory-programmed XFlash devices.

The FASTROM factory coded parts contain the code supplied by the customer. This implies that FLASH devices have to be configured by the customer using the Option Bytes while the FASTROM devices are factory-configured.

#### 14.1 **Option bytes**

The two option bytes allow the hardware configuration of the inicrocontroller to be selected.

The option bytes can be accessed only in programming mode (for example using a standard ST7 programming tool).

#### 14.1.1 **OPTION BYTE 1**

Bit 7:6 CKSEL[1:0] Startup clock selection.

This bit is used to select the startup frequency. By default, the internal RC is selected (see Table 75: Startup clock selection).

- Bit 5 Rese ven, must always be 1.

- Bit 4 Recerved, must always be 0.

- Obsolete Probable obsolete Probable Pro Bi's 3:2 LVD[1:0] Low Voltage Detection selection

These option bits enable the LVD block with a selected threshold as shown in Table 76: LVD threshold configuration.

Bit 1 WDG SW Hardware or software watchdog

This option bit selects the watchdog type.

- 0: Hardware (watchdog always enabled)

- 1: Software (watchdog to be enabled by software)

- Bit 0 WDG HALT Watchdog Reset on Halt

This option bit determines if a reset is generated when entering Halt mode while the watchdog is active.

- 0: No Reset generation when entering Halt mode

- 1: Reset generation when entering Halt mode

**Table 78:**

| ,             |   | OPTION BYTE 0 |        |    |   |      |      | OPTION BYTE |            |            |     | SYTE 1 |      |      |           |             |  |   |

|---------------|---|---------------|--------|----|---|------|------|-------------|------------|------------|-----|--------|------|------|-----------|-------------|--|---|

|               | 7 | 7             |        |    |   | 7 0  |      |             |            |            | 7   |        |      |      |           |             |  | 0 |

|               |   | R             | eserve | ed |   | SEC0 | FMPR | FMPW        | CKSEL<br>1 | CKSEL<br>0 | Res | Res    | LVD1 | LVD0 | WDG<br>SW | WDG<br>HALT |  |   |

| Default value | 1 | 1             | 1      | 1  | 0 | 0    | 0    | 0           | 0          | 0          | 1   | 0      | 1    | 1    | 1         | 1           |  |   |

# 14.2 Ordering information

Customer code is made up of the FASTROM contents and the list of the selected options (if any). The FASTROM contents are to be sent on diskette, or by electronic means, with the S19 hexadecimal file generated by the development tool. All unused bytes must be set to FFh. The selected options are communicated to STMicroelectronics using the correctly completed option list appended.

Refer to application note AN1635 for information on the counter listing returned by ST after code has been transferred.

The STMicroelectronics Sales Organization will be pleased to provide detailed information on contractual points.

Table 79. Supported order codes (1)

| Order code       | Program<br>memory<br>(bytes) | RAM<br>(bytes) | ACC    | Temperature range | Package              | Conditioning |

|------------------|------------------------------|----------------|--------|-------------------|----------------------|--------------|

| ST7FLITEUSA2B6   |                              | 151            | -      | 20,               | DIP8                 | Tube         |

| ST7FLITEUSA2M6   | 1 Kbyte                      | 128            |        | -40°C +85°C       | SO8                  | Tube         |

| ST7FLITEUSA2M6TR | FLASH                        | 120            | , :0   | -40 C +65 C       | SO8                  | Tape & Reel  |

| ST7FLITEUSA2U6Tn | 40                           | 16             | -      |                   | DFN8                 | Tape & Reel  |

| ST7FLITEUSA5B6   |                              |                | 10-bit |                   | DIP8                 | Tube         |

| ST7FLITEUSA5M6   | AU                           |                | 10-bit |                   | SO8                  | Tube         |

| ST7FLITEUSA5M6TR | 1 Kbyte<br>FLASH             | 128            | 10-bit | -40°C +85°C       | SO8                  | Tape & Reel  |

| ST/FLITEUSA5U6   |                              |                | 10-bit |                   | DFN8                 | Tray         |

| ST7FLITEUSA5U6TR |                              |                | 10-bit |                   | DFN8                 | Tape & Reel  |

| ST7FLITEUSICD    | 1 Kbyte<br>FLASH             | 128            | -      | -40°C +125°C      | DIP16 <sup>(2)</sup> | Tube         |

| ST7PLUSA2B6      |                              |                | -      |                   | DIP8                 | Tube         |

| ST7PLUSA2M6      | 1 Kbyte                      | 128            | -      | -40°C +85°C       | SO8                  | Tube         |

| ST7PLUSA2M6TR    | FASTROM                      | 120            | -      | -40 C +00 C       | SO8                  | Tape & Reel  |

| ST7PLUSA2U6TR    |                              |                |        | DFN8              | Tape & Reel          |              |

125/136

Table 79. Supported order codes (1) (continued)

| Order code    | Program<br>memory<br>(bytes) | RAM<br>(bytes) | ADC    | Temperature range | Package           | Conditioning |

|---------------|------------------------------|----------------|--------|-------------------|-------------------|--------------|

| ST7PLUSA5B6   | 1 Kbyte<br>FASTROM           | 128            | 10-bit | -40°C +85°C       | DIP8              | Tube         |

| ST7PLUSA5M6   |                              |                | 10-bit |                   | SO8               | Tube         |

| ST7PLUSA5M6TR |                              |                | 10-bit |                   | SO8               | Tape & Reel  |

| ST7PLUSA5U6   |                              |                | 10-bit |                   | DFN8              | Tray         |

| ST7PLUSA5U6TR |                              |                | 10-bit |                   | DFN8              | Tape & Reel  |

| ST7PLUSA2B3   | 1 Kbyte<br>FLASH             | 128            | -      | 40°C +125°C       | DIP8              | Tube         |

| ST7PLUSA2M3   |                              |                | -      |                   | SO8               | Tupe         |

| ST7PLUSA2M3TR |                              |                | -      |                   | SO8               | Tr.pe & Reel |

| ST7PLUSA2U3TR |                              |                | -      |                   | DFN8              | Tape & Reel  |

| ST7PLUSA5B3   | 1 Kbyte<br>FLASH             | 128            | 10-bit | -40°C +125°C      | DI <sub>D</sub> 8 | Tube         |

| ST7PLUSA5M3   |                              |                | 10-bit |                   | E08               | Tube         |

| ST7PLUSA5M3TR |                              |                | 10-bit |                   | SO8               | Tape & Reel  |

| ST7PLUSA5U3   |                              |                | 10-bit |                   | DFN8              | Tray         |

| ST7PLUSA5U3TR |                              |                | 10-bit |                   | DFN8              | Tape & Reel  |

| ST7PLUSA2B3   | 1 Kbyte<br>FASTROM           | 128            |        | -40°C +125°C      | DIP8              | Tube         |

| ST7PLUSA2M3   |                              |                | / -    |                   | SO8               | Tube         |

| ST7PLUSA2M3TR |                              |                | -      |                   | SO8               | Tape & Reel  |

| ST7PLUSA2U3TR |                              |                | -      |                   | DFN8              | Tape & Reel  |

| ST7PLUSA5B3   | 40                           | 128            | 10-bit | -40°C +125°C      | DIP8              | Tube         |

| ST7PLUSA5M3   | (0)                          |                | 10-bit |                   | SO8               | Tube         |

| ST7PLUSA5M3TR | 1 Kbyte<br>FASTROM           |                | 10-bit |                   | SO8               | Tape & Reel  |

| ST7PLUS/ 5JS  |                              |                | 10-bit |                   | DFN8              | Tray         |

| ST77LUSA5U3TR |                              |                | 10-bit |                   | DFN8              | Tape & Reel  |

<sup>1.</sup> Cor.tact ST sales office for product availability.

<sup>2.</sup> For development or tool prototyping purposes only, not orderable in production quantities.

# 16 Revision history

Table 82. Document revision history

| Date      | Revision | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|-----------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 06-Feb-06 | 1        | Initial release                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|           |          | Removed references to 3% RC Added note below Figure 4 Modified presentation of Section 4.3.1 Added notes to Section 6.2 (above Figure 9), replaced 8-bit calibration value to 10-bit calibration value and changed application note reference (AN2326 instead of AN1324) Modified Table 7: Clock register map and reset values and added b t 1. in the description of CKCNTCSR register Modified Figure 13 (added CKCNTCSR register) Added note 2 to EICRx description Modified caution in section 7.2 on page 25 Replaced V <sub>IT+(LVD)</sub> by V <sub>IT+(LVD)</sub> in Section : Monitoring the VDD main supply Modified LVDRF bit description in Section 7.4. : Register description Replaced "oscillator" by "main oscillator" in the second paragraph of Section 8.4.2: Halt mode Added note 1 to Figure 23 and and the 1 note 5 to Figure 24 Modified Section 8.5: Auto-wareup from Halt mode |

| 18-Apr-06 | 2 Prodi  | Replaced bit 1 by bit 2 on AWUF bit in Section 8.5.1: Register description Modified Section § 1: Introduction. Modified Section: External interrupt function. Updated Section 9.5: Interrupts. Modified Section Table 47.: Operating conditions with low voltage detector (LVD).  Modified Table 34: Auxiliary Voltage Detector (AVD) Thresholds. Modified Table 49: voltage drop between AVD flag set and LVD reset generation.  Nodified Table 50: Internal RC oscillator calibrated at 5 V. Modified Table 53: Supply current. Modified Table 54: On-chip peripherals. Modified Table 63: General characteristics. Modified Table 64: Output driving current. Modified Table 65: Asynchronous RESET pin characteristics. Modified Section 12.10: ADC characteristics.                                                                                                                                |

| osoleite  | Prodi    | Added Figure 49. Modified Figure 61. Removed EMC protection circuitry in Figure 62 (device works correctly without these components). Added ECOPACK text in Section 13: Package characteristics. Modified first paragraph in Section 14: Device configuration and ordering information. Modified Table 79. Modified conditioning option in option list. Modified Section 14.3: Development tools. Added Section 14.4: ST7 application notes. Added Section : . Added erratasheet at the end of the document.                                                                                                                                                                                                                                                                                                                                                                                            |