Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

| Product Status             | Obsolete                                                              |

|----------------------------|-----------------------------------------------------------------------|

| Core Processor             | ST7                                                                   |

| Core Size                  | 8-Bit                                                                 |

| Speed                      | 8MHz                                                                  |

| Connectivity               | - ·                                                                   |

| Peripherals                | LVD, POR, PWM, WDT                                                    |

| Number of I/O              | 5                                                                     |

| Program Memory Size        | 1KB (1K x 8)                                                          |

| Program Memory Type        | FLASH                                                                 |

| EEPROM Size                | -                                                                     |

| RAM Size                   | 128 x 8                                                               |

| Voltage - Supply (Vcc/Vdd) | 2.4V ~ 5.5V                                                           |

| Data Converters            | - ·                                                                   |

| Oscillator Type            | Internal                                                              |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                     |

| Mounting Type              | Surface Mount                                                         |

| Package / Case             | 8-SOIC (0.154", 3.90mm Width)                                         |

| Supplier Device Package    | 8-SOIC                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/st7fliteus2m6 |

|                            |                                                                       |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 1 Introduction

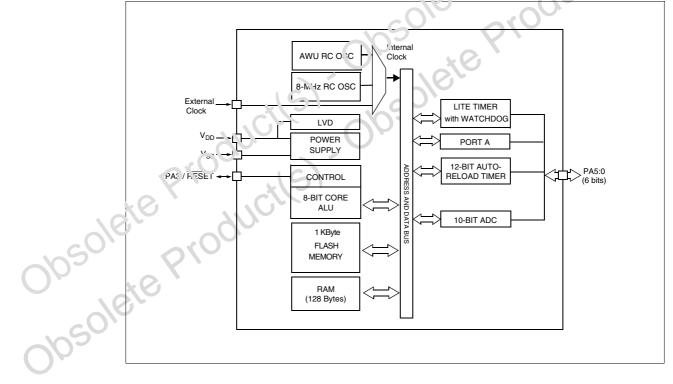

The ST7LITEUS2 and ST7LITEUS5 are members of the ST7 microcontroller family. All ST7 devices are based on a common industry-standard 8-bit core, featuring an enhanced instruction set.

The ST7LITEUS2 and ST7LITEUS5 feature FLASH memory with byte-by-byte In-Circuit Programming (ICP) and In-Application Programming (IAP) capability.

Under software control, the ST7LITEUS2 and ST7LITEUS5 can be placed in Wait, Slow, or Halt mode, reducing power consumption when the application is in idle or standby state.

The enhanced instruction set and addressing modes of the ST7 offer both power and flexibility to software developers, enabling the design of highly efficient and compact application code. In addition to standard 8-bit data management, all ST7 microcontrollers feature true bit manipulation, 8x8 unsigned multiplication and indirect addressing modes.

For easy reference, all parametric data are located in Section 12 on page 22.

The devices feature an on-chip debug module (DM) to support in cliculit debugging (ICD). For a description of the DM registers, refer to the ST7 I<sup>2</sup>C protocol reference manual.

### Figure 1. General block diagram

### 6.3.2 **RC Control register (RCCR)**

Reset value: 1111 1111 (FFh)

| 7   |     |     |      |         |     |     | 0   |

|-----|-----|-----|------|---------|-----|-----|-----|

| CR9 | CR8 | CR7 | CR6  | CR5     | CR4 | CR3 | CR2 |

|     |     |     | Read | / Write |     |     |     |

### Bits 7:0 CR[9:2] RC Oscillator Frequency Adjustment Bits

These bits, as well as CR[1:0] bits in the SICSR register must be written immediately after reset to adjust the RC oscillator frequency and to obtain the required accuracy. The application can store the correct value for each voltage range in Flash memory and write it to this register at startup. 00h = maximum available frequency

- FFh = lowest available frequency

- Note: To tune the oscillator, write a series of different value; in, the register until the correct frequency is reached. The fastest method is to use a dichotomy starting with 80h.

### 6.3.3 System Integrity (SI) Control/status register SICSR)

Reset value: 0000 0x00 (0xh)

| 7 |     |     |   | P <sup>-</sup> |       |      | 0     |

|---|-----|-----|---|----------------|-------|------|-------|

| 0 | CR1 | CR0 | 2 | 0              | LVDRF | AVDF | AVDIE |

|   |     | *19 |   | Read / Write   |       |      |       |

Bit 7 Reserved, must be kept cleared.

Bits 2:0 System Integrity bits. Refer to Section 7.4 on page 43. These bits, as well as CR[9:2] bits in the RCCR register must be written immediately after reset to adjust the RC oscillator frequency and to obtain the

- Bit 2 RC\_FLAG RC Selection

- This bit is set and cleared by hardware

- 0: No switch from RC to AWU requested

- 1: RC clock activated and temporization completed

- Bit 1 = Reserved, must be kept cleared.

- Bit 0 = **RC/AWU** RC/AWU Selection

- 0: RC enabled

- 1: AWU enabled (default value)

Table 7.Clock register map and reset values

| (Hex.) | Register<br>label       | 7        | 6        | 5        | 4        | 3        | 2            | 1         | 0           |

|--------|-------------------------|----------|----------|----------|----------|----------|--------------|-----------|-------------|

| 0038h  | MCCSR<br>Reset value    | 0        | 0        | 0        | 0        | 0        | 0            | MGO       | SMS<br>0    |

| 0039h  | RCCR<br>reset value     | CR9<br>1 | CR8<br>1 | CR7<br>1 | CR6<br>1 | CR5<br>1 | CF4          | CR3<br>1  | CR2         |

| 003Ah  | SICSR<br>reset value    | 0        | CR1      | CR0      | 0        | 0        | LVDRF<br>x   | AVDF<br>0 | AVDIE<br>0  |

| 003Eh  | AVDTHCR<br>reset value  | CK2<br>0 | CK1<br>0 | СК0<br>0 | 06       | 0 0      | 00           | AVD1<br>1 | AVD2<br>1   |

| 003Fh  | CKCNTCSR<br>reset value | 0        | 0        | 0        | 0        | AWU_FLAG | RC_FLAG<br>0 | 0         | RC/AWU<br>1 |

|        | reset value             | 20       |          |          |          |          |              |           |             |

57

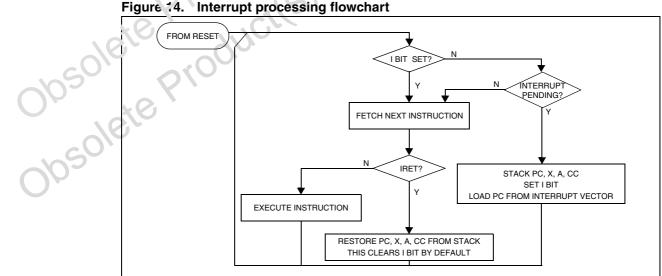

### 7.2 **External interrupts**

External interrupt vectors can be loaded into the PC register if the corresponding external interrupt occurred and if the I bit is cleared. These interrupts allow the processor to leave the Halt low power mode.

The external interrupt polarity is selected through the miscellaneous register or interrupt register (if available).

An external interrupt triggered on edge will be latched and the interrupt request automatically cleared upon entering the interrupt service routine.

Caution: The type of sensitivity defined in the Miscellaneous or Interrupt register (if available) applies to the ei source. In case of a NANDed source (as described in the I/O ports section), a low level on an I/O pin, configured as input with interrupt, masks the interrupt request even in case of rising-edge sensitivity.

### 7.3 **Peripheral interrupts**

Different peripheral interrupt flags in the status register are able to cause an interrupt when they are active if both:

- The I bit of the CC register is cleared.

- The corresponding enable bit is set in the control register.

If any of these two conditions is false, the interrupt is latched and thus remains pending.

Clearing an interrupt request is done by:

- Writing "0" to the corresponding bit in the status register or

- Access to the status rejuster while the flag is set followed by a read or write of an associated register.

Note:

The clearing security resets the internal latch. A pending interrupt (that is, waiting for being enabled) will therefore be lost if the clear sequence is executed.

### Interrupt processing flowchart Figure 14.

| N°              | Source block      | Description                        | Register<br>label                 | Priority<br>order | Exit<br>from<br>Halt | Address<br>vector           |             |

|-----------------|-------------------|------------------------------------|-----------------------------------|-------------------|----------------------|-----------------------------|-------------|

|                 | RESET             | Reset                              | N/A                               |                   | yes                  | FFFEh-FFFFh                 |             |

|                 | TRAP              | Software interrupt                 | IN/A                              |                   | no                   | FFFCh-FFFDh                 |             |

| 0               | AWU               | Auto-wakeup interrupt              | AWUCSR                            |                   | yes <sup>(1)</sup>   | FFFAh-FFFBh                 |             |

| 1               | ei0               | External interrupt 0               |                                   | Highest           |                      | FFF8h-FFF9h                 |             |

| 2               | ei1               | External interrupt 1               | - N/A                             | priority          | yes                  | FFF6h-FFF7h                 |             |

| 3               | ei2               | External interrupt 2               |                                   | N1/A              |                      |                             | FFF4h-EFF5h |

| 4               |                   | Not used                           |                                   |                   | no                   | FFI <sup>-</sup> 2.: TFI-3h |             |

| 5               | ei3               | External interrupt 3               |                                   |                   | yes                  | FFi <sup>-</sup> 0n-FFF1h   |             |

| 6 <sup>2)</sup> | ei4 <sup>2)</sup> | External interrupt 4 <sup>2)</sup> |                                   |                   | r.0 <sup>'2,</sup>   | FFEEh-FFEFh                 |             |

| 7               | SI                | AVD interrupt                      | SICSR                             |                   | Ono                  | FFECh-FFEDh                 |             |

| 8               | AT TIMER          | AT TIMER Output Compare Interrupt  | PWMxCS<br>R or<br>A™C <i>S</i> +î |                   | no                   | FFEAh-FFEBh                 |             |

| 9               |                   | AT TIMER Overflow Interrupt        | AT CSR                            | Lowest            | yes <sup>(3)</sup>   | FFE8h-FFE9h                 |             |

| 10              | LITE TIMER        | LITE TIMER Input Capture Interrupt | LTCSR                             | priority          | no                   | FFE6h-FFE7h                 |             |

| 11              |                   | LITE TIMER RTC1 Interrupt          | LTCSR                             | 8                 | yes <sup>(3)</sup>   | FFE4h-FFE5h                 |             |

| 12              |                   | Not used                           | 10                                |                   | no                   | FFE2h-FFE3h                 |             |

| 13              |                   | Not used                           | 5                                 |                   | no                   | FFE0h-FFE1h                 |             |

#### Table 9. Interrupt mapping

1. This interrupt exits the MCU from Auto-weikeup from Halt mode only.

2. This interrupt exits the MCU from V an and Active-halt modes only. Moreover, IS4[1:0] = 01 is the only safe configuration to avoid spurious interrupt in F alt and AWUFH mode

3. These interrupts exit the NCU from Active-halt mode only.

### External Interrupt Control register 1 (EICR1) 7.3.1

Reset value: 0000 0000 (00h)

## Bits 1:0 ISO[1:0] ei0 sensitivity These bits define the interrupt sensitivity for ei0 according to Table 10.

Note: 1 These 8 bits can be written only when the I bit in the CC register is set.

2 Changing the sensitivity of a particular external interrupt clears this pending interrupt. This can be used to clear unwanted pending interrupts. Refer to Section : External interrupt function.

## 7.3.2 External Interrupt Control register 2 (EICR2)

Reset value: 0000 0000 (00h)

| 7 |            |   |   |      |      |      | 0    |  |  |

|---|------------|---|---|------|------|------|------|--|--|

| 0 | 0          | 0 | 0 | IS41 | IS40 | IS31 | IS30 |  |  |

|   | Read/Write |   |   |      |      |      |      |  |  |

Bits 7:4 Reserved

- Bits 3:2 **IS4[1:0]** *ei4 sensitivity* These bits define the interrupt sensitivity for ei1 according to *Table 10*.

- Bits 1:0 **IS3[1:0]** *ei3 sensitivity* These bits define the interrupt sensitivity for Sid according to Table 10.

- Note: 1 These 8 bits can be written only when the I bit in نامن CC register is set.

- 2 Changing the sensitivity of a particular external interrupt clears this pending interrupt. This can be used to clear unwanted pending interrupts. Refer to Section : External interrupt function.

- 3 IS4[1:0] = 01 is the only safe configuration to avoid spurious interrupt in Halt and AWUFH modes.

|        | ISx1 | ાકેષ્ટ | External interrupt sensitivity |

|--------|------|--------|--------------------------------|

|        | 0    | 0      | Falling edge & low level       |

|        | 0    | 1      | Rising edge only               |

| 26     | 1    | 0      | Falling edge only              |

| SO.    | 10   | G      | Rising and falling edge        |

| 00     | 10   |        |                                |

| Obsole |      |        |                                |

### Table 10. Interrupt sensitivity bits

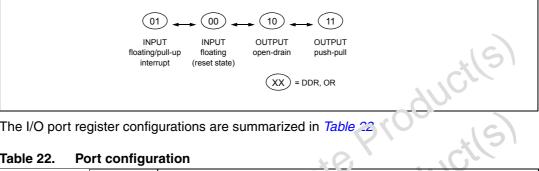

### I/O port implementation 9.6

The hardware implementation on each I/O port depends on the settings in the DDR and OR registers and specific feature of the I/O port such as ADC Input or true open drain.

Switching these I/O ports from one state to another should be done in a sequence that prevents unwanted side effects. Recommended safe transitions are illustrated in Figure 29. Other transitions are potentially risky and should be avoided, since they are likely to present unwanted side-effects such as spurious interrupt generation.

### Figure 29. Interrupt I/O port state transitions

The I/O port register configurations are summarized in Table 22

### Table 22. Port configuration

| Table 22. | Port configur   | ation    | × 9               |            | C//       |

|-----------|-----------------|----------|-------------------|------------|-----------|

| Port      | Pin name        | Input    | (DDR=0)           | Output     | (DDR=1)   |

| Port      | Fin name        | OR = 0   | <b>ਿ</b> ਯੋ = 1   | OR = 0     | OR = 1    |

| Port A    | PA0:2,<br>PA4:5 | floating | pull-up interrupt | open drain | push-pull |

|           | PA3             | G)·      |                   | open drain | push-pull |

After reset, to configure FAS as a general purpose output, the application has to program the MUXCR0 and MUXCR1 registers. See Section 6.5: Register description on page 37

|        |                    | Pere                    |          |   |   |   |   |   |   |          |

|--------|--------------------|-------------------------|----------|---|---|---|---|---|---|----------|

|        | Addre⊾s<br>્તિહx.) | Register<br>label       | Cz       | 6 | 5 | 4 | 3 | 2 | 1 | 0        |

| obsole | 0000h              | PADR<br>Reset<br>value  | MSB<br>0 | 0 | 0 | 0 | 0 | 0 | 0 | LSB<br>0 |

| Or     | 0001h              | PADDR<br>Reset<br>value | MSB<br>0 | 0 | 0 | 0 | 1 | 0 | 0 | LSB<br>0 |

| Obse   | 0002h              | PAOR<br>Reset<br>value  | MSB<br>0 | 0 | 0 | 0 | 0 | 0 | 1 | LSB<br>0 |

## Table 23 VC port register map and reset values

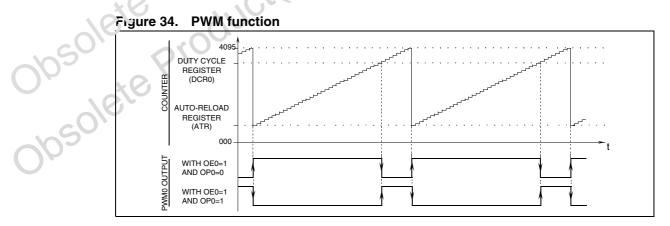

### PWM frequency and duty cycle

The PWM signal frequency ( $f_{\text{PWM}}$ ) is controlled by the counter period and the ATR register value.

$f_{PWM} = f_{COUNTER} / (4096 - ATR)$

Following the above formula, if  $f_{CPU}$  is 8 MHz, the maximum value of  $f_{PWM}$  is 4 MHz (ATR register value = 4094), and the minimum value is 2 kHz (ATR register value = 0).

*Note:* The maximum value of ATR is 4094 because it must be lower than the DCR value which must be 4095 in this case.

At reset, the counter starts counting from 0.

Software must write the duty cycle value in the DCR0H and DCR0L preload register: The DCR0H register must be written first. See caution below.

When a upcounter overflow occurs (OVF event), the ATR value is loaded in the upcounter, the preloaded Duty cycle value is transferred to the Duty Cycle register and the PWM0 signal is set to a high level. When the upcounter matches the DCRx value the PWM0 signals is set to a low level. To obtain a signal on the PWM0 pin, the contents of the DCR0 register must be greater than the contents of the ATR register.

The polarity bit can be used to invert the output signal.

The maximum available resolution for the PWM0 duty cycle is:

Resolution = 1 / (4096 - ATR)

- Note: To get the maximum resolution (1/40.16), 'he ATR register must be 0. With this maximum resolution and assuming that DCR=A1  $\overline{n}$ , a 0% or 100% duty cycle can be obtained by changing the polarity.

- **Caution:** As soon as the DCR0H is written, the compare function is disabled and will start only when the DCR0L value is written. If the DCR0H write occurs just before the compare event, the signal on the PV: A output may not be set to a low level. In this case, the DCRx register should be up acted just after an OVF event. If the DCR and ATR values are close, then the DCRx register should be updated just before an OVF event, in order not to miss a compare event and to have the right signal applied on the PWM output.

### 12 **Electrical characteristics**

### 12.1 Parameter conditions

Unless otherwise specified, all voltages are referred to V<sub>SS</sub>.

### 12.1.1 Minimum and maximum values

Unless otherwise specified the minimum and maximum values are guaranteed in the worst conditions of ambient temperature, supply voltage and frequencies by tests in production on 100% of the devices with an ambient temperature at  $T_A=25$  °C and  $T_A=T_Amax$  (given by the selected temperature range).

Data based on characterization results, design simulation and/or technology characteristics are indicated in the table footnotes and are not tested in production. Based cm characterization, the minimum and maximum values refer to sample tests and represent the mean value plus or minus three times the standard deviation (mean+ $3\Sigma$ ).

### 12.1.2 **Typical values**

Unless otherwise specified, typical data are based on  $\tau_{\star}$ =25 °C, V<sub>DD</sub>=5 V (for the 4.5 V $\leq$ V<sub>DD</sub> $\leq$ 5.5 V voltage range), V<sub>DD</sub>=3.75 V (for the 3 V $\leq$ V<sub>DD</sub> $\leq$ 4.5 V voltage range) and V<sub>DD</sub>=2.7 V (for the 2.4 V≤V<sub>DD</sub>≤3 V voltage range). They are given only as design guidelines and are not tested.

### 12.1.3 **Typical curves**

Unless otherwise specifie 1, all typical curves are given only as design guidelines and are not tested.

### 12.1.4 Loading caracitor

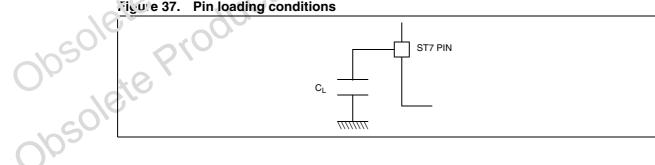

The lc ading conditions used for pin parameter measurement are shown in Figure 37.

## Figure 37. Pin loading conditions

| Symbol                                  | Ratings                                                           | Maximum value | Unit |

|-----------------------------------------|-------------------------------------------------------------------|---------------|------|

| I <sub>VDD</sub>                        | Total current into $V_{DD}$ power lines (source) <sup>(1)</sup>   | 75            |      |

| I <sub>VSS</sub>                        | Total current out of $V_{SS}$ ground lines (sink) <sup>(1)</sup>  | 150           |      |

|                                         | Output current sunk by any standard I/O and control pin           | 20            |      |

| I <sub>IO</sub>                         | Output current sunk by any high sink I/O pin                      | 40            |      |

|                                         | Output current source by any I/Os and control pin                 | -25           | mA   |

| (2)(3)                                  | Injected current on RESET pin                                     | ± 5           |      |

| I <sub>INJ(PIN)</sub> <sup>(2)(3)</sup> | Injected current on any other pin <sup>(4)</sup>                  | ± 5           | 51   |

| $\Sigma I_{\rm INJ(PIN)}^{(2)}$         | Total injected current (sum of all I/O and control pins) $^{(4)}$ | ± 20          |      |

Table 44.Current characteristics

1. All power ( $V_{DD}$ ) and ground ( $V_{SS}$ ) lines must always be connected to the extern al s  $v_{VY}$ .

2. I<sub>INJ(PIN)</sub> must never be exceeded. This is implicitly insured if V<sub>IN</sub> maximum <sup>1</sup>/<sub>3</sub> respected. If V<sub>IN</sub> maximum cannot be respected, the injection current must be limited externally to the I<sub>INJ(PIN)</sub> value. A positive injection is induced by V<sub>IN</sub>>V<sub>DD</sub> while a negative injection is induced r y V<sub>IN</sub><V<sub>SS</sub>.

3. Negative injection disturbs the analog performance of the device in particular, it induces leakage currents throughout the device including the analog inputs. To avoid in the sirable effects on the analog functions, care must be taken:

- Analog input pins must have a negative injection less than 0.8 mA (assuming that the impedance of the analog voltage is lower than the specified limits,

- Pure digital pins must have a negative injection less than 1.6 mA. In addition, it is recommended to inject the current as far as possible from the analog input pins.

4. When several inputs are submitted to a current injection, the maximum Σl<sub>INJ(PIN)</sub> is the absolute sum of the positive and negative injected currents (instantaneous values). These results are based on characterisation with Σl<sub>INJ(PIN)</sub> maximum current injection on four I/O port pins of the device.

### Table 45. Thermal characteristics

| Symbol                                                                        | Ratings                   | value       | Unit |  |  |  |

|-------------------------------------------------------------------------------|---------------------------|-------------|------|--|--|--|

| тетс                                                                          | Storage temperature range | -65 to +150 | °C   |  |  |  |

| TJ     Maximum junction temperature (see Section 13: Package characteristics) |                           |             |      |  |  |  |

# 12.3 12.3.1

## Operating conditions

## General operating conditions

$T_A = -40$  to +125 °C unless otherwise specified.

### Table 46. General operating conditions

| Symbol           | Parameter                      | Conditions                                                     | Min     | Max  | Unit |  |

|------------------|--------------------------------|----------------------------------------------------------------|---------|------|------|--|

| V                | V <sub>DD</sub> Supply voltage | f <sub>CPU</sub> = 4 MHz max.                                  | 2.4     | 5.5  | V    |  |

| ⊻ DD             | Supply voltage                 | f <sub>CPU</sub> = 8 MHz max.                                  | 3.3     | 5.5  | v    |  |

| f                | CPU clock frequency            | $3.3 \text{ V}{\leq} \text{V}_{\text{DD}}{\leq} 5.5 \text{ V}$ | up      | to 8 | MHz  |  |

| <sup>†</sup> CPU | CFO Clock frequency            | 2.4 V≤V <sub>DD</sub> <3.3 V                                   | up to 4 |      |      |  |

## 12.3.3 Auxiliary voltage detector (AVD) thresholds

$T_A = -40$  to 125°C, unless otherwise specified.

| Symbol                | Parameter                                                   | Conditions                                        | Min<br>(2)        | <b>Typ</b><br>(2) | <b>Max</b><br>(2) | Unit |

|-----------------------|-------------------------------------------------------------|---------------------------------------------------|-------------------|-------------------|-------------------|------|

| V <sub>IT+(AVD)</sub> | 1 => 0 AVDF flag toggle threshold<br>(V <sub>DD</sub> rise) | High threshold<br>Med. threshold<br>Low threshold | 4.0<br>3.4<br>2.6 | 4.4<br>3.7<br>2.9 | 4.8<br>4.1<br>3.2 | V    |

| V <sub>IT-(AVD)</sub> | 0 => 1 AVDF flag toggle threshold<br>(V <sub>DD</sub> fall) | High threshold<br>Med. threshold<br>Low threshold | 3.9<br>3.3<br>2.5 | 4.3<br>3.6<br>2.8 | 4.7<br>4.0<br>3.1 |      |

| V <sub>hys</sub>      | AVD voltage threshold hysteresis                            | $V_{\text{IT+(AVD)}}$ - $V_{\text{IT-(AVD)}}$     |                   | 150               |                   | mV   |

### Table 48. Operating characteristics with AVD<sup>(1)</sup>

1. Refer to Section : Monitoring the VDD main supply.

2. Not tested in production, guaranteed by characterization.

### Table 49. Voltage drop between AVD flag set and LVD (es at generation

| Parameter                                                    | Min <sup>(1)</sup> | <b>Typ</b> (1) | Max <sup>(1)</sup> | Unit |

|--------------------------------------------------------------|--------------------|----------------|--------------------|------|

| AVD med. threshold - AVD low. threshold                      | r.08               | 850            | 950                |      |

| AVD high. threshold - AVD low threshold                      | C1100              | 1450           | 1550               |      |

| AVD high. threshold - AVD med. threshold                     | 600                | 650            | 750                |      |

| AVD low threshold - LVD low threshold                        | 100                | 200            | 250                | mV   |

| AVD med. threshold - LVD 'ow threshold                       | 950                | 1050           | 1150               | IIIV |

| AVD med. threshold - LvD med. threshold                      | 250                | 300            | 400                |      |

| AVD high. threst.olc - LVD low threshold                     | 1600               | 1700           | 1800               |      |

| AVD high. (או אלה אלה) AVD high. איז AVD high. איז AVD high. | 900                | 1000           | 1050               |      |

## 12.3.4 Internal RC oscillator

To improve clock stability and frequency accuracy, it is recommended to place a decoupling capacitor, typically 100 nF, between the  $V_{DD}$  and  $V_{SS}$  pins as close as possible to the ST7 device.

## Internal RC oscillator calibrated at 5.0 V

The ST7 internal clock can be supplied by an internal RC oscillator (selectable by option byte).

، در ب

## 12.4.2 Internal RC oscillator supply current characteristics

| Symbol          | Parameter                                       |                        | Conditions                                  | Min | Тур  | Max <sup>(1)</sup> | Unit |  |

|-----------------|-------------------------------------------------|------------------------|---------------------------------------------|-----|------|--------------------|------|--|

|                 |                                                 |                        | T <sub>A</sub> =25 °C, int RC = 4 MHz       |     | 3.2  | 5.5                |      |  |

|                 | Supply current in Run mode <sup>(2)</sup>       | 5.0V                   | T <sub>A</sub> =25 °C, int RC = 8 MHz       |     | 5.7  | 8.5                |      |  |

|                 |                                                 | at                     | T <sub>A</sub> =25 °C, AWU RC               |     | 0.13 | 0.2                |      |  |

|                 | Supply current in Wait mode <sup>(3)</sup>      | calibrated             | T <sub>A</sub> =25 °C, int RC = 4 MHz       |     | 1.5  | 3.0                |      |  |

| I <sub>DD</sub> |                                                 | alibi                  | T <sub>A</sub> =25 °C, int RC = 8 MHz       |     | 1.9  | 4.5                | mA   |  |

|                 | Supply current in Slow mode <sup>(4)</sup>      | oscillator o           | $T_A$ =25 °C, int RC/32 = 250 kHz           |     | 1.3  | 2.0                |      |  |

|                 | Supply current in Slow-Wait mode <sup>(5)</sup> |                        | T <sub>A</sub> =25 °C, int RC/32 = 250 kHz  |     | 1.1  | 1.9                |      |  |

|                 | Supply current in Active-halt mode              | RC                     |                                             |     | U S  | 1.25               |      |  |

|                 |                                                 |                        | T <sub>A</sub> =25 °C, int RC = 4 MHz       | 2   | 2.0  | 3.0                | 5    |  |

|                 | Supply current in Run mode <sup>(2)</sup>       |                        | T <sub>A</sub> =25 °C, int RC = 2 MHz       |     | 1.3  | 2.0                |      |  |

|                 |                                                 | at 3                   | T <sub>A</sub> =25 °C, AWU RC               |     | 0.1  | 0.18               |      |  |

|                 | Supply current in Wait mode <sup>(3)</sup>      | ateo                   | T <sub>A</sub> =25 °C, int RC = 4 MHz       | ふ   | 1.0  | 1.6                |      |  |

| I <sub>DD</sub> | Supply current in wait mode                     | alibr                  | $T_A=25$ °C, in t F C = 2 MHz               | K,  | 0.9  | 1.5                | mA   |  |

|                 | Supply current in Slow mode (4)                 | toro                   | T <sub>A</sub> =25 C, int RC/32 = 250 kHz   |     | 0.95 | 1.5                |      |  |

|                 | Supply current in Slow-Wait mode <sup>(5)</sup> | o. c'llator calibrated | וֹ <sub>4</sub> =25 °C, int RC/32 = 250 kHz |     | 0.85 | 1.4                |      |  |

|                 | Supply current in Active-hat<br>mode            | ВС                     | 000                                         |     | 0.8  | 1.3                |      |  |

1. Data based on characterication results, not tested in production.

2. CPU running with more ory access, all I/O pins in input mode with a static value at VDD or VSS (no load), all peripherals in reset state; CPU clocr provided by the internal RC, LVD disabled.

3. All I/O pins in in private with a static value at V<sub>DD</sub> or V<sub>SS</sub> (no load), all peripherals in reset state; CPU clock provided by the intorr al RC, LVD disabled.

4. Slov n pute selected with  $f_{CPU}$  based on  $f_{OSC}$  divided by 32. All I/O pins in input mode with a static value at  $V_{DD}$  or  $V_{SS}$  (no open), all peripherals in reset state; CPU clock provided by the internal RC, LVD disabled.

Slow-Wait mode selected with f<sub>CPU</sub> based on f<sub>OSC</sub> divided by 32. All I/O pins in input mode with a static value at V<sub>DD</sub> or V<sub>SS</sub> (no load), all peripherals in reset state; CPU clock provided by the internal RC, LVD disabled.

### I/O port pin characteristics 12.8

### 12.8.1 **General characteristics**

Subject to general operating conditions for  $V_{DD}$ ,  $f_{OSC}$ , and  $T_A$  unless otherwise specified.

### Table 63. **General characteristics**

| Symbol                | Parameter                                                                          | 0                                                          | Conditions           | Min                | Тур                | Max                | Unit             |

|-----------------------|------------------------------------------------------------------------------------|------------------------------------------------------------|----------------------|--------------------|--------------------|--------------------|------------------|

| V <sub>IL</sub>       | Input low level voltage                                                            | -40°C to 125°C                                             |                      |                    |                    | $0.3V_{\text{DD}}$ | V                |

| V <sub>IH</sub>       | Input high level voltage                                                           | -40°C to                                                   | 125°C                | 0.7V <sub>DD</sub> |                    |                    |                  |

| V <sub>hys</sub>      | Schmitt trigger voltage hysteresis <sup>(1)</sup>                                  |                                                            |                      |                    | 400                | 10                 | mV               |

| ١L                    | Input leakage current                                                              | V <sub>SS</sub> ≤V <sub>IN</sub> :                         | ≤V <sub>DD</sub>     |                    |                    | -1                 |                  |

| ۱ <sub>S</sub>        | Static current<br>consumption induced by<br>each floating input pin <sup>(2)</sup> | Floating input mode                                        |                      | ~                  | 10(                |                    | μA               |

| _                     | Weak pull-up equivalent                                                            | V <sub>IN</sub> =V <sub>S</sub>                            | V <sub>DD</sub> =5 V | 80                 | 120                | 170                | 1                |

| R <sub>PU</sub>       | resistor <sup>(3)</sup><br>(4)                                                     | S                                                          | V <sub>DD</sub> =3 V |                    | 200 <sup>(1)</sup> |                    | kΩ               |

| C <sub>IO</sub>       | I/O pin capacitance                                                                |                                                            | <u> </u>             | 5                  | 5                  |                    | pF               |

| t <sub>f(IO)out</sub> | Output high to low level fall time <sup>1)</sup>                                   | C <sub>L</sub> =.50 n. <del>7</del><br>Petween 10% and 90% |                      | Ķ                  | 25                 |                    | 20               |

| t <sub>r(IO)out</sub> | Output low to high leve!<br>rise time <sup>1)</sup>                                |                                                            |                      |                    | 25                 |                    | ns               |

| t <sub>w(IT)in</sub>  | External interrapi oulse<br>time <sup>(5)</sup>                                    | 005                                                        |                      | 1                  |                    |                    | t <sub>CPU</sub> |

1. Data based on characterization results, not tested in production.

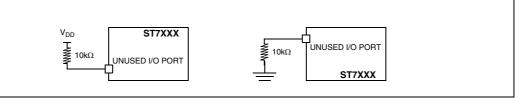

Configuration not recommended, all unused pins must be kept at a fixed voltage: using the output mode of the  $i^{\circ}$  for example or an external pull-up or pull-down resistor (see *Figure 48*). Static peak current value taken at a fixed V<sub>IN</sub> value, based on design simulation and technology characteristics, not tested in production. This value depends on V<sub>DD</sub> and temperature values. 2.

- The R<sub>PU</sub> pull-up equivalent resistor is based on a resistive transistor (corresponding  $I_{PU}$  current characteristics described in *Figure 49*).

- $R_{PU}$  not applicable on PA3 because it is multiplexed on RESET pin

- To generate an external interrupt, a minimum pulse width has to be applied on an I/O port pin configured 5. as an external interrupt source.

## Obsole Figure 48. Two typical applications with unused I/O pin

- **Caution**: During normal operation the ICCCLK pin must be pulled- up, internally or externally (external pull-up of 10k mandatory in noisy environment). This is to avoid entering I<sup>2</sup>C mode unexpectedly during a reset. 1.

- 2. I/O can be left unconnected if it is configured as output (0 or 1) by the software. This has the advantage of greater EMC robustness and lower cost.

57

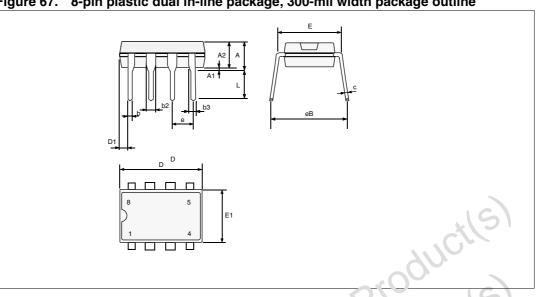

Figure 67. 8-pin plastic dual in-line package, 300-mil width package outline

| Table 72. | 8-pin plastic dual in-line package, 300-mil width package mechanical data |

|-----------|---------------------------------------------------------------------------|

|-----------|---------------------------------------------------------------------------|

|            | Dim  | mm   |      | 0      | inches <sup>(1)</sup> |        |        |

|------------|------|------|------|--------|-----------------------|--------|--------|

|            | Dim. | Min  | Тур  | Max    | Min                   | Тур    | Max    |

|            | А    |      | (    | 5.33   | Y                     |        | 0.2100 |

|            | A1   | 0.38 |      |        | 0.0150                |        |        |

|            | A2   | 2.92 | 3.30 | 4.95   | 0.1150                | 0.1300 | 0.1950 |

|            | b    | 0.36 | 0.46 | 0.56   | 0.0140                | 0.0180 | 0.0220 |

|            | b2   | 1 14 | 1.52 | 1.78   | 0.0450                | 0.0600 | 0.0700 |

|            | b3   | ý.76 | 0.99 | 1.14   | 0.0300                | 0.0390 | 0.0450 |

|            |      | 0.20 | 0.25 | 0.36   | 0.0080                | 0.0100 | 0.0140 |

|            | D    | 9.02 | 9.27 | 10.16  | 0.3550                | 0.3650 | 0.4000 |

| 26         | D1   | 0.13 |      |        | 0.0050                |        |        |

| SOI        | е    | 0    | 2.54 |        |                       | 0.1000 |        |

| 005        | eB   |      |      | 10.92  |                       |        | 0.4300 |

|            | E    | 7.62 | 7.87 | 8.26   | 0.3000                | 0.3100 | 0.3250 |

| Ole        | E1   | 6.10 | 6.35 | 7.11   | 0.2400                | 0.2500 | 0.2800 |

| 05         | L    | 2.92 | 3.30 | 3.81   | 0.1150                | 0.1300 | 0.1500 |

| <b>O</b> Y |      |      |      | Number | r of pins             |        |        |

| -          | Ν    |      |      | 8      | 3                     |        |        |

1. Values in inches are converted from mm and rounded to 4 decimal digits.

| Order code    | Program<br>memory<br>(bytes) | RAM<br>(bytes) | ADC    | Temperature<br>range | Package     | Conditioning |      |

|---------------|------------------------------|----------------|--------|----------------------|-------------|--------------|------|

| ST7PLUSA5B6   |                              |                | 10-bit |                      | DIP8        | Tube         |      |

| ST7PLUSA5M6   | +                            |                | 10-bit |                      | SO8         | Tube         |      |

| ST7PLUSA5M6TR | 1 Kbyte<br>FASTROM           | 128            | 10-bit | -40°C +85°C          | SO8         | Tape & Reel  |      |

| ST7PLUSA5U6   |                              |                | 10-bit |                      | DFN8        | Tray         |      |

| ST7PLUSA5U6TR | -                            |                | 10-bit | •                    | DFN8        | Tape & Reel  |      |

| ST7PLUSA2B3   |                              |                | -      |                      | DIP8        | Tube         |      |

| ST7PLUSA2M3   | 1 Kbyte                      | 100            | -      | 40%0 . 405%0         | SO8         | Tupe         |      |

| ST7PLUSA2M3TR | FLASH                        | 128            | -      | -40°C +125°C         | SO8         | Tripe & Reel |      |

| ST7PLUSA2U3TR | -                            |                | -      | •                    | DFN8        | Tape & Reel  |      |

| ST7PLUSA5B3   |                              |                | 10-bit |                      | DIP8        | Tube         |      |

| ST7PLUSA5M3   | -                            |                | 10-bit |                      | <b>૨</b> ૦8 | Tube         |      |

| ST7PLUSA5M3TR | 1 Kbyte<br>FLASH             | 128            | 10-bit | -40°C +125°ఁ         | SO8         | Tape & Reel  |      |

| ST7PLUSA5U3   | I LAON                       |                |        | 10-bit               |             | DFN8         | Tray |

| ST7PLUSA5U3TR | +                            |                | 10-bit | S                    | DFN8        | Tape & Reel  |      |

| ST7PLUSA2B3   |                              |                |        |                      | DIP8        | Tube         |      |

| ST7PLUSA2M3   | 1 Kbyte                      | 100            | -      | 4090 - 10590         | SO8         | Tube         |      |

| ST7PLUSA2M3TR | FASTROM                      | 128            | -      | -40°C +125°C         | SO8         | Tape & Reel  |      |

| ST7PLUSA2U3TR |                              |                |        | 02                   | DFN8        | Tape & Reel  |      |

| ST7PLUSA5B3   | <u> </u>                     | -              | 10-bit | - <del>-</del>       | DIP8        | Tube         |      |

| ST7PLUSA5M3   | 00                           |                | 10-bit | +                    | SO8         | Tube         |      |

| ST7PLUSA5M3TR | 1 Kbyte<br>FASTROM           | 128            | 10-bit | -40°C +125°C         | SO8         | Tape & Reel  |      |

| ST7PLUS/5JS   |                              |                | 10-bit | +                    | DFN8        | Tray         |      |

| ST7FLUSA5U3TR | 000                          |                | 10-bit |                      | DFN8        | Tape & Reel  |      |

Table 79.

Supported order codes <sup>(1)</sup> (continued)

1. Cor.tact ST sales office for product availability.

2. For development or tool prototyping purposes only, not orderable in production quantities.

obsolet

## 14.3 **Development tools**

Development tools for the ST7 microcontrollers include a complete range of hardware systems and software tools from STMicroelectronics and third-party tool suppliers. The range of tools includes solutions to help you evaluate microcontroller peripherals, develop and debug your application, and program your microcontrollers.

## 14.3.1 Starter kits

ST offers complete, affordable **starter kits**. Starter kits are complete, affordable hardware/software tool packages that include features and samples to help you quickly start developing your application.

## 14.3.2 Development and debugging tools

Application development for ST7 is supported by fully optimizing **C Compilers** and the **ST7 Assembler-Linker** toolchain, which are all seamlessly integrated in the ST7 integrated development environments in order to facilitate the debugging and fine-tuning of your application. The Cosmic C Compiler is available in a free version hat outputs up to 16 Kbytes of code.

The range of hardware tools includes full-featured **ST7 EV/U3 series emulators**, cost effective **ST7-DVP3 series emulators** and the low-cost **FLink** in-circuit debugger/programmer. These tools are support to by the **ST7 Toolset** from STMicroelectronics, which includes the STV/U7 integrated development environment (IDE) with high-level language debugger, eritor, project manager and integrated programming interface.

## 14.3.3 Programming tools

During the development cycle, the **ST7-DVP3** and **ST7-EMU3 series emulators** and the **RLink** provide in programming capability for programming the Flash microcontroller on your application board.

ST also provides a low-cost dedicated in-circuit programmer, the **ST7-STICK**, as well as **ST7 Socket Boards** which provide all the sockets required for programming any of the devices in a specific ST7 sub-family on a platform that can be used with any tool with incircuit programming capability for ST7.

For production programming of ST7 devices, ST's third-party tool partners also provide a complete range of gang and automated programming solutions, which are ready to integrate into your production environment.

## 14.3.4

## Order codes for development and programming tools

*Table 80* below lists the ordering codes for the ST7LITEUSx development and programming tools. For additional ordering codes for spare parts and accessories, refer to the online product selector at www.st.com/mcu.

| Identification     | Description                                                                          |  |  |  |  |  |  |

|--------------------|--------------------------------------------------------------------------------------|--|--|--|--|--|--|

| AN1044             | Multiple interrupt sources management for ST7 MCUs                                   |  |  |  |  |  |  |

| AN1045             | ST7 S/W implementation of I <sup>2</sup> C bus master                                |  |  |  |  |  |  |

| AN1046             | ART emulation software                                                               |  |  |  |  |  |  |

| AN1047             | anaging reception errors with the ST7 SCI peripherals                                |  |  |  |  |  |  |

| AN1048             | ST7 software LCD driver                                                              |  |  |  |  |  |  |

| AN1078             | PWM duty cycle switch implementing true 0% & 100% duty cycle                         |  |  |  |  |  |  |

| AN1082             | Description of the ST72141 motor control peripherals registers                       |  |  |  |  |  |  |

| AN1083             | ST72141 BLDC motor control software and flowchart example                            |  |  |  |  |  |  |

| AN1105             | ST7 pCAN peripheral driver                                                           |  |  |  |  |  |  |

| AN1129             | PWM management for BLDC motor drives using the ST72141                               |  |  |  |  |  |  |

| AN1130             | An introduction to sensorless brushless DC motor drive applications with the ST72141 |  |  |  |  |  |  |

| AN1148             | Using the ST7263 for designing a USB mouse                                           |  |  |  |  |  |  |

| AN1149             | Handling Suspend mode on a USB mouse                                                 |  |  |  |  |  |  |

| AN1180             | Using the ST7263 Kit to implement a USB game La                                      |  |  |  |  |  |  |

| AN1276             | BLDC motor start routine for the ST72141 nucrocontroller                             |  |  |  |  |  |  |

| AN1321             | Using the ST72141 motor control NCU it. sensor mode                                  |  |  |  |  |  |  |

| AN1325             | Using the ST7 USB low-speed firmware V4.x                                            |  |  |  |  |  |  |

| AN1445             | Emulated 16-bit slave SP;                                                            |  |  |  |  |  |  |

| AN1475             | Developing an ST72t5x mass storage application                                       |  |  |  |  |  |  |

| AN1504             | Starting a P.V.1 signal directly at high level using the ST7 16-bit timer            |  |  |  |  |  |  |

| AN1602             | 16-bit ti nin g operations using ST7262 or ST7263B ST7 USB MCUs                      |  |  |  |  |  |  |

| AN1633             | Lovice firmware upgrade (DFU) implementation in ST7 non-USB applications             |  |  |  |  |  |  |

| AN1712             | Generating a high resolution sinewave using ST7 PWMART                               |  |  |  |  |  |  |

| AN1713             | SMBus slave driver for ST7 I2C peripherals                                           |  |  |  |  |  |  |

| AN 1750            | Software UART using 12-bit ART                                                       |  |  |  |  |  |  |

| <b>∆</b> №1947     | ST7MC PMAC sine wave motor control software library                                  |  |  |  |  |  |  |

| General purpose    |                                                                                      |  |  |  |  |  |  |

| AN1476             | Low cost power supply for home appliances                                            |  |  |  |  |  |  |

| AN1526             | ST7FLITE0 quick reference note                                                       |  |  |  |  |  |  |

| AN1709             | EMC design for ST Microcontrollers                                                   |  |  |  |  |  |  |

| AN1752             | ST72324 quick reference note                                                         |  |  |  |  |  |  |

| Product evaluation | n                                                                                    |  |  |  |  |  |  |

| AN 910             | Performance benchmarking                                                             |  |  |  |  |  |  |

| AN 990             | ST7 benefits vs industry standard                                                    |  |  |  |  |  |  |

### Table 81. ST7 application notes (continued)

| Identification   | Description                                                                            |

|------------------|----------------------------------------------------------------------------------------|

| AN 987           | ST7 serial test controller programming                                                 |

| AN 988           | Starting with ST7 assembly tool chain                                                  |

| AN1039           | ST7 math utility routines                                                              |

| AN1071           | Half duplex USB-to-serial bridge using the ST72611 USB microcontroller                 |

| AN1106           | Translating assembly code from HC05 to ST7                                             |

| AN1179           | Programming ST7 Flash microcontrollers in remote ISP mode (In-situ programming)        |

| AN1446           | Using the ST72521 emulator to debug an ST72324 target application                      |

| AN1477           | Emulated data EEPROM with Xflash memory                                                |

| AN1527           | Developing a USB smartcard reader with ST7SCR                                          |

| AN1575           | On-board programming methods for XFLASH and HDFLASH ST7 MCUs                           |

| AN1576           | In-application programming (IAP) drivers for ST7 HDFLASH or XFLASH MCUs                |

| AN1577           | Device firmware upgrade (DFU) implementation for ST7 USB applications                  |

| AN1601           | Software implementation for ST7DALI-EVAL                                               |

| AN1603           | Using the ST7 USB device firmware upgrade development kit (DFU-DK)                     |

| AN1635           | ST7 customer ROM code release information                                              |

| AN1754           | Data logging program for testing S <sup>-</sup> 7 a אין lications via I <sup>2</sup> C |

| AN1796           | Field updates for FLASH based ST7 applications using a PC comm port                    |

| AN1900           | Hardware implementation for ST7DALI-EVAL                                               |

| AN1904           | ST7MC three-phase NC induction motor control software library                          |

| AN1905           | ST7MC thre                                                                             |

| System optimizat | tion                                                                                   |

| AN1711           | Suftware techniques for compensating ST7 ADC errors                                    |

| AN1827           | Implementation of SIGMA-DELTA ADC with ST7FLITE05/09                                   |

| AN2003           | PWM Management for 3-phase BLDC motor drives using the ST7FMC                          |

| NZU30            | Back EMF detection during PWM on time by ST7MC                                         |

| AN2013<br>AN2030 |                                                                                        |

### Table 81. ST7 application notes (continued)

## ST7LITEUS2, ST7LITEUS5

| Date        | Revision | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|-------------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 18-Sep-06   | 3        | Modified description of AVD[1:0] bits in the AVDTRH register in Section 7.4.4<br>Modified description of CNTR[11:0] bits in Section 10.2.6: Register description<br>Modified values in Table 44<br>LVD and AVD tables updated, Table 47, Table 48 and Table 49<br>Internal RC oscillator data modified in Table 50 and new table added Table 51<br>Typical data in Table 54 (on chip peripherals) modified<br>EMC characteristics updated, Section 12.7<br>R <sub>PU</sub> data corrected in Table 63 including additional notes<br>Output driving current table updated, Table 64<br>R <sub>ON</sub> data corrected in Table 65.<br>Modified ADC accuracy tables in Section 12.10<br>Section : updated<br>Errata sheet removed from document<br>Notes modified for low voltage detector Section 7.4.1<br>Notes updated in Section 4.4 (I <sup>2</sup> C Interface)<br>Thermal characteristics table updated, Table 74<br>Modified option list on Section 14.2: Ordering information<br>Modified Section 14.3: Development tools<br>Modified text in Section :                                                                                        |

| 26-Jan-07   | 4        | Added -40°C to 125°C temperature range<br>Modified note on ei4 in Table 9. Interrupt mapping<br>Added note 3 to Section 7.3 2° External Interrupt Control register 2 (EICR2)<br>Added Figure 41 and Figure 40<br>Added a note to LV DRF in Section 7.4.4: Register description<br>Section 6.4.1: Introduction<br>Modified Table 47 and Table 48<br>Modified Table 47 and Table 48<br>Modified Table 50Updated Table 53<br>Undeted Table 64<br>Mod fied R <sub>AIN</sub> and ADC accuracy tables in Section 12.10: ADC characteristics<br>Modified Table 80<br>Modified Table 79<br>Modified option list on Figure 69: Option list                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 06-Feb-2009 | 5        | Document reformatted.<br>Replaced ST7ULTRALITE by ST7LITEUS2 and ST7LITEUS5.<br>Removed limitations in user and in I <sup>2</sup> C mode from <i>Section 15: Known</i><br><i>limitations</i> , and added <i>External interrupt 2 (ei2)</i> .<br>Added MCO on pin 3.<br>Updated <i>Section 12.3.2: Operating conditions with low voltage detector (LVD)</i> ,<br><i>Section 12.3.3: Auxiliary voltage detector (AVD) thresholds, Section 12.3.4:</i><br><i>Internal RC oscillator, Section 12.4: Supply current characteristics,</i> and<br><i>Section 12.8.2: Output driving current characteristics.</i><br>Updated internal RC prescaler to add 500 KHz.<br>Updated ECOPACK text in <i>Section 13.1: Package mechanical data.</i> Added<br>PDIP16 silhouette on cover page, and updated <i>Table 73: 16-pin plastic dual in-<br/>line package, 300-mil width, package mechanical data</i> and <i>Figure 68: 16-pin</i><br><i>plastic dual in-line package, 300-mil width, package outline.</i><br>Changed order codes to die A version in <i>Table 79: Supported order codes.</i><br>Removed soldering information section.<br>Updated option list. |

## Table 82. Document revision history (continued)

### Please Read Carefully:

Information in this document is provided solely in connection with ST products. STMicroelectronics NV and its subsidia. ec (ST") reserve the right to make changes, corrections, modifications or improvements, to this document, and the products and ser ice's doscribed herein at any time, without notice.

All ST products are sold pursuant to ST's terms and conditions of sale.

Purchasers are solely responsible for the choice, selection and use of the ST products and solvices described herein, and ST assumes no liability whatsoever relating to the choice, selection or use of the ST products and services described herein.

No license, express or implied, by estoppel or otherwise, to any intellectual property 1.9, is is granted under this document. If any part of this document refers to any third party products or services it shall not be deemed a licer se grant by ST for the use of such third party products or services, or any intellectual property contained therein or considered as a tria ranty covering the use in any manner whatsoever of such third party products or services or any intellectual property contained therein or considered as a tria ranty covering the use in any manner whatsoever of such third party products or services or any intellectual property contained to the trian the trian trian.

UNLESS OTHERWISE SET FORTH IN ST'S TERMS AND CONDITIONS OF SALE ST DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY WITH RESPECT TO THE USE AND/OR BALE OF ST PRODUCTS INCLUDING WITHOUT LIMITATION IMPLIED WARRANTIES OF MERCHANTABILITY, FITNE'SS FOP A PARTICULAR PURPOSE (AND THEIR EQUIVALENTS UNDER THE LAWS OF ANY JURISDICTION), OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.

UNLESS EXPRESSLY APPROVED IN VIRITING BY AN AUTHORIZED ST REPRESENTATIVE, ST PRODUCTS ARE NOT RECOMMENDED, AUTHORIZED OR WARRANTED FOR USE IN MILITARY, AIR CRAFT, SPACE, LIFE SAVING, OR LIFE SUSTAINING APPLICATIONS, NOR IN PRCD JC 'S OR SYSTEMS WHERE FAILURE OR MALFUNCTION MAY RESULT IN PERSONAL INJURY, DEATH, OR SEVERE PF OP IN TY OR ENVIRONMENTAL DAMAGE. ST PRODUCTS WHICH ARE NOT SPECIFIED AS "AUTOMOTIVE GRADE" MAY ONLY BE USED IN AUTOMOTIVE APPLICATIONS AT USER'S OWN RISK.

Resale of S. p or ucts with provisions different from the statements and/or technical features set forth in this document shall immediately void any war any granted by ST for the ST product or service described herein and shall not create or extend in any manner whatsoever, any liability of ST.

ST and the ST logo are trademarks or registered trademarks of ST in various countries.

Information in this document supersedes and replaces all information previously supplied.

The ST logo is a registered trademark of STMicroelectronics. All other names are the property of their respective owners.

© 2009 STMicroelectronics - All rights reserved

STMicroelectronics group of companies

Australia - Belgium - Brazil - Canada - China - Czech Republic - Finland - France - Germany - Hong Kong - India - Israel - Italy - Japan -Malaysia - Malta - Morocco - Singapore - Spain - Sweden - Switzerland - United Kingdom - United States of America

www.st.com