Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                                |

|----------------------------|-------------------------------------------------------------------------|

| Core Processor             | ST7                                                                     |

| Core Size                  | 8-Bit                                                                   |

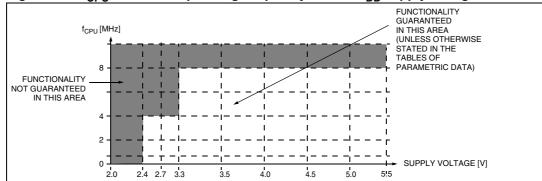

| Speed                      | 8MHz                                                                    |

| Connectivity               |                                                                         |

| Peripherals                | LVD, POR, PWM, WDT                                                      |

| Number of I/O              | 5                                                                       |

| Program Memory Size        | 1KB (1K x 8)                                                            |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                |                                                                         |

| RAM Size                   | 128 × 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 2.4V ~ 5.5V                                                             |

| Data Converters            |                                                                         |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                           |

| Package / Case             | 8-SOIC (0.154", 3.90mm Width)                                           |

| Supplier Device Package    | 8-SOIC                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/st7fliteus2m6tr |

|                            |                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 1 Introduction

The ST7LITEUS2 and ST7LITEUS5 are members of the ST7 microcontroller family. All ST7 devices are based on a common industry-standard 8-bit core, featuring an enhanced instruction set.

The ST7LITEUS2 and ST7LITEUS5 feature FLASH memory with byte-by-byte In-Circuit Programming (ICP) and In-Application Programming (IAP) capability.

Under software control, the ST7LITEUS2 and ST7LITEUS5 can be placed in Wait, Slow, or Halt mode, reducing power consumption when the application is in idle or standby state.

The enhanced instruction set and addressing modes of the ST7 offer both power and flexibility to software developers, enabling the design of highly efficient and compact application code. In addition to standard 8-bit data management, all ST7 microcontrollers feature true bit manipulation, 8x8 unsigned multiplication and indirect addressing modes.

For easy reference, all parametric data are located in Section 12 on page 22.

The devices feature an on-chip debug module (DM) to support in cliculit debugging (ICD). For a description of the DM registers, refer to the ST7 I<sup>2</sup>C protocol reference manual.

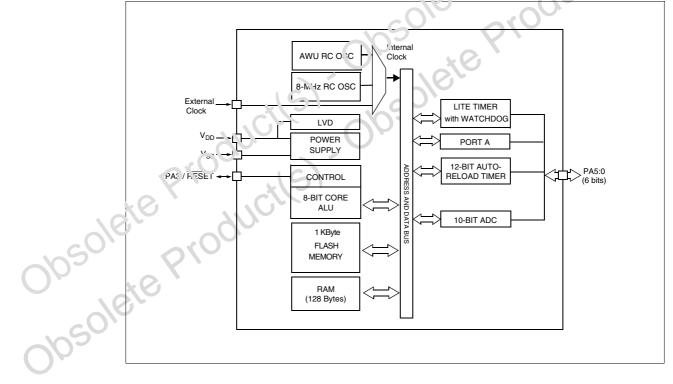

### Figure 1. General block diagram

5

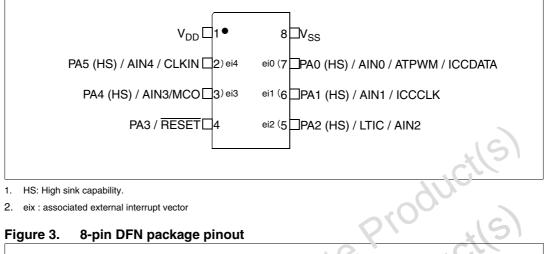

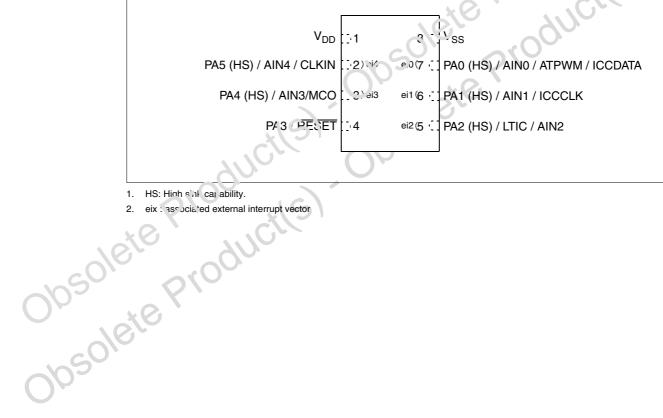

#### **Pin description** 2

- eix : as scieted external interrupt vector

| Address                                            | Block             | Register<br>label                                    | Register name                                                                                                                                                               | Reset status                           | Remark                          |

|----------------------------------------------------|-------------------|------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|---------------------------------|

| 0049h<br>004Ah                                     | AWU               | AWUPR<br>AWUCSR                                      | AWU Prescaler register<br>AWU Control/Status register                                                                                                                       | FFh<br>00h                             | R/W<br>R/W                      |

| 004Bh<br>004Ch<br>004Dh<br>004Eh<br>004Fh<br>0050h | DM <sup>(4)</sup> | DMCR<br>DMSR<br>DMBK1H<br>DMBK1L<br>DMBK2H<br>DMBK2L | DM Control register<br>DM Status register<br>DM Breakpoint register 1 High<br>DM Breakpoint register 1 Low<br>DM Breakpoint register 2 High<br>DM Breakpoint register 2 Low | 00h<br>00h<br>00h<br>00h<br>00h<br>00h | R/W<br>R/W<br>R/W<br>R/W<br>R/W |

| 0051h to<br>007Fh                                  |                   |                                                      | Reserved area (47 bytes)                                                                                                                                                    |                                        | 16)                             |

|                                                    |                   |                                                      | olete                                                                                                                                                                       | duc                                    |                                 |

|                                                    | ter               | produ                                                | ct(s) obsolete                                                                                                                                                              | produc                                 |                                 |

#### Hardware register map (continued)<sup>(1)</sup> Table 3.

the  $I^2C$  protocol routine. This routine enables the ST7 to receive bytes from the  $I^2C$  interface.

- Download ICP driver code in RAM from the ICCDATA pin

- Execute ICP driver code in RAM to program the FLASH memory

Depending on the ICP driver code downloaded in RAM, FLASH memory programming can be fully customized (number of bytes to program, program locations, or selection of the serial communication interface for downloading).

## 4.3.2 In application programming (IAP)

This mode uses an IAP driver program previously programmed in Sector 0 by the user (in ICP mode).

This mode is fully controlled by user software. This allows it to be adapted to the user application, (user-defined strategy for entering programming mode, choice of communications protocol used to fetch the data to be stored etc).

IAP mode can be used to program any memory areas except Sector 9, which is write/erase protected to allow recovery in case errors occur during the programming operation.

# 4.4 I<sup>2</sup>C interface

ICP needs a minimum of 4 and up to 6 pins to be connected to the programming tool. These pins are:

- RESET: device reset

- V<sub>SS</sub>: device power supply ground

- ICCCLK: I<sup>2</sup>C output sector clock pin

- ICCDATA: I<sup>2</sup>C input serial data pin-

- CLKIN: main clock input for external source

- V<sub>DD</sub>: application board power supply

Refer to *Figure 6* for a description of the I<sup>2</sup>C interface.

C the ICCCLK or ICCDATA pins are only used as outputs in the application, no signal isolation is necessary. As soon as the programming tool is plugged to the board, even if an I<sup>2</sup>C session is not in progress, the ICCCLK and ICCDATA pins are not available for the application. If they are used as inputs by the application, isolation such as a serial resistor has to be implemented in case another device forces the signal. Refer to the programming tool documentation for recommended resistor values.

During the ICP session, the programming tool must control the RESET pin. This can lead to conflicts between the programming tool and the application reset circuit if it drives more than 5 mA at high level (push pull output or pull-up resistor<1 k $\Omega$ ). A schottky diode can be used to isolate the application RESET circuit in this case. When using a classical RC network with R>1 k $\Omega$  or a reset management IC with open drain output and pull-up resistor>1 k $\Omega$ , no additional components are needed. In all cases the user must ensure that no external reset is generated by the application during the I<sup>2</sup>C session.

The use of Pin 7 of the I<sup>2</sup>C connector depends on the programming tool architecture. This pin must be connected when using most ST programming tools (it is used to monitor the application power supply). Please refer to the programming tool manual.

# 4.7 **Register description**

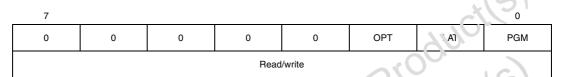

## 4.7.1 Flash Control/Status register (FCSR)

This register controls the XFlash erasing and programming using ICP, IAP or other programming methods.

1st RASS Key: 0101 0110 (56h)

2nd RASS Key: 1010 1110 (AEh)

When an EPB or another programming tool is used (in socket or ICP mode), the RASS keys are sent automatically.

Reset value: 000 0000 (00h)

### Table 4. FLASH register map and reset values

|                  |                   | LASIII                 | egister | map and | I IESEL VO | alues |   |          | CN                    |          |

|------------------|-------------------|------------------------|---------|---------|------------|-------|---|----------|-----------------------|----------|

|                  | Address<br>(Hex.) | Register<br>Label      | 7       | 6       | 5          | OP    | 3 | 20       | <b>S</b> <sub>1</sub> | 0        |

|                  | 002Fh             | FCSR<br>Reset<br>value | 0       | 0       | 0          | 0     | 0 | OPT<br>0 | LAT<br>0              | PGM<br>0 |

|                  |                   |                        | ctle    | )       | 705        |       |   |          |                       |          |

|                  | Q                 | rodu                   |         | 5) - )  |            |       |   |          |                       |          |

| ole              | ,e `              | du                     | CL      |         |            |       |   |          |                       |          |

| Obsole<br>Obsole | teP               |                        |         |         |            |       |   |          |                       |          |

| obsolt           |                   |                        |         |         |            |       |   |          |                       |          |

| 05               |                   |                        |         |         |            |       |   |          |                       |          |

#### 6.3.2 **RC Control register (RCCR)**

Reset value: 1111 1111 (FFh)

| 7   |     |     |      |         |     |     | 0   |

|-----|-----|-----|------|---------|-----|-----|-----|

| CR9 | CR8 | CR7 | CR6  | CR5     | CR4 | CR3 | CR2 |

|     |     |     | Read | / Write |     |     |     |

#### Bits 7:0 CR[9:2] RC Oscillator Frequency Adjustment Bits

These bits, as well as CR[1:0] bits in the SICSR register must be written immediately after reset to adjust the RC oscillator frequency and to obtain the required accuracy. The application can store the correct value for each voltage range in Flash memory and write it to this register at startup. 00h = maximum available frequency

- FFh = lowest available frequency

- Note: To tune the oscillator, write a series of different value; in, the register until the correct frequency is reached. The fastest method is to use a dichotomy starting with 80h.

#### 6.3.3 System Integrity (SI) Control/status register SICSR)

Reset value: 0000 0x00 (0xh)

| 7 |     |     |   | P <sup>-</sup> |       |      | 0     |

|---|-----|-----|---|----------------|-------|------|-------|

| 0 | CR1 | CR0 | 2 | 0              | LVDRF | AVDF | AVDIE |

|   |     | *19 |   | Read / Write   |       |      |       |

Bit 7 Reserved, must be kept cleared.

Bits 2:0 System Integrity bits. Refer to Section 7.4 on page 43. These bits, as well as CR[9:2] bits in the RCCR register must be written immediately after reset to adjust the RC oscillator frequency and to obtain the

#### 6.4.5 Internal watchdog reset

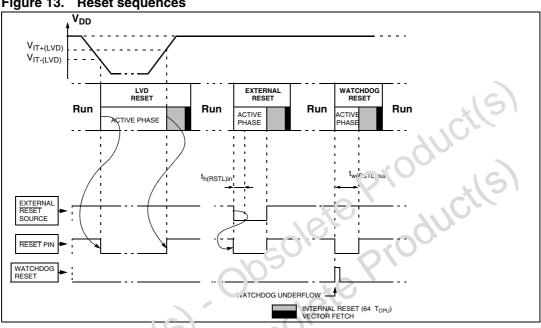

The reset sequence generated by a internal watchdog counter overflow is shown in Figure 13.

Starting from the watchdog counter underflow, the device RESET pin acts as an output that is pulled low during at least tw(RSTL)out.

#### 6.5 Register description

#### 6.5.1 Multionexed I/O Reset Control register 1 (MUXCR1)

Resot value: 0000 0000 (00h)

| 10 | 7     |       |       |             |        |       |      | 0    |

|----|-------|-------|-------|-------------|--------|-------|------|------|

|    | MIR15 | MIR14 | MIR13 | MIR12       | MIR11  | MIR10 | MIR9 | MIR8 |

|    | xe`   | ·     |       | Read / Writ | e once |       |      |      |

# 6.5.2

# Multiplexed I/O Reset Control register 0 (MUXCR0)

Reset value: 0000 0000 (00h)

| 7    |      |      |           |          |      |      | 0    |

|------|------|------|-----------|----------|------|------|------|

| MIR7 | MIR6 | MIR5 | MIR4      | MIR3     | MIR2 | MIR1 | MIR0 |

|      |      |      | Read / Wr | ite once |      |      |      |

Bits 15:0 MIR[15:0]

#### 7.2 **External interrupts**

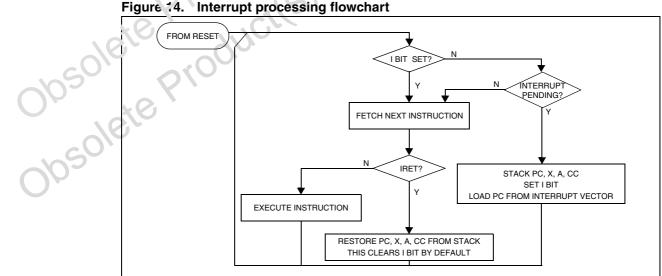

External interrupt vectors can be loaded into the PC register if the corresponding external interrupt occurred and if the I bit is cleared. These interrupts allow the processor to leave the Halt low power mode.

The external interrupt polarity is selected through the miscellaneous register or interrupt register (if available).

An external interrupt triggered on edge will be latched and the interrupt request automatically cleared upon entering the interrupt service routine.

Caution: The type of sensitivity defined in the Miscellaneous or Interrupt register (if available) applies to the ei source. In case of a NANDed source (as described in the I/O ports section), a low level on an I/O pin, configured as input with interrupt, masks the interrupt request even in case of rising-edge sensitivity.

#### 7.3 **Peripheral interrupts**

Different peripheral interrupt flags in the status register are able to cause an interrupt when they are active if both:

- The I bit of the CC register is cleared.

- The corresponding enable bit is set in the control register.

If any of these two conditions is false, the interrupt is latched and thus remains pending.

Clearing an interrupt request is done by:

- Writing "0" to the corresponding bit in the status register or

- Access to the status rejuster while the flag is set followed by a read or write of an associated register.

Note:

The clearing security resets the internal latch. A pending interrupt (that is, waiting for being enabled) will therefore be lost if the clear sequence is executed.

#### Interrupt processing flowchart Figure 14.

#### Bit 2 LVDRF LVD reset flag

This bit indicates that the last Reset was generated by the LVD block. It is set by hardware (LVD reset) and cleared when read. See WDGRF flag description in *Section 10.1.6 on page 69* for more details. When the LVD is disabled by OPTION BYTE, the LVDRF bit value is undefined.

- Note: If the selected clock source is one of the two internal ones, and if  $V_{DD}$  remains below the selected LVD threshold during less than  $T_{AWU}$  (33us typ.), the LVDRF flag cannot be set even if the device is reset by the LVD. If the selected clock source is the external clock (CLKIN), the flag is never set if the reset occurs during Halt mode. In run mode the flag is set only if  $f_{CLKIN}$  is greater than 10 MHz.

- Bit 1 **AVDF** *Voltage Detector flag* This read-only bit is set and cleared by hardware. If the AVDIE bit is set, an interrupt request is generated when the AVDF bit is set. Refer to *Figure 17* for additional details 0: V<sub>DD</sub> over AVD threshold

1: V<sub>DD</sub> under AVD threshold

Bit 0 AVDIE Voltage Detector interrupt enable This bit is set and cleared by software. It enables an marrupt to be generated when the AVDF flag is set. The pending interrupt information is automatically cleared when software enters the AVD interrupt routine. 0: AVD interrupt disabled 1: AVD interrupt enabled

### AVD Threshold Selection register (MVDTHCR)

Refer to Section 6.3.4: AVD Threshold' Selection register (AVDTHCR) for a full description of this register.

## **Application notes**

The LVDRF flag is not cleared when another reset type occurs (external or watchdog), the LVDRF flag remains set to keep trace of the original failure.

In this case, a watchdog reset can be detected by software while an external reset can not.

|       | 10.013 10.        | System                    | integrity | register | map an   | u reser | values |            |           |            |

|-------|-------------------|---------------------------|-----------|----------|----------|---------|--------|------------|-----------|------------|

| cole  | Address<br>(Hex.) | Register<br>label         | 7         | 6        | 5        | 4       | 3      | 2          | 1         | 0          |

| 0/05  | 003Ah             | SICSR<br>reset<br>value   | 0         | 1        | 1        | 0       | 0      | LVDRF<br>x | AVDF<br>0 | AVDIE<br>0 |

| 00501 | 003Eh             | AVDTHCR<br>reset<br>value | CK2<br>0  | CK1<br>0 | СК0<br>0 | 0       | 0      | 0          | AVD1<br>1 | AVD2<br>1  |

Table 15. System integrity register map and reset values

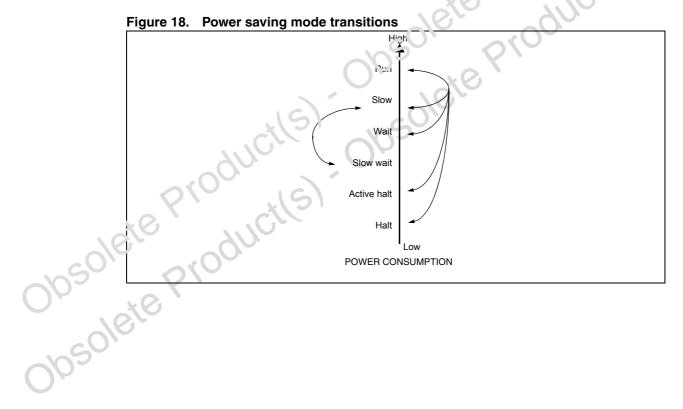

# 8 Power saving modes

## 8.1 Introduction

To give a large measure of flexibility to the application in terms of power consumption, four main power saving modes are implemented in the ST7 (see *Figure 18*):

- Slow

- Wait (and Slow-wait)

- Active-halt

- Auto-wakeup from Halt (AWUFH)

- Halt

After a reset the normal operating mode is selected by default (Run mode). This incle drives the device (CPU and embedded peripherals) by means of a master clock which is based on the main oscillator frequency (f<sub>OSC</sub>).

From Run mode, the different power saving modes may be selected by setting the relevant register bits or by calling the specific ST7 software instruction whose action depends on the oscillator status.

| AWUPR[7:0] | Dividing factor |

|------------|-----------------|

| 00h        | Forbidden       |

| 01h        | 1               |

|            |                 |

| FEh        | 254             |

| FFh        | 255             |

Table 15. Configuring the dividing factor

In AWU mode, the period that the MCU stays in Halt Mode (t<sub>AWU</sub> in *Figure 26*) is defined by

$$t_{AWU} = 64 \times AWUPR \times \frac{1}{f_{AWURC}} + t_{RCSTRT}$$

This prescaler register can be programmed to modify the time that the MCU stays in Halt mode before waking up automatically.

Note: If 00h is written to AWUPR, depending on the product, an inter upt is generated immediately after a HALT instruction, or the AWUPR remains unchanged.

Table 16. AWU register map and reset values

|                  | Address<br>(Hex.) | Register<br>label              | 7          | 6                | 5               | 4               | 3               | 2               | 1               | 0               |

|------------------|-------------------|--------------------------------|------------|------------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|

|                  | 0049h             | <b>AWUPR</b><br>Reset<br>value | AWUP<br>R7 | AW'JP<br>R6<br>1 | AWUP<br>R5<br>1 | AWUP<br>R4<br>1 | AWUP<br>R3<br>1 | AWUP<br>R2<br>1 | AWUP<br>R1<br>1 | AWUP<br>R0<br>1 |

|                  | 004Ah             | AWUCSR<br>Reset<br>Vถิ่นจ      | 0          | 0                | 0               | 0               | 0               | AWUF            | AWUM            | AWUE<br>N       |

| opsole           | , eP              | rodu                           | ctle       | )                |                 |                 |                 |                 |                 |                 |

| Obsole<br>Obsole |                   |                                |            |                  |                 |                 |                 |                 |                 |                 |

# 10.1.6 Register description

## Lite timer control/status register (LTCSR)

Reset value: 0000 0x00 (0xh)

| ICIE | ICF                                                                                                                           | ТВ                                                                                                                                                                                                               | TBIE                                                                                                                                                             | TBF                                                              |        |              |             |

|------|-------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------|--------|--------------|-------------|

|      |                                                                                                                               |                                                                                                                                                                                                                  |                                                                                                                                                                  | IDF                                                              | WDGR   | WDGE         | WDGD        |

|      |                                                                                                                               |                                                                                                                                                                                                                  | Read /                                                                                                                                                           | ' Write                                                          |        |              |             |

|      | This bi<br>0: Inpu<br>1: Inpu<br>t 6 ICF In<br>This bi<br>Writing<br>0: No i<br>1: An in                                      | It Capture (IC<br>at Capture (IC<br>aput Capture<br>t is set by ha<br>to this bit do<br>nput capture<br>nput capture                                                                                             | leared by sof<br>) interrupt dis<br>) interrupt en<br><i>Flag.</i><br>rdware and c<br>pes not chang                                                              | sabled<br>pabled<br>leared by so<br>ge the bit val               |        |              | (5)         |

| Bit  | This bi<br>0: Time<br>1: Time<br>t 4 <b>TBIE</b> 7<br>This 5:<br>0: Time<br>t 3 <b>TBF</b> 7<br>This bi<br>Writing<br>0: No c | nebase perio<br>t is set and c<br>ebase period<br>ebase period<br>t is set and c<br>ebase (TB) ir<br>cebase (TB) ir<br>cimebase (TB) ir<br>cimebase Inte<br>t is set by ha<br>g to this bit ha<br>counter overfi | lea ed t y sof<br>$= t_{OSC} * 800$<br>$= t_{OSC} * 160$<br>leared by sof<br>hterrupt disab<br>hterrupt disab<br>hterrupt Flag.<br>rdware and c<br>as no effect. | 0 (1 ms @ 8<br>00 (2 ms @<br>tware.<br>led<br>ed<br>leared by so | 8 MHz) | ng the LTCSF | t register. |

### ST7LITEUS2, ST7LITEUS5

|          | Mode     |          | Syntax                 | Destination/<br>source      | Pointer address | Pointer<br>size | Length<br>(bytes) |

|----------|----------|----------|------------------------|-----------------------------|-----------------|-----------------|-------------------|

| Long     | Indirect | Indexed  | ld A,([\$10.w],X)      | 0000FFFF                    | 00FF            | word            | + 2               |

| Relative | Direct   |          | jrne loop              | PC-128/PC+127 <sup>1)</sup> |                 |                 | + 1               |

| Relative | Indirect |          | jrne [\$10]            | PC-128/PC+127 <sup>1)</sup> | 00FF            | byte            | + 2               |

| Bit      | Direct   |          | bset \$10,#7           | 00FF                        |                 |                 | + 1               |

| Bit      | Indirect |          | bset [\$10],#7         | 00FF                        | 00FF            | byte            | + 2               |

| Bit      | Direct   | Relative | btjt \$10,#7,skip      | 00FF                        |                 |                 | + 2               |

| Bit      | Indirect | Relative | btjt<br>[\$10],#7,skip | 00FF                        | 00FF            | byte            | +3                |

| Table 36. ST7 addressing mode overview (continued) <sup>(</sup> |

|-----------------------------------------------------------------|

|-----------------------------------------------------------------|

1. At the time the instruction is executed, the Program Counter (PC) points to the instruction following JRxx.

## 11.1.1 Inherent mode

All Inherent instructions consist of a single byte. The opcode (u) y specifies all the required information for the CPU to process the operation.

| Inherent instruction    | Function                            |

|-------------------------|-------------------------------------|

| NOP                     | I 'o operation                      |

| TRAP                    | S/W Interrupt                       |

| WFI                     | Wait For Interrupt (low power mode) |

| HALT                    | Halt Oscillator (lowest power mode) |

| RET                     | Subroutine return                   |

| IRET                    | Interrupt subroutine return         |

| SIM                     | Set interrupt mask                  |

| RM                      | Reset interrupt mask                |

| ISCF                    | Set carry flag                      |

| RCF                     | Reset carry flag                    |

| RSP                     | Reset stack pointer                 |

| LD                      | Load                                |

| CLR                     | Clear                               |

| PUSH/POP                | Push/Pop to/from the stack          |

| INC/DEC                 | Increment/Decrement                 |

| TNZ                     | Test Negative or Zero               |

| CPL, NEG                | 1 or 2 complement                   |

| MUL                     | Byte multiplication                 |

| SLL, SRL, SRA, RLC, RRC | Shift and rotate operations         |

| SWAP                    | Swap nibbles                        |

Table 37.

Instructions supporting inherent addressing mode

## 11.1.2 Immediate

Immediate instructions have 2 bytes, the first byte contains the opcode, the second byte contains the operand value.

| Table 38. | Instructions supporting inherent immediate addressing mode |

|-----------|------------------------------------------------------------|

|-----------|------------------------------------------------------------|

| Immediate instruction | Function              |

|-----------------------|-----------------------|

| LD                    | Load                  |

| СР                    | Compare               |

| BCP                   | Bit compare           |

| AND, OR, XOR          | Logical operations    |

| ADC, ADD, SUB, SBC    | Arithmetic operations |

## 11.1.3 Direct

In Direct instructions, the operands are referenced by their memory ac dress.

The direct addressing mode consists of two submodes:

## Direct (short) addressing mode

the address is a byte, thus requires only 1 byte offer the opcode, but only allows 00 - FF addressing space.

## Direct (long) addressing mode

The address is a word, thus allo ving 64 Kbyte addressing space, but requires 2 bytes after the opcode.

# 11.1.4 Indexed morie (no offset, short, long)

In this mode, the operand is referenced by its memory address, which is defined by the unsigned addition of an index register (X or Y) with an offset.

indirect addressing mode consists of three submodes:

## Indexed mode (no offset)

There is no offset (no extra byte after the opcode), and allows 00 - FF addressing space.

## Indexed mode (short)

The offset is a byte, thus requires only 1 byte after the opcode and allows 00 - 1FE addressing space.

## Indexed mode (long)

The offset is a word, thus allowing 64 Kbyte addressing space and requires 2 bytes after the opcode.

ار بر

|                                  | . (  | ,   |      |      |      |       |     |     |

|----------------------------------|------|-----|------|------|------|-------|-----|-----|

| Shift and rotates                | SLL  | SRL | SRA  | RLC  | RRC  | SWAP  | SLA |     |

| Unconditional jump or call       | JRA  | JRT | JRF  | JP   | CALL | CALLR | NOP | RET |

| Conditional branch               | JRxx |     |      |      |      |       |     |     |

| Interruption management          | TRAP | WFI | HALT | IRET |      |       |     |     |

| Condition code flag modification | SIM  | RIM | SCF  | RCF  |      |       |     |     |

### Table 41. ST7 instruction set (continued)

### Using a prebyte

The instructions are described with 1 to 4 bytes.

In order to extend the number of available opcodes for an 8-bit CPU (256 opcodes), three different prebyte opcodes are defined. These prebytes modify the meaning of the instruction they precede.

The whole instruction becomes:

PC-2 End of previous instruction

PC-1 Prebyte

PC Opcode

PC+1 Additional word (0 to 2) according to the number of bytes required to compute the effective address

These prebytes enable instruction in Y as well as indirect addressing modes to be implemented. They precede the opcode of the instruction in X or the instruction using direct addressing mode. The prebytes are:

PDY 90 Replace an X based instruction using immediate, direct, indexed, or inherent addressing mode by a Y on a.

PIX 92 Replace an instruction using direct, direct bit or direct relative addressing mode to an instruction using the corresponding indirect addressing mode.

It also changes an instruction using X indexed addressing mode to an instruction using indirect X indexed addressing mode.

P.V 91 Replace an instruction using X indirect indexed addressing mode by a Y one.

# 11.2.1 hlegal opcode reset

In order to provide enhanced robustness to the device against unexpected behavior, a system of illegal opcode detection is implemented. If a code to be executed does not correspond to any opcode or prebyte value, a reset is generated. This, combined with the watchdog, allows the detection and recovery from an unexpected fault or interference.

Note:

A valid prebyte associated with a valid opcode forming an unauthorized combination does not generate a reset.

| Mnemo | Description           | Function/example | Dst | Src | Н | I | N | Z | С |

|-------|-----------------------|------------------|-----|-----|---|---|---|---|---|

| ADC   | Add with carry        | A=A+M+C          | А   | М   | Н | - | Ν | Z | С |

| ADD   | Addition              | A=A+M            | А   | М   | Н | - | Ν | Z | С |

| AND   | Logical and           | A = A . M        | А   | М   | - | - | Ν | Z | - |

| BCP   | Bit compare A, Memory | tst (A . M)      | А   | М   | - | - | Ν | Z | - |

### Table 42.Illegal opcode detection

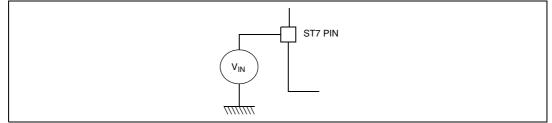

#### 12.1.5 Pin input voltage

The input voltage measurement on a pin of the device is described in *Figure 38*.

### Figure 38. Pin input voltage

#### 12.2 Absolute maximum ratings

Stresses above those listed as "absolute maximum ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device under these conditions is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

1. Directly connecting the I/O pins to  $V_{DD}$  or  $V_{SS}\, \mbox{could Gamage the device if an unexpected}$ change of the I/O configuration occurs (for example due to a corrupted program counter). To guarantee safe operation, this connection has to be done through a pull-up or pull-down resistor (typical: 10 k $\Omega$  for I/Os). Unused 1/O pins must be tied in the same way to V<sub>DD</sub> or V<sub>SS</sub> according to their reset configuration

|        | Symbol                                                                                              | Ratings                                                                                                                                                                                              | Maximum value                                                                                          | Unit      |

|--------|-----------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|-----------|

|        | V <sub>DD</sub> - V <sub>SS</sub>                                                                   | S. upply voltage                                                                                                                                                                                     | 7.0                                                                                                    | V         |

|        | VIN                                                                                                 | Input voltage on any pin <sup>(1)</sup>                                                                                                                                                              | $V_{SS}\mbox{-}0.3$ to $V_{DD}\mbox{+}0.3$                                                             | v         |

|        | VELTD(HBM)                                                                                          | Electrostatic discharge voltage (Human Body Model)                                                                                                                                                   | see Section 12                                                                                         | 2.7.2     |

| 016    | V <sub>ESD(MM)</sub>                                                                                | Electrostatic discharge voltage (Machine Model)                                                                                                                                                      | see Section 12                                                                                         | 2.7.2     |

| Obsole | <ol> <li>I<sub>INJ(PIN)</sub> must never<br/>cannot be respecte<br/>injection is induced</li> </ol> | be exceeded. This is implicitly insured if $V_{IN}$ maximum<br>d, the injection current must be limited externally to the<br>by $V_{IN}$ > $V_{DD}$ while a negative injection is induced by $V_{I}$ | is respected. If V <sub>IN</sub> max<br>I <sub>INJ(PIN)</sub> value. A positiv<br>N <v<sub>SS.</v<sub> | imum<br>e |

Voltage characteristics Table 43.

#### 12.3.2 Operating conditions with low voltage detector (LVD)

| Operati                                     | ing conditions with low                                  | v voltage detector (                                | LVD)              |                   |                   | 5    |

|---------------------------------------------|----------------------------------------------------------|-----------------------------------------------------|-------------------|-------------------|-------------------|------|

| T <sub>A</sub> = -40 t<br><b>Table 47</b> . | o 125 °C, unless otherwise s<br>Operating characteristic |                                                     |                   | 90                |                   |      |

| Symbol                                      | Parameter                                                | Conditions                                          | Min               | Тур               | Max               | Unit |

| V <sub>IT+(LVD)</sub>                       | Reset release threshold<br>(V <sub>DD</sub> rise)        | High thresho'd<br>Med. threshold<br>Low threshold   | 3.9<br>3.2<br>2.5 | 4.2<br>3.5<br>2.7 | 4.5<br>3.8<br>3.0 | V    |

| V <sub>IT-(LVD)</sub>                       | Reset generation threshold<br>(V <sub>DD</sub> fall)     | r ligh threshold<br>Med. threshold<br>Low threshold | 3.7<br>3.0<br>2.4 | 4.0<br>3.3<br>2.6 | 4.3<br>3.6<br>2.9 | V    |

| V <sub>hys</sub>                            | LVD voltage thresho'd<br>hysteresis                      | V <sub>IT+(LVD)</sub> -V <sub>IT-(LVD)</sub>        |                   | 150               |                   | mV   |

| V <sub>tPOR</sub>                           | V <sub>DD</sub> rise ime rate (1)(2)                     | 30-                                                 | 20                |                   |                   | μs/V |

| I <sub>DD(LVD)</sub>                        | LV'フレベベ5 current consumption                             | V <sub>DD</sub> = 5 V                               |                   | 220               |                   | μA   |

Not tested in production. The  $V_{DD}$  rise time rate condition is needed to ensure a correct device power-on and LVD reset release. When the  $V_{DD}$  slope is outside these values, the LVD may not release properly the reset of the MCU

red in productic ...ease. When the V<sub>DL</sub>

2. Use of LVD with capac recommended to pull V<sub>L</sub> page 114.

3. Not tested in production. Use of LVD with capacitive power supply: with this type of power supply, if power cuts occur in the application, it is recommended to pull  $V_{DD}$  down to 0V to ensure optimum restart conditions. Refer to circuit example in *Figure 61 on page 114*.

57

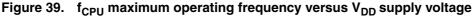

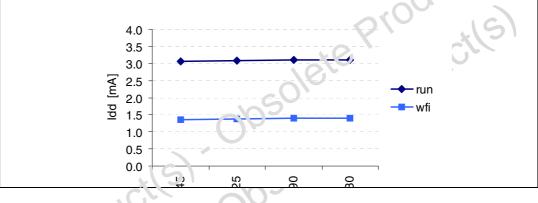

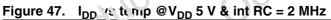

Figure 45.  $I_{DD}$  vs temp @V<sub>DD</sub> 5 V & int RC = 8 MHz

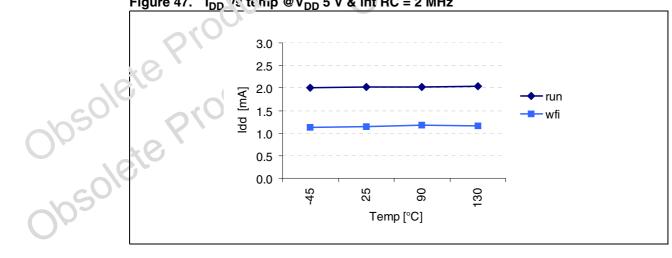

Figure 49. Typical  $I_{PU}$  vs.  $V_{DD}$  with  $V_{IN}=V_{SS}I$

# 12.8.2 Output driving current characteristics

Subject to general operating conditions for  $V_{DD}$ ,  $f_{CPU}$ , and  $T_A$  , nless otherwise specified.

| Symbol                                | Parameter                                                                                             | C                 | Conditions                                      | Min                   | Max  | Unit |

|---------------------------------------|-------------------------------------------------------------------------------------------------------|-------------------|-------------------------------------------------|-----------------------|------|------|

|                                       | Output low level voltage for PA3/RESET star Jar                                                       | D                 | I <sub>IO</sub> = +5 mA,T <sub>A</sub> ≤ 125 °C |                       | 1200 |      |

| V <sub>OL</sub> <sup>(1)</sup>        | I/O pin (see <i>Figure 52</i> )                                                                       |                   | I <sub>IO</sub> = +2 mA,T <sub>A</sub> ≤ 125 °C |                       | 400  |      |

| VOL 1                                 | Output low level voltage for a high sink I/O pin                                                      | _5 <              | $I_{IO}$ =+20 mA, $T_A$ ≤ 125 °C                |                       | 1300 |      |

|                                       | when 4 pins are sunk at same time (see Figure 55)                                                     | VDD               | I <sub>IO</sub> = +8 mA,T <sub>A</sub> ≤ 125 °C |                       | 750  |      |

| V <sub>OH</sub> <sup>(2)</sup>        | Output high level voltane for an I/O pin when 4 pins                                                  |                   | I <sub>IO</sub> = -5 mA,T <sub>A</sub> ≤ 125 °C | V <sub>DD</sub> -1500 |      |      |

| ∙он                                   | are sourced at same tin e (see Figure 58)                                                             |                   | $I_{IO}$ = -2 mA, $T_A \le$ 125 °C              | V <sub>DD</sub> -800  |      |      |

| (1)(2)                                | Output lov' le vei voltage for PA3/RESET standard<br>I/O pin (see <i>Figure 51</i> )                  |                   | I <sub>IO</sub> = +2 mA,T <sub>A</sub> ≤ 125 °C |                       | 500  |      |

| V <sub>OL</sub> <sup>(1)(3)</sup>     | Orbet low level voltage for a high sink I/O pin                                                       | =3 V              | $I_{IO}$ = +2 mA, $T_A \le$ 125 °C              |                       | 180  | mV   |

| ~0                                    | when 4 pins are sunk at same time (see <i>Figure 54</i> )                                             | VDD               | I <sub>IO</sub> = +8 mA,T <sub>A</sub> ≤ 125 °C |                       | 600  |      |

| V.<br>(2)(3)                          | Output high level voltage for an I/O pin when 4 pins are sourced at same time (see <i>Figure 57</i> ) |                   | I <sub>IO</sub> = -2 mA,T <sub>A</sub> ≤ 125 °C | V <sub>DD</sub> -800  |      |      |

| (1)(3)                                | Output low level voltage for PA3/RESET standard I/O pin (see <i>Figure 53</i> )                       | >                 | I <sub>IO</sub> = +2 mA,T <sub>A</sub> ≤ 125 °C |                       | 700  |      |

| V <sub>OL</sub> <sup>(1)(3)</sup>     | Output low level voltage for a high sink I/O pin                                                      | 2.4 \             | $I_{IO}$ = +2 mA, $T_A \le$ 125 °C              |                       | 200  |      |

| · · · · · · · · · · · · · · · · · · · | when 4 pins are sunk at same time (see <i>Figure 53</i> )                                             | V <sub>DD</sub> = | I <sub>IO</sub> =+8 mA,T <sub>A</sub> ≤ 125 °C  |                       | 800  |      |

| V <sub>OH</sub><br>(2)(3)             | Output high level voltage for an I/O pin when 4 pins are sourced at same time (see <i>Figure 56</i> ) |                   | I <sub>IO</sub> =-2 mA,T <sub>A</sub> ≤ 125 °C  | V <sub>DD</sub> -900  |      |      |

Table 64. Output driving current characteristics

1. The  $I_{IO}$  current sunk must always respect the absolute maximum rating specified in *Table 52* and the sum of  $I_{IO}$  (I/O ports and control pins) must not exceed  $I_{VSS}$ .

2. The  $I_{IO}$  current sourced must always respect the absolute maximum rating specified in *Table 52* and the sum of  $I_{IO}$  (I/O ports and control pins) must not exceed  $I_{VDD}$ . True open drain I/O pins do not have  $V_{OH}$ .

3. Not tested in production, based on characterization results.

| Identification     | Description                                                                          |  |  |  |

|--------------------|--------------------------------------------------------------------------------------|--|--|--|

| AN1044             | Multiple interrupt sources management for ST7 MCUs                                   |  |  |  |

| AN1045             | ST7 S/W implementation of I <sup>2</sup> C bus master                                |  |  |  |

| AN1046             | UART emulation software                                                              |  |  |  |

| AN1047             | Managing reception errors with the ST7 SCI peripherals                               |  |  |  |

| AN1048             | ST7 software LCD driver                                                              |  |  |  |

| AN1078             | PWM duty cycle switch implementing true 0% & 100% duty cycle                         |  |  |  |

| AN1082             | Description of the ST72141 motor control peripherals registers                       |  |  |  |

| AN1083             | 72141 BLDC motor control software and flowchart example                              |  |  |  |

| AN1105             | ST7 pCAN peripheral driver                                                           |  |  |  |

| AN1129             | PWM management for BLDC motor drives using the ST72141                               |  |  |  |

| AN1130             | An introduction to sensorless brushless DC motor drive applications with the ST72141 |  |  |  |

| AN1148             | Using the ST7263 for designing a USB mouse                                           |  |  |  |

| AN1149             | Handling Suspend mode on a USB mouse                                                 |  |  |  |

| AN1180             | Using the ST7263 Kit to implement a USB game La                                      |  |  |  |

| AN1276             | BLDC motor start routine for the ST72141 nucrocontroller                             |  |  |  |

| AN1321             | Using the ST72141 motor control NCU it. sensor mode                                  |  |  |  |

| AN1325             | Using the ST7 USB low-speed firmware V4.x                                            |  |  |  |

| AN1445             | Emulated 16-bit slave SP;                                                            |  |  |  |

| AN1475             | Developing an ST72t5x mass storage application                                       |  |  |  |

| AN1504             | Starting a P.V.1 signal directly at high level using the ST7 16-bit timer            |  |  |  |

| AN1602             | 16-bit ti nin g operations using ST7262 or ST7263B ST7 USB MCUs                      |  |  |  |

| AN1633             | Lovice firmware upgrade (DFU) implementation in ST7 non-USB applications             |  |  |  |

| AN1712             | Generating a high resolution sinewave using ST7 PWMART                               |  |  |  |

| AN1713             | SMBus slave driver for ST7 I2C peripherals                                           |  |  |  |

| AN 1750            | Software UART using 12-bit ART                                                       |  |  |  |

| <b>∆</b> №1947     | ST7MC PMAC sine wave motor control software library                                  |  |  |  |

| General purpose    |                                                                                      |  |  |  |

| AN1476             | Low cost power supply for home appliances                                            |  |  |  |

| AN1526             | ST7FLITE0 quick reference note                                                       |  |  |  |

| AN1709             | EMC design for ST Microcontrollers                                                   |  |  |  |

| AN1752             | ST72324 quick reference note                                                         |  |  |  |

| Product evaluation | n                                                                                    |  |  |  |

| AN 910             | Performance benchmarking                                                             |  |  |  |

| AN 990             | ST7 benefits vs industry standard                                                    |  |  |  |

### Table 81. ST7 application notes (continued)