Welcome to E-XFL.COM

## What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

## Details

| Product Status             | Obsolete                                                              |

|----------------------------|-----------------------------------------------------------------------|

| Core Processor             | ST7                                                                   |

| Core Size                  | 8-Bit                                                                 |

| Speed                      | 8MHz                                                                  |

| Connectivity               | -                                                                     |

| Peripherals                | LVD, POR, PWM, WDT                                                    |

| Number of I/O              | 5                                                                     |

| Program Memory Size        | 1KB (1K x 8)                                                          |

| Program Memory Type        | FLASH                                                                 |

| EEPROM Size                | -                                                                     |

| RAM Size                   | 128 x 8                                                               |

| Voltage - Supply (Vcc/Vdd) | 2.4V ~ 5.5V                                                           |

| Data Converters            | A/D 5x10b                                                             |

| Oscillator Type            | Internal                                                              |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                    |

| Mounting Type              | Surface Mount                                                         |

| Package / Case             | 8-SOIC (0.154", 3.90mm Width)                                         |

| Supplier Device Package    | 8-SOIC                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/st7fliteus5m3 |

|                            |                                                                       |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Figure 48.               | Two typical applications with unused I/O pin                                                                                                                                                                                                |                                       |     |

|--------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|-----|

| Figure 49.               | Typical IPU vs. VDD with VIN=VSSI.                                                                                                                                                                                                          |                                       |     |

| Figure 50.               | Typical VOL at VDD = 2.4 V (standard pins)                                                                                                                                                                                                  |                                       |     |

| Figure 51.<br>Figure 52. | Typical VOL at VDD = 3 V (standard pins)<br>Typical VOL at VDD = 5 V (standard pins)                                                                                                                                                        |                                       |     |

| Figure 53.               | Typical VOL at VDD = $2.4 \text{ V}$ (standard pins)                                                                                                                                                                                        |                                       |     |

| Figure 54.               | Typical VOL at VDD = $3 V$ (HS pins)                                                                                                                                                                                                        |                                       |     |

| Figure 55.               | Typical VOL at VDD = $5 V$ (HS pins)                                                                                                                                                                                                        |                                       |     |

| Figure 56.               | Typical VDD-VOH at VDD = 2.4 V (HS pins)                                                                                                                                                                                                    |                                       |     |

| Figure 57.               | Typical VDD-VOH at VDD = 3 V (HS pins)                                                                                                                                                                                                      |                                       |     |

| Figure 58.               | Typical VDD-VOH at VDD = 5 V (HS pins)                                                                                                                                                                                                      |                                       |     |

| Figure 59.               | Typical VOL vs. VDD (HS pins)                                                                                                                                                                                                               |                                       |     |

| Figure 60.<br>Figure 61. | Typical VDD-VOH vs. VDD (HS pins).RESET pin protection when LVD is enabled                                                                                                                                                                  |                                       |     |

| Figure 62.               | RESET pin protection when LVD is disabled                                                                                                                                                                                                   |                                       |     |

| Figure 63.               | Typical application with ADC                                                                                                                                                                                                                |                                       |     |

| Figure 64.               | ADC accuracy characteristics                                                                                                                                                                                                                | · · · · · · · · · · · · · · · · · · · | 117 |

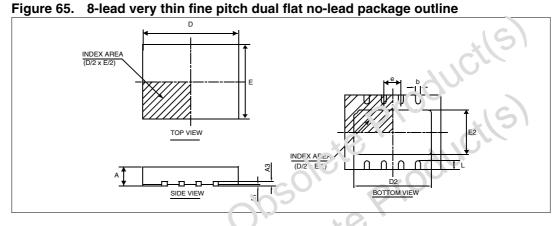

| Figure 65.               | 8-lead very thin fine pitch dual flat no-lead package outline                                                                                                                                                                               |                                       |     |

| Figure 66.               | 8-pin plastic small outline package, 150-mil width package outline                                                                                                                                                                          |                                       |     |

| Figure 67.               | 8-pin plastic dual in-line package, 300-mil width package outline<br>16-pin plastic dual in-line package, 300-mil width, package outline                                                                                                    |                                       |     |

| Figure 69                | Ontion list                                                                                                                                                                                                                                 |                                       | 127 |

|                          | Option list                                                                                                                                                                                                                                 | <u> </u>                              |     |

|                          | 50.00                                                                                                                                                                                                                                       |                                       |     |

|                          |                                                                                                                                                                                                                                             |                                       |     |

|                          |                                                                                                                                                                                                                                             |                                       |     |

|                          | 100                                                                                                                                                                                                                                         |                                       |     |

|                          | (5) 60'                                                                                                                                                                                                                                     |                                       |     |

|                          |                                                                                                                                                                                                                                             |                                       |     |

|                          |                                                                                                                                                                                                                                             |                                       |     |

|                          |                                                                                                                                                                                                                                             |                                       |     |

|                          | 010 16                                                                                                                                                                                                                                      |                                       |     |

|                          |                                                                                                                                                                                                                                             |                                       |     |

|                          |                                                                                                                                                                                                                                             |                                       |     |

|                          |                                                                                                                                                                                                                                             |                                       |     |

| SO.                      | 200                                                                                                                                                                                                                                         |                                       |     |

| $\sim$                   |                                                                                                                                                                                                                                             |                                       |     |

| U.                       | ×0                                                                                                                                                                                                                                          |                                       |     |

|                          | 2°                                                                                                                                                                                                                                          |                                       |     |

| <u> </u>                 | -                                                                                                                                                                                                                                           |                                       |     |

| 203-                     |                                                                                                                                                                                                                                             |                                       |     |

| U Y                      |                                                                                                                                                                                                                                             |                                       |     |

|                          |                                                                                                                                                                                                                                             |                                       |     |

|                          | 8-pin plastic small outline package, 150-mil width package of the<br>8-pin plastic dual in-line package, 300-mil width package outline<br>16-pin plastic dual in-line package, 300-mil width, package outline<br>Option list<br>Option list |                                       |     |

|                          |                                                                                                                                                                                                                                             |                                       |     |

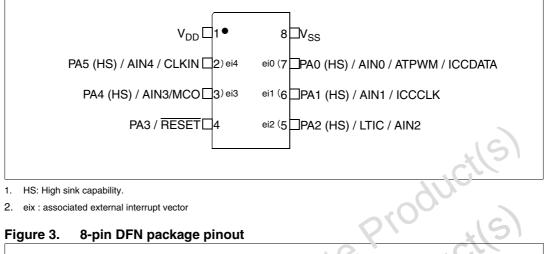

## **Pin description** 2

- eix : as scieted external interrupt vector

In flash devices, this protection is removed by reprogramming the option. In this case, program memory is automatically erased, and the device can be reprogrammed.

Readout protection selection depends on the device type:

- In Flash devices it is enabled and removed through the FMP R bit in the option byte.

- In ROM devices it is enabled by mask option specified in the option list.

#### 4.5.2 Flash Write/Erase protection

Write/erase protection, when set, makes it impossible to both overwrite and erase program memory. Its purpose is to provide advanced security to applications and prevent any change being made to the memory content.

Once set, Write/erase protection can never be removed. Warning: write-protected flash device is no longer reprogrammable.

Write/erase protection is enabled through the FMP W bit in the option byte.

end l<sup>2</sup>C protocol, re . / l<sup>2</sup>C protocol reference Obsolete Product(s) For details on Flash programming and I<sup>2</sup>C protucol, refer to the ST7 Flash programming reference manual and to the ST7 I<sup>2</sup>C protocol reference manual.

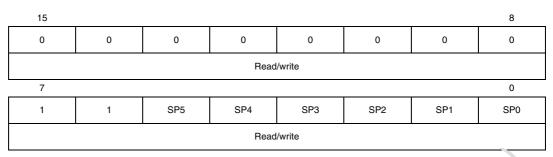

#### 5.3.5 Stack Pointer (SP)

Reset value: 00 FFh

The Stack Pointer is a 16-bit register which is always pointing to the next free location in the stack. It is then decremented after data has been pushed onto the stack and incremented before data is popped from the stack (see Figure 8).

Since the stack is 64 bytes deep, the 10 most significant bits are force 1 by nardware. Following an MCU Reset, or after a Reset Stack Pointer instruction (RSP), the Stack Pointer contains its reset value (the SP5 to SP0 bits are set) which is the stack higher address.

The least significant byte of the Stack Pointer (called S) can be directly accessed by a LD instruction.

## Note: When the lower limit is exceeded, the Stack Fointer wraps around to the stack upper limit. without indicating the stack overflow. The previously stored information is then overwritten and therefore lost. The stack also wrops in case of an underflow.

The stack is used to save the return address during a subroutine call and the CPU context during an interrupt. The user may also directly manipulate the stack by means of the PUSH and POP instructions. Ir. the case of an interrupt, the PCL is stored at the first location pointed to by the SP Then the other registers are stored in the next locations as shown in Figure 8.

- and the context is pushed on the stack. A subroutine call is located at two locations and an interrupt five locations in the stack area.

- Bit 2 RC\_FLAG RC Selection

- This bit is set and cleared by hardware

- 0: No switch from RC to AWU requested

- 1: RC clock activated and temporization completed

- Bit 1 = Reserved, must be kept cleared.

- Bit 0 = **RC/AWU** RC/AWU Selection

- 0: RC enabled

- 1: AWU enabled (default value)

Table 7.Clock register map and reset values

| (Hex.) | Register<br>label       | 7        | 6        | 5        | 4        | 3        | 2            | 1         | 0           |

|--------|-------------------------|----------|----------|----------|----------|----------|--------------|-----------|-------------|

| 0038h  | MCCSR<br>Reset value    | 0        | 0        | 0        | 0        | 0        | 0            | MGO       | SMS<br>0    |

| 0039h  | RCCR<br>reset value     | CR9<br>1 | CR8<br>1 | CR7<br>1 | CR6<br>1 | CR5<br>1 | CF4          | CR3<br>1  | CR2         |

| 003Ah  | SICSR<br>reset value    | 0        | CR1      | CR0      | 0        | 0        | LVDRF<br>x   | AVDF<br>0 | AVDIE<br>0  |

| 003Eh  | AVDTHCR<br>reset value  | CK2<br>0 | CK1<br>0 | СК0<br>0 | 06       | 0 0      | 00           | AVD1<br>1 | AVD2<br>1   |

| 003Fh  | CKCNTCSR<br>reset value | 0        | 0        | 0        | 0        | AWU_FLAG | RC_FLAG<br>0 | 0         | RC/AWU<br>1 |

|        | reset value             | 20       |          |          |          |          |              |           |             |

57

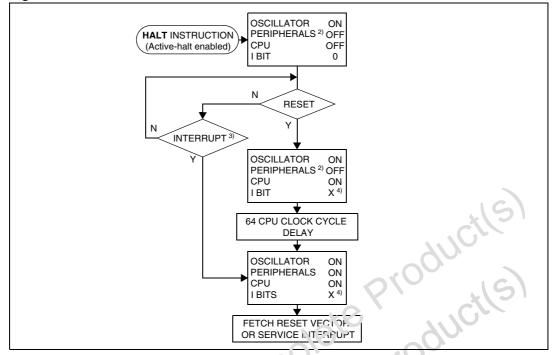

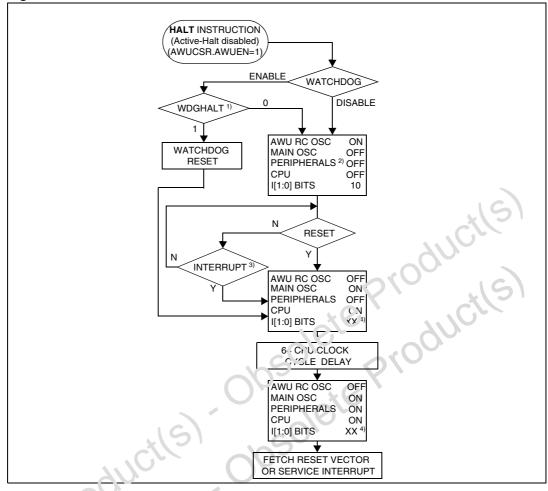

Figure 22. Active-halt mode flowchart

1. This delay occurs only if the MCU exits Active-halt node by means of a reset.

2. Peripherals clocked with an external clock South cr.n still be active.

- 3. Only the Lite Timer RTC and AT Timer interrun's can exit the MCU from Active-halt mode.

- 4. Before servicing an interrupt, the CC register is pushed on the stack. The I bit of the CC register is set during the interrupt routine and cleared when the CC register is popped.

# 8.4.2 Halt mode

The Halt mode s the lowest power consumption mode of the MCU. It is entered by executing the 'HALT' instruction when Active-halt mode is disabled.

The MCU can exit Halt mode on reception of either a specific interrupt (see *Table 9: In errupt mapping*) or a reset. When exiting Halt mode by means of a reset or an interrupt, the main oscillator is immediately turned on and the 64 CPU cycle delay is used to stabilize it. After the start up delay, the CPU resumes operation by servicing the interrupt or by fetching the reset vector which woke it up (see *Figure 24*).

When entering Halt mode, the I bit in the CC register is forced to 0 to enable interrupts. Therefore, if an interrupt is pending, the MCU wakes immediately.

In Halt mode, the main oscillator is turned off causing all internal processing to be stopped, including the operation of the on-chip peripherals. All peripherals are not clocked except the ones which get their clock supply from another clock generator (such as an external or auxiliary oscillator).

The compatibility of watchdog operation with Halt mode is configured by the "WDGHALT" option bit of the option byte. The HALT instruction when executed while the watchdog system is enabled, can generate a watchdog reset (see *Section 14.1: Option bytes* for more details).

- WDGHALT is an option bit. See option byte section for more details. 1.

- 2. Perpheral clocked with an external clock source can still be active.

- Only an AWUFH interrupt and some specific interrupts can exit the MCU from Halt mode (such as external int strupt). Refer to Table 9: Interrupt mapping for more details.

. It Only a. interrup 4. Before s set to the popped. Before servicing an interrupt, the CC register is pushed on the stack. The I[1:0] bits of the CC register are set to the current software priority level of the interrupt routine and recovered when the CC register is

## 9 I/O ports

#### 9.1 Introduction

The I/O port offers different functional modes:

Transfer of data through digital inputs and outputs

and for specific pins:

- External interrupt generation

- Alternate signal input/output for the on-chip peripherals.

An I/O port contains up to 6 pins. Each pin (except PA3/RESET) can be programmed independently as digital input (with or without interrupt generation) or digital output

### 9.2 **Functional description**

Each port has 2 main registers:

- Data register (DR)

- Data Direction register (DDR)

and one optional register:

Option register (OR)

Each I/O pin may be programmed us ng the corresponding register bits in the DDR and OR registers: bit X corresponding to pin X of the port. The same correspondence is used for the DR register.

The following description takes into account the OR register, (for specific ports which do not provide this register refer to the I/O Port Implementation section). The generic I/O block diagram is show: in Figure 28.

#### 9.2.1 Input modes

The input configuration is selected by clearing the corresponding DDR register bit.

In this case, reading the DR register returns the digital value applied to the external I/O pin.

Different input modes can be selected by software through the OR register.

Writing the DR register modifies the latch value but does not affect the pin status.

PA3 cannot be configured as input.

# **External interrupt function**

When an I/O is configured as Input with Interrupt, an event on this I/O can generate an external interrupt request to the CPU.

Each pin can independently generate an interrupt request. The interrupt sensitivity is independently programmable using the sensitivity bits in the EICR register.

External interrupts are hardware interrupts. Fetching the corresponding interrupt vector automatically clears the request latch. Changing the sensitivity of a particular external interrupt clears this pending interrupt. This can be used to clear unwanted pending interrupts.

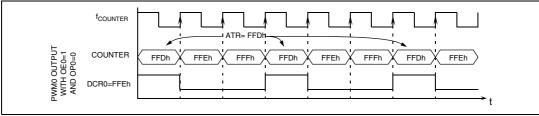

Figure 35. **PWM signal example**

## Output compare mode

To use this function, the OE bit must be 0, otherwise the compare is done with the shadow register instead of the DCRx register. Software must then write a 12-bit value in the DCR0H and DCR0L registers. This value will be loaded immediately (without waiting for an OV) event).

The DCR0H must be written first, the output compare function starts only when the DCR0L value is written.

When the 12-bit upcounter (CNTR) reaches the value stored in .hc DCR0H and DCR0L registers, the CMPF0 bit in the PWM0CSR register is set and an interrupt request is generated if the CMPIE bit is set.

- The output compare function is only available for DGRx values other than 0 (reset value). Note:

- Caution: At each OVF event, the DCRx value is written in a shadow register, even if the DCR0L value has not yet been written (in this case, the sizedow register will contain the new DCR0H value and the old DCR0L value), then:

- If OE=1 (PWM mode); the compare is done between the timer counter and the shadow register (and not DCRx)

- If OE=0 (OCiviF mode): the compare is done between the timer counter and DCRx. There is no PWM signal.

The compare between DCRx or the shadow register and the timer counter is locred until DCR0L is written.

#### 10.2.4 Low power modes

## Table 27. Description of low power modes

| 103                                     | Mode        | Description                                        |

|-----------------------------------------|-------------|----------------------------------------------------|

| )*                                      | Slow        | The input frequency is divided by 32               |

| ~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~ | Wait        | No effect on AT timer                              |

| SO                                      | Active-halt | AT timer halted except if CK0=1, CK1=0 and OVFIE=1 |

| 105                                     | Halt        | AT timer halted                                    |

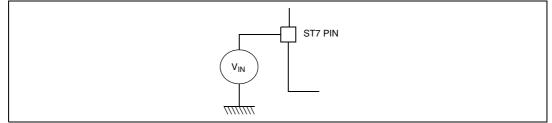

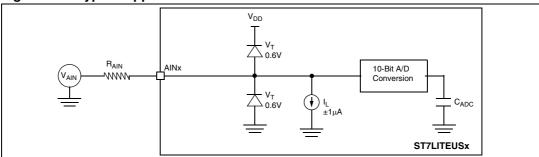

#### 12.1.5 Pin input voltage

The input voltage measurement on a pin of the device is described in *Figure 38*.

## Figure 38. Pin input voltage

#### 12.2 Absolute maximum ratings

Stresses above those listed as "absolute maximum ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device under these conditions is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

1. Directly connecting the I/O pins to  $V_{DD}$  or  $V_{SS}\, \mbox{could Gamage the device if an unexpected}$ change of the I/O configuration occurs (for example due to a corrupted program counter). To guarantee safe operation, this connection has to be done through a pull-up or pull-down resistor (typical: 10 k $\Omega$  for I/Os). Unused 1/O pins must be tied in the same way to V<sub>DD</sub> or V<sub>SS</sub> according to their reset configuration

|                                                                                                                                                      | Symbol                            | Ratings                                            | Maximum value                              | Unit  |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|----------------------------------------------------|--------------------------------------------|-------|--|

|                                                                                                                                                      | V <sub>DD</sub> - V <sub>SS</sub> | S. upply voltage                                   | 7.0                                        | V     |  |

|                                                                                                                                                      | VIN                               | Input voltage on any pin <sup>(1)</sup>            | $V_{SS}\mbox{-}0.3$ to $V_{DD}\mbox{+}0.3$ | v     |  |

|                                                                                                                                                      | VELTD(HBM)                        | Electrostatic discharge voltage (Human Body Model) | see Section 12                             | 2.7.2 |  |

| 016                                                                                                                                                  | V <sub>ESD(MM)</sub>              | Electrostatic discharge voltage (Machine Model)    | see Section 12.7.2                         |       |  |

| <ul> <li><sup>1</sup> <sup>1</sup> <sup>1</sup> <sup>1</sup> <sup>1</sup> <sup>1</sup> <sup>1</sup> <sup>1</sup> <sup>1</sup> <sup>1</sup></li></ul> |                                   |                                                    |                                            |       |  |

Voltage characteristics Table 43.

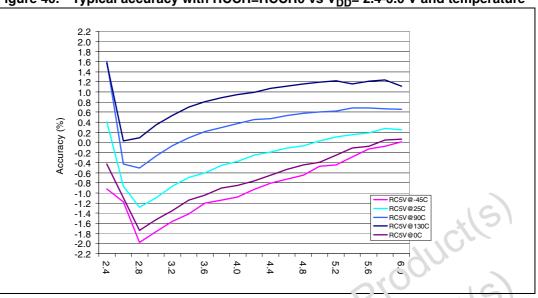

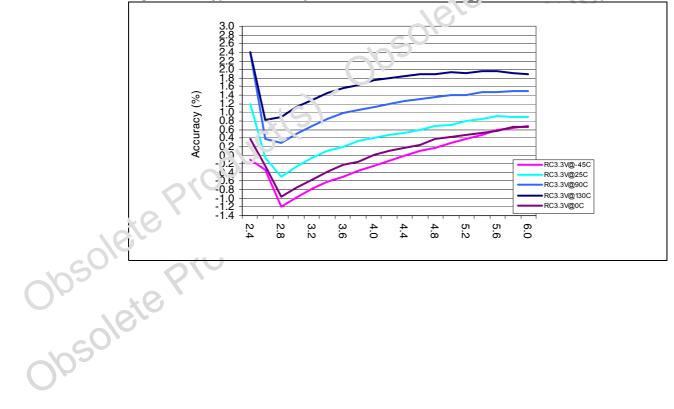

Figure 40. Typical accuracy with RCCR=RCCR0 vs V<sub>DD</sub>= 2.4-6.0 V and temperature

Figure 41. Typical accuracy with RCCR=RCCR1 vs Von= 2.4-6.0V and temperature

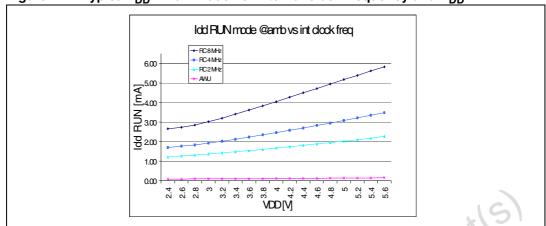

#### 12.4.3 **On-chip peripherals**

Table 54. **On-chip peripheral characteristics**

| Symbol               | Parameter                                              | Conditions                |                         | Тур <sup>(1)</sup> | Unit |

|----------------------|--------------------------------------------------------|---------------------------|-------------------------|--------------------|------|

| 1                    | 12-bit auto-reload timer supply current <sup>(2)</sup> | $f_{CPU} = 4 MHz$         | V <sub>DD</sub> = 3.0 V | 15                 |      |

| DD(AT)               |                                                        | f <sub>CPU</sub> = 8 MHz  | V <sub>DD</sub> = 5.0 V | 30                 | μA   |

| I <sub>DD(ADC)</sub> | ADC supply current when converting <sup>(3)</sup>      | $f_{ADC} = 2 MHz$         | V <sub>DD</sub> = 3.0 V | 450                | μA   |

|                      | ADC supply current when converting V                   | $f_{ADC} = 4 \text{ MHz}$ | V <sub>DD</sub> = 5.0 V | 750                |      |

1. Not tested in production, guaranteed by characterization.

Data based on a differential I<sub>DD</sub> measurement between reset configuration (timer stopped) and the timer running in PWM 2. mode at  $f_{cpu} = 8$  MHz.

3. Data based on a differential IDD measurement between reset configuration and continuous A/D conversions with ampli ier off.

# 12.5

| Table 55. | <b>General timings</b> |

|-----------|------------------------|

|-----------|------------------------|

| Clock                | Clock and timing characteristics                                                                 |                         |      |                    |      |                  |  |  |

|----------------------|--------------------------------------------------------------------------------------------------|-------------------------|------|--------------------|------|------------------|--|--|

| Subject to           | Subject to general operating conditions for $V_{DD}$ , $f_{OSC}$ , and $\mathcal{T}_{\lambda}$ . |                         |      |                    |      |                  |  |  |

| Table 55             | . General timings                                                                                |                         |      | 0                  |      |                  |  |  |

| Symbol               | Parameter <sup>(1)</sup>                                                                         | Con ditions             | Min  | Typ <sup>(2)</sup> | Мах  | Unit             |  |  |

| +                    | Instruction evelo time                                                                           |                         | 2    | 3                  | 12   | t <sub>CPU</sub> |  |  |

| t <sub>c(INST)</sub> | Instruction cycle time                                                                           | <sup>1</sup> CPU=8 MHz  | 250  | 375                | 1500 | ns               |  |  |

| +                    | Interrupt reaction time <sup>(ij)</sup><br>$t_{v(IT)} = \Delta t_{c(II \cup CT)} - 10$           | f <sub>CPU</sub> =8 MHz | 10   |                    | 22   | t <sub>CPU</sub> |  |  |

| t <sub>v(IT)</sub>   |                                                                                                  |                         | 1.25 |                    | 2.75 | μS               |  |  |

1. Data based on the acterization. Not tested in production.

2. Data bas id an typical application software.

Time measured between interrupt event and interrupt vector fetch.  $\Delta t_{c(INST)}$  is the number of  $t_{CPU}$  cycles meded to finish the current instruction execution. 3.

#### Table 56. Auto-wakeup RC oscillator

| 18              | Table 56. Auto-wakeup RC os        | cillator            |     |     |      |      |

|-----------------|------------------------------------|---------------------|-----|-----|------|------|

| 50 <sup>1</sup> | Parameter                          | Conditions          | Min | Тур | Max  | Unit |

| 002             | Supply Voltage Range               |                     | 2.4 | 5.0 | 5.5  | V    |

|                 | Operating Temperature Range        |                     | -40 | 25  | 125  | °C   |

| $O_{l_k}$       | Current Consumption <sup>(1)</sup> | Without prescaler   | 2.0 | 8.0 | 14.0 | μA   |

| abso            | Consumption <sup>(1)</sup>         | AWU RC switched off |     | 0   |      | μA   |

| <b>O</b> P      | Output Frequency <sup>(1)</sup>    |                     | 20  | 33  | 60   | kHz  |

1. Data guaranteed by design.

## 12.6 **Memory characteristics**

$T_A$  = -40 to 125 °C, unless otherwise specified;

| Table 57. | RAM and Hardware registers |

|-----------|----------------------------|

|           |                            |

| Symbol          | Parameter              | Conditions           | Min | Тур | Max | Unit |

|-----------------|------------------------|----------------------|-----|-----|-----|------|

| V <sub>RM</sub> | Data retention mode 1) | Halt mode (or Reset) | 1.6 |     |     | V    |

#### Table 58. **Flash Program memory**

| Symbol            | Parameter                                      | Conditions                                                 | Min                | Тур | Max  | Unit   |

|-------------------|------------------------------------------------|------------------------------------------------------------|--------------------|-----|------|--------|

| V <sub>DD</sub>   | Operating voltage for Flash<br>write/erase     |                                                            | 2.4 <sup>(1)</sup> |     | 5.5  | v      |

| t <sub>prog</sub> | Programming time for 1~32 bytes <sup>(2)</sup> | T <sub>A</sub> =-40 to +125°C                              |                    | 5   | 10   | ms     |

| prog              | Programming time for 1 kByte                   | T <sub>A</sub> =+25°C                                      |                    | 610 | 0.32 | s      |

| t <sub>RET</sub>  | Data retention <sup>(3)</sup>                  | T <sub>A</sub> =+55°C <sup>(4)</sup>                       | 26                 |     | 10   | years  |

| N <sub>RW</sub>   | Write erase cycles                             | T <sub>A</sub> =+25°C                                      | 10k <sup>(5)</sup> |     | 11-  | cycles |

| I <sub>DD</sub>   | Supply current <sup>(6)</sup>                  | Read / Write / Erase<br>modes tobute 8 MHz,<br>Vpp = 5.3 V | 0                  | 90  | 2.6  | mA     |

|                   |                                                | No nead/No Write<br>Mode                                   |                    |     | 100  | μA     |

|                   | 15                                             | Power down mode /<br>Halt                                  |                    | 0   | 0.1  | μA     |

Minimum V<sub>DD</sub> supply vclage vithout losing data stored in RAM (in Halt mode or under reset) or in hardware registers (cnly in Halt mode). Guaranteed by construction, not tested in production. 1.

2. Up to 32 bytes can be programmed at a time.

3. Data based on reliability test results and monitored in production.

- ...d c ...e dr.a ruter 5. Losign target v 3. Guaranteed by 4. The dr.a retention time increases when the  $T_A$  decreases.

- 5. Design target value pending full product characterization.

5. Guaranteed by Design. Not tested in production.

# 12.7 EMC characteristics

Susceptibility tests are performed on a sample basis during product characterization.

# 12.7.1 Functional EMS (electromagnetic susceptibility)

Based on a simple running application on the product (toggling 2 LEDs through I/O ports), the product is stressed by two electromagnetic events until a failure occurs (indicated by the LEDs).

- **ESD**: Electrostatic discharge (positive and negative) is applied on all pins of the device until a functional disturbance occurs. This test conforms with the IEC 1000-4-2 standard.

- **FTB**: A Burst of Fast Transient voltage (positive and negative) is applied to V<sub>DD</sub> and V<sub>SS</sub> through a 100 pF capacitor, until a functional disturbance occurs. This test conforms with the IEC 1000-4-4 standard.

A device reset allows normal operations to be resumed. The test results are given in the table below based on the EMS levels and classes defined in application rote AN1709.

# Designing hardened software to avoid noise problems

EMC characterization and optimization are performed at component level with a typical application environment and simplified MCU software. It should be noted that good EMC performance is highly dependent on the user application and the software in particular.

Therefore it is recommended that the use, applies EMC software optimization and prequalification tests in relation with the EMC level requested for his application.

## Software recommendations

The software flowchart must include the management of runaway conditions such as:

- Corrupted program counter

- Unexpected result

- Critical Data corruption (control registers...)

# Pre-qualification trials

Note: of the common failures (unexpected reset and program counter corruption) can be reproduced by manually forcing a low state on the RESET pin or the Oscillator pins for 1 second.

To complete these trials, ESD stress can be applied directly on the device, over the range of specification values. When unexpected behavior is detected, the software can be hardened to prevent unrecoverable errors occurring (see application note AN1015).

| Symbol            | ool Parameter Conditions                                                                                                          |                                                                                                                    | Level/<br>class |

|-------------------|-----------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|-----------------|

| V <sub>FESD</sub> | Voltage limits to be applied on any I/O pin to induce a functional disturbance                                                    | $V_{DD}=5$ V, $T_A=+25$ °C, $f_{OSC}=8$ MHz,<br>SO8 package,<br>conforms to IEC 1000-4-2                           | 3B              |

| V <sub>FFTB</sub> | Fast transient voltage burst limits to be applied through 100 pF on $V_{DD}$ and $V_{DD}$ pins to induce a functional disturbance | V <sub>DD</sub> =5 V, T <sub>A</sub> =+25 °C, f <sub>OSC</sub> =8 MHz,<br>SO8 package,<br>conforms to IEC 1000-4-4 | 4B              |

Table 59. EMC characteristics

Just

## Figure 63. Typical application with ADC

| Symbol<br>(1)     | Parameter                    | Conditions                                                         | Тур  | Max Jr it |

|-------------------|------------------------------|--------------------------------------------------------------------|------|-----------|

| IE <sub>T</sub> I | Total unadjusted error       |                                                                    | 2.1  | 5.0       |

| IE <sub>O</sub> I | Offset error                 |                                                                    | (°.2 | 2.5       |

| IE <sub>G</sub> I | Gain Error                   | f <sub>CPU</sub> =8 MHz,<br>f <sub>ADC</sub> =4 MHz <sup>(1)</sup> | 2.3  | 1.5 LSB   |

| IE <sub>D</sub> I | Differential linearity error |                                                                    | 1.9  | 3.5       |

| IELI              | Integral linearity error     | 1010                                                               | 1.9  | 4.5       |

1. Data based on characterization results over the whole temperature range.

#### Table 68. ADC accuracy with $V_D$ = 2.7 to 3.3 V

| Symbol<br>(1)     | Parameter                    | Conditions                                                         | Тур | Мах | Unit |

|-------------------|------------------------------|--------------------------------------------------------------------|-----|-----|------|

| IE <sub>T</sub> I | Total unadjusted error       | 5                                                                  | 2.0 | 3.0 |      |

| IE <sub>O</sub> I | Offset er.or                 |                                                                    | 0.1 | 1.5 |      |

| IE <sub>G</sub> I | Gran Error                   | f <sub>CPU</sub> =4 MHz,<br>f <sub>ADC</sub> =2 MHz <sup>(1)</sup> | 0.4 | 1.4 | LSB  |

| IE <sub>D</sub> , | Lifferential linearity error |                                                                    | 1.8 | 2.5 |      |

| 121               | Integral linearity error     |                                                                    | 1.7 | 2.5 |      |

|                | 1-01              | Chiser Chish                            | f <sub>CPU</sub> =4 MHz,<br>f <sub>ADC</sub> =2 MHz <sup>(1)</sup> | 0.1 | 1.5 |      |

|----------------|-------------------|-----------------------------------------|--------------------------------------------------------------------|-----|-----|------|

|                | IE <sub>G</sub> I | Gran Error                              |                                                                    | 0.4 | 1.4 | LSB  |

|                | IE <sub>D</sub> , | Lifferential linearity error            |                                                                    | 1.8 | 2.5 |      |

|                |                   | Integral linearity error                |                                                                    | 1.7 | 2.5 |      |

| 16             | 1. Data ba        | sed on characterization results over th | e whole temperature range.                                         |     |     |      |

| SO             | Table 69.         | ADC accuracy with $V_{DD} =$            | 2.4V to 2.7V                                                       |     |     |      |

| 000            | Symbol<br>(1)     | Parameter                               | Conditions                                                         | Тур | Max | Unit |

| olk            | ΙΕ <sub>Τ</sub> Ι | Total unadjusted error                  |                                                                    | 2.2 | 3.5 |      |

| abso           | IE <sub>O</sub> I | Offset error                            | ]                                                                  | 0.5 | 1.5 |      |

| O <sub>2</sub> | IE <sub>G</sub> I | Gain Error                              | f <sub>CPU</sub> =2 MHz,<br>f <sub>ADC</sub> =1 MHz <sup>(1)</sup> | 0.5 | 1.5 | LSB  |

|                | IE <sub>D</sub> I | Differential linearity error            |                                                                    | 1.8 | 2.5 |      |

|                | ΙΕ <sub>L</sub> Ι | Integral linearity error                |                                                                    | 1.8 | 2.5 |      |

1. Data based on characterization results at a temperature  $\ge 25^{\circ}$ C.

# 13 Package characteristics

In order to meet environmental requirements, ST offers these devices in different grades of ECOPACK<sup>®</sup> packages, depending on their level of environmental compliance. ECOPACK<sup>®</sup> specifications, grade definitions and product status are available at: <u>www.st.com</u>. ECOPACK<sup>®</sup> is an ST trademark.

# 13.1 Package mechanical data

# Table 70. 8-lead very thin fine pitch dual flat no-lead package mechanical data

|               | Dim    |      | Cmn. | 6    |             | inches <sup>(1)</sup> |        |

|---------------|--------|------|------|------|-------------|-----------------------|--------|

|               | Dim. – |      | Тур  | Max  | Min         | Тур                   | Мах    |

|               | А      | 0.90 | 0.90 | 1.00 | 0.0310      | 0.0350                | 0.0390 |

|               | A      | 0.00 | 0.02 | 0.05 | 0.0000      | 0.0010                | 0.0020 |

|               | A3     | Ċ    | 0.20 |      |             | 0.0080                |        |

| 10            | b      | 0.25 | 0.30 | 0.35 | 0.0100      | 0.0120                | 0.0140 |

| $cO^{\prime}$ | D      | 00   | 4.50 |      |             | 0.1770                |        |

| 005           | D2     | 3.50 | 3.65 | 3.75 | 0.1380      | 0.1440                | 0.1480 |

| 0.            | X CE   |      | 3.50 |      |             | 0.1380                |        |

| 26            | E2     | 1.96 | 2.11 | 2.21 | 0.0770      | 0.0830                | 0.0870 |

| 50.           | е      |      | 0.80 |      |             | 0.0310                |        |

| 00-           | L      | 0.30 | 0.40 | 0.50 | 0.0120      | 0.0160                | 0.0200 |

|               |        |      |      | Numl | ber of pins |                       |        |

|               | Ν      |      |      |      | 8           |                       |        |

1. Values in inches are converted from mm and rounded to 4 decimal digits.

#### Table 75. Startup clock selection

| Configuration                | CKSEL1 | CKSEL0 |

|------------------------------|--------|--------|

| Internal RC as Startup Clock | 0      | 0      |

| Reserved                     | 0      | 0      |

| AWU RC as a Startup Clock    | 0      | 1      |

| Reserved                     | 1      | 0      |

| External Clock on pin PA5    | 1      | 1      |

#### Table 76. LVD threshold configuration

| Configuration                        | LVD1 | LVD0       |  |  |

|--------------------------------------|------|------------|--|--|

| LVD Off                              | 1    | 51         |  |  |

| Highest voltage threshold            |      | 0          |  |  |

| Medium voltage threshold             | Ū    | 1          |  |  |

| Lowest voltage threshold             | 0    | <b>C</b> 0 |  |  |

| OPTION BYTE 0                        |      |            |  |  |

| Bits 7:4 Reserved, must always be 1. | C    |            |  |  |

| Bit 3 Reserved, must alway be ).     |      |            |  |  |

|                                      |      |            |  |  |

#### 14.1.2 **OPTION BYTE 0**

- Bits 7:4 Reserved, must always be 1

- Bit 3 Reserved, must always be 7.

- Bit 2 SEC0 Sector 0 size definition This option bit indicates the size of sector 0 according to the following table (see Table 77: Definition of sector 0 size).

## Bit 1 FMP R Geadout protection

Reac out protection, when selected provides a protection against program memory content extraction and against write access to Flash memory. Erasing the option bytes when the FMP\_R option is selected will cause the whole memory to be erased first, and the device can be reprogrammed. Refer to Section 4.5 and the ST7 Flash Programming Reference Manual for more details.

- 0: Readout protection off

- 1: Readout protection on

## Bit 0 FMP\_W FLASH write protection

This option indicates if the FLASH program memory is write protected. Warning: When this option is selected, the program memory (and the option bit itself) can never be erased or programmed again.

- 0: Write protection off

- 1: Write protection on

# Obsolete P Bit Definition of sector 0 size

| Sector 0 Size | SEC0 |

|---------------|------|

| 0.5k          | 0    |

| 1k            | 1    |

## ST7LITEUS2, ST7LITEUS5

| Supported                  | In-circuit Deb<br>serie              | ougger, RLink<br>es <sup>(1)</sup> | Emul                             | ator              | Program                                      | ming tool                       |

|----------------------------|--------------------------------------|------------------------------------|----------------------------------|-------------------|----------------------------------------------|---------------------------------|

| products                   | Starter kit<br>without demo<br>board | Starter kit with<br>Demo Board     | DVP series                       | EMU series        | In-circuit<br>programmer                     | ST socket<br>boards and<br>EPBs |

| ST7FLITEUS2<br>ST7FLITEUS5 | STX-RLINK <sup>(2)</sup>             | STFLITE-<br>SK/RAIS <sup>(2)</sup> | ST7MDT10-<br>DVP3 <sup>(3)</sup> | ST7MDT10-<br>EMU3 | STX-RLINK<br>ST7-<br>STICK <sup>(5)(4)</sup> | ST7SB10-<br>SU0 <sup>(5)</sup>  |

#### Table 80. Development tool order codes for the ST7LITEUSx family

1. Available from ST or from Raisonance, www.raisonance.com.

USB connection to PC. 2.

## 14.4 ST7 application notes

#### Table 81. ST7 application notes

| 2. USB connection t                                         | io PC.                                                                                                                               |  |  |

|-------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|--|--|

| <ol> <li>Includes connecti<br/>guide for connect</li> </ol> | ion kit for Plastic DIP16/SO16 only. See "How to order an EMU or DVP" in ST product and tool selection ion kit ordering information. |  |  |

| 4. Parallel port conn                                       | nection to PC.                                                                                                                       |  |  |

| 14.4 ST                                                     | <ul> <li>application notes</li> </ul>                                                                                                |  |  |

| Identification                                              | Description                                                                                                                          |  |  |

| Application exam                                            | nples                                                                                                                                |  |  |

| AN1658                                                      | Serial numbering implementation                                                                                                      |  |  |

| AN1720                                                      | Managing the readout protection in flash microcontrollers                                                                            |  |  |

| AN1755                                                      | A high resolution/precision thermometer using ST7 and NE555                                                                          |  |  |

| AN1756                                                      | Choosing a LAU implementation strategy with ST7DALI                                                                                  |  |  |

| AN1812                                                      | A hig'l precision, low cost, single supply ADC for positive and negative input voltages                                              |  |  |

| Example drivers                                             | P. ctle                                                                                                                              |  |  |

| AN 969                                                      | SCI communication between ST7 and PC                                                                                                 |  |  |

| AN 970                                                      | SPI communication between ST7 and EEPROM                                                                                             |  |  |

| Ai 1071                                                     | I <sup>2</sup> C communication between ST7 and M24Cxx EEPROM                                                                         |  |  |

| AN 972                                                      | ST7 software SPI master communication                                                                                                |  |  |

| AN 973                                                      | SCI software communication with a PC using ST72251 16-bit timer                                                                      |  |  |

| AN 974                                                      | Real time clock with ST7 Timer Output Compare                                                                                        |  |  |

| AN 976                                                      | Driving a buzzer through ST7 timer PWM function                                                                                      |  |  |

| AN 979                                                      | Driving an analog keyboard with the ST7 ADC                                                                                          |  |  |

| AN 980                                                      | ST7 keypad decoding techniques, implementing wakeup on keystroke                                                                     |  |  |

| AN1017                                                      | Using the ST7 universal serial bus microcontroller                                                                                   |  |  |

| AN1041                                                      | Using ST7 PWM signal to generate analog output (sinusoïd)                                                                            |  |  |

| AN1042                                                      | 1042 ST7 routine for I <sup>2</sup> C slave mode management                                                                          |  |  |

## Please Read Carefully:

Information in this document is provided solely in connection with ST products. STMicroelectronics NV and its subsidia. ec (ST") reserve the right to make changes, corrections, modifications or improvements, to this document, and the products and ser ice's doscribed herein at any time, without notice.

All ST products are sold pursuant to ST's terms and conditions of sale.

Purchasers are solely responsible for the choice, selection and use of the ST products and solvices described herein, and ST assumes no liability whatsoever relating to the choice, selection or use of the ST products and services described herein.

No license, express or implied, by estoppel or otherwise, to any intellectual property 1.9, is is granted under this document. If any part of this document refers to any third party products or services it shall not be deemed a licer se grant by ST for the use of such third party products or services, or any intellectual property contained therein or considered as a tria ranty covering the use in any manner whatsoever of such third party products or services or any intellectual property contained therein or considered as a tria ranty covering the use in any manner whatsoever of such third party products or services or any intellectual property contained to the trian the trian trian.

UNLESS OTHERWISE SET FORTH IN ST'S TERMS AND CONDITIONS OF SALE ST DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY WITH RESPECT TO THE USE AND/OR BALE OF ST PRODUCTS INCLUDING WITHOUT LIMITATION IMPLIED WARRANTIES OF MERCHANTABILITY, FITNE'SS FOP A PARTICULAR PURPOSE (AND THEIR EQUIVALENTS UNDER THE LAWS OF ANY JURISDICTION), OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.

UNLESS EXPRESSLY APPROVED IN VIRITING BY AN AUTHORIZED ST REPRESENTATIVE, ST PRODUCTS ARE NOT RECOMMENDED, AUTHORIZED OR WARRANTED FOR USE IN MILITARY, AIR CRAFT, SPACE, LIFE SAVING, OR LIFE SUSTAINING APPLICATIONS, NOR IN PRCD JC 'S OR SYSTEMS WHERE FAILURE OR MALFUNCTION MAY RESULT IN PERSONAL INJURY, DEATH, OR SEVERE PF OP IN TY OR ENVIRONMENTAL DAMAGE. ST PRODUCTS WHICH ARE NOT SPECIFIED AS "AUTOMOTIVE GRADE" MAY ONLY BE USED IN AUTOMOTIVE APPLICATIONS AT USER'S OWN RISK.

Resale of S. p or ucts with provisions different from the statements and/or technical features set forth in this document shall immediately void any war any granted by ST for the ST product or service described herein and shall not create or extend in any manner whatsoever, any liability of ST.

ST and the ST logo are trademarks or registered trademarks of ST in various countries.

Information in this document supersedes and replaces all information previously supplied.

The ST logo is a registered trademark of STMicroelectronics. All other names are the property of their respective owners.

© 2009 STMicroelectronics - All rights reserved

STMicroelectronics group of companies

Australia - Belgium - Brazil - Canada - China - Czech Republic - Finland - France - Germany - Hong Kong - India - Israel - Italy - Japan -Malaysia - Malta - Morocco - Singapore - Spain - Sweden - Switzerland - United Kingdom - United States of America

www.st.com