Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                          |

|----------------------------|--------------------------------------------------------------------------|

|                            |                                                                          |

| Product Status             | Obsolete                                                                 |

| Core Processor             | ST7                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 8MHz                                                                     |

| Connectivity               | -                                                                        |

| Peripherals                | LVD, POR, PWM, WDT                                                       |

| Number of I/O              | 5                                                                        |

| Program Memory Size        | 1KB (1K x 8)                                                             |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | -                                                                        |

| RAM Size                   | 128 x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 2.4V ~ 5.5V                                                              |

| Data Converters            | A/D 5x10b                                                                |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 8-VDFN Exposed Pad                                                       |

| Supplier Device Package    | -                                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/st7fliteus5u6-tr |

|       |       | 12.8.1     | General characteristics                           |

|-------|-------|------------|---------------------------------------------------|

|       |       | 12.8.2     | Output driving current characteristics            |

|       | 12.9  | Control    | pin characteristics                               |

|       | 12.10 | ADC ch     | aracteristics 115                                 |

| 13    | Packa | age cha    | racteristics118                                   |

|       | 13.1  | Packag     | e mechanical data118                              |

|       | 13.2  | Therma     | d characteristics                                 |

| 14    | Devic | e confi    | guration and ordering information                 |

|       | 14.1  | Option     | bytes 123                                         |

|       |       | 14.1.1     | OPTION BYTE 1                                     |

|       |       | 14.1.2     | OPTION BYTE 0                                     |

|       | 14.2  | Orderin    | g information                                     |

|       | 14.3  | Develop    | oment tools                                       |

|       |       | 14.3.1     | Starter kits                                      |

|       |       | 14.3.2     | Development and deburging tools                   |

|       |       | 14.3.3     | Programming tools                                 |

|       |       | 14.3.4     | Order codes for uevelopment and programming tools |

|       | 14.4  | -          | plication nores                                   |

| 15    |       |            | mions 133                                         |

| opsol | Revis | on his     | tory                                              |

| 10    | 40    | . 011 1113 | 104                                               |

|       | 3,    | .0         | 90.                                               |

| 2050  | •     | 010        |                                                   |

| Ob    | 18 ×  |            |                                                   |

|       | S     |            |                                                   |

| 1250° |       |            |                                                   |

| Oh    |       |            |                                                   |

|       |       |            |                                                   |

|       |       |            |                                                   |

## List of tables

| Table 1.  | Device summary                                                                           | . 1 |

|-----------|------------------------------------------------------------------------------------------|-----|

| Table 2.  | Device pin description                                                                   | 14  |

| Table 3.  | Hardware register map                                                                    |     |

| Table 4.  | FLASH register map and reset values                                                      | 22  |

| Table 5.  | Predefined RC oscillator calibration values                                              |     |

| Table 6.  | Internal RC prescaler selection bits                                                     | 32  |

| Table 7.  | Clock register map and reset values                                                      | 33  |

| Table 8.  | Multiplexed IO register map and reset values                                             | 38  |

| Table 9.  | Interrupt mapping                                                                        |     |

| Table 10. | Interrupt sensitivity bits                                                               | 42  |

| Table 11. | Description of low power modes                                                           | 46  |

| Table 12. | Description of interrupt events                                                          | 46  |

| Table 13. | System integrity register map and reset values                                           | 47  |

| Table 14. | Enabling/disabling Active-halt and Halt modes                                            | 50  |

| Table 15. | Configuring the dividing factor                                                          | 58  |

| Table 16. | AWU register map and reset values                                                        | 58  |

| Table 17. | DR register value and output pin status                                                  | 60  |

| Table 18. | I/O port mode options                                                                    | 62  |

| Table 19. | I/O port configurations                                                                  | 62  |

| Table 20. | Effect of low power modes on I/O ports                                                   | 63  |

| Table 21. | Description of interrupt events                                                          | 63  |

| Table 22. | Port configuration                                                                       | 64  |

| Table 23. | I/O port register map and reset values                                                   | 64  |

| Table 24. | Description of low power modes                                                           | 68  |

| Table 25. | Interrupt events                                                                         | 68  |

| Table 26. | Lite timer register map and reset values                                                 |     |

| Table 27. | Description of low po ver modes                                                          | 73  |

| Table 28. | Interrupt events                                                                         | 74  |

| Table 29. | Counter chick selection                                                                  | 75  |

| Table 30. | Register map and reset values                                                            | 77  |

| Table 31. | Effect of low power modes                                                                | 81  |

| Table 32. | Chainel selection                                                                        | 82  |

| Table 33. | Configuring the ADC clock speed                                                          | 83  |

| Table 34. | ADC register map and reset values                                                        | 83  |

| ahle 35.  | Description of addressing modes                                                          | 84  |

| Table 36. | ST7 addressing mode overview                                                             |     |

| Table 37. | Instructions supporting inherent addressing mode                                         |     |

| Table 38. | Instructions supporting inherent immediate addressing mode                               | 86  |

| Table 39. | Instructions supporting direct, indexed, indirect and indirect indexed addressing modes. | 87  |

| Table 40. | Instructions supporting relative modes                                                   | 88  |

| Table 41. | ST7 instruction set                                                                      | 88  |

| Table 42. | Illegal opcode detection                                                                 | 89  |

| Table 43. | Voltage characteristics                                                                  | 93  |

| Table 44. | Current characteristics                                                                  | 94  |

| Table 45. | Thermal characteristics                                                                  |     |

| Table 46. | General operating conditions                                                             |     |

| Table 47. | Operating characteristics with LVD                                                       |     |

| Table 48. | Operating characteristics with AVD                                                       | 96  |

577

In flash devices, this protection is removed by reprogramming the option. In this case, program memory is automatically erased, and the device can be reprogrammed.

Readout protection selection depends on the device type:

- In Flash devices it is enabled and removed through the FMP R bit in the option byte.

- In ROM devices it is enabled by mask option specified in the option list.

#### 4.5.2 Flash Write/Erase protection

Write/erase protection, when set, makes it impossible to both overwrite and erase program memory. Its purpose is to provide advanced security to applications and prevent any change being made to the memory content.

Once set, Write/erase protection can never be removed. Warning: write-protected flash device is no longer reprogrammable.

Write/erase protection is enabled through the FMP W bit in the oution byte.

and I<sup>2</sup>C protocol, re. / I<sup>2</sup>C protocol reference For details on Flash programming and I<sup>2</sup>C protocol, refer to the ST7 Flash programming reference manual and to the ST7 I<sup>2</sup>C proteon reference manual.

## 4.7 Register description

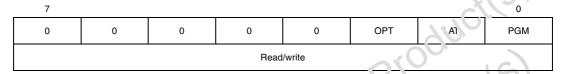

## 4.7.1 Flash Control/Status register (FCSR)

This register controls the XFlash erasing and programming using ICP, IAP or other programming methods.

1st RASS Key: 0101 0110 (56h) 2nd RASS Key: 1010 1110 (AEh)

When an EPB or another programming tool is used (in socket or ICP mode), the RASS keys

are sent automatically.

Reset value: 000 0000 (00h)

Table 4. FLASH register map and reset values

|        | Tubic 4.          | I LACIII               | egiotei i | map and | i i coct vi | uiucs |    |          |          |          |

|--------|-------------------|------------------------|-----------|---------|-------------|-------|----|----------|----------|----------|

|        | Address<br>(Hex.) | Register<br>Label      | 7         | 6       | 5           |       | 3  | 20       | 1        | 0        |

|        | 002Fh             | FCSR<br>Reset<br>value | 0         | 0       | 00          | 0     | 80 | OPT<br>0 | LAT<br>0 | PGM<br>0 |

|        | ucils) obsole     |                        |           |         |             |       |    |          |          |          |

|        | 0                 | login                  | .16       |         |             |       |    |          |          |          |

| 2/6    | 16,               | Odi                    | CIL       |         |             |       |    |          |          |          |

| Obsole | *eP               | (0)                    |           |         |             |       |    |          |          |          |

| 5/50/8 | 3                 |                        |           |         |             |       |    |          |          |          |

| OA     |                   |                        |           |         |             |       |    |          |          |          |

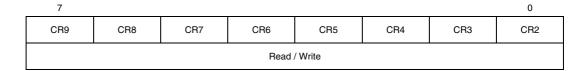

#### 6.3.2 **RC Control register (RCCR)**

Reset value: 1111 1111 (FFh)

### Bits 7:0 CR[9:2] RC Oscillator Frequency Adjustment Bits

These bits, as well as CR[1:0] bits in the SICSR register must be written immediately after reset to adjust the RC oscillator frequency and to obtain the required accuracy. The application can store the correct value for each voltage range in Flash memory and write it to this register at startup.

00h = maximum available frequency

FFh = lowest available frequency

Note: To tune the oscillator, write a series of different value in the register until the correct frequency is reached. The fastest method is to use a dichotomy starting with 80h.

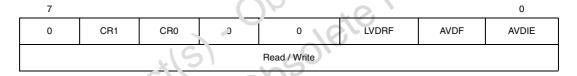

#### 6.3.3 System Integrity (SI) Control/status register (SICSR)

Reset value: 0000 0x00 (0xh)

- Bit 7 Reserved, must be kept cleared.

- Dits, as well as CR[9:2] bits in the RCCR registry immediately after reset to adjust the RC oscillator frequency accuracy. Refer to Section 6.2 on page 28.

Bits 4:3 Reserved, must be kept cleared.

Bits 2:0 System Integrity bits. Refer to Section 7.4 on page 43. These bits, as well as CR[9:2] bits in the RCCR register must be written immediately after reset to adjust the RC oscillator frequency and to obtain the

RESET WATCHDOG RESET

| PULSE | ILLEGAL OPCODE RESET 1)

| LVD RESET |

Figure 12. Reset block diagram

1. Section 11.2.1: Illegal opcode reset for more details on illegal opcode reset conditions

## 6.4.2 Asynchronous external RESET pin

The RESET pin is both an input and an open-drain outout with integrated R<sub>ON</sub> weak pull-up resistor. This pull-up has no fixed value but varies in accordance with the input voltage. It can be pulled low by external circuitry to reset the decide. See Electrical Characteristic section for more details.

A  $\overline{\text{RESET}}$  signal originating from an external source must have a duration of at least  $t_{h(RSTL)in}$  in order to be recognized (see Figure 13). This detection is asynchronous and therefore the MCU can enter reset state even in Halt mode.

The RESET pin is an asyr concous signal which plays a major role in EMS performance. In a noisy environment, it is recommended to follow the guidelines mentioned in the electrical characteristics section.

### 6.4.3 External Fewer-on reset

If the LVD is disabled by option byte, to start up the microcontroller correctly, the user must ensure by means of an external reset circuit that the reset signal is held low until  $V_{DD}$  is over the minimum level specified for the selected  $f_{CLKIN}$  frequency.

A proper reset signal for a slow rising  $V_{DD}$  supply can generally be provided by an external RC network connected to the  $\overline{\text{RESET}}$  pin.

### 6.4.4 Internal low voltage detector (LVD) reset

Two different reset sequences caused by the internal LVD circuitry can be distinguished:

- Power-on reset

- Voltage Drop reset

The device  $\overline{RESET}$  pin acts as an output that is pulled low when  $V_{DD} < V_{IT+}$  (rising edge) or  $V_{DD} < V_{IT-}$  (falling edge) as shown in *Figure 13*.

The LVD filters spikes on V<sub>DD</sub> larger than t<sub>q(VDD)</sub> to avoid parasitic resets.

Note: 1 These 8 bits can be written only when the I bit in the CC register is set.

2 Changing the sensitivity of a particular external interrupt clears this pending interrupt. This can be used to clear unwanted pending interrupts. Refer to Section: External interrupt function.

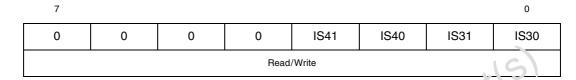

### 7.3.2 External Interrupt Control register 2 (EICR2)

Reset value: 0000 0000 (00h)

Bits 7:4 Reserved

Bits 3:2 IS4[1:0] ei4 sensitivity

These bits define the interrupt sensitivity for eil according to Table 10.

Bits 1:0 IS3[1:0] ei3 sensitivity

These bits define the interrupt sensitivity for the according to Table 10.

Note: 1 These 8 bits can be written only when the I bit ir ເກັບ CC register is set.

- 2 Changing the sensitivity of a particular external interrupt clears this pending interrupt. This can be used to clear unwanted pending interrupts. Refer to Section: External interrupt function.

- 3 IS4[1:0] = 01 is the only safe configuration to avoid spurious interrupt in Halt and AWUFH modes.

Table 10. Interrupt sensitivity bits

|        | ISx1 IS | 13    | External interrupt sensitivity |

|--------|---------|-------|--------------------------------|

|        | 0 0     | *(5)  | Falling edge & low level       |

|        | 1       | 1.100 | Rising edge only               |

| 76     | 1 (     | 20    | Falling edge only              |

| 1050.  | 10      | ,     | Rising and falling edge        |

| 00     | (8)     |       |                                |

| Opsole | ,       |       |                                |

#### 7.4.3 Low power modes

Table 11. **Description of low power modes**

| Mode | Description                                                                                                       |

|------|-------------------------------------------------------------------------------------------------------------------|

| Wait | No effect on SI. AVD interrupts cause the device to exit from Wait mode.                                          |

| Halt | The SICSR register is frozen. The AVD remains active but the AVD interrupt cannot be used to exit from Halt mode. |

### Interrupts

The AVD interrupt event generates an interrupt if the corresponding Enable Control Bit (AVDIE) is set and the interrupt mask in the CC register is reset (RIM instruction).

Table 12. **Description of interrupt events**

| Interrupt Event | Event flag | Enable control bit | Exit fiolo<br>Valt | Exit from<br>Halt |

|-----------------|------------|--------------------|--------------------|-------------------|

| AVD event       | AVDF       | AVDIE              | Yes                | No                |

#### 7.4.4 **Register description**

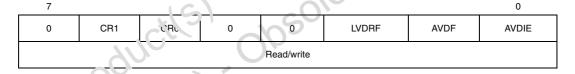

## System Integrity (SI) Control/Status regimer (SICSR

Reset value: 0000 0x00 (0xh)

3it 7 Reserved, must be kept cleared.

Obsolete F Bits 6:5 CR[1:0] RC Oscillator Frequency Adjustment bits

These bits, as well as CR[9:2] bits in the RCCR register must be written immediately after reset to adjust the RC oscillator frequency and to obtain the required accuracy. Refer to Section 6.2: Internal RC oscillator adjustment on page 28.

Bits 4:3 Reserved, must be kept cleared.

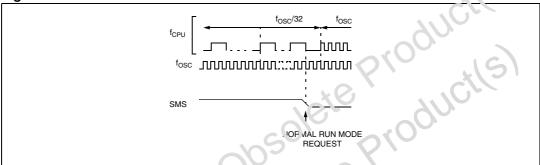

#### 8.2 Slow mode

This mode has two targets:

- To reduce power consumption by decreasing the internal clock in the device,

- To adapt the internal clock frequency (f<sub>CPU</sub>) to the available supply voltage.

Slow mode is controlled by the SMS bit in the MCCSR register which enables or disables Slow mode.

In this mode, the oscillator frequency is divided by 32. The CPU and peripherals are clocked at this lower frequency.

Note:

Slow-wait mode is activated when entering Wait mode while the device is already in Slow mode.

Figure 19. Slow mode clock transition

#### 8.3 Wait mode

Wait mode places the MCU in a low power consumption mode by stopping the CPU.

This power saving mode is selected by calling the 'WFI' instruction.

All perion erac remain active. During Wait mode, the I bit of the CC register is cleared, to enable all interrupts. All other registers and memory remain unchanged. The MCU remains ne MCU will remain in Wait mode until a Reset or an Interrupt of Refer to Figure 20 for a description of the Wait mode flowchart. in Wait mode until an interrupt or reset occurs, whereupon the Program Counter branches to

The MCU will remain in Wait mode until a Reset or an Interrupt occurs, causing it to wakeup.

Table 15. Configuring the dividing factor

|            | <u> </u>        |

|------------|-----------------|

| AWUPR[7:0] | Dividing factor |

| 00h        | Forbidden       |

| 01h        | 1               |

|            |                 |

| FEh        | 254             |

| FFh        | 255             |

In AWU mode, the period that the MCU stays in Halt Mode (t<sub>AWU</sub> in Figure 26) is defined by

$$t_{AWU} = 64 \times AWUPR \times \frac{1}{f_{AWURC}} + t_{RCSTRT}$$

This prescaler register can be programmed to modify the time that the MCU stays in Halt mode before waking up automatically.

Note:

If 00h is written to AWUPR, depending on the product, an intercupt is generated immediately after a HALT instruction, or the AWUPR remains unchanged.

Table 16. AWU register map and reset values

|                              | WUP R7 | AW'JP<br>R6<br>1 | AWUP<br>R5<br>1 | 4<br>AWUP<br>R4<br>1 | AWUP<br>R3<br>1 | AWUP<br>R2<br>1<br>AWUF | AWUP<br>R1<br>1 | AWUP<br>R0<br>1<br>AWUE<br>N |

|------------------------------|--------|------------------|-----------------|----------------------|-----------------|-------------------------|-----------------|------------------------------|

| eset<br>lue<br>WUCSR<br>eset | R7     | R6<br>1          | R5<br>1         | R4<br>1              | R3<br>1         | R2<br>1                 | R1<br>1         | R0<br>1<br>AWUE              |

| eset                         | 0      | 0                | 0               | 0                    | 0               | AWUF                    | AWUM            |                              |

|                              | x1S    |                  | •               | •                    |                 |                         |                 |                              |

| 1.16                         |        |                  |                 |                      |                 |                         |                 |                              |

| ogini                        |        |                  |                 |                      |                 |                         |                 |                              |

|                              |        |                  |                 |                      |                 |                         |                 |                              |

|                              |        |                  |                 |                      |                 |                         |                 |                              |

|                              |        |                  |                 |                      |                 |                         |                 |                              |

#### 9 I/O ports

#### 9.1 Introduction

The I/O port offers different functional modes:

Transfer of data through digital inputs and outputs

and for specific pins:

- External interrupt generation

- Alternate signal input/output for the on-chip peripherals.

An I/O port contains up to 6 pins. Each pin (except PA3/RESET) can be programmed independently as digital input (with or without interrupt generation) or digital output

#### 9.2 **Functional description**

Each port has 2 main registers:

- Data register (DR)

- Data Direction register (DDR)

and one optional register:

Option register (OR)

ponding he a Each I/O pin may be programmed using the corresponding register bits in the DDR and OR registers: bit X corresponding to pin X of the port. The same correspondence is used for the DR register.

The following description takes into account the OR register, (for specific ports which do not provide this register refer to the I/O Port Implementation section). The generic I/O block diagram is show: in Figure 28.

#### 9.2.1 Input modes

The input configuration is selected by clearing the corresponding DDR register bit.

In this case, reading the DR register returns the digital value applied to the external I/O pin.

Different input modes can be selected by software through the OR register.

Writing the DR register modifies the latch value but does not affect the pin status.

PA3 cannot be configured as input.

### **External interrupt function**

When an I/O is configured as Input with Interrupt, an event on this I/O can generate an external interrupt request to the CPU.

Each pin can independently generate an interrupt request. The interrupt sensitivity is independently programmable using the sensitivity bits in the EICR register.

External interrupts are hardware interrupts. Fetching the corresponding interrupt vector automatically clears the request latch. Changing the sensitivity of a particular external interrupt clears this pending interrupt. This can be used to clear unwanted pending interrupts.

#### Bit 2 WDGRF Force Reset/ Reset Status Flag

This bit is used in two ways: it is set by software to force a watchdog reset. It is set by hardware when a watchdog reset occurs and cleared by hardware or by software. It is cleared by hardware only when an LVD reset occurs. It can be cleared by software after a read access to the LTCSR register.

- 0: No watchdog reset occurred.

- 1: Force a watchdog reset (write), or, a watchdog reset occurred (read).

#### Bit 1 WDGE Watchdog Enable

This bit is set and cleared by software.

- 0: Watchdog disabled

- 1: Watchdog enabled

#### Bit 0 WDGD Watchdog Reset Delay

This bit is set by software. It is cleared by hardware at the end of each WDG period.

- 0: Watchdog reset not delayed

- 1: Watchdog reset delayed

### **Lite Timer Input Capture register (LTICR)**

Reset value: 0000 0000 (00h)

### Bit 7:0 ICR[7:0] Input capture value

These bits are lead by software and cleared by hardware after a reset. If the ICF bit in the LFCSh is cleared, the value of the 8-bit up-counter will be captured when a rising or falling edge occurs on the LTIC pin.

Table 26. Lite timer register map and reset values

| Address<br>(Hex.) | Register label | 7    | 6    | 5    | 4    | 3    | 2     | 1    | 0    |

|-------------------|----------------|------|------|------|------|------|-------|------|------|

| 95                | LTCSR          | ICIE | ICF  | TB   | TBIE | TBF  | WDGRF | WDGE | WDGD |

|                   | Reset value    | 0    | 0    | 0    | 0    | 0    | x     | 0    | 0    |

| ос                | LTICR          | ICR7 | ICR6 | ICR5 | ICR4 | ICR3 | ICR2  | ICR1 | ICR0 |

|                   | Reset value    | 0    | 0    | 0    | 0    | 0    | 0     | 0    | 0    |

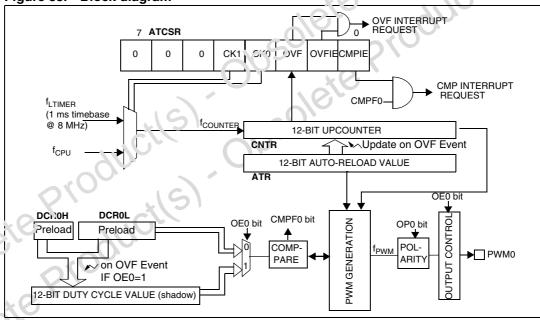

## 10.2 12-bit auto-reload timer (AT)

### 10.2.1 Introduction

The 12-bit auto-reload timer can be used for general-purpose timing functions. It is based on a free-running 12-bit upcounter with a PWM output channel.

#### 10.2.2 Main features

- 12-bit upcounter with 12-bit auto-reload register (ATR)

- Maskable overflow interrupt

- PWM signal generator

- Frequency range 2 kHz 4 MHz (@ 8 MHz f<sub>CPU</sub>)

- Programmable duty-cycle

- Polarity control

- Maskable compare interrupt

- Output compare function

Figure 33. Block diagram

### 10.2.3 Functional description

#### **PWM** mode

This mode allows a pulse width modulated signals to be generated on the PWM0 output pin with minimum core processing overhead. The PWM0 output signal can be enabled or disabled using the OE0 bit in the PWMCR register. When this bit is set the PWM I/O pin is configured as output push-pull alternate function.

Note: CMPF0 is available in PWM mode (see Section : PWM0 control/status register (PWM0CSR)).

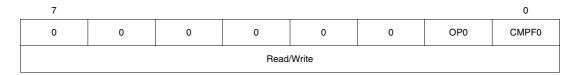

## PWM0 control/status register (PWM0CSR)

Reset value: 0000 0000 (00h)

Bit 7:2 Reserved, must be kept cleared.

### Bit 1 **OP0** PWM0 output polarity.

This bit is read/write by software and cleared by hardware after a reset. This bit selects the polarity of the PWM0 signal.

- 0: The PWM0 signal is not inverted.

- 1: The PWM0 signal is inverted.

### Bit 0 CMPF0 PWM0 Compare Flag.

This bit is set by hardware and cleared by software by reading the PWM0CSR register. It indicates that the upcounter value matrix s the DCR0 register value. 0: Upcounter value does not match DCR value.

1: Upcounter value matches DCR value.

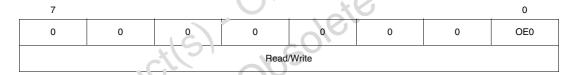

### PWM output control register (PWMCR)

Reset value: 0000 0000 (00h)

Bits 7:1 Roserved, must be kept cleared.

### Bit U OE0 PWM0 Output enable.

- 0: PWM0 output Alternate Function disabled (I/O pin free for general purpose I/O)

- 1: PWM0 output enabled

Register map and reset values

| This bit is set and cleared by software.  0: PWM0 output Alternate Function disabled (I/O pin free for general purpose I/O)  1: PWM0 output enabled  Table 30. Register map and reset values |                   |                      |          |          |          |          |            |            |            |            |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|----------------------|----------|----------|----------|----------|------------|------------|------------|------------|

| 00                                                                                                                                                                                           | Address<br>(Hex.) | Register<br>label    | 7        | 6        | 5        | 4        | 3          | 2          | 1          | 0          |

| ~\\S <sup>0</sup> \\                                                                                                                                                                         | 0D                | ATCSR<br>Reset value | 0        | 0        | 0        | CK1<br>0 | CK0<br>0   | OVF<br>0   | OVFIE<br>0 | CMPIE<br>0 |

| Ob                                                                                                                                                                                           | 0E                | CNTRH<br>Reset value | 0        | 0        | 0        | 0        | CN11<br>0  | CN10<br>0  | CN9<br>0   | CN8<br>0   |

|                                                                                                                                                                                              | 0F                | CNTRL<br>Reset value | CN7<br>0 | CN6<br>0 | CN5<br>0 | CN4<br>0 | CN3<br>0   | CN2<br>0   | CN1<br>0   | CN0<br>0   |

|                                                                                                                                                                                              | 10                | ATRH<br>Reset value  | 0        | 0        | 0        | 0        | ATR11<br>0 | ATR10<br>0 | ATR9<br>0  | ATR8<br>0  |

cycles) and the C<sub>ADC</sub> sample capacitor is disconnected from the analog input pin to get the optimum analog to digital conversion accuracy.

• The total conversion time:

t<sub>CONV</sub> = t<sub>SAMPLE</sub> + t<sub>HOLD</sub>

While the ADC is on, these two phases are continuously repeated.

At the end of each conversion, the sample capacitor is kept loaded with the previous measurement load. The advantage of this behavior is that it minimizes the current consumption on the analog pin in case of single input channel measurement.

#### A/D conversion

The analog input ports must be configured as input, no pull-up, no interrupt. Refer to the "I/O ports" chapter. Using these pins as analog inputs does not affect the ability of the port to be read as a logic input.

In the ADCCSR register, select the CS[2:0] bits to assign the analog channe, to convert.

#### **ADC** conversion mode

In the ADCCSR register, set the ADON bit to enable the A/D converser and to start the conversion. From this time on, the ADC performs a continuous conversion of the selected channel. When a conversion is complete:

- The EOC bit is set by hardware.

- The result is in the ADCDR registers.

A read to the ADCDRH resets the ECC Lin

To read the 10 bits, perform the following steps:

- 1. Poll EOC bit

- 2. Read ADCDRL

- 3. Read ADCDRH. This clears EOC automatically.

To read only 3 bits, perform the following steps:

- 1. Poll EOC pit

- 1. Read ADCDRH. This clears EOC automatically.

## 10.3.4 Low power modes

The A/D converter may be disabled by resetting the ADON bit. This feature allows reduced power consumption when no conversion is needed and between single shot conversions.

Table 31. Effect of low power modes

| Mode | Description                                                                                                                                                                                                                |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Wait | No effect on A/D converter                                                                                                                                                                                                 |

| Halt | A/D converter disabled.  After wakeup from Halt mode, the A/D converter requires a stabilization time t <sub>STAB</sub> (see <i>Section 12: Electrical characteristics</i> ) before accurate conversions can be performed. |

#### 12.4.3 On-chip peripherals

Table 54. On-chip peripheral characteristics

| Symbol   | Parameter                                   | Cor                      | Typ <sup>(1)</sup>      | Unit |                   |

|----------|---------------------------------------------|--------------------------|-------------------------|------|-------------------|

| 1        | 12-bit auto-reload timer supply current (2) | f <sub>CPU</sub> = 4 MHz | V <sub>DD</sub> = 3.0 V | 15   |                   |

| IDD(AT)  | 12-bit auto-reload timer supply current V   | f <sub>CPU</sub> = 8 MHz | V <sub>DD</sub> = 5.0 V | 30   | <b>Unit</b><br>μΑ |

|          | ADC supply current when converting (3)      | f <sub>ADC</sub> = 2 MHz | V <sub>DD</sub> = 3.0 V | 450  | μΑ                |

| IDD(ADC) | ADC supply current when converting V        | f <sub>ADC</sub> = 4 MHz | V <sub>DD</sub> = 5.0 V | 750  |                   |

- 1. Not tested in production, guaranteed by characterization.

- 2. Data based on a differential I<sub>DD</sub> measurement between reset configuration (timer stopped) and the timer running in PWM mode at  $f_{cpu} = 8 \text{ MHz}$ .

- 3. Data based on a differential I<sub>DD</sub> measurement between reset configuration and continuous A/D conversions with amplicient

## 12.5

|                      | Clock and timing characteristics                                        |                                                   |      |                    |      |                  |

|----------------------|-------------------------------------------------------------------------|---------------------------------------------------|------|--------------------|------|------------------|

| Subject to           | o general operating conditior                                           | ns for V <sub>DD</sub> , f <sub>OSC</sub> , ລາປີເ | λ.   | Al                 | Cer  |                  |

| Table 55             | General timings                                                         |                                                   |      | $O_{O_{r}}$        |      |                  |

| Symbol               | Parameter <sup>(1)</sup>                                                | Conditions                                        | Min  | Typ <sup>(2)</sup> | Max  | Unit             |

| t                    | Instruction cycle time                                                  | T <sub>CPU</sub> =8 MHz                           | 2    | 3                  | 12   | $t_{\text{CPU}}$ |

| t <sub>c(INST)</sub> | instruction cycle time                                                  | ICPU-0 IVII IZ                                    | 250  | 375                | 1500 | ns               |

| t                    | Interrupt reaction $t_{\text{C(II}} = \Delta t_{\text{C(II}} = T) + 10$ | f <sub>CPU</sub> =8 MHz                           | 10   | ·                  | 22   | t <sub>CPU</sub> |

| t <sub>v(IT)</sub>   | $t_{v(IT)} = \Delta t_{c(II \cup S, T)} - 10$                           | ICbn=o IAII 15                                    | 1.25 |                    | 2.75 | μS               |

- 1. Data based on the acterization. Not tested in production.

- 2. Data bas id an typical application software.

- 3. Time measured between interrupt event and interrupt vector fetch.  $\Delta t_{\text{c(INST)}}$  is the number of  $t_{\text{CPU}}$  cycles meded to finish the current instruction execution.

Table 56. Auto-wakeup RC oscillator

| 16                                      | Table 56. Auto-wakeup RC           | oscillator          |     |     |      |      |

|-----------------------------------------|------------------------------------|---------------------|-----|-----|------|------|

| ,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,, | Parameter                          | Conditions          | Min | Тур | Max  | Unit |

| 002                                     | Supply Voltage Range               |                     | 2.4 | 5.0 | 5.5  | V    |

|                                         | Operating Temperature Range        |                     | -40 | 25  | 125  | °C   |

| · O)                                    | Current Consumption <sup>(1)</sup> | Without prescaler   | 2.0 | 8.0 | 14.0 | μA   |

| 205                                     | Consumption <sup>(1)</sup>         | AWU RC switched off |     | 0   |      | μA   |

| Ob                                      | Output Frequency <sup>(1)</sup>    |                     | 20  | 33  | 60   | kHz  |

1. Data guaranteed by design.

#### 12.7.2 **Electromagnetic Interference (EMI)**

Based on a simple application running on the product (toggling 2 LEDs through the I/O ports), the product is monitored in terms of emission. This emission test is in line with the norm SAE J 1752/3 which specifies the board and the loading of each pin.

EMI characteristics<sup>(1)</sup> Table 60.

| Symbol           | Parameter  | Conditions                                                                           | Monitored frequency band | Max vs.<br>[f <sub>OSC</sub> /f <sub>CPU</sub> ] | Unit |

|------------------|------------|--------------------------------------------------------------------------------------|--------------------------|--------------------------------------------------|------|

|                  |            |                                                                                      | inequency band           | -/8 MHz                                          |      |

|                  |            |                                                                                      | 0.1 MHz to<br>30 MHz     | 21                                               |      |

| S <sub>EMI</sub> | Peak level | V <sub>DD</sub> =5 V, T <sub>A</sub> =+25 °C,<br>SO8 package,<br>conforming to SAE J | 30 MHz to<br>130 MHz     | 23                                               | dΒμV |

|                  | 1752/3     |                                                                                      | 130 MHz to<br>1 GHz      | 10                                               |      |

|                  |            |                                                                                      | SAE EMí (_e'/ei          | 3                                                | 7    |

<sup>1.</sup> Data based on characterization results, not tested in production.

#### 12.7.3 Absolute maximum ratings (electrical sensitivity)

Based on three different tests (ESD, LU and DLU) using specific measurement methods, the product is stressed in order to detern ine ts performance in terms of electrical sensitivity. For more details, refer to the application note AN1181.

### Electrostatic discharge (ESD)

Electrostatic discharges (a positive then a negative pulse separated by 1 second) are applied to the pins of each sample according to each pin combination. The sample size depends on inc number of supply pins in the device (3 parts\*(n+1) supply pin). One model can be simulated: Human Body Model. This test conforms to the JESD22-A114A/A115A standar 1.

Table 61. **Absolute maximum ratings**

| 00501 | Symbol                | Ratings                                            | Conditions            | Maximum<br>value <sup>(1)</sup> | Unit |

|-------|-----------------------|----------------------------------------------------|-----------------------|---------------------------------|------|

| 0,    | V <sub>ESD(HBM)</sub> | Electrostatic discharge voltage (human body model) | T <sub>A</sub> =+25°C | > 4000                          | V    |

| 60/   | 1. Data base          | ed on characterization results, not tested         | in production.        |                                 | _    |

| 000   | Static and            | d dynamic latchup                                  |                       |                                 |      |

Data based on characterization results, not tested in production.

### Static and dynamic latchup

- LU: 3 complementary static tests are required on 10 parts to assess the latchup performance. A supply overvoltage (applied to each power supply pin) and a current injection (applied to each input, output and configurable I/O pin) are performed on each sample. This test conforms to the EIA/JESD 78 IC latchup standard. For more details, refer to the application note AN1181.

- **DLU**: Electrostatic discharges (one positive then one negative test) are applied to each pin of 3 samples when the micro is running to assess the latchup performance in

## 13 Package characteristics

In order to meet environmental requirements, ST offers these devices in different grades of ECOPACK<sup>®</sup> packages, depending on their level of environmental compliance. ECOPACK<sup>®</sup> specifications, grade definitions and product status are available at: <a href="www.st.com">www.st.com</a>. ECOPACK® is an ST trademark.

## 13.1 Package mechanical data

Figure 65. 8-lead very thin fine pitch dual flat no-lead package outline

| NDEX AREA | (D/2 x E/2) | | (D/2 x

Table 70. 8-lead very thin fine pitch dual flat no-lead package mechanical data

|       | Dim  |      | Cmn) | C    |             | inches <sup>(1)</sup> |        |

|-------|------|------|------|------|-------------|-----------------------|--------|

|       | Dim. |      | Тур  | Max  | Min         | Тур                   | Max    |

|       | Α    | 0.90 | 0.90 | 1.00 | 0.0310      | 0.0350                | 0.0390 |

|       | A:   | 0.00 | 0.02 | 0.05 | 0.0000      | 0.0010                | 0.0020 |

|       | A3   | ·C   | 0.20 |      |             | 0.0080                |        |

| 10    | b    | 0.25 | 0.30 | 0.35 | 0.0100      | 0.0120                | 0.0140 |

| colle | D    | 0,   | 4.50 |      |             | 0.1770                |        |

| 0/09  | D2   | 3.50 | 3.65 | 3.75 | 0.1380      | 0.1440                | 0.1480 |

| OF    | X OE |      | 3.50 |      |             | 0.1380                |        |

| 7/6   | E2   | 1.96 | 2.11 | 2.21 | 0.0770      | 0.0830                | 0.0870 |

| 1250. | е    |      | 0.80 |      |             | 0.0310                |        |

| Oh    | L    | 0.30 | 0.40 | 0.50 | 0.0120      | 0.0160                | 0.0200 |

|       |      |      |      | Num  | per of pins |                       |        |

|       | N    |      |      |      | 8           |                       |        |

<sup>1.</sup> Values in inches are converted from mm and rounded to 4 decimal digits.

118/136

Table 75. Startup clock selection

| Configuration                | CKSEL1 | CKSEL0 |

|------------------------------|--------|--------|

| Internal RC as Startup Clock | 0      | 0      |

| Reserved                     | 0      | 0      |

| AWU RC as a Startup Clock    | 0      | 1      |

| Reserved                     | 1      | 0      |

| External Clock on pin PA5    | 1      | 1      |

Table 76. LVD threshold configuration

|                                      |      | 1    |  |  |  |

|--------------------------------------|------|------|--|--|--|

| Configuration                        | LVD1 | FAD0 |  |  |  |

| LVD Off                              | 1    | (51) |  |  |  |

| Highest voltage threshold            | 1,10 | 0    |  |  |  |

| Medium voltage threshold             | O V  | 1    |  |  |  |

| Lowest voltage threshold             | 0    | 0    |  |  |  |

| OPTION BYTE 0                        |      |      |  |  |  |

| Bits 7:4 Reserved, must always be 1. |      |      |  |  |  |

| Bit 3 Reserved, must always be 0.    |      |      |  |  |  |

|                                      |      |      |  |  |  |

#### 14.1.2 **OPTION BYTE 0**

- Bits 7:4 Reserved, must always be 1

- Bit 3 Reserved, must always be 7.

- Bit 2 SEC0 Sector 0 size definition

This option bit indicates the size of sector 0 according to the following table (see Table 77: Defin ticn of sector 0 size).

#### Bit 1 FMP R Readout protection

Reac out protection, when selected provides a protection against program memory content extraction and against write access to Flash memory. Erasing the option bytes when the FMP\_R option is selected will cause the whole memory to be erased first, and the device can be reprogrammed. Refer to Section 4.5 and the ST7 Flash Programming Reference Manual for more details.

- 0: Readout protection off

- 1: Readout protection on

#### Bit 0 FMP\_W FLASH write protection

- 0: Write protection off

- 1: Write protection on

Definition of sector 0 size

| Obsole<br>cole | tePr      | bytes when the FMP_R of erased first, and the device ST7 Flash Programming FO: Readout protection off 1: Readout protection on this option indicates if the | otection<br>e FLASH program memory is write protected.<br>on is selected, the program memory (and the option bit |  |

|----------------|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|--|

| 002            | Table 77. | Definition of sector 0 size                                                                                                                                 | е                                                                                                                |  |

|                |           | Sector 0 Size                                                                                                                                               | SEC0                                                                                                             |  |

|                |           | 0.5k                                                                                                                                                        | 0                                                                                                                |  |

|                |           | 1k                                                                                                                                                          | 1                                                                                                                |  |

# 16 Revision history

Table 82. Document revision history

| Date      | Revision | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|-----------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 06-Feb-06 | 1        | Initial release                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|           |          | Removed references to 3% RC Added note below Figure 4 Modified presentation of Section 4.3.1 Added notes to Section 6.2 (above Figure 9), replaced 8-bit calibration value to 10-bit calibration value and changed application note reference (AN2326 instead of AN1324) Modified Table 7: Clock register map and reset values and added b t 1. in the description of CKCNTCSR register Modified Figure 13 (added CKCNTCSR register) Added note 2 to EICRx description Modified caution in section 7.2 on page 25 Replaced V <sub>IT+(LVD)</sub> by V <sub>IT+(LVD)</sub> in Section : Monitoring the VDD main supply Modified LVDRF bit description in Section 7.4. : Register description Replaced "oscillator" by "main oscillator" in the second paragraph of Section 8.4.2: Halt mode Added note 1 to Figure 23 and and the 1 note 5 to Figure 24 Modified Section 8.5: Auto-wareup from Halt mode |

| 18-Apr-06 | 2 Prodi  | Replaced bit 1 by bit 2 on AWUF bit in Section 8.5.1: Register description Modified Section § 1: Introduction. Modified Section: External interrupt function. Updated Section 9.5: Interrupts. Modified Section Table 47.: Operating conditions with low voltage detector (LVD).  Modified Table 34: Auxiliary Voltage Detector (AVD) Thresholds. Modified Table 49: voltage drop between AVD flag set and LVD reset generation.  Nodified Table 50: Internal RC oscillator calibrated at 5 V. Modified Table 53: Supply current. Modified Table 54: On-chip peripherals. Modified Table 63: General characteristics. Modified Table 64: Output driving current. Modified Table 65: Asynchronous RESET pin characteristics. Modified Section 12.10: ADC characteristics.                                                                                                                                |

| osoleite  | Prodi    | Added Figure 49. Modified Figure 61. Removed EMC protection circuitry in Figure 62 (device works correctly without these components). Added ECOPACK text in Section 13: Package characteristics. Modified first paragraph in Section 14: Device configuration and ordering information. Modified Table 79. Modified conditioning option in option list. Modified Section 14.3: Development tools. Added Section 14.4: ST7 application notes. Added Section : . Added erratasheet at the end of the document.                                                                                                                                                                                                                                                                                                                                                                                            |