Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                               |

|----------------------------|-------------------------------------------------------------------------------|

| Product Status             | Active                                                                        |

| Core Processor             | 80C51                                                                         |

| Core Size                  | 8-Bit                                                                         |

| Speed                      | 40MHz                                                                         |

| Connectivity               | CANbus, UART/USART                                                            |

| Peripherals                | POR, PWM, WDT                                                                 |

| Number of I/O              | 34                                                                            |

| Program Memory Size        | 32KB (32K x 8)                                                                |

| Program Memory Type        | FLASH                                                                         |

| EEPROM Size                | 2K x 8                                                                        |

| RAM Size                   | 1.25K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                                     |

| Data Converters            | A/D 8x10b                                                                     |

| Oscillator Type            | External                                                                      |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                             |

| Mounting Type              | Surface Mount                                                                 |

| Package / Case             | 44-LCC (J-Lead)                                                               |

| Supplier Device Package    | 44-PLCC (16.6x16.6)                                                           |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/at89c51cc01ca-slsum |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

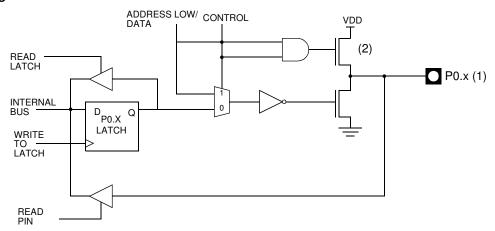

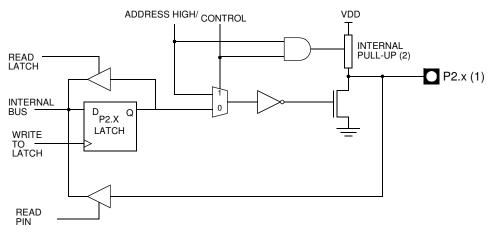

Figure 2. Port 0 Structure

- Notes: 1. Port 0 is precluded from use as general-purpose I/O Ports when used as address/data bus drivers.

- 2. Port 0 internal strong pull-ups assist the logic-one output for memory bus cycles only. Except for these bus cycles, the pull-up FET is off, Port 0 outputs are open-drain.

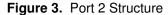

- Notes: 1. Port 2 is precluded from use as general-purpose I/O Ports when as address/data bus drivers.

- Port 2 internal strong pull-ups FET (P1 in FiGURE) assist the logic-one output for memory bus cycle.

When Port 0 and Port 2 are used for an external memory cycle, an internal control signal switches the output-driver input from the latch output to the internal address/data line.

# Read-Modify-Write Instructions

Some instructions read the latch data rather than the pin data. The latch based instructions read the data, modify the data and then rewrite the latch. These are called "Read-Modify-Write" instructions. Below is a complete list of these special instructions (see Table ). When the destination operand is a Port or a Port bit, these instructions read the latch rather than the pin:

## Registers

#### Table 15. PCON Register

PCON (S:87h) – Power configuration Register

| 7             | 6               | 5                                             | 4                                                                                                                                                                                | 3                             | 2               | 1              | 0             |  |  |  |

|---------------|-----------------|-----------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|-----------------|----------------|---------------|--|--|--|

| SMOD1         | SMOD0           | -                                             | POF                                                                                                                                                                              | GF1                           | GF0             | PD             | IDL           |  |  |  |

| Bit<br>Number | Bit<br>Mnemonic | Description                                   |                                                                                                                                                                                  |                               |                 |                |               |  |  |  |

| 7             | SMOD1           |                                               | Serial port Mode bit 1<br>Set to select double baud rate in mode 1, 2 or 3                                                                                                       |                               |                 |                |               |  |  |  |

| 6             | SMOD0           |                                               |                                                                                                                                                                                  | SCON register<br>ON register. | ſ.              |                |               |  |  |  |

| 5             | -               | <b>Reserved</b><br>The value re               | ad from this b                                                                                                                                                                   | it is indetermi               | nate. Do not se | et this bit.   |               |  |  |  |

| 4             | POF             |                                               | gnize next re                                                                                                                                                                    |                               | o its nominal v | oltage. Can a  | lso be set by |  |  |  |

| 3             | GF1             | General-pur<br>One use is to<br>during Idle m | indicate whe                                                                                                                                                                     | ther an interru               | upt occurred di | uring normal o | operation or  |  |  |  |

| 2             | GF0             | General-pur<br>One use is to<br>during Idle m | indicate whe                                                                                                                                                                     | ther an interru               | pt occurred d   | uring normal o | operation or  |  |  |  |

| 1             | PD              | Cleared by h<br>Set to activa                 | <b>Power-down Mode bit</b><br>Cleared by hardware when an interrupt or reset occurs.<br>Set to activate the Power-down mode.<br>If IDL and PD are both set, PD takes precedence. |                               |                 |                |               |  |  |  |

| 0             | IDL             | Set to activat                                | ardware whei<br>te the Idle mo                                                                                                                                                   |                               | or reset occurs | 5.             |               |  |  |  |

Reset Value = 00X1 0000b

```

Examples

;* NAME: api_rd_eeprom_byte

;* DPTR contain address to read.

;* Acc contain the reading value

;* NOTE: before execute this function, be sure the EEPROM is not BUSY

api_rd_eeprom_byte:

; Save and clear EA

MOV EECON, #02h; map EEPROM in XRAM space

MOVX A, @DPTR

MOV EECON, #00h; unmap EEPROM

; Restore EA

ret

;* NAME: api_ld_eeprom_cl

;* DPTR contain address to load

;* Acc contain value to load

;* NOTE: in this example we load only 1 byte, but it is possible upto

;* 128 Bytes.

;* before execute this function, be sure the EEPROM is not BUSY

*****

api_ld_eeprom_cl:

; Save and clear EA

MOV EECON, #02h ; map EEPROM in XRAM space

MOVX @DPTR, A

MOVEECON, #00h; unmap EEPROM

; Restore EA

ret

;* NAME: api_wr_eeprom

;* NOTE: before execute this function, be sure the EEPROM is not BUSY

api_wr_eeprom:

; Save and clear EA

MOV EECON, #050h

MOV EECON, #0A0h

; Restore EA

ret

```

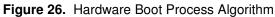

# Overview of FM0 The CPU interfaces to the Flash memory through the FCON register and AUXR1 register. These registers are used to:

Map the memory spaces in the adressable space

- Launch the programming of the memory spaces

- Get the status of the Flash memory (busy/not busy)

**Mapping of the Memory Space** By default, the user space is accessed by MOVC instruction for read only. The column latches space is made accessible by setting the FPS bit in FCON register. Writing is possible from 0000h to 7FFFh, address bits 6 to 0 are used to select an address within a page while bits 14 to 7 are used to select the programming address of the page. Setting FPS bit takes precedence on the EXTRAM bit in AUXR register.

The other memory spaces (user, extra row, hardware security) are made accessible in the code segment by programming bits FMOD0 and FMOD1 in FCON register in accordance with Table 25. A MOVC instruction is then used for reading these spaces.

Table 25. FM0 Blocks Select Bits

| FMOD1 | FMOD0 | FM0 Adressable space           |

|-------|-------|--------------------------------|

| 0     | 0     | User (0000h-7FFFh)             |

| 0     | 1     | Extra Row(FF80h-FFFFh)         |

| 1     | 0     | Hardware Security Byte (0000h) |

| 1     | 1     | Reserved                       |

#### Launching Programming

FPL3:0 bits in FCON register are used to secure the launch of programming. A specific sequence must be written in these bits to unlock the write protection and to launch the programming. This sequence is 5xh followed by Axh. Table 26 summarizes the memory spaces to program according to FMOD1:0 bits.

## Registers

### FCON RegisterFCON (S:D1h)

Flash Control Register

| 7             | 6               | 5                          | 4            | 3                                            | 2     | 1              | 0       |

|---------------|-----------------|----------------------------|--------------|----------------------------------------------|-------|----------------|---------|

| FPL3          | FPL2            | FPL1                       | FPL0         | FPS                                          | FMOD1 | FMOD0          | FBUSY   |

| Bit<br>Number | Bit<br>Mnemonic | Description                |              |                                              |       |                |         |

| 7-4           | FPL3:0          | •                          | lowed by AXh | ommand Bits<br>to launch the                 |       | g according to | FMOD1:0 |

| 3             | FPS             | Set to map the             |              | <b>ce</b><br>ch space in the<br>nemory space |       | y space.       |         |

| 2-1           | FMOD1:0         | Flash Mode<br>See Table 25 | or Table 26. |                                              |       |                |         |

| 0             | FBUSY           | Clear by hard              |              | gramming is in<br>rogramming is<br>ftware.   |       |                |         |

Reset Value = 0000 0000b

### Application Programming Interface

Several Application Program Interface (API) calls are available for use by an application program to permit selective erasing and programming of Flash pages. All calls are made by functions.

All of these APIs are described in detail in the following documents on the Atmel web site.

- Datasheet Bootloader CAN T89C51CC01

- Datasheet Bootloader UART T89C51CC01

### **XROW Bytes**

#### Table 33. XROW Mapping

| Description                                     | Default Value | Address |

|-------------------------------------------------|---------------|---------|

| Copy of the Manufacturer Code                   | 58h           | 30h     |

| Copy of the Device ID#1: Family code            | D7h           | 31h     |

| Copy of the Device ID#2: Memories size and type | F7h           | 60h     |

| Copy of the Device ID#3: Name and Revision      | FFh           | 61h     |

For slaves A and B, bit 2 is a don't care bit; for slave C, bit 2 is set. To communicate with all of the slaves, the master must send an address FFh. To communicate with slaves A and B, but not slave C, the master can send and address FBh.

### Registers

Table 35. SCON Register

SCON (S:98h) Serial Control Register

| 7             | 6               | 5                                                                                                         | 4                                                                                                                                                                             | 3               | 2                                                                    | 1             | 0       |  |

|---------------|-----------------|-----------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|----------------------------------------------------------------------|---------------|---------|--|

| FE/SM0        | SM1             | SM2                                                                                                       | REN                                                                                                                                                                           | TB8             | RB8                                                                  | TI            | RI      |  |

| Bit<br>Number | Bit<br>Mnemonic | Description                                                                                               |                                                                                                                                                                               |                 |                                                                      |               |         |  |

| 7             | FE              | Clear to rese                                                                                             | <b>for bit (SMOD</b><br>It the error sta<br>vare when an                                                                                                                      | te, not cleared | d by a valid sto<br>t is detected.                                   | op bit.       |         |  |

|               | SM0             |                                                                                                           | <b>Iode bit 0 (SI</b><br>I for serial por                                                                                                                                     | ,               | ion.                                                                 |               |         |  |

| 6             | SM1             | Serial port N           SM0         SM1           0         0           1         0           1         1 | <b>Iode bit 1</b><br><u>Mode</u><br>Shift Register<br>8-bit UART<br>9-bit UART<br>9-bit UART                                                                                  | Variable        | <u>te</u><br>(or F <sub>XTAL</sub> /6 in<br>or F <sub>XTAL</sub> /32 | mode X2)      |         |  |

| 5             | SM2             | Clear to disa                                                                                             | ble multiproce                                                                                                                                                                | ssor commur     | <b>Communicat</b><br>nication feature<br>ation feature in            | Э.            |         |  |

| 4             | REN             |                                                                                                           | <b>nable bit</b><br>ble serial rece<br>e serial recept                                                                                                                        |                 |                                                                      |               |         |  |

| 3             | TB8             | Clear to trans                                                                                            | <b>Bit 8/Ninth b</b><br>smit a logic 0<br>nit a logic 1 in                                                                                                                    | in the 9th bit. | in modes 2 a                                                         | ind 3         |         |  |

| 2             | RB8             | Cleared by h                                                                                              | t <b>8/Ninth bit r</b><br>ardware if 9th<br>vare if 9th bit r                                                                                                                 | bit received i  |                                                                      |               |         |  |

| 1             | ΤI              | Clear to ackr<br>Set by hardw                                                                             | ransmit Interrupt flag<br>lear to acknowledge interrupt.<br>et by hardware at the end of the 8th bit time in mode 0 or at the beginning of the<br>top bit in the other modes. |                 |                                                                      |               |         |  |

| 0             | RI              | Set by hardw                                                                                              | nowledge inter                                                                                                                                                                | d of the 8th bi | t time in mode                                                       | 0, see Figure | 29. and |  |

Reset Value = 0000 0000b Bit addressable

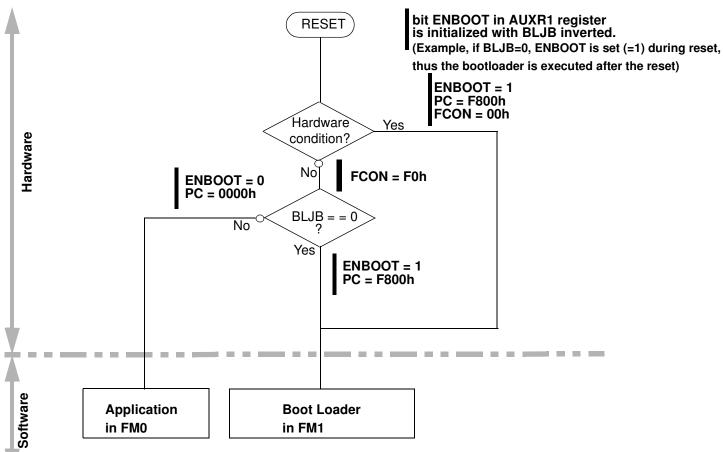

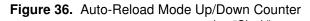

Figure 35. Timer Interrupt System

| Timer            |                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Timer 2          | The T89C51CC01 timer 2 is compatible with timer 2 in the 80C52.                                                                                                                                                                                                                                                                                                                                                                                 |

|                  | It is a 16-bit timer/counter: the count is maintained by two eight-bit timer registers, TH2 and TL2 that are cascade- connected. It is controlled by T2CON register (See Table ) and T2MOD register (See Table 48). Timer 2 operation is similar to Timer 0 and Timer 1. C/T2 selects $F_{T2 clock}/6$ (timer operation) or external pin T2 (counter operation) as timer clock. Setting TR2 allows TL2 to be incremented by the selected input. |

|                  | Timer 2 includes the following enhancements:                                                                                                                                                                                                                                                                                                                                                                                                    |

|                  | Auto-reload mode (up or down counter)                                                                                                                                                                                                                                                                                                                                                                                                           |

|                  | Programmable clock-output                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Auto-Reload Mode | The auto-reload mode configures timer 2 as a 16-bit timer or event counter with auto-<br>matic reload. This feature is controlled by the DCEN bit in T2MOD register (See<br>Table 48). Setting the DCEN bit enables timer 2 to count up or down as shown in<br>Figure 36. In this mode the T2EX pin controls the counting direction.                                                                                                            |

|                  | When T2EX is high, timer 2 counts up. Timer overflow occurs at FFFFh which sets the TF2 flag and generates an interrupt request. The overflow also causes the 16-bit value in RCAP2H and RCAP2L registers to be loaded into the timer registers TH2 and TL2.                                                                                                                                                                                    |

|                  | When T2EX is low, timer 2 counts down. Timer underflow occurs when the count in the timer registers TH2 and TL2 equals the value stored in RCAP2H and RCAP2L registers. The underflow sets TF2 flag and reloads FFFFh into the timer registers.                                                                                                                                                                                                 |

The EXF2 bit toggles when timer 2 overflow or underflow, depending on the direction of the count. EXF2 does not generate an interrupt. This bit can be used to provide 17-bit resolution.

#### Table 49. TL2 Register

#### TL2 (S:CCh) Timer 2 Low Byte Register

| 7             | 6               | 5           | 4        | 3 | 2 | 1 | 0 |

|---------------|-----------------|-------------|----------|---|---|---|---|

| -             | -               | -           | -        | - | - | - | - |

| Bit<br>Number | Bit<br>Mnemonic | Description |          |   |   |   |   |

| 7-0           |                 | Low Byte of | Timer 2. |   |   |   |   |

Reset Value = 0000 0000b Not bit addressable

#### Table 50. RCAP2H Register

RCAP2H (S:CBh) Timer 2 Reload/Capture High Byte Register

| 7             | 6               | 5            | 4             | 3           | 2 | 1 | 0 |

|---------------|-----------------|--------------|---------------|-------------|---|---|---|

| -             | -               | -            | -             | -           | - | - | - |

| Bit<br>Number | Bit<br>Mnemonic | Description  |               |             |   |   |   |

| 7-0           |                 | High Byte of | Timer 2 Reloa | ad/Capture. |   |   |   |

Reset Value = 0000 0000b Not bit addressable

#### Table 51. RCAP2L Register

RCAP2L (S:CAH) TIMER 2 Reload/Capture Low Byte Register

| 7             | 6               | 5           | 4             | 3          | 2 | 1 | 0 |

|---------------|-----------------|-------------|---------------|------------|---|---|---|

| -             | -               | -           | -             | -          | - | - | - |

| Bit<br>Number | Bit<br>Mnemonic | Description |               |            |   |   |   |

| 7-0           |                 | Low Byte of | Timer 2 Reloa | d/Capture. |   |   |   |

Reset Value = 0000 0000b Not bit addressable

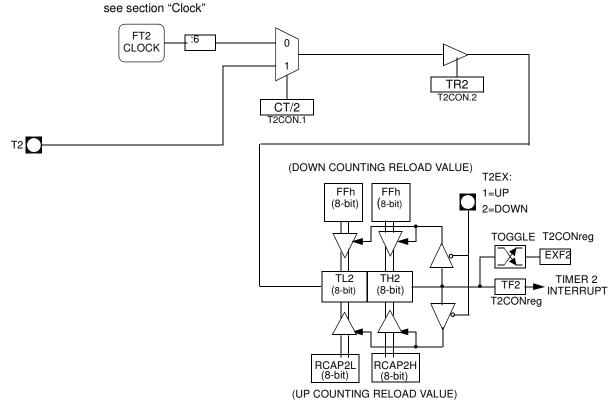

### **Data and Remote Frame**

Description of the different steps for:

Data Frame

# 90 A/T89C51CC01

#### 4. Interrupt routine

// Save the current CANPAGE

// Find the first message object which generate an interrupt in CANSIT1 and CANSIT2  $% \left( \mathcal{A}^{\prime}\right) =\left( \mathcal{A}^{\prime}\right) \left( \mathcal{A}^{\prime}$

// Select the corresponding message object

$\ensuremath{\prime\prime}\xspace$  Analyse the CANSTCH register to identify which kind of interrupt is generated

// Manage the interrupt

// Clear the status register CANSTCH = 00h;

// if it is not a channel interrupt but a general interrupt

// Manage the general interrupt and clear CANGIT register

$//\ {\rm restore}$  the old CANPAGE

#### Table 60. CANGIT Register

CANGIT (S:9Bh) CAN General Interrupt

| 7             | 6            | 5                                                               | 4                                                                                                                                                                                                                                                                                                                                                              | 3                | 2               | 1                | 0         |  |

|---------------|--------------|-----------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|-----------------|------------------|-----------|--|

| CANIT         | -            | OVRTIM                                                          | OVRBUF                                                                                                                                                                                                                                                                                                                                                         | SERG             | CERG            | FERG             | AERG      |  |

| Bit<br>Number | Bit Mnemonic | Descripti                                                       | on                                                                                                                                                                                                                                                                                                                                                             |                  |                 |                  |           |  |

| 7             | CANIT        | This statu<br>interrupt c                                       | nterrupt Flag<br>s bit is the ima<br>ontroller.<br>used in the cas                                                                                                                                                                                                                                                                                             | age of all the ( |                 | r interrupts se  | nt to the |  |

| 6             | -            | Reserved<br>The value                                           | l<br>s read from th                                                                                                                                                                                                                                                                                                                                            | is bit is indete | rminate. Do n   | ot set this bit. |           |  |

| 5             | OVRTIM       | This statu<br>If the bit E                                      | CAN Timer<br>s bit is set whe<br>TIM in the IE1<br>bit in order to                                                                                                                                                                                                                                                                                             | register is se   | t, an interrupt |                  |           |  |

| 4             | OVRBUF       | 0 - no inte<br>1 - IT turn<br>This bit is<br>Bit resetal        | <b>Dverrun BUFFER</b><br>) - no interrupt.<br>1 - IT turned on<br>This bit is set when the buffer is full.<br>Bit resetable by user.<br>see Figure 46.                                                                                                                                                                                                         |                  |                 |                  |           |  |

| 3             | SERG         | Detection                                                       | or General<br>of more than t<br>can generate a                                                                                                                                                                                                                                                                                                                 |                  |                 |                  | ty.       |  |

| 2             | CERG         | The receive<br>from the s<br>If this che-<br>set.               | This flag can generate an interrupt. resetable by user.<br><b>CRC Error General</b><br>The receiver performs a CRC check on each destuffed received message<br>rom the start of frame up to the data field.<br>If this checking does not match with the destuffed CRC field, a CRC error is<br>set.<br>This flag can generate an interrupt. resetable by user. |                  |                 |                  |           |  |

| 1             | FERG         | The form<br>following b<br>CRC delin<br>acknowled<br>end_of_fra | Form Error General<br>The form error results from one or more violations of the fixed form in the<br>following bit fields:<br>CRC delimiter<br>acknowledgment delimiter<br>end_of_frame<br>This flag can generate an interrupt. resetable by user.                                                                                                             |                  |                 |                  |           |  |

| 0             | AERG         | No detect                                                       | edgment Erro<br>ion of the dom<br>can generate a                                                                                                                                                                                                                                                                                                               | inant bit in the | -               |                  |           |  |

Note: 1. This field is Read Only.

Reset Value = 0x00 0000b

#### Table 63. CANGIE Register

CANGIE (S:C1h) CAN General Interrupt Enable

| 7             | 6            | 5                                      | 4    | 3                 | 2             | 1               | 0        |

|---------------|--------------|----------------------------------------|------|-------------------|---------------|-----------------|----------|

| -             | -            | ENRX                                   | ENTX | ENERCH            | ENBUF         | ENERG           | -        |

| Bit<br>Number | Bit Mnemonic | Description                            | on   |                   |               |                 |          |

| 7-6           | -            | Reserved<br>The value                  |      | nese bits are ir  | determinate.  | Do not set the  | se bits. |

| 5             | ENRX         | Enable Re<br>0 - Disable<br>1 - Enable | -    | upt               |               |                 |          |

| 4             | ENTX         | Enable Tr<br>0 - Disable<br>1 - Enable |      | rupt              |               |                 |          |

| 3             | ENERCH       | Enable M<br>0 - Disable<br>1 - Enable  | 9    | ct Error Interr   | upt           |                 |          |

| 2             | ENBUF        | Enable B<br>0 - Disable<br>1 - Enable  | -    |                   |               |                 |          |

| 1             | ENERG        | Enable Ge<br>0 - Disable<br>1 - Enable |      | Interrupt         |               |                 |          |

| 0             | -            | Reserved<br>The value                  |      | is bit is indeter | minate. Do no | t set this bit. |          |

Note: See Figure 46

Reset Value = xx00 000xb

#### Table 64. CANEN1 Register

CANEN1 (S:CEh Read Only) CAN Enable Message Object Registers 1

| 7             | 6            | 5                                                   | 4                                                                                                                                                                                                                                                       | 3     | 2     | 1 | 0 |  |  |

|---------------|--------------|-----------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-------|---|---|--|--|

| -             | ENCH14       | ENCH13                                              | ENCH12                                                                                                                                                                                                                                                  | ENCH9 | ENCH8 |   |   |  |  |

| Bit<br>Number | Bit Mnemonic | Descriptio                                          | Description                                                                                                                                                                                                                                             |       |       |   |   |  |  |

| 7             | -            | Reserved<br>The value                               | Reserved<br>The values read from this bit is indeterminate. Do not set this bit.                                                                                                                                                                        |       |       |   |   |  |  |

| 6-0           | ENCH14:8     | 0 - messa<br>emission o<br>1 - messa<br>This bit is | Enable Message Object<br>0 - message object is disabled => the message object is free for a new<br>emission or reception.<br>1 - message object is enabled.<br>This bit is resetable by re-writing the CANCONCH of the corresponding<br>message object. |       |       |   |   |  |  |

Reset Value = x000 0000b

#### Table 91. CANIDM4 Register for V2.0 part B

CANIDM4 for V2.0 part B (S:C7h) CAN Identifier Mask Registers 4

| 7             | 6            | 5                        | 4                                                                                                | 3 | 2 | 1 | 0 |  |  |

|---------------|--------------|--------------------------|--------------------------------------------------------------------------------------------------|---|---|---|---|--|--|

| IDMSK 4       | IDMSK 3      | IDMSK 2                  | MSK 2 IDMSK 1 IDMSK 0 RTRMSK -                                                                   |   |   |   |   |  |  |

| Bit<br>Number | Bit Mnemonic | Description              | Description                                                                                      |   |   |   |   |  |  |

| 7-3           | IDMSK4:0     | 0 - compa<br>1 - bit com | Dentifier Mask Value<br>- comparison true forced.<br>- bit comparison enabled.<br>see Figure 50. |   |   |   |   |  |  |

| 2             | RTRMSK       | 0 - compa                | Remote Transmission Request Mask Value<br>- comparison true forced.<br>- bit comparison enabled. |   |   |   |   |  |  |

| 1             | -            | Reserved<br>The value    | Reserved<br>The value read from this bit is indeterminate. Do not set this bit.                  |   |   |   |   |  |  |

| 0             | IDEMSK       | 0 - compa                | IDentifier Extension Mask Value<br>0 - comparison true forced.<br>1 - bit comparison enabled.    |   |   |   |   |  |  |

Note: The ID Mask is only used for reception.

No default value after reset.

#### Table 92. CANMSG Register

CANMSG (S:A3h) CAN Message Data Register

| 7             | 6            | 5                                                                                     | 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 3     | 2     | 1     | 0     |  |  |

|---------------|--------------|---------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-------|-------|-------|--|--|

| MSG 7         | MSG 6        | MSG 5                                                                                 | MSG 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | MSG 3 | MSG 2 | MSG 1 | MSG 0 |  |  |

| Bit<br>Number | Bit Mnemonic | Descriptio                                                                            | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |       |       |       |       |  |  |

| 7-0           | MSG7:0       | This regist<br>object reg<br>After writir<br>specified r<br>index. If a<br>reading cy | <b>Message Data</b><br>This register contains the mailbox data byte pointed at the page message object register.<br>After writing in the page message object register, this byte is equal to the specified message location (in the mailbox) of the pre-defined identifier + index. If auto-incrementation is used, at the end of the data register writing or reading cycle, the mailbox pointer is auto-incremented. The range of the counting is 8 with no end loop (0, 1,, 7, 0,) |       |       |       |       |  |  |

No default value after reset.

| Analog-to-Digital<br>Converter (ADC) | This section describes the on-chip 10 bit analog-to-digital converter of the T89C51CC01. Eight ADC channels are available for sampling of the external sources AN0 to AN7. An analog multiplexer allows the single ADC converter to select one from the 8 ADC channels as ADC input voltage (ADCIN). ADCIN is converted by the 10-bit cascaded potentiometric ADC.                                                                                                                                                                        |

|--------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                      | Two modes of conversion are available:<br>- Standard conversion (8 bits).<br>- Precision conversion (10 bits).                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                                      | For the precision conversion, set bit PSIDLE in ADCON register and start conversion.<br>The device is in a pseudo-idle mode, the CPU does not run but the peripherals are<br>always running. This mode allows digital noise to be as low as possible, to ensure high<br>precision conversion.                                                                                                                                                                                                                                             |

|                                      | For this mode it is necessary to work with end of conversion interrupt, which is the only way to wake the device up.                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                                      | If another interrupt occurs during the precision conversion, it will be served only after this conversion is completed.                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Features                             | <ul> <li>8 channels with multiplexed inputs</li> <li>10-bit cascaded potentiometric ADC</li> <li>Conversion time 16 micro-seconds (typ.)</li> <li>Zero Error (offset) ± 2 LSB max</li> <li>Positive External Reference Voltage Range (VAREF) 2.4 to 3.0 Volt (typ.)</li> <li>ADCIN Range 0 to 3Volt</li> <li>Integral non-linearity typical 1 LSB, max. 2 LSB</li> <li>Differential non-linearity typical 0.5 LSB, max. 1 LSB</li> <li>Conversion Complete Flag or Conversion Complete Interrupt</li> <li>Selectable ADC Clock</li> </ul> |

| ADC Port 1 I/O Functions             | Port 1 pins are general I/O that are shared with the ADC channels. The channel select bit in ADCF register define which ADC channel/port1 pin will be used as ADCIN. The remaining ADC channels/port1 pins can be used as general-purpose I/O or as the alternate function that is available.                                                                                                                                                                                                                                             |

|                                      | A conversion launched on a channel which are not selected on ADCF register will not have any effect.                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| VAREF                                | VAREF should be connected to a low impedance point and must remain in the range specified in Table 122. If the ADC is not used, it is recommended to connect VAREF to VAGND.                                                                                                                                                                                                                                                                                                                                                              |

### Registers

#### Table 115. IEN0 Register

IEN0 (S:A8h) Interrupt Enable Register

| 7             | 6               | 5                                                                                                                | 4                                                                                                                                                                                                              | 3   | 2   | 1   | 0   |  |  |  |

|---------------|-----------------|------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|-----|--|--|--|

| EA            | EC              | ET2                                                                                                              | ES                                                                                                                                                                                                             | ET1 | EX1 | ET0 | EX0 |  |  |  |

| Bit<br>Number | Bit<br>Mnemonic | Description                                                                                                      | Description                                                                                                                                                                                                    |     |     |     |     |  |  |  |

| 7             | EA              | Clear to disa<br>Set to enable<br>If EA=1, eacl                                                                  | hable All Interrupt bit<br>ear to disable all interrupts.<br>et to enable all interrupts.<br>EA=1, each interrupt source is individually enabled or disabled by setting or<br>earing its interrupt enable bit. |     |     |     |     |  |  |  |

| 6             | EC              |                                                                                                                  | pt Enable<br>ble the PCA in<br>the PCA inte                                                                                                                                                                    |     |     |     |     |  |  |  |

| 5             | ET2             | Clear to disa                                                                                                    | Timer 2 Overflow Interrupt Enable bit<br>Clear to disable Timer 2 overflow interrupt.<br>Set to enable Timer 2 overflow interrupt.                                                                             |     |     |     |     |  |  |  |

| 4             | ES              | Clear to disa                                                                                                    | Serial Port Enable bit<br>Clear to disable serial port interrupt.<br>Set to enable serial port interrupt.                                                                                                      |     |     |     |     |  |  |  |

| 3             | ET1             | Clear to disa                                                                                                    | Fimer 1 Overflow Interrupt Enable bit<br>Clear to disable timer 1 overflow interrupt.<br>Set to enable timer 1 overflow interrupt.                                                                             |     |     |     |     |  |  |  |

| 2             | EX1             | Clear to disa                                                                                                    | External Interrupt 1 Enable bit<br>Clear to disable external interrupt 1.<br>Set to enable external interrupt 1.                                                                                               |     |     |     |     |  |  |  |

| 1             | ET0             | Clear to disa                                                                                                    | Timer 0 Overflow Interrupt Enable bit<br>Clear to disable timer 0 overflow interrupt.<br>Set to enable timer 0 overflow interrupt.                                                                             |     |     |     |     |  |  |  |

| 0             | EX0             | External Interrupt 0 Enable bit<br>Clear to disable external interrupt 0.<br>Set to enable external interrupt 0. |                                                                                                                                                                                                                |     |     |     |     |  |  |  |

Reset Value = 0000 0000b bit addressable

#### Table 116. IEN1 Register

IEN1 (S:E8h) Interrupt Enable Register

| 7             | 6               | 5                                                                                                   | 4                                                                                                                                 | 3               | 2              | 1            | 0    |  |  |

|---------------|-----------------|-----------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|-----------------|----------------|--------------|------|--|--|

| -             | -               | -                                                                                                   | -                                                                                                                                 | -               | ETIM           | EADC         | ECAN |  |  |

| Bit<br>Number | Bit<br>Mnemonic | Description                                                                                         | Description                                                                                                                       |                 |                |              |      |  |  |

| 7             | -               | <b>Reserved</b><br>The value rea                                                                    | teserved<br>he value read from this bit is indeterminate. Do not set this bit.                                                    |                 |                |              |      |  |  |

| 6             | -               | <b>Reserved</b><br>The value rea                                                                    | ad from this b                                                                                                                    | it is indetermi | nate. Do not s | et this bit. |      |  |  |

| 5             | -               | <b>Reserved</b><br>The value rea                                                                    | Reserved<br>The value read from this bit is indeterminate. Do not set this bit.                                                   |                 |                |              |      |  |  |

| 4             | -               | Reserved<br>The value rea                                                                           | Reserved<br>The value read from this bit is indeterminate. Do not set this bit.                                                   |                 |                |              |      |  |  |

| 3             | -               | Reserved<br>The value rea                                                                           | Reserved<br>The value read from this bit is indeterminate. Do not set this bit.                                                   |                 |                |              |      |  |  |

| 2             | ETIM            | Clear to disa                                                                                       | Timer Overrun Interrupt Enable bit<br>Clear to disable the timer overrun interrupt.<br>Set to enable the timer overrun interrupt. |                 |                |              |      |  |  |

| 1             | EADC            | ADC Interrupt Enable bit<br>Clear to disable the ADC interrupt.<br>Set to enable the ADC interrupt. |                                                                                                                                   |                 |                |              |      |  |  |

| 0             | ECAN            | CAN Interrupt Enable bit<br>Clear to disable the CAN interrupt.<br>Set to enable the CAN interrupt. |                                                                                                                                   |                 |                |              |      |  |  |

Reset Value = xxxx x000b bit addressable

# AIMEL

# Datasheet Change Log for T89C51CC01

Changes from 4129F -11/02 to 4129G - 04/03

Changes from 4129G - 04/03 to 4129H - 10/03

Changes from 4129H - 10/03 to 4129I - 12/03

Changes from 4129I - 12/03 to 4129J - 08/04

1. Changed the endurance of Flash to 100, 000 Write/Erase cycles.

- Added note on Flash retention formula for V<sub>IH1</sub>, in Section "DC Parameters for Standard Voltage", page 144.

- 1. Updated "Electrical Characteristics" on page 144.

- 2. Corrected Figure 46 on page 84.

- 1. Correction in Registers CPA and CPS0.

- 2. Added note regarding PSEN during power On see Section "Hardware Boot Process", page 48.

- 1. Figure clock-out mode modified see, Figure 37 on page 67.

- 2. Added explanation on the CAN protocol, see Section "CAN Controller", page 75.

- 3. Corrected error in Table 53 on page 72, (1.25ms to 1.25s) for Time-out Computation.

- 1. Minor corrections throughout the document.

- 2. Clarification to Mode Switching Waveforms diagram. See page 16.

- Changes from 4129K 01/05 to 4129L 08/05

Changes from 4129L 08/05 to 4129M 02/08

Changes from 4129J -

08/04 to 4129K 01/05

Changes from 4129M 02/08 to 4129N 03/08

- 1. Added green product ordering information.

- 1. Removed non-green packages from ordering information.

- 1. Removed CA-BGA package offering from ordering information.

- 2. Updated package drawings.

#### **Atmel Corporation**

2325 Orchard Parkway San Jose, CA 95131, USA Tel: 1(408) 441-0311 Fax: 1(408) 487-2600

#### **Regional Headquarters**

#### Europe

Atmel Sarl Route des Arsenaux 41 Case Postale 80 CH-1705 Fribourg Switzerland Tel: (41) 26-426-5555 Fax: (41) 26-426-5500

#### Asia

Room 1219 Chinachem Golden Plaza 77 Mody Road Tsimshatsui East Kowloon Hong Kong Tel: (852) 2721-9778 Fax: (852) 2722-1369

#### Japan

9F, Tonetsu Shinkawa Bldg. 1-24-8 Shinkawa Chuo-ku, Tokyo 104-0033 Japan Tel: (81) 3-3523-3551 Fax: (81) 3-3523-7581

#### **Atmel Operations**

Memory

2325 Orchard Parkway San Jose, CA 95131, USA Tel: 1(408) 441-0311 Fax: 1(408) 436-4314

#### Microcontrollers

2325 Orchard Parkway San Jose, CA 95131, USA Tel: 1(408) 441-0311 Fax: 1(408) 436-4314

La Chantrerie BP 70602 44306 Nantes Cedex 3, France Tel: (33) 2-40-18-18-18 Fax: (33) 2-40-18-19-60

#### ASIC/ASSP/Smart Cards

Zone Industrielle 13106 Rousset Cedex, France Tel: (33) 4-42-53-60-00 Fax: (33) 4-42-53-60-01

1150 East Cheyenne Mtn. Blvd. Colorado Springs, CO 80906, USA Tel: 1(719) 576-3300 Fax: 1(719) 540-1759

Scottish Enterprise Technology Park Maxwell Building East Kilbride G75 0QR, Scotland Tel: (44) 1355-803-000 Fax: (44) 1355-242-743

#### **RF**/Automotive

Theresienstrasse 2 Postfach 3535 74025 Heilbronn, Germany Tel: (49) 71-31-67-0 Fax: (49) 71-31-67-2340

1150 East Cheyenne Mtn. Blvd. Colorado Springs, CO 80906, USA Tel: 1(719) 576-3300 Fax: 1(719) 540-1759

#### Biometrics/Imaging/Hi-Rel MPU/

High Speed Converters/RF Datacom Avenue de Rochepleine BP 123 38521 Saint-Egreve Cedex, France Tel: (33) 4-76-58-30-00 Fax: (33) 4-76-58-34-80

*Literature Requests* www.atmel.com/literature

**Disclaimer:** Atmel Corporation makes no warranty for the use of its products, other than those expressly contained in the Company's standard warranty which is detailed in Atmel's Terms and Conditions located on the Company's web site. The Company assumes no responsibility for any errors which may appear in this document, reserves the right to change devices or specifications detailed herein at any time without notice, and does not make any commitment to update the information contained herein. No licenses to patents or other intellectual property of Atmel are granted by the Company in connection with the sale of Atmel products, expressly or by implication. Atmel's products are not authorized for use as critical components in life support devices or systems.

© Atmel Corporation 2008. All rights reserved. Atmel<sup>®</sup> and combinations thereof are the registered trademarks of Atmel Corporation or its subsidiaries. Other terms and product names may be the trademarks of others.