# E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                |

|----------------------------|----------------------------------------------------------------|

| Product Status             | Active                                                         |

| Core Processor             | 80C51                                                          |

| Core Size                  | 8-Bit                                                          |

| Speed                      | 40MHz                                                          |

| Connectivity               | CANbus, UART/USART                                             |

| Peripherals                | POR, PWM, WDT                                                  |

| Number of I/O              | 34                                                             |

| Program Memory Size        | 32KB (32K x 8)                                                 |

| Program Memory Type        | FLASH                                                          |

| EEPROM Size                | 2K x 8                                                         |

| RAM Size                   | 1.25К х 8                                                      |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                      |

| Data Converters            | A/D 8x10b                                                      |

| Oscillator Type            | External                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                              |

| Mounting Type              | Surface Mount                                                  |

| Package / Case             | 44-LQFP                                                        |

| Supplier Device Package    | 44-VQFP (10x10)                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/atmel/at89c51cc01ua-rltum |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## A/T89C51CC01

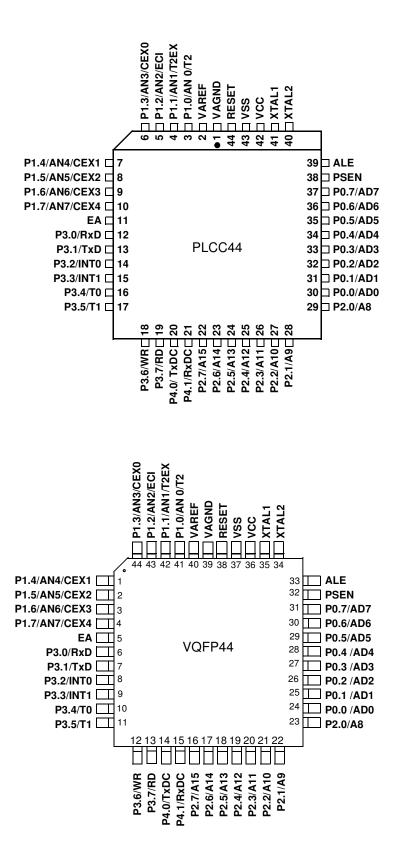

## **Pin Configuration**

| Clock       | <ul> <li>The T89C51CC01 core needs only 6 clock periods per machine cycle. This feature, called "X2", provides the following advantages:</li> <li>Divides frequency crystals by 2 (cheaper crystals) while keeping the same CPU power.</li> <li>Saves power consumption while keeping the same CPU power (oscillator power saving).</li> <li>Saves power consumption by dividing dynamic operating frequency by 2 in operating and idle modes.</li> <li>Increases CPU power by 2 while keeping the same crystal frequency.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|             | In order to keep the original C51 compatibility, a divider-by-2 is inserted between the XTAL1 signal and the main clock input of the core (phase generator). This divider may be disabled by the software.<br>An extra feature is available to start after Reset in the X2 mode. This feature can be enabled by a bit X2B in the Hardware Security Byte. This bit is described in the section "In-System-Programming".                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Description | <ul> <li>The X2 bit in the CKCON register (see Table 12) allows switching from 12 clock cycles per instruction to 6 clock cycles and vice versa. At reset, the standard speed is activated (STD mode).</li> <li>Setting this bit activates the X2 feature (X2 mode) for the CPU Clock only (see Figure 5.).</li> <li>The Timers 0, 1 and 2, Uart, PCA, Watchdog or CAN switch in X2 mode only if the corresponding bit is cleared in the CKCON register.</li> <li>The clock for the whole circuit and peripheral is first divided by two before being used by the CPU core and peripherals. This allows any cyclic ratio to be accepted on the XTAL1 input. In X2 mode, as this divider is bypassed, the signals on XTAL1 must have a cyclic ratio between 40 to 60%. Figure 5. shows the clock generation block diagram. The X2 bit is validated on the XTAL1÷2 rising edge to avoid glitches when switching from the X2 to the STD mode. Figure 6 shows the mode switching waveforms.</li> </ul> |

Warm Reset

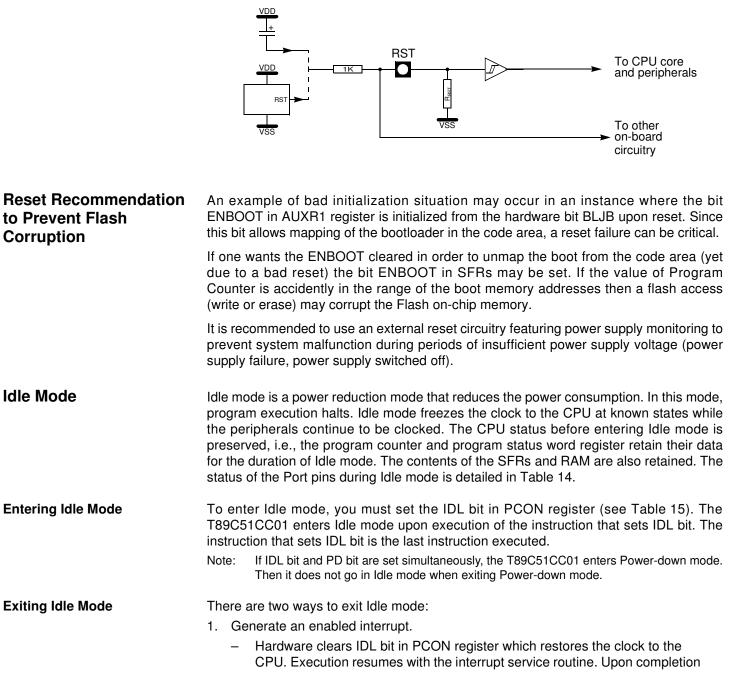

To achieve a valid reset, the reset signal must be maintained for at least 2 machine cycles (24 oscillator clock periods) while the oscillator is running. The number of clock periods is mode independent (X2 or X1).

Watchdog ResetAs detailed in Section "PCA Watchdog Timer", page 123, the WDT generates a 96-clock<br/>period pulse on the RST pin. In order to properly propagate this pulse to the rest of the<br/>application in case of external capacitor or power-supply supervisor circuit, a 1KΩ resis-<br/>tor must be added as shown Figure 8.

#### Figure 8. Reset Circuitry for WDT reset out usage

## **Data Memory**

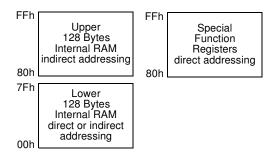

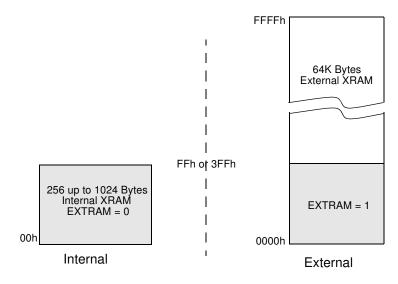

The T89C51CC01 provides data memory access in two different spaces:

- 1. The internal space mapped in three separate segments:

- the lower 128 Bytes RAM segment.

- the upper 128 Bytes RAM segment.

- the expanded 1024 Bytes RAM segment (XRAM).

- 2. The external space.

A fourth internal segment is available but dedicated to Special Function Registers, SFRs, (addresses 80h to FFh) accessible by direct addressing mode.

Figure 11 shows the internal and external data memory spaces organization.

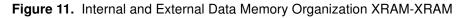

## **External Space**

#### **Memory Interface**

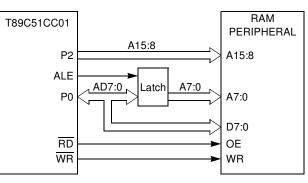

The external memory interface comprises the external bus (port 0 and port 2) as well as the bus control signals ( $\overline{RD}$ ,  $\overline{WR}$ , and ALE).

Figure 13 shows the structure of the external address bus. P0 carries address A7:0 while P2 carries address A15:8. Data D7:0 is multiplexed with A7:0 on P0. Table 17 describes the external memory interface signals.

Table 17. External Data Memory Interface Signals

| Signal<br>Name | Туре | Description                                                                                                   | Alternative<br>Function |

|----------------|------|---------------------------------------------------------------------------------------------------------------|-------------------------|

| A15:8          | 0    | Address Lines<br>Upper address lines for the external bus.                                                    | P2.7:0                  |

| AD7:0          | I/O  | Address/Data Lines<br>Multiplexed lower address lines and data for the external<br>memory.                    | P0.7:0                  |

| ALE            | 0    | Address Latch Enable<br>ALE signals indicates that valid address information are available<br>on lines AD7:0. | -                       |

| RD             | 0    | <b>Read</b><br>Read signal output to external data memory.                                                    | P3.7                    |

| WR             | 0    | <b>Write</b><br>Write signal output to external memory.                                                       | P3.6                    |

#### **External Bus Cycles**

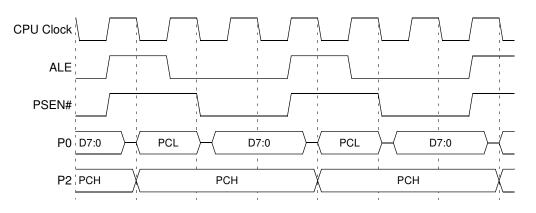

This section describes the bus cycles the T89C51CC01 executes to read (see Figure 14), and write data (see Figure 15) in the external data memory.

External memory cycle takes 6 CPU clock periods. This is equivalent to 12 oscillator clock period in standard mode or 6 oscillator clock periods in X2 mode. For further information on X2 mode.

Slow peripherals can be accessed by stretching the read and write cycles. This is done using the M0 bit in AUXR register. Setting this bit changes the width of the RD and WR signals from 3 to 15 CPU clock periods.

For simplicity, the accompanying figures depict the bus cycle waveforms in idealized form and do not provide precise timing information. For bus cycle timing parameters refer to the Section "AC Characteristics".

### Figure 19. External Code Fetch Waveforms

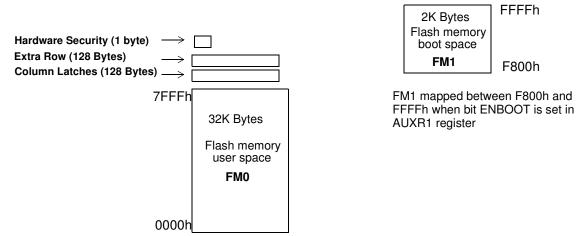

#### Flash Memory Architecture

T89C51CC01 features two on-chip Flash memories:

- Flash memory FM0:

- containing 32K Bytes of program memory (user space) organized into 128 byte pages,

- Flash memory FM1: 2K Bytes for boot loader and Application Programming Interfaces (API).

The FM0 can be program by both parallel programming and Serial In-System-Programming (ISP) whereas FM1 supports only parallel programming by programmers. The ISP mode is detailed in the "In-System-Programming" section.

All Read/Write access operations on Flash Memory by user application are managed by a set of API described in the "In-System-Programming" section.

### Figure 20. Flash Memory Architecture

## A/T89C51CC01

Note: The last page address used when loading the column latch is the one used to select the page programming address.

#### **Programming the Flash Spaces**

User

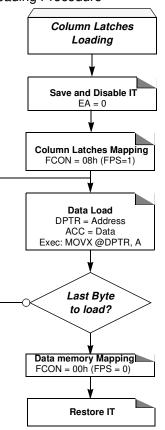

The following procedure is used to program the User space and is summarized in Figure 22:

- Load up to one page of data in the column latches from address 0000h to 7FFFh.

- Save then disable the interrupts.

- Launch the programming by writing the data sequence 50h followed by A0h in FCON register (only from FM1).

- The end of the programming indicated by the FBUSY flag cleared.

- Restore the interrupts.

Extra Row

The following procedure is used to program the Extra Row space and is summarized in Figure 22:

- Load data in the column latches from address FF80h to FFFFh.

- Save then disable the interrupts.

- Launch the programming by writing the data sequence 52h followed by A2h in FCON register. This step of the procedure must be executed from FM1. The end of the programming indicated by the FBUSY flag cleared. The end of the programming indicated by the FBUSY flag cleared.

- Restore the interrupts.

## **Boot Process**

| Software Boot Process<br>Example | Many algorithms can be used for the software boot process. Below are descriptions of the different flags and Bytes.                                                                                                                                                                                                                                                                                                                                                                      |

|----------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                  | <ul> <li>Boot Loader Jump Bit (BLJB):</li> <li>This bit indicates if on RESET the user wants to jump to this application at address @0000h on FM0 or execute the boot loader at address @F800h on FM1.</li> <li>BLJB = 0 (i.e. bootloader FM1 executed after a reset) is the default Atmel factory programming.</li> <li>To read or modify this bit, the APIs are used.</li> </ul>                                                                                                       |

|                                  | Boot Vector Address (SBV):<br>- This byte contains the MSB of the user boot loader address in FM0.<br>- The default value of SBV is FCh (no user boot loader in FM0).<br>- To read or modify this byte, the APIs are used.                                                                                                                                                                                                                                                               |

|                                  | Extra Byte (EB) and Boot Status Byte (BSB):<br>- These Bytes are reserved for customer use.<br>- To read or modify these Bytes, the APIs are used.                                                                                                                                                                                                                                                                                                                                       |

| Hardware Boot Process            | At the falling edge of RESET, the bit ENBOOT in AUXR1 register is initialized with the value of Boot Loader Jump Bit (BLJB).                                                                                                                                                                                                                                                                                                                                                             |

|                                  | Further at the falling edge of RESET if the following conditions (called Hardware condi-<br>tion) are detected. The FCON register is initialized with the value 00h and the PC is<br>initialized with F800h (FM1 lower byte = Bootloader entry point).                                                                                                                                                                                                                                   |

|                                  | <ul> <li>Hardware Conditions:</li> <li>PSEN low<sup>(1)</sup></li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                                  | • EA high,                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                                  | <ul> <li>ALE high (or not connected).</li> <li>The Hardware condition forces the bootloader to be executed, whatever BLJB value is.</li> </ul>                                                                                                                                                                                                                                                                                                                                           |

|                                  | Then BLBJ will be checked.                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                                  | If no hardware condition is detected, the FCON register is initialized with the value F0h. Then BLJB value will be checked.                                                                                                                                                                                                                                                                                                                                                              |

|                                  | Conditions are:                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                                  | <ul> <li>If bit BLJB = 1:<br/>User application in FM0 will be started at @0000h (standard reset).</li> </ul>                                                                                                                                                                                                                                                                                                                                                                             |

|                                  | <ul> <li>If bit BLJB = 0:<br/>Boot loader will be started at @F800h in FM1.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                   |

|                                  | <ol> <li>Note: 1. As PSEN is an output port in normal operating mode (running user applications or bootloader applications) after reset it is recommended to release PSEN after the falling edge of Reset is signaled.<br/>The hardware conditions are sampled at reset signal Falling Edge, thus they can be released at any time when reset input is low.</li> <li>2. To ensure correct microcontroller startup, the PSEN pin should not be tied to ground during power-on.</li> </ol> |

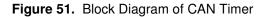

## Time Trigger Communication (TTC) and Message Stamping

The T89C51CC01 has a programmable 16-bit Timer (CANTIMH and CANTIML) for message stamp and TTC.

This CAN Timer starts after the CAN controller is enabled by the ENA bit in the CANG-CON register.

Two modes in the timer are implemented:

- Time Trigger Communication:

- Capture of this timer value in the CANTTCH and CANTTCL registers on Start Of Frame (SOF) or End Of Frame (EOF), depending on the SYNCTTC bit in the CANGCON register, when the network is configured in TTC by the TTC bit in the CANGCON register.

Note: In this mode, CAN only sends the frame once, even if an error occurs.

- Message Stamping

- Capture of this timer value in the CANSTMPH and CANSTMPL registers of the message object which received or sent the frame.

- All messages can be stamps.

- The stamping of a received frame occurs when the RxOk flag is set.

- The stamping of a sent frame occurs when the TxOk flag is set.

The CAN Timer works in a roll-over from FFFFh to 0000h which serves as a time base.

When the timer roll-over from FFFFh to 0000h, an interrupt is generated if the ETIM bit in the interrupt enable register IEN1 is set.

## Registers

Table 58. CANGCON Register

CANGCON (S:ABh) CAN General Control Register

| 7             | 6            | 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 4                                                                                                                                                                                                                 | 3                                                                            | 2                             | 1                           | 0                              |  |

|---------------|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------|-------------------------------|-----------------------------|--------------------------------|--|

| ABRQ          | OVRQ         | TTC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | SYNCTTC                                                                                                                                                                                                           | AUTOBAUD                                                                     | TEST                          | ENA                         | GRES                           |  |

| Bit<br>Number | Bit Mnemonic | Descripti                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | on                                                                                                                                                                                                                |                                                                              |                               |                             |                                |  |

| 7             | ABRQ         | and DLC i<br>communic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | to-resetable b<br>register) is dor<br>cations are imr                                                                                                                                                             | it. A reset of the<br>le for each mes<br>nediately aborto<br>setting the app | sage object.<br>ed but the or | The pending<br>1-going comm | transmission<br>unication will |  |

| 6             | OVRQ         | Auto-rese<br>Set to ser                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Overload frame request (initiator)<br>Auto-resetable bit.<br>Set to send an overload frame after the next received message.<br>Cleared by the hardware at the beginning of transmission of the overload<br>frame. |                                                                              |                               |                             |                                |  |

| 5             | ттс          | set to sele                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | <b>in Timer Trigg</b><br>ect node in TT<br>sable TTC fea                                                                                                                                                          |                                                                              | ation                         |                             |                                |  |

| 4             | SYNCTTC      | When this<br>Frame.<br>When this                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | bit is clear the                                                                                                                                                                                                  | <b>C</b><br>TTC timer is ca<br>e TTC timer is c<br>he TTC mode.              | -                             |                             |                                |  |

| 3             | AUTOBAUD     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | <b>UD</b><br>ve listening m<br>isable listening                                                                                                                                                                   |                                                                              |                               |                             |                                |  |

| 2             | TEST         | Test mode<br>use.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | e. The test mo                                                                                                                                                                                                    | de is intended f                                                             | or factory te                 | sting and not               | for customer                   |  |

| 1             | ENA/STB      | Enable/Standby CAN Controller<br>When this bit is set, it enables the CAN controller and its input clock.<br>When this bit is clear, the on-going communication is terminated normally and<br>the CAN controller state of the machine is frozen (the ENCH bit of each<br>message object does not change).<br>In the standby mode, the transmitter constantly provides a recessive level; the<br>receiver is not activated and the input clock is stopped in the CAN controller.<br>During the disable mode, the registers and the mailbox remain accessible.<br>Note that two clock periods are needed to start the CAN controller state of the<br>machine. |                                                                                                                                                                                                                   |                                                                              |                               |                             |                                |  |

| 0             | GRES         | Auto-rese                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                   | <b>re reset)</b><br>reset command<br>Iller. After a res                      |                               |                             |                                |  |

Reset Value = 0000 0000b

## Table 75. CANSTCH Register

CANSTCH (S:B2h) CAN Message Object Status Register

| 7             | 6            | 5                                                                                                                                                                                                                                                                                                      | 4                                                                                                                                                                                                                                                                                                                                                                                   | 3                                          | 2    | 1    | 0     |  |  |

|---------------|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------|------|------|-------|--|--|

| DLCW          | ТХОК         | RXOK                                                                                                                                                                                                                                                                                                   | BERR                                                                                                                                                                                                                                                                                                                                                                                | SERR                                       | CERR | FERR | AERR  |  |  |

| Bit<br>Number | Bit Mnemonic | Descripti                                                                                                                                                                                                                                                                                              | on                                                                                                                                                                                                                                                                                                                                                                                  |                                            |      |      |       |  |  |

| 7             | DLCW         | The incom                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                     | rning<br>does not have<br>le CANCONCI      |      |      |       |  |  |

| 6             | тхок         | The comn<br>When the<br>are enable<br>supplied f                                                                                                                                                                                                                                                       | <b>Transmit OK</b><br>The communication enabled by transmission is completed.<br>When the controller is ready to send a frame, if two or more message objects<br>are enabled as producers, the lower index message object (0 to 13) is<br>supplied first.<br>This flag can generate an interrupt and it must be cleared by software.                                                |                                            |      |      |       |  |  |

| 5             | RXOK         | The comm<br>In the cas<br>message                                                                                                                                                                                                                                                                      | <b>Receive OK</b><br>The communication enabled by reception is completed.<br>In the case of two or more message object reception hits, the lower index<br>message object (0 to 13) is updated first.<br>This flag can generate an interrupt and it must be cleared by software.                                                                                                     |                                            |      |      |       |  |  |

| 4             | BERR         | The bit va<br>Exception<br>the monito<br>and the ac<br>error fram                                                                                                                                                                                                                                      | <b>Bit Error (Only in Transmission)</b><br>The bit value monitored is different from the bit value sent.<br>Exceptions:<br>the monitored recessive bit sent as a dominant bit during the arbitration field<br>and the acknowledge slot detecting a dominant bit during the sending of an<br>error frame.<br>This flag can generate an interrupt and it must be cleared by software. |                                            |      |      |       |  |  |

| 3             | SERR         |                                                                                                                                                                                                                                                                                                        | of more than                                                                                                                                                                                                                                                                                                                                                                        | five consecuti<br>an interrupt an          |      |      |       |  |  |

| 2             | CERR         | <b>CRC Error</b><br>The receiver performs a CRC check on each destuffed received message from the start of frame up to the data field.<br>If this checking does not match with the destuffed CRC field, a CRC error is set.<br>This flag can generate an interrupt and it must be cleared by software. |                                                                                                                                                                                                                                                                                                                                                                                     |                                            |      |      |       |  |  |

| 1             | FERR         | Form Error<br>The form error results from one or more violations of the fixed form in the<br>following bit fields:<br>CRC delimiter<br>acknowledgment delimiter<br>end_of_frame<br>This flag can generate an interrupt.                                                                                |                                                                                                                                                                                                                                                                                                                                                                                     |                                            |      |      |       |  |  |

| 0             | AERR         | No detect                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                     | or<br>hinant bit in the<br>an interrupt an | -    |      | ware. |  |  |

Note: See Figure 46.

No default value after reset.

#### Table 85. CANIDM2 Register for V2.0 part A

CANIDM2 for V2.0 part A (S:C5h) CAN Identifier Mask Registers 2

| 7             | 6            | 5                        | 4                                                                                                     | 3 | 2 | 1 | 0 |  |

|---------------|--------------|--------------------------|-------------------------------------------------------------------------------------------------------|---|---|---|---|--|

| IDMSK 2       | IDMSK 1      | IDMSK 0                  | -                                                                                                     | - | - | - | - |  |

| Bit<br>Number | Bit Mnemonie | c Descripti              | Description                                                                                           |   |   |   |   |  |

| 7-5           | IDTMSK2:0    | 0 - compa<br>1 - bit con | IDentifier Mask Value<br>0 - comparison true forced.<br>1 - bit comparison enabled.<br>See Figure 50. |   |   |   |   |  |

| 4-0           | -            |                          | <b>Reserved</b><br>The values read from these bits are indeterminate. Do not set these bits.          |   |   |   |   |  |

No default value after reset.

#### Table 86. CANIDM3 Register for V2.0 part A

CANIDM3 for V2.0 part A (S:C6h) CAN Identifier Mask Registers 3

| 7             | 6           | 5           | 4                                                              | 3 | 2 | 1 | 0 |  |

|---------------|-------------|-------------|----------------------------------------------------------------|---|---|---|---|--|

| -             | -           | -           | -                                                              | - | - | - | - |  |

| Bit<br>Number | Bit Mnemoni | Description |                                                                |   |   |   |   |  |

| 7-0           | -           |             | Reserved<br>The values read from these bits are indeterminate. |   |   |   |   |  |

No default value after reset.

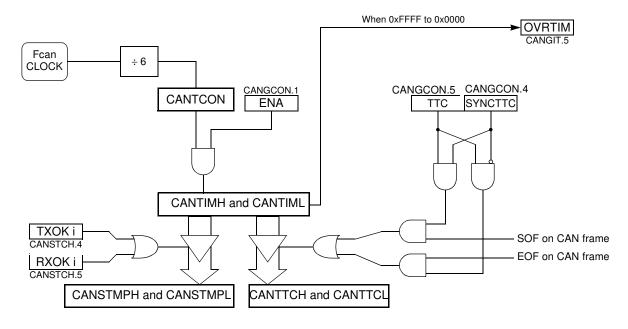

## High Speed Output Mode

In this mode the CEX output (on port 1) associated with the PCA module will toggle each time a match occurs between the PCA counter and the module's capture registers. To activate this mode the TOG, MAT, and ECOM bits in the module's CCAPMn SFR must be set.

Figure 57. PCA High Speed Output Mode

### Pulse Width Modulator Mode

All the PCA modules can be used as PWM outputs. The output frequency depends on the source for the PCA timer. All the modules will have the same output frequency because they all share the PCA timer. The duty cycle of each module is independently variable using the module's capture register CCAPLn. When the value of the PCA CL SFR is less than the value in the module's CCAPLn SFR the output will be low, when it is equal to or greater than it, the output will be high. When CL overflows from FF to 00, CCAPLn is reloaded with the value in CCAPHn. the allows the PWM to be updated without glitches. The PWM and ECOM bits in the module's CCAPMn register must be set to enable the PWM mode.

## Table 101. CCON Register

CCON (S:D8h) PCA Counter Control Register

| 7             | 6               | 5                                                                                                                                                                                                            | 4                                                                                                                                                                                                            | 3                                                               | 2              | 1            | 0           |  |

|---------------|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------|----------------|--------------|-------------|--|

| CF            | CR              | -                                                                                                                                                                                                            | CCF4                                                                                                                                                                                                         | CCF3                                                            | CCF2           | CCF1         | CCF0        |  |

| Bit<br>Number | Bit<br>Mnemonic | Description                                                                                                                                                                                                  |                                                                                                                                                                                                              |                                                                 |                |              |             |  |

| 7             | CF              | Set by hardw<br>interrupt requ                                                                                                                                                                               |                                                                                                                                                                                                              | PCA Timer/C<br>F bit in CMOD                                    |                | •            | rates a PCA |  |

| 6             | CR              | Clear to turn                                                                                                                                                                                                | Counter Run<br>the PCA Tim<br>le PCA Timer                                                                                                                                                                   | er/Counter off                                                  |                |              |             |  |

| 5             | -               | <b>Reserved</b><br>The value re                                                                                                                                                                              | ad from this b                                                                                                                                                                                               | it is indetermi                                                 | nate. Do not s | et this bit. |             |  |

| 4             | CCF4            | Set by hardw<br>interrupt requ                                                                                                                                                                               | PCA Module 4 Compare/Capture flag<br>Set by hardware when a match or capture occurs. This generates a PCA<br>interrupt request if the ECCF 4 bit in CCAPM 4 register is set.<br>Must be cleared by software. |                                                                 |                |              |             |  |

| 3             | CCF3            | Set by hardw<br>interrupt requ                                                                                                                                                                               | vare when a n                                                                                                                                                                                                | Capture flag<br>natch or captu<br>CF 3 bit in CC<br>ure.        |                |              | PCA         |  |

| 2             | CCF2            | PCA Module 2 Compare/Capture flag<br>Set by hardware when a match or capture occurs. This generates a PCA<br>interrupt request if the ECCF 2 bit in CCAPM 2 register is set.<br>Must be cleared by software. |                                                                                                                                                                                                              |                                                                 |                |              |             |  |

| 1             | CCF1            | PCA Module 1 Compare/Capture flag<br>Set by hardware when a match or capture occurs. This generates a PCA<br>interrupt request if the ECCF 1 bit in CCAPM 1 register is set.<br>Must be cleared by software. |                                                                                                                                                                                                              |                                                                 |                |              |             |  |

| 0             | CCF0            | Set by hardw<br>interrupt requ                                                                                                                                                                               | vare when a n                                                                                                                                                                                                | <b>Capture flag</b><br>natch or captu<br>CF 0 bit in CC<br>Ire. |                |              | PCA         |  |

Reset Value = 00X0 0000b

## Table 116. IEN1 Register

IEN1 (S:E8h) Interrupt Enable Register

| 7             | 6               | 5                                                                                                                                 | 4              | 3               | 2              | 1            | 0    |

|---------------|-----------------|-----------------------------------------------------------------------------------------------------------------------------------|----------------|-----------------|----------------|--------------|------|

| -             | -               | -                                                                                                                                 | -              | -               | ETIM           | EADC         | ECAN |

| Bit<br>Number | Bit<br>Mnemonic | Description                                                                                                                       |                |                 |                |              |      |

| 7             | -               | <b>Reserved</b><br>The value rea                                                                                                  | ad from this b | it is indetermi | nate. Do not s | et this bit. |      |

| 6             | -               | <b>Reserved</b><br>The value rea                                                                                                  | ad from this b | it is indetermi | nate. Do not s | et this bit. |      |

| 5             | -               | <b>Reserved</b><br>The value rea                                                                                                  | ad from this b | it is indetermi | nate. Do not s | et this bit. |      |

| 4             | -               | Reserved<br>The value rea                                                                                                         | ad from this b | it is indetermi | nate. Do not s | et this bit. |      |

| 3             | -               | Reserved<br>The value rea                                                                                                         | ad from this b | it is indetermi | nate. Do not s | et this bit. |      |

| 2             | ETIM            | Timer Overrun Interrupt Enable bit<br>Clear to disable the timer overrun interrupt.<br>Set to enable the timer overrun interrupt. |                |                 |                |              |      |

| 1             | EADC            | ADC Interrupt Enable bit<br>Clear to disable the ADC interrupt.<br>Set to enable the ADC interrupt.                               |                |                 |                |              |      |

| 0             | ECAN            | CAN Interrupt Enable bit<br>Clear to disable the CAN interrupt.<br>Set to enable the CAN interrupt.                               |                |                 |                |              |      |

Reset Value = xxxx x000b bit addressable

#### External Program Memory Characteristics

#### Table 123. Symbol Description

| Symbol            | Parameter                          |

|-------------------|------------------------------------|

| Т                 | Oscillator clock period            |

| T <sub>LHLL</sub> | ALE pulse width                    |

| T <sub>AVLL</sub> | Address Valid to ALE               |

| T <sub>LLAX</sub> | Address Hold After ALE             |

| T <sub>LLIV</sub> | ALE to Valid Instruction In        |

| T <sub>LLPL</sub> | ALE to PSEN                        |

| T <sub>PLPH</sub> | PSEN Pulse Width                   |

| T <sub>PLIV</sub> | PSEN to Valid Instruction In       |

| T <sub>PXIX</sub> | Input Instruction Hold After PSEN  |

| T <sub>PXIZ</sub> | Input Instruction Float After PSEN |

| T <sub>AVIV</sub> | Address to Valid Instruction In    |

| T <sub>PLAZ</sub> | PSEN Low to Address Float          |

## Table 124. AC Parameters for a Fix Clock (F = 40 MHz)

| Symbol            | Min | Max | Units |

|-------------------|-----|-----|-------|

| Т                 | 25  |     | ns    |

| T <sub>LHLL</sub> | 40  |     | ns    |

| T <sub>AVLL</sub> | 10  |     | ns    |

| T <sub>LLAX</sub> | 10  |     | ns    |

| T <sub>LLIV</sub> |     | 70  | ns    |

| T <sub>LLPL</sub> | 15  |     | ns    |

| T <sub>PLPH</sub> | 55  |     | ns    |

| T <sub>PLIV</sub> |     | 35  | ns    |

| T <sub>PXIX</sub> | 0   |     | ns    |

| T <sub>PXIZ</sub> |     | 18  | ns    |

| T <sub>AVIV</sub> |     | 85  | ns    |

| T <sub>PLAZ</sub> |     | 10  | ns    |

| Symbol            | Туре | Standard<br>Clock | X2 Clock  | X parameter | Units |

|-------------------|------|-------------------|-----------|-------------|-------|

| T <sub>LHLL</sub> | Min  | 2 T - x           | T - x     | 10          | ns    |

| T <sub>AVLL</sub> | Min  | T - x             | 0.5 T - x | 15          | ns    |

| T <sub>LLAX</sub> | Min  | T - x             | 0.5 T - x | 15          | ns    |

| T <sub>LLIV</sub> | Max  | 4 T - x           | 2 T - x   | 30          | ns    |

| T <sub>LLPL</sub> | Min  | T - x             | 0.5 T - x | 10          | ns    |

| T <sub>PLPH</sub> | Min  | 3 T - x           | 1.5 T - x | 20          | ns    |

| T <sub>PLIV</sub> | Max  | 3 T - x           | 1.5 T - x | 40          | ns    |

| T <sub>PXIX</sub> | Min  | х                 | х         | 0           | ns    |

| T <sub>PXIZ</sub> | Max  | T - x             | 0.5 T - x | 7           | ns    |

| T <sub>AVIV</sub> | Max  | 5 T - x           | 2.5 T - x | 40          | ns    |

| T <sub>PLAZ</sub> | Max  | х                 | х         | 10          | ns    |

Table 125. AC Parameters for a Variable Clock

## **External Program Memory Read Cycle**

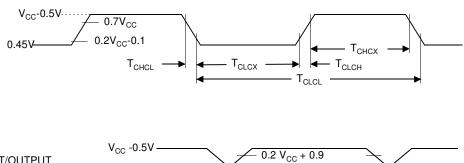

#### **External Clock Drive** Waveforms

**AC Testing Input/Output**

Waveforms

INPUT/OUTPUT

0.2 V<sub>CC</sub> - 0.1

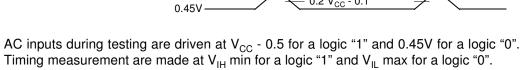

**Float Waveforms**

For timing purposes as port pin is no longer floating when a 100 mV change from load voltage occurs and begins to float when a 100 mV change from the loaded  $\rm V_{OH}/V_{OL}$  level occurs.  $I_{OL}/I_{OH} \ge \pm 20$  mA.

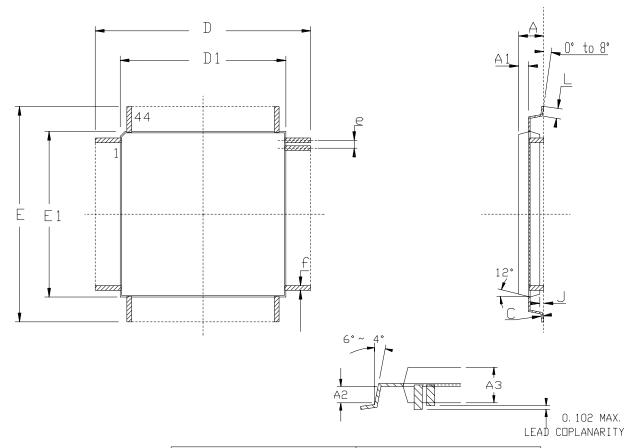

## Package Drawings

## VQFP44

|     | М     | М      | INCH      |       |  |

|-----|-------|--------|-----------|-------|--|

|     | Min   | Max    | Min       | Ma×   |  |

| А   | _     | 1, 60  | _         | , 063 |  |

| A 1 | Ο,    | 64 REF | . 025 REF |       |  |

| A2  | Ο,    | 64 REF | .025 REF  |       |  |

| АЗ  | 1, 35 | 1, 45  | . 053     | , 057 |  |

| D   | 11,90 | 12.10  | , 468     | , 476 |  |

| D 1 | 9, 90 | 10, 10 | , 390     | , 398 |  |

| E   | 11,90 | 12, 10 | , 468     | , 476 |  |

| E 1 | 9, 90 | 10, 10 | . 390     | , 398 |  |

| J   | 0, 05 | _      | , 002     | _     |  |

| L   | 0, 45 | 0, 75  | . 018     | , 030 |  |

| e   | 0, 8  | O BSC  | .0315 BSC |       |  |

| f   | 0, 3  | 5 BSC  | , O14 BSC |       |  |

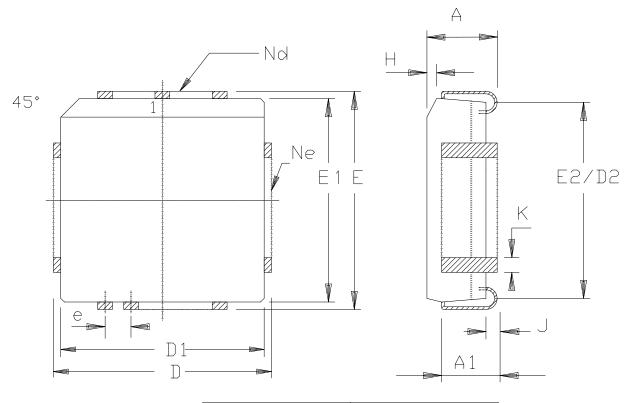

PLCC44

|         | ММ    |        | INCH  |       |

|---------|-------|--------|-------|-------|

| A       | 4. 20 | 4. 57  | , 165 | , 180 |

| A 1     | 2, 29 | 3.04   | , 090 | . 120 |

| D       | 17.40 | 17.65  | , 685 | . 695 |

| D1      | 16.44 | 16, 66 | , 647 | , 656 |

| D2      | 14.99 | 16.00  | , 590 | , 630 |

| E       | 17.40 | 17.65  | , 685 | , 695 |

| E 1     | 16.44 | 16, 66 | , 647 | , 656 |

| E2      | 14.99 | 16.00  | , 590 | , 630 |

| e       | 1. 27 | BSC    | , 050 | BSC   |

| н       | 1.07  | 1.42   | . 042 | . 056 |

| J       | 0.51  | -      | , 020 | _     |

| К       | 0, 33 | 0, 53  | . 013 | . 021 |

| Nd      | 1 1   |        | 1 1   |       |

| Ne      | 1 1   |        | 1 1   |       |

| PKG STD |       | 00     |       |       |