#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Obsolete                                                                     |

|----------------------------|------------------------------------------------------------------------------|

| Core Processor             | 80C51                                                                        |

| Core Size                  | 8-Bit                                                                        |

| Speed                      | 40MHz                                                                        |

| Connectivity               | CANbus, UART/USART                                                           |

| Peripherals                | POR, PWM, WDT                                                                |

| Number of I/O              | 34                                                                           |

| Program Memory Size        | 32KB (32K x 8)                                                               |

| Program Memory Type        | FLASH                                                                        |

| EEPROM Size                | 2K x 8                                                                       |

| RAM Size                   | 1.25K x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                                    |

| Data Converters            | A/D 8x10b                                                                    |

| Oscillator Type            | External                                                                     |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                                |

| Package / Case             | 64-LFBGA, CSPBGA                                                             |

| Supplier Device Package    | 64-CSPBGA (8x8)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/t89c51cc01ca-7ctim |

|                            |                                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

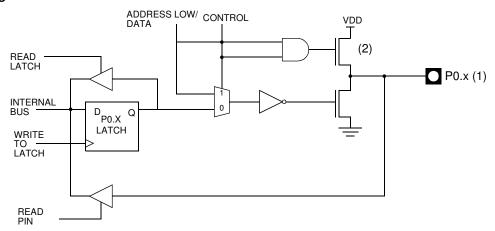

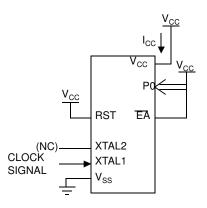

Figure 2. Port 0 Structure

- Notes: 1. Port 0 is precluded from use as general-purpose I/O Ports when used as address/data bus drivers.

- 2. Port 0 internal strong pull-ups assist the logic-one output for memory bus cycles only. Except for these bus cycles, the pull-up FET is off, Port 0 outputs are open-drain.

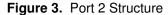

- Notes: 1. Port 2 is precluded from use as general-purpose I/O Ports when as address/data bus drivers.

- Port 2 internal strong pull-ups FET (P1 in FiGURE) assist the logic-one output for memory bus cycle.

When Port 0 and Port 2 are used for an external memory cycle, an internal control signal switches the output-driver input from the latch output to the internal address/data line.

# Read-Modify-Write Instructions

Some instructions read the latch data rather than the pin data. The latch based instructions read the data, modify the data and then rewrite the latch. These are called "Read-Modify-Write" instructions. Below is a complete list of these special instructions (see Table ). When the destination operand is a Port or a Port bit, these instructions read the latch rather than the pin:

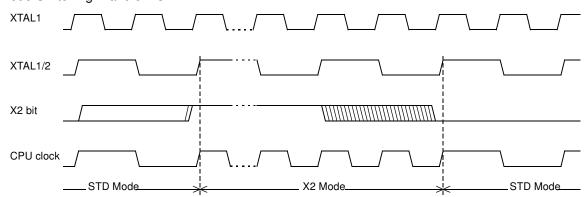

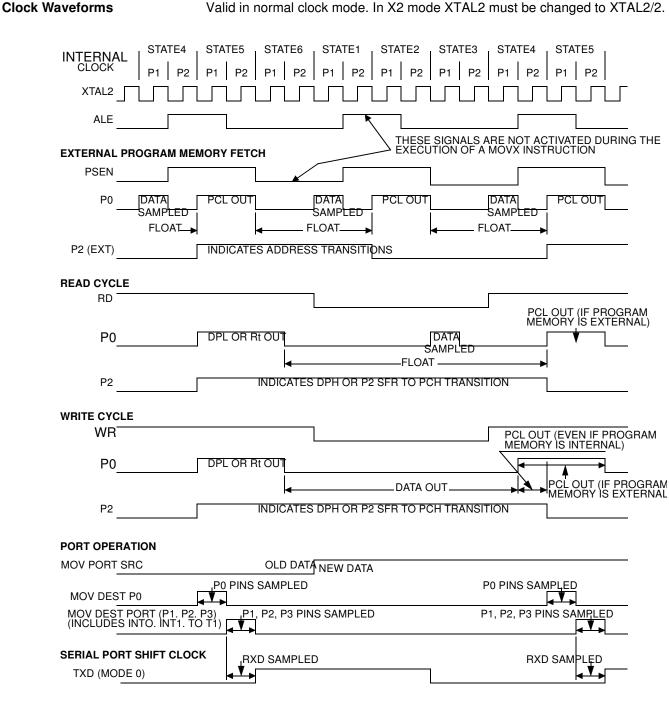

### Figure 6. Mode Switching Waveforms

Note: In order to prevent any incorrect operation while operating in the X2 mode, users must be aware that all peripherals using the clock frequency as a time reference (UART, timers...) will have their time reference divided by two. For example a free running timer generating an interrupt every 20 ms will then generate an interrupt every 10 ms. A UART with a 4800 baud rate will have a 9600 baud rate.

# A/T89C51CC01

# Sharing Instructions Table 29. Instructions shared

| Action | RAM | XRAM<br>ERAM | EEPROM<br>DATA | Boot<br>FLASH | FM0   | Hardware<br>Byte | XROW  |

|--------|-----|--------------|----------------|---------------|-------|------------------|-------|

| Read   | MOV | MOVX         | MOVX           | MOVC          | MOVC  | MOVC             | MOVC  |

| Write  | MOV | MOVX         | MOVX           | -             | by cl | by cl            | by cl |

by cl: using Column Latch Note:

## Table 30. Read MOVX A, @DPTR

| EEE bit in<br>EECON<br>Register | FPS in<br>FCON Register | ENBOOT | EA | XRAM<br>ERAM | EEPROM<br>DATA | Flash<br>Column<br>Latch |

|---------------------------------|-------------------------|--------|----|--------------|----------------|--------------------------|

| 0                               | 0                       | Х      | х  | OK           |                |                          |

| 0                               | 1                       | Х      | х  | ОК           |                |                          |

| 1                               | 0                       | Х      | х  |              | ОК             |                          |

| 1                               | 1                       | Х      | Х  | OK           |                |                          |

## Table 31. Write MOVX @DPTR,A

| EEE bit in<br>EECON<br>Register | FPS bit in<br>FCON Register | ENBOOT | EA | XRAM<br>ERAM | EEPROM<br>Data | Flash<br>Column<br>Latch |

|---------------------------------|-----------------------------|--------|----|--------------|----------------|--------------------------|

| 0                               | 0                           | х      | Х  | ОК           |                |                          |

| 0                               | 4                           | х      | 1  |              |                | ОК                       |

| 0                               | I                           | ^      | 0  | ОК           |                |                          |

| 1                               | 0                           | х      | Х  |              | ОК             |                          |

| 1                               | 1                           | х      | 1  |              |                | ОК                       |

| I                               | I                           | ~      | 0  | ОК           |                |                          |

## Table 39. PCON Register

PCON (S:87h) Power Control Register

| 7             | 6               | 5                                                                                                                                                             | 4                                                                                                             | 3              | 2          | 1  | 0             |  |

|---------------|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|----------------|------------|----|---------------|--|

| SMOD1         | SMOD0           | _                                                                                                                                                             | POF                                                                                                           | GF1            | GF0        | PD | IDL           |  |

| Bit<br>Number | Bit<br>Mnemonic | Description                                                                                                                                                   |                                                                                                               |                |            |    |               |  |

| 7             | SMOD1           | Serial port I<br>Set to select                                                                                                                                |                                                                                                               | rate in mode 1 | l, 2 or 3. |    |               |  |

| 6             | SMOD0           | Clear to sele                                                                                                                                                 | Serial port Mode bit 0<br>Clear to select SM0 bit in SCON register.<br>Set to select FE bit in SCON register. |                |            |    |               |  |

| 5             | -               | <b>Reserved</b><br>The value re                                                                                                                               | <b>Reserved</b><br>The value read from this bit is indeterminate. Do not set this bit.                        |                |            |    |               |  |

| 4             | POF             | <b>Power-Off Flag</b><br>Clear to recognize next reset type.<br>Set by hardware when VCC rises from 0 to its nominal voltage. Can also be set<br>by software. |                                                                                                               |                |            |    | n also be set |  |

| 3             | GF1             | General-purpose Flag<br>Cleared by user for general-purpose usage.<br>Set by user for general-purpose usage.                                                  |                                                                                                               |                |            |    |               |  |

| 2             | GF0             | <b>General-purpose Flag</b><br>Cleared by user for general-purpose usage.<br>Set by user for general-purpose usage.                                           |                                                                                                               |                |            |    |               |  |

| 1             | PD              | Power-Down mode bit<br>Cleared by hardware when reset occurs.<br>Set to enter power-down mode.                                                                |                                                                                                               |                |            |    |               |  |

| 0             | IDL             | Idle mode bit<br>Clear by hardware when interrupt or reset occurs.<br>Set to enter idle mode.                                                                 |                                                                                                               |                |            |    |               |  |

Reset Value = 00X1 0000b Not bit addressable

| Timer 1                                   | Timer 1 is identical to Timer 0 excepted for Mode 3 which is a hold-count mode. The fol-<br>lowing comments help to understand the differences:                                                                                                                                                                                                                                                                                          |

|-------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                           | <ul> <li>Timer 1 functions as either a Timer or event Counter in three modes of operation.</li> <li>Figure 31 to Figure 33 show the logical configuration for modes 0, 1, and 2. Timer 1's mode 3 is a hold-count mode.</li> </ul>                                                                                                                                                                                                       |

|                                           | • Timer 1 is controlled by the four high-order bits of TMOD register (see Figure 41) and bits 2, 3, 6 and 7 of TCON register (see Figure 40). TMOD register selects the method of Timer gating (GATE1), Timer or Counter operation (C/T1#) and mode of operation (M11 and M01). TCON register provides Timer 1 control functions: overflow flag (TF1), run control bit (TR1), interrupt flag (IE1) and interrupt type control bit (IT1). |

|                                           | • Timer 1 can serve as the Baud Rate Generator for the Serial Port. Mode 2 is best suited for this purpose.                                                                                                                                                                                                                                                                                                                              |

|                                           | <ul> <li>For normal Timer operation (GATE1 = 0), setting TR1 allows TL1 to be incremented<br/>by the selected input. Setting GATE1 and TR1 allows external pin INT1# to control<br/>Timer operation.</li> </ul>                                                                                                                                                                                                                          |

|                                           | • Timer 1 overflow (count rolls over from all 1s to all 0s) sets the TF1 flag generating an interrupt request.                                                                                                                                                                                                                                                                                                                           |

|                                           | • When Timer 0 is in mode 3, it uses Timer 1's overflow flag (TF1) and run control bit (TR1). For this situation, use Timer 1 only for applications that do not require an interrupt (such as a Baud Rate Generator for the Serial Port) and switch Timer 1 in and out of mode 3 to turn it off and on.                                                                                                                                  |

|                                           | It is important to stop Timer/Counter before changing mode.                                                                                                                                                                                                                                                                                                                                                                              |

| Mode 0 (13-bit Timer)                     | Mode 0 configures Timer 1 as a 13-bit Timer, which is set up as an 8-bit Timer (TH1 reg-<br>ister) with a modulo-32 prescaler implemented with the lower 5 bits of the TL1 register<br>(see Figure 31). The upper 3 bits of TL1 register are ignored. Prescaler overflow incre-<br>ments TH1 register.                                                                                                                                   |

| Mode 1 (16-bit Timer)                     | Mode 1 configures Timer 1 as a 16-bit Timer with TH1 and TL1 registers connected in cascade (see Figure 32). The selected input increments TL1 register.                                                                                                                                                                                                                                                                                 |

| Mode 2 (8-bit Timer with Auto-<br>Reload) | Mode 2 configures Timer 1 as an 8-bit Timer (TL1 register) with automatic reload from TH1 register on overflow (see Figure 33). TL1 overflow sets TF1 flag in TCON register and reloads TL1 with the contents of TH1, which is preset by software. The reload leaves TH1 unchanged.                                                                                                                                                      |

| Mode 3 (Halt)                             | Placing Timer 1 in mode 3 causes it to halt and hold its count. This can be used to halt Timer 1 when TR1 run control bit is not available i.e. when Timer 0 is in mode 3.                                                                                                                                                                                                                                                               |

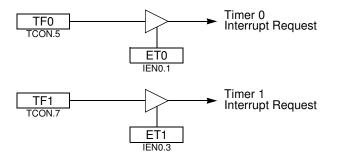

| Interrupt                                 | Each Timer handles one interrupt source that is the timer overflow flag TF0 or TF1. This flag is set every time an overflow occurs. Flags are cleared when vectoring to the Timer interrupt routine. Interrupts are enabled by setting $ETx$ bit in IEN0 register. This assumes interrupts are globally enabled by setting EA bit in IEN0 register.                                                                                      |

Figure 35. Timer Interrupt System

## Table 42. TH0 Register

TH0 (S:8Ch) Timer 0 High Byte Register

| 7             | 6               | 5            | 4          | 3 | 2 | 1 | 0 |

|---------------|-----------------|--------------|------------|---|---|---|---|

| -             | -               | -            | -          | - | - | - | - |

| Bit<br>Number | Bit<br>Mnemonic | Description  |            |   |   |   |   |

| 7:0           |                 | High Byte of | f Timer 0. |   |   |   |   |

Reset Value = 0000 0000b

#### Table 43. TL0 Register

TL0 (S:8Ah) Timer 0 Low Byte Register

| 7             | 6               | 5           | 4           | 3 | 2 | 1 | 0 |

|---------------|-----------------|-------------|-------------|---|---|---|---|

| -             | -               | -           | -           | - | - | - | - |

| Bit<br>Number | Bit<br>Mnemonic | Description | Description |   |   |   |   |

| 7:0           |                 | Low Byte of | Timer 0.    |   |   |   |   |

Reset Value = 0000 0000b

### Table 44. TH1 Register

TH1 (S:8Dh) Timer 1 High Byte Register

| 7             | 6               | 5           | 4          | 3 | 2 | 1 | 0 |

|---------------|-----------------|-------------|------------|---|---|---|---|

| -             | -               | -           | -          | - | - | - | - |

| Bit<br>Number | Bit<br>Mnemonic | Description |            |   |   |   |   |

| 7:0           |                 | High Byte o | f Timer 1. |   |   |   |   |

Reset Value = 0000 0000b

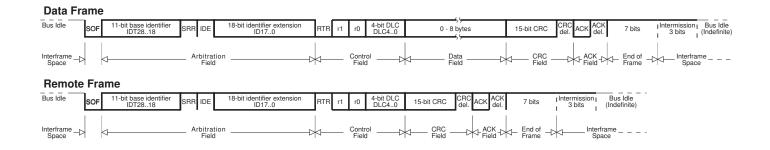

number of following data bytes in the "Data field". In a remote frame, the DLC contains the number of requested data bytes. The "Data field" that follows can hold up to 8 data bytes. The frame integrity is guaranteed by the following "Cyclic Redundant Check (CRC)" sum. The "ACKnowledge (ACK) field" compromises the ACK slot and the ACK delimiter. The bit in the ACK slot is sent as a recessive bit and is overwritten as a dominant bit by the receivers which have at this time received the data correctly. Correct messages are acknowledged by the receivers regardless of the result of the acceptance test. The end of the message is indicated by "End Of Frame (EOF)". The "Intermission Frame Space (IFS)" is the minimum number of bits separating consecutive messages. If there is no following bus access by any node, the bus remains idle.

## CAN Extended Frame

A message in the CAN extended frame format is likely the same as a message in CAN standard frame format. The difference is the length of the identifier used. The identifier is made up of the existing 11-bit identifier (base identifier) and an 18-bit extension (identifier extension). The distinction between CAN standard frame format and CAN extended frame format is made by using the IDE bit which is transmitted as dominant in case of a frame in CAN standard frame format, and transmitted as recessive in the other case.

| Format Co-existence | As the two formats have to co-exist on one bus, it is laid down which message has<br>higher priority on the bus in the case of bus access collision with different formats and<br>the same identifier / base identifier: The message in CAN standard frame format always<br>has priority over the message in extended format. |  |  |  |  |

|---------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

|                     | There are three different types of CAN modules available:                                                                                                                                                                                                                                                                     |  |  |  |  |

|                     | <ul> <li>2.0A - Considers 29 bit ID as an error</li> </ul>                                                                                                                                                                                                                                                                    |  |  |  |  |

|                     | <ul> <li>– 2.0B Passive - Ignores 29 bit ID messages</li> </ul>                                                                                                                                                                                                                                                               |  |  |  |  |

|                     | <ul> <li>2.0B Active - Handles both 11 and 29 bit ID Messages</li> </ul>                                                                                                                                                                                                                                                      |  |  |  |  |

| Bit Timing          | To ensure correct sampling up to the last bit, a CAN node needs to re-synch<br>throughout the entire frame. This is done at the beginning of each message with t<br>ing edge SOF and on each recessive to dominant edge.                                                                                                      |  |  |  |  |

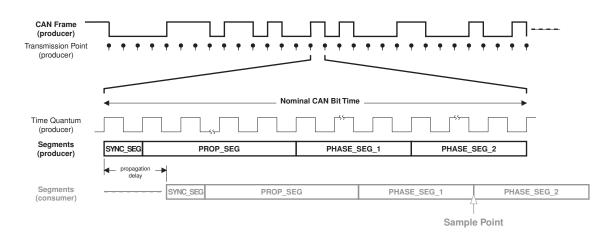

Bit Construction One CAN bit time is specified as four non-overlapping time segments. Each segment is constructed from an integer multiple of the Time Quantum. The Time Quantum or TQ is the smallest discrete timing resolution used by a CAN node.

# A/T89C51CC01

## Figure 41. CAN Bit Construction

| Synchronization Segment     | The first segment is used to synchronize the various bus nodes.                                                                                                                                                                                                                                                                                                                                         |

|-----------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                             | On transmission, at the start of this segment, the current bit level is output. If there is a bit state change between the previous bit and the current bit, then the bus state change is expected to occur within this segment by the receiving nodes.                                                                                                                                                 |

| Propagation Time Segment    | This segment is used to compensate for signal delays across the network.                                                                                                                                                                                                                                                                                                                                |

|                             | This is necessary to compensate for signal propagation delays on the bus line and through the transceivers of the bus nodes.                                                                                                                                                                                                                                                                            |

| Phase Segment 1             | Phase Segment 1 is used to compensate for edge phase errors.                                                                                                                                                                                                                                                                                                                                            |

|                             | This segment may be lengthened during resynchronization.                                                                                                                                                                                                                                                                                                                                                |

| Sample Point                | The sample point is the point of time at which the bus level is read and interpreted as the value of the respective bit. Its location is at the end of Phase Segment 1 (between the two Phase Segments).                                                                                                                                                                                                |

| Phase Segment 2             | This segment is also used to compensate for edge phase errors.                                                                                                                                                                                                                                                                                                                                          |

|                             | This segment may be shortened during resynchronization, but the length has to be at least as long as the information processing time and may not be more than the length of Phase Segment 1.                                                                                                                                                                                                            |

| Information Processing Time | It is the time required for the logic to determine the bit level of a sampled bit.                                                                                                                                                                                                                                                                                                                      |

|                             | The Information processing Time begins at the sample point, is measured in TQ and is fixed at 2 TQ for the Atmel CAN. Since Phase Segment 2 also begins at the sample point and is the last segment in the bit time, Phase Segment 2 minimum shall not be less than the Information processing Time.                                                                                                    |

| Bit Lengthening             | As a result of resynchronization, Phase Segment 1 may be lengthened or Phase Segment 2 may be shortened to compensate for oscillator tolerances. If, for example, the transmitter oscillator is slower than the receiver oscillator, the next falling edge used for resynchronization may be delayed. So Phase Segment 1 is lengthened in order to adjust the sample point and the end of the bit time. |

| Bit Shortening               | If, on the other hand, the transmitter oscillator is faster than the receiver one, the next falling edge used for resynchronization may be too early. So Phase Segment 2 in bit N is shortened in order to adjust the sample point for bit N+1 and the end of the bit time                                                             |

|------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Synchronization Jump Width   | The limit to the amount of lengthening or shortening of the Phase Segments is set by the Resynchronization Jump Width.                                                                                                                                                                                                                 |

|                              | This segment may not be longer than Phase Segment 2.                                                                                                                                                                                                                                                                                   |

| Programming the Sample Point | Programming of the sample point allows "tuning" of the characteristics to suit the bus.                                                                                                                                                                                                                                                |

|                              | Early sampling allows more Time Quanta in the Phase Segment 2 so the Synchroniza-<br>tion Jump Width can be programmed to its maximum. This maximum capacity to<br>shorten or lengthen the bit time decreases the sensitivity to node oscillator tolerances,<br>so that lower cost oscillators such as ceramic resonators may be used. |

Late sampling allows more Time Quanta in the Propagation Time Segment which allows a poorer bus topology and maximum bus length.

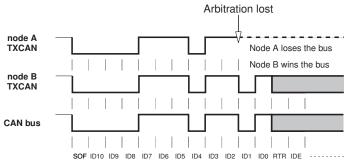

## ArbitrationFigure 42. Bus Arbitration

The CAN protocol handles bus accesses according to the concept called "Carrier Sense Multiple Access with Arbitration on Message Priority".

During transmission, arbitration on the CAN bus can be lost to a competing device with a higher priority CAN Identifier. This arbitration concept avoids collisions of messages whose transmission was started by more than one node simultaneously and makes sure the most important message is sent first without time loss.

The bus access conflict is resolved during the arbitration field mostly over the identifier value. If a data frame and a remote frame with the same identifier are initiated at the same time, the data frame prevails over the remote frame (c.f. RTR bit).

**Errors** The CAN protocol signals any errors immediately as they occur. Three error detection mechanisms are implemented at the message level and two at the bit level:

Error at Message Level

- Cyclic Redundancy Check (CRC) The CRC safeguards the information in the frame by adding redundant check bits at the transmission end. At the receiver these bits are re-computed and tested against the received bits. If they do not agree there has been a CRC error.

- Frame Check This mechanism verifies the structure of the transmitted frame by checking the bit fields against the fixed format and the frame size. Errors detected by frame checks are designated "format errors".

78 A/T89C51CC01

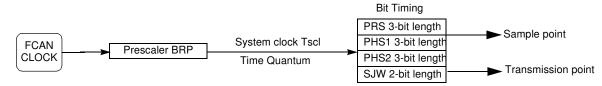

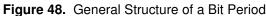

## **Bit Timing and Baud Rate**

FSM's (Finite State Machine) of the CAN channel need to be synchronous to the time quantum. So, the input clock for bit timing is the clock used into CAN channel FSM's.

Field and segment abbreviations:

- BRP: Baud Rate Prescaler.

- TQ: Time Quantum (output of Baud Rate Prescaler).

- SYNS: SYNchronization Segment is 1 TQ long.

- PRS: PRopagation time Segment is programmable to be 1, 2, ..., 8 TQ long.

- PHS1: PHase Segment 1 is programmable to be 1, 2, ..., 8 TQ long.

- PHS2: PHase Segment 2 is programmable to be superior or equal to the INFORMATION PROCESSING TIME and inferior or equal to TPHS1.

- INFORMATION PROCESSING TIME is 2 TQ.

- SJW: (Re) Synchronization Jump Width is programmable to be minimum of PHS1 and 4.

The total number of TQ in a bit time has to be programmed at least from 8 to 25.

### Figure 47. Sample And Transmission Point

The baud rate selection is made by Tbit calculation:

Tbit = Tsyns + Tprs + Tphs1 + Tphs2

- 1. Tsyns = Tscl = (BRP[5..0] + 1)/Fcan = 1TQ.

- 2. Tprs = (1 to 8) \* Tscl = (PRS[2..0]+ 1) \* Tscl

- 3. Tphs1 = (1 to 8) \* Tscl = (PHS1[2..0]+ 1) \* Tscl

- 4. Tphs2 = (1 to 8) \* Tscl = (PHS2[2..0]+ 1) \* Tscl Tphs2 = Max of (Tphs1 and 2TQ)

- 5. Tsjw = (1 to 4) \* Tscl = (SJW[1..0]+ 1) \* Tscl

The total number of Tscl (Time Quanta) in a bit time must be comprised between **8 to 25**.

# A/T89C51CC01

## Table 59. CANGSTA Register

CANGSTA (S:AAh Read Only) CAN General Status Register

| 7             | 6            | 5                            | 4                                                                                                                                                                                                            | 3                               | 2                                                            | 1                | 0              |  |

|---------------|--------------|------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|--------------------------------------------------------------|------------------|----------------|--|

| -             | OVFG         | -                            | TBSY                                                                                                                                                                                                         | RBSY                            | ENFG                                                         | BOFF             | ERRP           |  |

| Bit<br>Number | Bit Mnemonic | Description                  | on                                                                                                                                                                                                           |                                 |                                                              |                  |                |  |

| 7             | -            | <b>Reserved</b><br>The value |                                                                                                                                                                                                              | nis bit is indete               | erminate. Do n                                               | ot set this bit. |                |  |

| 6             | OVFG         | This statu<br>is sent.       |                                                                                                                                                                                                              | the hardware<br>rate an interru | as long as the<br>ıpt                                        | produced ove     | erload frame   |  |

| 5             | -            | Reserved<br>The value        |                                                                                                                                                                                                              | is bit is indete                | erminate. Do n                                               | ot set this bit. |                |  |

| 4             | TBSY         | generates<br>bit is also     | s bit is set by<br>a frame (rem<br>active during                                                                                                                                                             | ote, data, ove                  | as long as the<br>rload or error f<br>Spacing if a f<br>ipt. | rame) or an a    | ck field. This |  |

| 3             | RBSY         | monitors a                   | s bit is set by<br>a frame.                                                                                                                                                                                  | the hardware<br>rate an interru | as long as the<br>ıpt.                                       | CAN receive      | r acquires or  |  |

| 2             | ENFG         | Because a<br>bit gives th    | Enable On-chip CAN Controller Flag<br>Because an enable/disable command is not effective immediately, this status<br>bit gives the true state of a chosen mode.<br>This flag does not generate an interrupt. |                                 |                                                              |                  |                |  |

| 1             | BOFF         | Bus Off M<br>see Figur       |                                                                                                                                                                                                              |                                 |                                                              |                  |                |  |

| 0             | ERRP         | Error Pas<br>see Figur       | sive Mode<br>e 49                                                                                                                                                                                            |                                 |                                                              |                  |                |  |

Reset Value = x0x0 0000b

## Table 60. CANGIT Register

CANGIT (S:9Bh) CAN General Interrupt

| 7             | 6            | 5                                                               | 4                                                                                  | 3                                | 2                        | 1                | 0         |

|---------------|--------------|-----------------------------------------------------------------|------------------------------------------------------------------------------------|----------------------------------|--------------------------|------------------|-----------|

| CANIT         | -            | OVRTIM                                                          | OVRBUF                                                                             | SERG                             | CERG                     | FERG             | AERG      |

| Bit<br>Number | Bit Mnemonic | Descripti                                                       | on                                                                                 |                                  |                          |                  |           |

| 7             | CANIT        | This statu<br>interrupt c                                       | nterrupt Flag<br>s bit is the ima<br>controller.<br>used in the cas                | age of all the (                 |                          | r interrupts se  | nt to the |

| 6             | -            | Reserved<br>The value                                           | l<br>s read from th                                                                | is bit is indete                 | rminate. Do n            | ot set this bit. |           |

| 5             | OVRTIM       | This statu<br>If the bit E                                      | CAN Timer<br>s bit is set whe<br>TIM in the IE1<br>bit in order to                 | register is se                   | t, an interrupt          |                  |           |

| 4             | OVRBUF       |                                                                 | rrupt.<br>ed on<br>set when the<br>ole by user.                                    | buffer is full.                  |                          |                  |           |

| 3             | SERG         | Detection                                                       | or General<br>of more than t<br>can generate a                                     |                                  |                          |                  | ty.       |

| 2             | CERG         | The receive<br>from the s<br>If this che-<br>set.               | or General<br>ver performs a<br>tart of frame u<br>cking does no<br>can generate a | p to the data<br>t match with tl | field.<br>ne destuffed C | CRC field, a C   | -         |

| 1             | FERG         | The form<br>following b<br>CRC delin<br>acknowled<br>end_of_fra | niter<br>dgment delimi                                                             | ter                              |                          |                  | m in the  |

| 0             | AERG         | No detect                                                       | edgment Erro<br>ion of the dom<br>can generate a                                   | inant bit in the                 | -                        |                  |           |

Note: 1. This field is Read Only.

Reset Value = 0x00 0000b

#### Table 79. CANIDT4 Register for V2.0 part A

CANIDT4 for V2.0 part A (S:BFh) CAN Identifier Tag Registers 4

| 7             | 6            | 5                     | 4                                                                                     | 3           | 2        | 1 | 0             |  |

|---------------|--------------|-----------------------|---------------------------------------------------------------------------------------|-------------|----------|---|---------------|--|

| -             | -            | •                     | -                                                                                     | -           | RTRTAG   | - | <b>RB0TAG</b> |  |

| Bit<br>Number | Bit Mnemonic | Descripti             | Description                                                                           |             |          |   |               |  |

| 7-3           | -            | Reserved<br>The value | Reserved<br>The values read from these bits are indeterminate. Do not set these bits. |             |          |   |               |  |

| 2             | RTRTAG       | Remote T              | ransmission                                                                           | Request Tag | g Value. |   |               |  |

| 1             | -            |                       | Reserved<br>The values read from this bit are indeterminate. Do not set these bit.    |             |          |   |               |  |

| 0             | RB0TAG       | Reserved              | Bit 0 Tag Va                                                                          | lue.        |          |   |               |  |

No default value after reset.

#### Table 80. CANIDT1 Register for V2.0 part B

CANIDT1 for V2.0 part B (S:BCh) CAN Identifier Tag Registers 1

| 7      | 6            | 5           | 4      | 3      | 2      | 1      | 0      |

|--------|--------------|-------------|--------|--------|--------|--------|--------|

| IDT 28 | IDT 27       | IDT 26      | IDT 25 | IDT 24 | IDT 23 | IDT 22 | IDT 21 |

| Bit    |              |             |        |        |        |        |        |

| Number | Bit Mnemonic | Description | on     |        |        |        |        |

No default value after reset.

Table 81. CANIDT2 Register for V2.0 part B

CANIDT2 for V2.0 part B (S:BDh) CAN Identifier Tag Registers 2

| 7             | 6            | 5                       | 4                         | 3      | 2      | 1      | 0      |

|---------------|--------------|-------------------------|---------------------------|--------|--------|--------|--------|

| IDT 20        | IDT 19       | IDT 18                  | IDT 17                    | IDT 16 | IDT 15 | IDT 14 | IDT 13 |

| Bit<br>Number | Bit Mnemonic | Descripti               | on                        |        |        |        |        |

| 7-0           | IDT20:13     | IDentifier<br>See Figur | <b>Tag Value</b><br>e 50. |        |        |        |        |

No default value after reset.

### Table 85. CANIDM2 Register for V2.0 part A

CANIDM2 for V2.0 part A (S:C5h) CAN Identifier Mask Registers 2

| 7             | 6            | 5                        | 4                                                                                                | 3             | 2              | 1              | 0         |

|---------------|--------------|--------------------------|--------------------------------------------------------------------------------------------------|---------------|----------------|----------------|-----------|

| IDMSK 2       | IDMSK 1      | IDMSK 0                  | -                                                                                                | -             | -              | -              | -         |

| Bit<br>Number | Bit Mnemonie | c Descripti              | on                                                                                               |               |                |                |           |

| 7-5           | IDTMSK2:0    | 0 - compa<br>1 - bit con | Dentifier Mask Value<br>- comparison true forced.<br>- bit comparison enabled.<br>See Figure 50. |               |                |                |           |

| 4-0           | -            | Reserved<br>The value    |                                                                                                  | iese bits are | indeterminate. | Do not set the | ese bits. |

No default value after reset.

### Table 86. CANIDM3 Register for V2.0 part A

CANIDM3 for V2.0 part A (S:C6h) CAN Identifier Mask Registers 3

| 7             | 6            | 5                     | 4  | 3                | 2             | 1 | 0 |

|---------------|--------------|-----------------------|----|------------------|---------------|---|---|

| -             | -            | -                     | -  | -                | -             | - | - |

| Bit<br>Number | Bit Mnemonie | c Descripti           | on |                  |               |   |   |

| 7-0           | -            | Reserved<br>The value |    | iese bits are ir | ndeterminate. |   |   |

No default value after reset.

Table 104. CCAPMn Registers

CCAPM0 (S:DAh) CCAPM1 (S:DBh) CCAPM2 (S:DCh) CCAPM3 (S:DDh) CCAPM4 (S:DEh) PCA Compare/Capture Module n Mode registers (n=0..4)

| 7             | 6               | 5                                             | 4                                                                                                                                                                                                             | 3                                                     | 2              | 1              | 0            |  |

|---------------|-----------------|-----------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|----------------|----------------|--------------|--|

| -             | ECOMn           | CAPPn                                         | CAPNn                                                                                                                                                                                                         | MATn                                                  | TOGn           | PWMn           | ECCFn        |  |

| Bit<br>Number | Bit<br>Mnemonic | Description                                   |                                                                                                                                                                                                               |                                                       |                |                |              |  |

| 7             | -               | <b>Reserved</b><br>The Value re               | ad from this b                                                                                                                                                                                                | it is indetermi                                       | nate. Do not s | et this bit.   |              |  |

| 6             | ECOMn           | Clear to disa<br>Set to enable<br>The Compare |                                                                                                                                                                                                               | are function.                                         |                |                |              |  |

| 5             | CAPPn           | Clear to disa                                 | <b>Capture Mode (Positive) Module x bit</b><br>Clear to disable the Capture function triggered by a positive edge on CEXx pin.<br>Set to enable the Capture function triggered by a positive edge on CEXx pin |                                                       |                |                |              |  |

| 4             | CAPNn           | Clear to disa                                 | ble the Captu                                                                                                                                                                                                 | ) Module x bit<br>re function trig<br>function trigge | gered by a ne  |                |              |  |

| 3             | MATn            |                                               | natch of the F                                                                                                                                                                                                | PCA Counter w<br>r, flagging an i                     |                | are/Capture re | egister sets |  |

| 2             | TOGn            | The toggle m<br>Set when a m                  | <b>Toggle Module x bit</b><br>The toggle mode is configured by setting ECOMx, MATx and TOGx bits.<br>Set when a match of the PCA Counter with the Compare/Capture register<br>toggles the CEXx pin.           |                                                       |                |                |              |  |

| 1             | PWMn            | Set to config                                 | Pulse Width Modulation Module x Mode bit<br>Set to configure the module x as an 8-bit Pulse Width Modulator with output<br>waveform on CEXx pin.                                                              |                                                       |                |                |              |  |

| 0             | ECCFn           | Clear to disa                                 |                                                                                                                                                                                                               | it<br>n CCON regis<br>CCON registe                    |                |                |              |  |

Reset Value = X000 0000b

- Notes: 1. Operating  $I_{CC}$  is measured with all output pins disconnected; XTAL1 driven with  $T_{CLCH}$ ,  $T_{CHCL} = 5$  ns (see Figure 67.),  $V_{IL} = V_{SS} + 0.5V$ ,  $V_{IH} = V_{CC} 0.5V$ ; XTAL2 N.C.;  $\overline{EA} = RST = Port \ 0 = V_{CC}$ .  $I_{CC}$  would be slightly higher if a crystal oscillator used (see Figure 64.).

- 2. Idle I<sub>CC</sub> is measured with all output pins disconnected; XTAL1 driven with T<sub>CLCH</sub>, T<sub>CHCL</sub> = 5 ns, V<sub>IL</sub> = V<sub>SS</sub> + 0.5V, V<sub>IH</sub> = V<sub>CC</sub> 0.5V; XTAL2 N.C; Port 0 = V<sub>CC</sub>;  $\overline{EA}$  = RST = V<sub>SS</sub> (see Figure 65.).

- 3. Power-down  $I_{CC}$  is measured with all output pins disconnected;  $\overline{EA} = V_{CC}$ , PORT 0 =  $V_{CC}$ ; XTAL2 NC.; RST =  $V_{SS}$  (see Figure 66.). In addition, the WDT must be inactive and the POF flag must be set.

- 4. Capacitance loading on Ports 0 and 2 may cause spurious noise pulses to be superimposed on the V<sub>OL</sub>s of ALE and Ports 1 and 3. The noise is due to external bus capacitance discharging into the Port 0 and Port 2 pins when these pins make 1 to 0 transitions during bus operation. In the worst cases (capacitive loading 100pF), the noise pulse on the ALE line may exceed 0.45V with maxi V<sub>OL</sub> peak 0.6V. A Schmitt Trigger use is not necessary.

- 5. Typicals are based on a limited number of samples and are not guaranteed. The values listed are at room temperature.

- Under steady state (non-transient) conditions, I<sub>OL</sub> must be externally limited as follows:

Maximum  $I_{OL}$  per port pin: 10 mA Maximum  $I_{OL}$  per 8-bit port:

Port 0: 26 mA

Ports 1, 2 and 3: 15 mA

Maximum total I<sub>OL</sub> for all output pins: 71 mA

If  $I_{OL}$  exceeds the test condition,  $V_{OL}$  may exceed the related specification. Pins are not guaranteed to sink current greater than the listed test conditions.

- 7. ICC\_FLASH\_WRITE operating current while a Flash block write is on going.

- 8. Flash Retention is guaranteed with the same formula for  $V_{CC}$  Min down to 0.

Figure 64. I<sub>CC</sub> Test Condition, Active Mode

All other pins are disconnected.

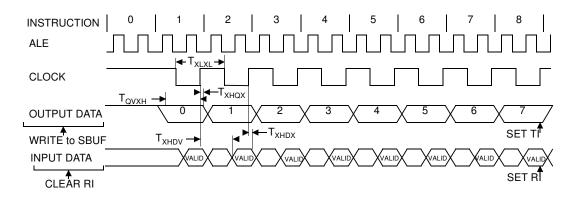

| Symbol            | Min | Мах | Units |

|-------------------|-----|-----|-------|

| T <sub>XLXL</sub> | 300 |     | ns    |

| T <sub>QVHX</sub> | 200 |     | ns    |

| T <sub>XHQX</sub> | 30  |     | ns    |

| T <sub>XHDX</sub> | 0   |     | ns    |

| T <sub>XHDV</sub> |     | 117 | ns    |

### Table 130. AC Parameters for a Fix Clock (F = 40 MHz)

## Table 131. AC Parameters for a Variable Clock

| Symbol            | Туре | Standard<br>Clock | X2 Clock | X parameter<br>for -M range | Units |

|-------------------|------|-------------------|----------|-----------------------------|-------|

| T <sub>XLXL</sub> | Min  | 12 T              | 6 T      |                             | ns    |

| T <sub>QVHX</sub> | Min  | 10 T - x          | 5 T - x  | 50                          | ns    |

| T <sub>XHQX</sub> | Min  | 2 T - x           | T - x    | 20                          | ns    |

| T <sub>XHDX</sub> | Min  | х                 | х        | 0                           | ns    |

| T <sub>XHDV</sub> | Max  | 10 T - x          | 5 T- x   | 133                         | ns    |

# Shift Register Timing Waveforms

## External Clock Drive Characteristics (XTAL1)

## Table 132. AC Parameters

| Symbol                               | Parameter               | Min | Мах | Units |

|--------------------------------------|-------------------------|-----|-----|-------|

| T <sub>CLCL</sub>                    | Oscillator Period       | 25  |     | ns    |

| T <sub>CHCX</sub>                    | High Time               | 5   |     | ns    |

| T <sub>CLCX</sub>                    | Low Time                | 5   |     | ns    |

| T <sub>CLCH</sub>                    | Rise Time               |     | 5   | ns    |

| T <sub>CHCL</sub>                    | Fall Time               |     | 5   | ns    |

| T <sub>CHCX</sub> /T <sub>CLCX</sub> | Cyclic ratio in X2 mode | 40  | 60  | %     |

This diagram indicates when signals are clocked internally. The time it takes the signals to propagate to the pins, however, ranges from 25 to 125 ns. This propagation delay is dependent on variables such as temperature and pin loading. Propagation also varies from output to output and component. Typically though ( $T_A=25$ °C fully loaded) RD and WR propagation delays are approximately 50ns. The other signals are typically 85 ns. Propagation delays are incorporated in the AC specifications.