#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Obsolete                                                                     |

|----------------------------|------------------------------------------------------------------------------|

| Core Processor             | 80C51                                                                        |

| Core Size                  | 8-Bit                                                                        |

| Speed                      | 40MHz                                                                        |

| Connectivity               | CANbus, UART/USART                                                           |

| Peripherals                | POR, PWM, WDT                                                                |

| Number of I/O              | 32                                                                           |

| Program Memory Size        | 32KB (32K x 8)                                                               |

| Program Memory Type        | FLASH                                                                        |

| EEPROM Size                | 2K x 8                                                                       |

| RAM Size                   | 1.25K x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                                    |

| Data Converters            | A/D 8x10b                                                                    |

| Oscillator Type            | External                                                                     |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                                |

| Package / Case             | 44-LQFP                                                                      |

| Supplier Device Package    | 44-VQFP (10x10)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/t89c51cc01ua-rltim |

|                            |                                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

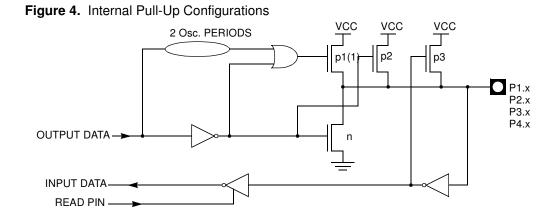

Note: Port 2 p1 assists the logic-one output for memory bus cycles.

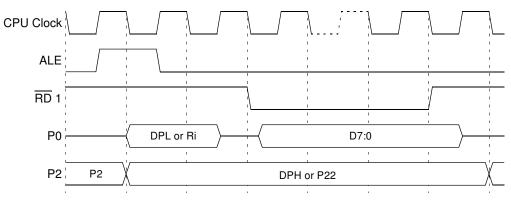

Figure 14. External Data Read Waveforms

- Notes: 1. RD signal may be stretched using M0 bit in AUXR register.

- 2. When executing MOVX @Ri instruction, P2 outputs SFR content.

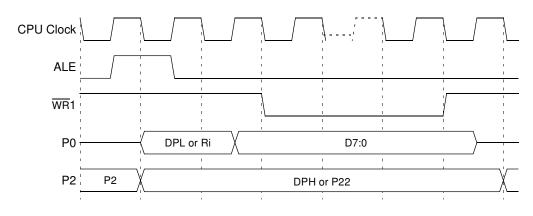

#### Figure 15. External Data Write Waveforms

Notes: 1. WR signal may be stretched using M0 bit in AUXR register.

2. When executing MOVX @Ri instruction, P2 outputs SFR content.

```

Examples

;* NAME: api_rd_eeprom_byte

;* DPTR contain address to read.

;* Acc contain the reading value

;* NOTE: before execute this function, be sure the EEPROM is not BUSY

api_rd_eeprom_byte:

; Save and clear EA

MOV EECON, #02h; map EEPROM in XRAM space

MOVX A, @DPTR

MOV EECON, #00h; unmap EEPROM

; Restore EA

ret

;* NAME: api_ld_eeprom_cl

;* DPTR contain address to load

;* Acc contain value to load

;* NOTE: in this example we load only 1 byte, but it is possible upto

;* 128 Bytes.

;* before execute this function, be sure the EEPROM is not BUSY

*****

api_ld_eeprom_cl:

; Save and clear EA

MOV EECON, #02h ; map EEPROM in XRAM space

MOVX @DPTR, A

MOVEECON, #00h; unmap EEPROM

; Restore EA

ret

;* NAME: api_wr_eeprom

;* NOTE: before execute this function, be sure the EEPROM is not BUSY

api_wr_eeprom:

; Save and clear EA

MOV EECON, #050h

MOV EECON, #0A0h

; Restore EA

ret

```

### Registers

#### Table 21. EECON Register

EECON (S:0D2h) EEPROM Control Register

| 7          | 6               | 5                              | 4                                                                                                                                                            | 3                                                           | 2           | 1   | 0      |  |  |  |

|------------|-----------------|--------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|-------------|-----|--------|--|--|--|

| EEPL3      | EEPL2           | EEPL1                          | EEPL0                                                                                                                                                        | -                                                           | -           | EEE | EEBUSY |  |  |  |

| Bit Number | Bit<br>Mnemonic | Descriptio                     | Description                                                                                                                                                  |                                                             |             |     |        |  |  |  |

| 7-4        | EEPL3-0         | •                              | Programming Launch command bits<br>Write 5Xh followed by AXh to EEPL to launch the programming.                                                              |                                                             |             |     |        |  |  |  |

| 3          | -               | Reserved<br>The value r        | Reserved<br>The value read from this bit is indeterminate. Do not set this bit.                                                                              |                                                             |             |     |        |  |  |  |

| 2          | -               | <b>Reserved</b><br>The value r | Reserved<br>The value read from this bit is indeterminate. Do not set this bit.                                                                              |                                                             |             |     |        |  |  |  |

| 1          | EEE             | Set to map<br>latches)         | Enable EEPROM Space bit<br>Set to map the EEPROM space during MOVX instructions (Write in the column<br>latches)<br>Clear to map the XRAM space during MOVX. |                                                             |             |     |        |  |  |  |

| 0          | EEBUSY          | Set by hard<br>Cleared by      | hardware wh                                                                                                                                                  | <b>g</b><br>rogramming is<br>en programmi<br>d by software. | ng is done. |     |        |  |  |  |

Reset Value = XXXX XX00b Not bit addressable

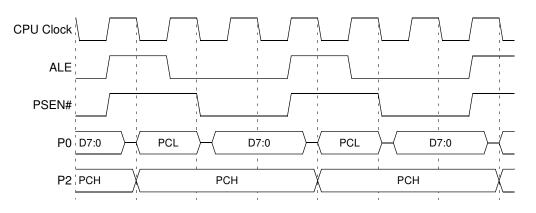

#### Figure 19. External Code Fetch Waveforms

#### Flash Memory Architecture

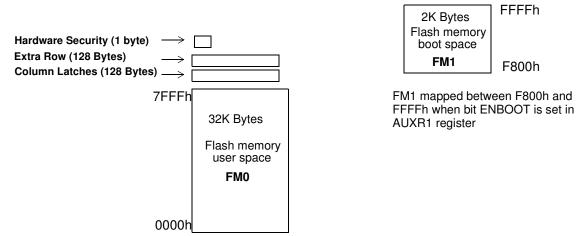

T89C51CC01 features two on-chip Flash memories:

- Flash memory FM0:

- containing 32K Bytes of program memory (user space) organized into 128 byte pages,

- Flash memory FM1: 2K Bytes for boot loader and Application Programming Interfaces (API).

The FM0 can be program by both parallel programming and Serial In-System-Programming (ISP) whereas FM1 supports only parallel programming by programmers. The ISP mode is detailed in the "In-System-Programming" section.

All Read/Write access operations on Flash Memory by user application are managed by a set of API described in the "In-System-Programming" section.

#### Figure 20. Flash Memory Architecture

Note: The last page address used when loading the column latch is the one used to select the page programming address.

#### **Programming the Flash Spaces**

User

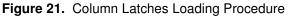

The following procedure is used to program the User space and is summarized in Figure 22:

- Load up to one page of data in the column latches from address 0000h to 7FFFh.

- Save then disable the interrupts.

- Launch the programming by writing the data sequence 50h followed by A0h in FCON register (only from FM1).

- The end of the programming indicated by the FBUSY flag cleared.

- Restore the interrupts.

Extra Row

The following procedure is used to program the Extra Row space and is summarized in Figure 22:

- Load data in the column latches from address FF80h to FFFFh.

- Save then disable the interrupts.

- Launch the programming by writing the data sequence 52h followed by A2h in FCON register. This step of the procedure must be executed from FM1. The end of the programming indicated by the FBUSY flag cleared. The end of the programming indicated by the FBUSY flag cleared.

- Restore the interrupts.

For slaves A and B, bit 2 is a don't care bit; for slave C, bit 2 is set. To communicate with all of the slaves, the master must send an address FFh. To communicate with slaves A and B, but not slave C, the master can send and address FBh.

### Registers

Table 35. SCON Register

SCON (S:98h) Serial Control Register

| 7             | 6               | 5                             | 4                                                                                                                                                                                               | 3               | 2              | 1             | 0       |  |  |  |  |

|---------------|-----------------|-------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|----------------|---------------|---------|--|--|--|--|

| FE/SM0        | SM1             | SM2                           | REN                                                                                                                                                                                             | TB8             | RB8            | TI            | RI      |  |  |  |  |

| Bit<br>Number | Bit<br>Mnemonic | Description                   | Description                                                                                                                                                                                     |                 |                |               |         |  |  |  |  |

| 7             | FE              | Clear to rese                 | Framing Error bit (SMOD0=1)<br>Clear to reset the error state, not cleared by a valid stop bit.<br>Set by hardware when an invalid stop bit is detected.                                        |                 |                |               |         |  |  |  |  |

|               | SM0             |                               | <b>Iode bit 0 (SI</b><br>I for serial por                                                                                                                                                       | ,               | ion.           |               |         |  |  |  |  |

| 6             | SM1             |                               |                                                                                                                                                                                                 |                 |                |               |         |  |  |  |  |

| 5             | SM2             | Clear to disa                 | Serial port Mode 2 bit/Multiprocessor Communication Enable bit<br>Clear to disable multiprocessor communication feature.<br>Set to enable multiprocessor communication feature in mode 2 and 3. |                 |                |               |         |  |  |  |  |

| 4             | REN             |                               | <b>nable bit</b><br>ble serial rece<br>e serial recept                                                                                                                                          |                 |                |               |         |  |  |  |  |

| 3             | TB8             | Clear to trans                | <b>Bit 8/Ninth b</b><br>smit a logic 0<br>nit a logic 1 in                                                                                                                                      | in the 9th bit. | in modes 2 a   | ind 3         |         |  |  |  |  |

| 2             | RB8             | Cleared by h                  | t <b>8/Ninth bit r</b><br>ardware if 9th<br>vare if 9th bit r                                                                                                                                   | bit received i  |                |               |         |  |  |  |  |

| 1             | TI              | Clear to ackr<br>Set by hardw | Transmit Interrupt flagClear to acknowledge interrupt.Set by hardware at the end of the 8th bit time in mode 0 or at the beginning of the<br>stop bit in the othermodes.                        |                 |                |               |         |  |  |  |  |

| 0             | RI              | Set by hardw                  | nowledge inter                                                                                                                                                                                  | d of the 8th bi | t time in mode | 0, see Figure | 29. and |  |  |  |  |

Reset Value = 0000 0000b Bit addressable

### Registers

#### Table 46. T2CON Register

T2CON (S:C8h) Timer 2 Control Register

| 7             | 6               | 5                                                                                                                                                                                                                                                           | 4                                                                                                                                                                                   | 3                                                                  | 2               | 1                        | 0        |  |  |  |  |  |

|---------------|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|-----------------|--------------------------|----------|--|--|--|--|--|

| TF2           | EXF2            | RCLK                                                                                                                                                                                                                                                        | TCLK                                                                                                                                                                                | EXEN2                                                              | TR2             | C/T2#                    | CP/RL2#  |  |  |  |  |  |

| Bit<br>Number | Bit<br>Mnemonic | Description                                                                                                                                                                                                                                                 | Description                                                                                                                                                                         |                                                                    |                 |                          |          |  |  |  |  |  |

| 7             | TF2             | TF2 is not se<br>Must be clea                                                                                                                                                                                                                               | <b>Fimer 2 Overflow Flag</b><br>FF2 is not set if RCLK=1 or TCLK = 1.<br>Must be cleared by software.<br>Set by hardware on timer 2 overflow.                                       |                                                                    |                 |                          |          |  |  |  |  |  |

| 6             | EXF2            | <b>Timer 2 External Flag</b><br>Set when a capture or a reload is caused by a negative transition on T2EX pin if EXEN2=1.<br>Set to cause the CPU to vector to timer 2 interrupt routine when timer 2 interrupt is enabled.<br>Must be cleared by software. |                                                                                                                                                                                     |                                                                    |                 |                          |          |  |  |  |  |  |

| 5             | RCLK            | Clear to use                                                                                                                                                                                                                                                | Receive Clock bit<br>Clear to use timer 1 overflow as receive clock for serial port in mode 1 or 3.<br>Set to use timer 2 overflow as receive clock for serial port in mode 1 or 3. |                                                                    |                 |                          |          |  |  |  |  |  |

| 4             | TCLK            |                                                                                                                                                                                                                                                             | timer 1 overfl                                                                                                                                                                      | ow as transmi<br>v as transmit c                                   |                 |                          |          |  |  |  |  |  |

| 3             | EXEN2           | Clear to igno<br>Set to cause                                                                                                                                                                                                                               | a capture or                                                                                                                                                                        | <b>bit</b><br>T2EX pin for ti<br>reload when a<br>used to clock ti | negative tran   |                          | X pin is |  |  |  |  |  |

| 2             | TR2             | Timer 2 Run<br>Clear to turn<br>Set to turn of                                                                                                                                                                                                              | off timer 2.                                                                                                                                                                        |                                                                    |                 |                          |          |  |  |  |  |  |

| 1             | C/T2#           | Clear for time                                                                                                                                                                                                                                              |                                                                                                                                                                                     | <b>bit</b><br>nput from inte<br>input from T2                      |                 | tem: F <sub>osc</sub> ). |          |  |  |  |  |  |

| 0             | CP/RL2#         | If RCLK=1 or<br>timer 2 overf<br>Clear to auto<br>EXEN2=1.                                                                                                                                                                                                  | low.<br>p-reload on tim                                                                                                                                                             | <b>bit</b><br>//RL2# is ignor<br>ner 2 overflows<br>transitions or | s or negative t | transitions on           |          |  |  |  |  |  |

Reset Value = 0000 0000b Bit addressable

|                               | <ul> <li>ACK Errors         As already mentioned frames received are acknowledged by all receivers through         positive acknowledgement. If no acknowledgement is received by the transmitter of         the message an ACK error is indicated.     </li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|-------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Error at Bit Level            | <ul> <li>Monitoring         The ability of the transmitter to detect errors is based on the monitoring of bus         signals. Each node which transmits also observes the bus level and thus detects         differences between the bit sent and the bit received. This permits reliable detection         of global errors and errors local to the transmitter.     </li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                               | <ul> <li>Bit Stuffing         The coding of the individual bits is tested at bit level. The bit representation used by         CAN is "Non Return to Zero (NRZ)" coding, which guarantees maximum efficiency         in bit coding. The synchronization edges are generated by means of bit stuffing.     </li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Error Signalling              | If one or more errors are discovered by at least one node using the above mechanisms, the current transmission is aborted by sending an "error flag". This prevents other nodes accepting the message and thus ensures the consistency of data throughout the network. After transmission of an erroneous message that has been aborted, the sender automatically re-attempts transmission.                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

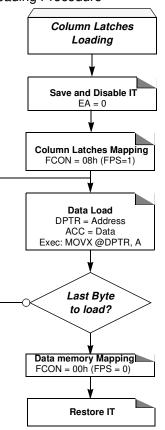

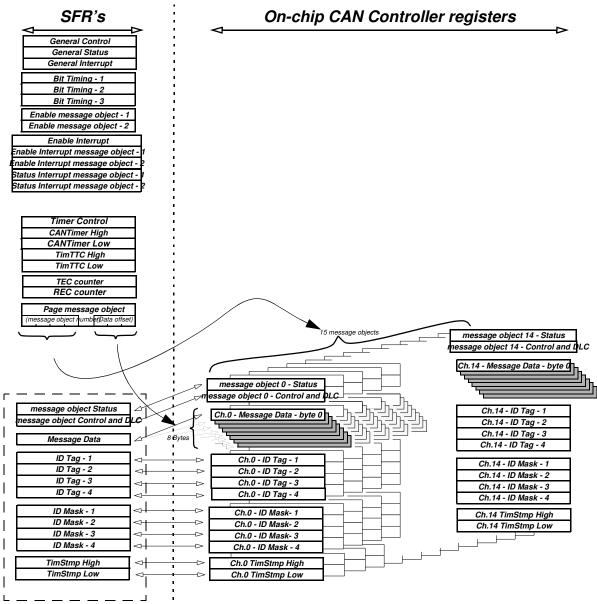

| CAN Controller                | The CAN Controller accesses are made through SFR.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| CAN Controller<br>Description | <ul><li>Several operations are possible by SFR:</li><li>arithmetic and logic operations, transfers and program control (SFR is accessible by</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                               | Several operations are possible by SFR:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                               | <ul> <li>Several operations are possible by SFR:</li> <li>arithmetic and logic operations, transfers and program control (SFR is accessible by direct addressing).</li> <li>15 independent message objects are implemented, a pagination system manages</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                               | <ul> <li>Several operations are possible by SFR:</li> <li>arithmetic and logic operations, transfers and program control (SFR is accessible by direct addressing).</li> <li>15 independent message objects are implemented, a pagination system manages their accesses.</li> <li>Any message object can be programmed in a reception buffer block (even non-consecutive buffers). For the reception of defined messages one or several receiver message objects can be masked without participating in the buffer feature. An IT is generated when the buffer is full. The frames following the buffer-full interrupt will not be taken into account until at least one of the buffer message objects is re-enabled in reception. Higher priority of a message object for reception or transmission is given to the lower</li> </ul> |

message object Window SFRs

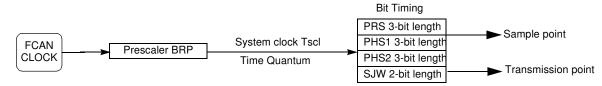

### **Bit Timing and Baud Rate**

FSM's (Finite State Machine) of the CAN channel need to be synchronous to the time quantum. So, the input clock for bit timing is the clock used into CAN channel FSM's.

Field and segment abbreviations:

- BRP: Baud Rate Prescaler.

- TQ: Time Quantum (output of Baud Rate Prescaler).

- SYNS: SYNchronization Segment is 1 TQ long.

- PRS: PRopagation time Segment is programmable to be 1, 2, ..., 8 TQ long.

- PHS1: PHase Segment 1 is programmable to be 1, 2, ..., 8 TQ long.

- PHS2: PHase Segment 2 is programmable to be superior or equal to the INFORMATION PROCESSING TIME and inferior or equal to TPHS1.

- INFORMATION PROCESSING TIME is 2 TQ.

- SJW: (Re) Synchronization Jump Width is programmable to be minimum of PHS1 and 4.

The total number of TQ in a bit time has to be programmed at least from 8 to 25.

#### Figure 47. Sample And Transmission Point

The baud rate selection is made by Tbit calculation:

Tbit = Tsyns + Tprs + Tphs1 + Tphs2

- 1. Tsyns = Tscl = (BRP[5..0] + 1)/Fcan = 1TQ.

- 2. Tprs = (1 to 8) \* Tscl = (PRS[2..0]+ 1) \* Tscl

- 3. Tphs1 = (1 to 8) \* Tscl = (PHS1[2..0]+ 1) \* Tscl

- 4. Tphs2 = (1 to 8) \* Tscl = (PHS2[2..0]+ 1) \* Tscl Tphs2 = Max of (Tphs1 and 2TQ)

- 5. Tsjw = (1 to 4) \* Tscl = (SJW[1..0]+ 1) \* Tscl

The total number of Tscl (Time Quanta) in a bit time must be comprised between **8 to 25**.

#### Table 59. CANGSTA Register

CANGSTA (S:AAh Read Only) CAN General Status Register

| 7             | 6            | 5                                       | 4                                                                                                                                                                                                                                                                                                            | 3                               | 2                      | 1           | 0             |  |  |  |

|---------------|--------------|-----------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|------------------------|-------------|---------------|--|--|--|

| -             | OVFG         | -                                       | TBSY                                                                                                                                                                                                                                                                                                         | RBSY                            | ENFG                   | BOFF        | ERRP          |  |  |  |

| Bit<br>Number | Bit Mnemonic | Description                             | Description                                                                                                                                                                                                                                                                                                  |                                 |                        |             |               |  |  |  |

| 7             | -            | <b>Reserved</b><br>The value            | Reserved<br>The values read from this bit is indeterminate. Do not set this bit.                                                                                                                                                                                                                             |                                 |                        |             |               |  |  |  |

| 6             | OVFG         | This statu<br>is sent.                  | <b>Overload Frame Flag</b><br>This status bit is set by the hardware as long as the produced overload frame<br>is sent.<br>This flag does not generate an interrupt                                                                                                                                          |                                 |                        |             |               |  |  |  |

| 5             | -            | Reserved<br>The value                   | teserved<br>he values read from this bit is indeterminate. Do not set this bit.                                                                                                                                                                                                                              |                                 |                        |             |               |  |  |  |

| 4             | TBSY         | This status<br>generates<br>bit is also | <b>Transmitter Busy</b><br>This status bit is set by the hardware as long as the CAN transmitter<br>generates a frame (remote, data, overload or error frame) or an ack field. This<br>bit is also active during an InterFrame Spacing if a frame must be sent.<br>This flag does not generate an interrupt. |                                 |                        |             |               |  |  |  |

| 3             | RBSY         | monitors a                              | s bit is set by<br>a frame.                                                                                                                                                                                                                                                                                  | the hardware<br>rate an interru | as long as the<br>ıpt. | CAN receive | r acquires or |  |  |  |

| 2             | ENFG         | Because a<br>bit gives the              | <b>Enable On-chip CAN Controller Flag</b><br>Because an enable/disable command is not effective immediately, this status<br>bit gives the true state of a chosen mode.<br>This flag does not generate an interrupt.                                                                                          |                                 |                        |             |               |  |  |  |

| 1             | BOFF         |                                         | Bus Off Mode<br>see Figure 49                                                                                                                                                                                                                                                                                |                                 |                        |             |               |  |  |  |

| 0             | ERRP         | Error Pas<br>see Figur                  | sive Mode<br>e 49                                                                                                                                                                                                                                                                                            |                                 |                        |             |               |  |  |  |

Reset Value = x0x0 0000b

#### Table 69. CANIE2 Register

CANIE2 (S:C3h) CAN Enable Interrupt Message Object Registers 2

| 7             | 6            | 5                         | 4            | 3                              | 2                  | 1               | 0      |  |  |  |

|---------------|--------------|---------------------------|--------------|--------------------------------|--------------------|-----------------|--------|--|--|--|

| IECH 7        | IECH 6       | IECH 5                    | IECH 4       | IECH 3                         | IECH 2             | IECH 1          | IECH 0 |  |  |  |

| Bit<br>Number | Bit Mnemonic | Description               | Description  |                                |                    |                 |        |  |  |  |

| 7-0           | IECH7:0      | 0 - disable<br>1 - enable | e IT.<br>IT. | essage Objec<br>0 -> Enable IT | t<br>∵s of message | e objects 3 and | d 2.   |  |  |  |

Reset Value = 0000 0000b

#### Table 70. CANBT1 Register

CANBT1 (S:B4h) CAN Bit Timing Registers 1

| 7             | 6            | 5                     | 4                                                                                                                                                                                                      | 3     | 2     | 1     | 0 |  |  |  |

|---------------|--------------|-----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-------|-------|---|--|--|--|

| -             | BRP 5        | BRP 4                 | BRP 3                                                                                                                                                                                                  | BRP 2 | BRP 1 | BRP 0 | - |  |  |  |

| Bit<br>Number | Bit Mnemonic | Descripti             | Description                                                                                                                                                                                            |       |       |       |   |  |  |  |

| 7             | -            | Reserved<br>The value | Reserved<br>The value read from this bit is indeterminate. Do not set this bit.                                                                                                                        |       |       |       |   |  |  |  |

| 6-1           | BRP5:0       | The period            | Baud rate prescaler         The period of the CAN controller system clock Tscl is programmable and determines the individual bit timing.         BRP[50] + 1         Tscl = $\frac{BRP[50] + 1}{Fcan}$ |       |       |       |   |  |  |  |

|               |              |                       |                                                                                                                                                                                                        |       |       |       |   |  |  |  |

| 0             | -            |                       | Reserved<br>The value read from this bit is indeterminate. Do not set this bit.                                                                                                                        |       |       |       |   |  |  |  |

Note: The CAN controller bit timing registers must be accessed only if the CAN controller is disabled with the ENA bit of the CANGCON register set to 0. See Figure 48.

No default value after reset.

#### Table 93. CANTCON Register

CANTCON (S:A1h) CAN Timer ClockControl

| 7               | 6               | 5               | 4               | 3                                 | 2               | 1               | 0        |  |  |

|-----------------|-----------------|-----------------|-----------------|-----------------------------------|-----------------|-----------------|----------|--|--|

| <b>TPRESC 7</b> | <b>TPRESC 6</b> | <b>TPRESC 5</b> | <b>TPRESC 4</b> | <b>TPRESC 3</b>                   | <b>TPRESC 2</b> | <b>TPRESC 1</b> | TPRESC 0 |  |  |

| Bit<br>Number   | Bit Mnemon      | ic Descripti    | Description     |                                   |                 |                 |          |  |  |

| 7-0             | TPRESC7:        | This roois      | to 255.         | <b>N Timer</b><br>aler for the ma | in timer upper  | counter         |          |  |  |

Reset Value = 00h

#### Table 94. CANTIMH Register

CANTIMH (S:ADh) CAN Timer High

| 7             | 6             |     | 5                  | 4                                | 3             | 2             | 1         | 0         |

|---------------|---------------|-----|--------------------|----------------------------------|---------------|---------------|-----------|-----------|

| CANGTIM<br>15 | CANGTIM<br>14 | CA  | NGTIM<br>13        | CANGTIM<br>12                    | CANGTIM<br>11 | CANGTIM<br>10 | CANGTIM 9 | CANGTIM 8 |

| Bit<br>Number | Bit Mnemo     | nic | Description        |                                  |               |               |           |           |

| 7-0           | CANGTIM1      | 5:8 | High by<br>See Fig | <b>yte of Messag</b><br>jure 51. | ge Timer      |               |           |           |

Reset Value = 0000 0000b

#### Table 95. CANTIML Register

CANTIML (S:ACh) CAN Timer Low

| 7         | 6            | 5                     | 4                                | 3         | 2         | 1         | 0         |  |  |

|-----------|--------------|-----------------------|----------------------------------|-----------|-----------|-----------|-----------|--|--|

| CANGTIM 7 | CANGTIM 6    | CANGTIM 5             | CANGTIM 4                        | CANGTIM 3 | CANGTIM 2 | CANGTIM 1 | CANGTIM 0 |  |  |

| Bit       |              |                       |                                  |           |           |           |           |  |  |

| Number    | Bit Mnemonio | Description           | Description                      |           |           |           |           |  |  |

| 7-0       | CANGTIM7:0   | Low byte<br>See Figur | of Message <sup>-</sup><br>e 51. | Timer     |           |           |           |  |  |

Reset Value = 0000 0000b

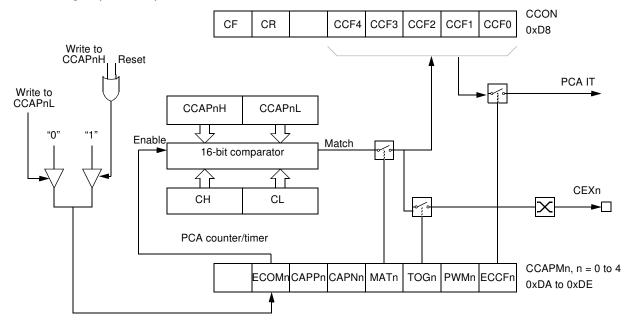

### High Speed Output Mode

In this mode the CEX output (on port 1) associated with the PCA module will toggle each time a match occurs between the PCA counter and the module's capture registers. To activate this mode the TOG, MAT, and ECOM bits in the module's CCAPMn SFR must be set.

Figure 57. PCA High Speed Output Mode

#### Pulse Width Modulator Mode

All the PCA modules can be used as PWM outputs. The output frequency depends on the source for the PCA timer. All the modules will have the same output frequency because they all share the PCA timer. The duty cycle of each module is independently variable using the module's capture register CCAPLn. When the value of the PCA CL SFR is less than the value in the module's CCAPLn SFR the output will be low, when it is equal to or greater than it, the output will be high. When CL overflows from FF to 00, CCAPLn is reloaded with the value in CCAPHn. the allows the PWM to be updated without glitches. The PWM and ECOM bits in the module's CCAPMn register must be set to enable the PWM mode.

Table 104. CCAPMn Registers

CCAPM0 (S:DAh) CCAPM1 (S:DBh) CCAPM2 (S:DCh) CCAPM3 (S:DDh) CCAPM4 (S:DEh) PCA Compare/Capture Module n Mode registers (n=0..4)

| 7             | 6               | 5                                             | 4                                                                                                                                                                                                                                                                          | 3                                                     | 2             | 1              | 0            |  |  |  |  |  |

|---------------|-----------------|-----------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|---------------|----------------|--------------|--|--|--|--|--|

| -             | ECOMn           | CAPPn                                         | CAPNn                                                                                                                                                                                                                                                                      | MATn                                                  | TOGn          | PWMn           | ECCFn        |  |  |  |  |  |

| Bit<br>Number | Bit<br>Mnemonic | Description                                   | Description                                                                                                                                                                                                                                                                |                                                       |               |                |              |  |  |  |  |  |

| 7             | -               | <b>Reserved</b><br>The Value re               | Reserved<br>The Value read from this bit is indeterminate. Do not set this bit.                                                                                                                                                                                            |                                                       |               |                |              |  |  |  |  |  |

| 6             | ECOMn           | Clear to disa<br>Set to enable<br>The Compare | Enable Compare Mode Module x bit<br>Clear to disable the Compare function.<br>Set to enable the Compare function.<br>The Compare function is used to implement the software Timer, the high-speed<br>output, the Pulse Width Modulator (PWM) and the Watchdog Timer (WDT). |                                                       |               |                |              |  |  |  |  |  |

| 5             | CAPPn           | Clear to disa                                 | Capture Mode (Positive) Module x bit<br>Clear to disable the Capture function triggered by a positive edge on CEXx pin.<br>Set to enable the Capture function triggered by a positive edge on CEXx pin                                                                     |                                                       |               |                |              |  |  |  |  |  |

| 4             | CAPNn           | Clear to disa                                 | ble the Captu                                                                                                                                                                                                                                                              | ) Module x bit<br>re function trig<br>function trigge | gered by a ne |                |              |  |  |  |  |  |

| 3             | MATn            |                                               | natch of the F                                                                                                                                                                                                                                                             | PCA Counter w<br>r, flagging an i                     |               | are/Capture re | egister sets |  |  |  |  |  |

| 2             | TOGn            |                                               | node is config<br>natch of the F                                                                                                                                                                                                                                           | ured by setting<br>PCA Counter w                      |               |                |              |  |  |  |  |  |

| 1             | PWMn            | Set to config                                 | Pulse Width Modulation Module x Mode bit<br>Set to configure the module x as an 8-bit Pulse Width Modulator with output<br>waveform on CEXx pin.                                                                                                                           |                                                       |               |                |              |  |  |  |  |  |

| 0             | ECCFn           | Clear to disa                                 |                                                                                                                                                                                                                                                                            | <b>it</b><br>n CCON regis<br>CCON registe             |               |                |              |  |  |  |  |  |

Reset Value = X000 0000b

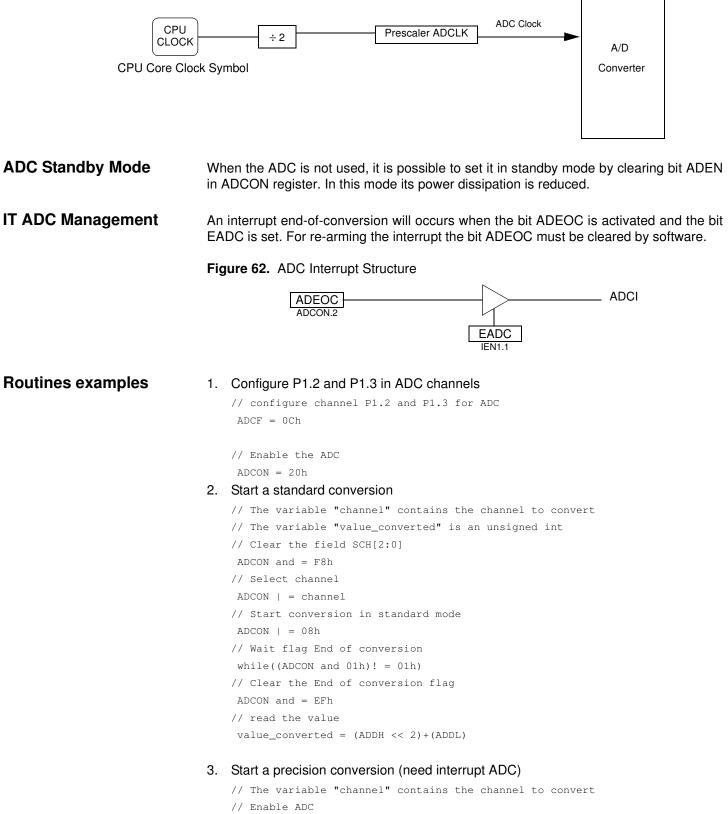

| Analog-to-Digital<br>Converter (ADC) | This section describes the on-chip 10 bit analog-to-digital converter of the T89C51CC01. Eight ADC channels are available for sampling of the external sources AN0 to AN7. An analog multiplexer allows the single ADC converter to select one from the 8 ADC channels as ADC input voltage (ADCIN). ADCIN is converted by the 10-bit cascaded potentiometric ADC.                                                                                                                                                                        |  |  |  |

|--------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

|                                      | Two modes of conversion are available:<br>- Standard conversion (8 bits).<br>- Precision conversion (10 bits).                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |

|                                      | For the precision conversion, set bit PSIDLE in ADCON register and start conversion.<br>The device is in a pseudo-idle mode, the CPU does not run but the peripherals are<br>always running. This mode allows digital noise to be as low as possible, to ensure high<br>precision conversion.                                                                                                                                                                                                                                             |  |  |  |

|                                      | For this mode it is necessary to work with end of conversion interrupt, which is the only way to wake the device up.                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |

|                                      | If another interrupt occurs during the precision conversion, it will be served only after this conversion is completed.                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

| Features                             | <ul> <li>8 channels with multiplexed inputs</li> <li>10-bit cascaded potentiometric ADC</li> <li>Conversion time 16 micro-seconds (typ.)</li> <li>Zero Error (offset) ± 2 LSB max</li> <li>Positive External Reference Voltage Range (VAREF) 2.4 to 3.0 Volt (typ.)</li> <li>ADCIN Range 0 to 3Volt</li> <li>Integral non-linearity typical 1 LSB, max. 2 LSB</li> <li>Differential non-linearity typical 0.5 LSB, max. 1 LSB</li> <li>Conversion Complete Flag or Conversion Complete Interrupt</li> <li>Selectable ADC Clock</li> </ul> |  |  |  |

| ADC Port 1 I/O Functions             | Port 1 pins are general I/O that are shared with the ADC channels. The channel select bit in ADCF register define which ADC channel/port1 pin will be used as ADCIN. The remaining ADC channels/port1 pins can be used as general-purpose I/O or as the alternate function that is available.                                                                                                                                                                                                                                             |  |  |  |

|                                      | A conversion launched on a channel which are not selected on ADCF register will not have any effect.                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |

| VAREF                                | VAREF should be connected to a low impedance point and must remain in the range specified in Table 122. If the ADC is not used, it is recommended to connect VAREF to VAGND.                                                                                                                                                                                                                                                                                                                                                              |  |  |  |

#### Figure 61. A/D Converter clock

EADC = 1

132 A/T89C51CC01

#### Table 116. IEN1 Register

IEN1 (S:E8h) Interrupt Enable Register

| 7             | 6               | 5                                                                                                                                 | 4 | 3 | 2    | 1    | 0    |  |  |

|---------------|-----------------|-----------------------------------------------------------------------------------------------------------------------------------|---|---|------|------|------|--|--|

| -             | -               | -                                                                                                                                 | - | - | ETIM | EADC | ECAN |  |  |

| Bit<br>Number | Bit<br>Mnemonic | Description                                                                                                                       |   |   |      |      |      |  |  |

| 7             | -               | <b>Reserved</b><br>The value read from this bit is indeterminate. Do not set this bit.                                            |   |   |      |      |      |  |  |

| 6             | -               | Reserved<br>The value read from this bit is indeterminate. Do not set this bit.                                                   |   |   |      |      |      |  |  |

| 5             | -               | Reserved<br>The value read from this bit is indeterminate. Do not set this bit.                                                   |   |   |      |      |      |  |  |

| 4             | -               | Reserved<br>The value read from this bit is indeterminate. Do not set this bit.                                                   |   |   |      |      |      |  |  |

| 3             | -               | Reserved<br>The value read from this bit is indeterminate. Do not set this bit.                                                   |   |   |      |      |      |  |  |

| 2             | ETIM            | Timer Overrun Interrupt Enable bit<br>Clear to disable the timer overrun interrupt.<br>Set to enable the timer overrun interrupt. |   |   |      |      |      |  |  |

| 1             | EADC            | ADC Interrupt Enable bit<br>Clear to disable the ADC interrupt.<br>Set to enable the ADC interrupt.                               |   |   |      |      |      |  |  |

| 0             | ECAN            | CAN Interrupt Enable bit<br>Clear to disable the CAN interrupt.<br>Set to enable the CAN interrupt.                               |   |   |      |      |      |  |  |

Reset Value = xxxx x000b bit addressable

# AIMEL

### Datasheet Change Log for T89C51CC01

Changes from 4129F -11/02 to 4129G - 04/03

Changes from 4129G - 04/03 to 4129H - 10/03

Changes from 4129H - 10/03 to 4129I - 12/03

Changes from 4129I - 12/03 to 4129J - 08/04

1. Changed the endurance of Flash to 100, 000 Write/Erase cycles.

- Added note on Flash retention formula for V<sub>IH1</sub>, in Section "DC Parameters for Standard Voltage", page 144.

- 1. Updated "Electrical Characteristics" on page 144.

- 2. Corrected Figure 46 on page 84.

- 1. Correction in Registers CPA and CPS0.

- 2. Added note regarding PSEN during power On see Section "Hardware Boot Process", page 48.

- 1. Figure clock-out mode modified see, Figure 37 on page 67.

- 2. Added explanation on the CAN protocol, see Section "CAN Controller", page 75.

- 3. Corrected error in Table 53 on page 72, (1.25ms to 1.25s) for Time-out Computation.

- 1. Minor corrections throughout the document.

- 2. Clarification to Mode Switching Waveforms diagram. See page 16.

- Changes from 4129K 01/05 to 4129L 08/05

Changes from 4129L 08/05 to 4129M 02/08

Changes from 4129J -

08/04 to 4129K 01/05

Changes from 4129M 02/08 to 4129N 03/08

- 1. Added green product ordering information.

- 1. Removed non-green packages from ordering information.

- 1. Removed CA-BGA package offering from ordering information.

- 2. Updated package drawings.