Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                |

|----------------------------|-----------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M4F                                                      |

| Core Size                  | 32-Bit Single-Core                                                    |

| Speed                      | 72MHz                                                                 |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART               |

| Peripherals                | DMA, I <sup>2</sup> S, POR, PWM, WDT                                  |

| Number of I/O              | 51                                                                    |

| Program Memory Size        | 256KB (256K x 8)                                                      |

| Program Memory Type        | FLASH                                                                 |

| EEPROM Size                | -                                                                     |

| RAM Size                   | 8K x 8                                                                |

| Voltage - Supply (Vcc/Vdd) | 1.65V ~ 1.95V                                                         |

| Data Converters            | A/D 4x12b; D/A 2x12b                                                  |

| Oscillator Type            | Internal                                                              |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                     |

| Mounting Type              | Surface Mount                                                         |

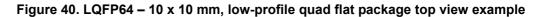

| Package / Case             | 64-LQFP                                                               |

| Supplier Device Package    | 64-LQFP (10x10)                                                       |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32f358rct6 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 3.7 **Power management**

### 3.7.1 Power supply schemes

- V<sub>SS</sub>, V<sub>DD</sub> = 1.8 V+/- 8%: external power supply for I/Os and core. It is provided externally through V<sub>DD</sub> pins.

- V<sub>SSA</sub>, V<sub>DDA</sub> = 1.65 to 3.6 V: external analog power supply for ADC, DACs, comparators operational amplifiers, reset blocks, RCs and PLL. The minimum voltage to be applied to V<sub>DDA</sub> differs from one analog peripheral to another. *Table 3* provides the summary of the V<sub>DDA</sub> ranges for analog peripherals. The V<sub>DDA</sub> voltage level must be always greater or equal to the V<sub>DD</sub> voltage level and must be provided first.

- V<sub>BAT</sub>= 1.65 to 3.6 V: power supply for RTC, external clock 32 kHz oscillator and backup registers (through power switch which is guaranteed in the full range of VDD) when VDD is not present.

| Analog peripheral | Minimum V <sub>DDA</sub> supply | Maximum V <sub>DDA</sub> supply |

|-------------------|---------------------------------|---------------------------------|

| ADC               | 1.8 V                           | 3.6 V                           |

| COMP              | 1.65 V                          | 3.6 V                           |

| DAC / OPAMP       | 2.4 V                           | 3.6V                            |

Table 3. External analog supply values for analog peripherals

## 3.7.2 Power supply supervision

The device power on reset is controlled through the external NPOR pin. The device remains in reset state when NPOR pin is held low.

To guarantee a proper power-on reset, the NPOR pin must be held low when VDDA is applied. Then, when VDD is stable, the reset state can be exited by:

- either putting the NPOR pin in high impedance. NPOR pin has an internal pull up.

- or forcing the pin to high level by connecting it to V<sub>DDA</sub>.

## 3.7.3 Low-power modes

The STM32F358xC devices support two low-power modes to achieve the best compromise between low-power consumption, short startup time and available wakeup sources:

Sleep mode

In Sleep mode, only the CPU is stopped. All peripherals continue to operate and can wake up the CPU when an interrupt/event occurs.

• Stop mode

Stop mode achieves the lowest power consumption while retaining the content of SRAM and registers. All clocks in the 1.8 V domain are stopped, the PLL, the HSI RC and the HSE crystal oscillators are disabled.

The device can be woken up from Stop mode by any of the EXTI line. The EXTI line source can be one of the 16 external lines, the RTC alarm, COMPx, I2Cx or U(S)ARTx.

*Note:* The RTC, the IWDG and the corresponding clock sources are not stopped by entering Stop mode.

• 17-bit Auto-reload counter for periodic interrupt with wakeup from STOP capability.

The RTC clock sources can be:

- A 32.768 kHz external crystal

- A resonator or oscillator

- The internal low-power RC oscillator (typical frequency of 40 kHz)

- The high-speed external clock divided by 32.

# 3.19 Inter-integrated circuit interface (I<sup>2</sup>C)

Up to two I<sup>2</sup>C bus interfaces can operate in multimaster and slave modes. They can support standard (up to 100 KHz), fast (up to 400 KHz) and fast mode + (up to 1 MHz) modes. Both support 7-bit and 10-bit addressing modes, multiple 7-bit slave addresses (2 addresses, 1 with configurable mask). They also include programmable analog and digital noise filters.

|                                     | Analog filter                                         | Digital filter                                                                                       |

|-------------------------------------|-------------------------------------------------------|------------------------------------------------------------------------------------------------------|

| Pulse width of<br>suppressed spikes | ≥ 50 ns                                               | Programmable length from 1 to 15<br>I2C peripheral clocks                                            |

| Benefits                            | Available in Stop mode                                | <ol> <li>Extra filtering capability vs.<br/>standard requirements.</li> <li>Stable length</li> </ol> |

| Drawbacks                           | Variations depending on temperature, voltage, process | Wakeup from Stop on address<br>match is not available when digital<br>filter is enabled.             |

In addition, they provide hardware support for SMBUS 2.0 and PMBUS 1.1: ARP capability, Host notify protocol, hardware CRC (PEC) generation/verification, timeouts verifications and ALERT protocol management. They also have a clock domain independent from the CPU clock, allowing the I2Cx (x=1,2) to wake up the MCU from Stop mode on address match. The I2C interfaces can be served by the DMA controller. Refer to *Table 7* for the features available in I2C1 and I2C2.

Table 7. STM32F358xC I<sup>2</sup>C implementation

| I2C features <sup>(1)</sup>                                 | I2C1 | I2C2 |

|-------------------------------------------------------------|------|------|

| 7-bit addressing mode                                       | Х    | Х    |

| 10-bit addressing mode                                      | Х    | Х    |

| Standard mode (up to 100 kbit/s)                            | Х    | Х    |

| Fast mode (up to 400 kbit/s)                                | Х    | Х    |

| Fast Mode Plus with 20mA output drive I/Os (up to 1 Mbit/s) | Х    | Х    |

| Independent clock                                           | Х    | Х    |

| SMBus                                                       | Х    | Х    |

| Wakeup from STOP                                            | Х    | Х    |

1. X = supported.

Table 13. STM32F358xC pin definitions

| Pir     | n numb | ber    |                                                |          | JIE 13.       |       | Pin functions                                           |                                      |

|---------|--------|--------|------------------------------------------------|----------|---------------|-------|---------------------------------------------------------|--------------------------------------|

| LQFP100 | LQFP64 | LQFP48 | Pin name<br>(function<br>after<br>reset)       | Pin type | I/O structure | Notes | Alternate functions                                     | Additional functions                 |

| 1       | -      | -      | PE2                                            | I/O      | FT            | (1)   | TRACECK, TIM3_CH1,<br>TSC_G7_IO1, EVENTOUT              | -                                    |

| 2       | -      | -      | PE3                                            | I/O      | FT            | (1)   | TRACED0, TIM3_CH2,<br>TSC_G7_IO2, EVENTOUT              | -                                    |

| 3       | -      | -      | PE4                                            | I/O      | FT            | (1)   | TRACED1, TIM3_CH3,<br>TSC_G7_IO3, EVENTOUT              | -                                    |

| 4       | -      | -      | PE5                                            | I/O      | FT            | (1)   | TRACED2, TIM3_CH4,<br>TSC_G7_IO4, EVENTOUT              | -                                    |

| 5       | -      | -      | PE6                                            | I/O      | FT            | (1)   | TRACED3, EVENTOUT                                       | WKUP3, RTC_TAMP3                     |

| 6       | 1      | 1      | V <sub>BAT</sub>                               | S        | -             | -     | Backup pov                                              | wer supply                           |

| 7       | 2      | 2      | PC13 <sup>(2)</sup>                            | I/O      | тс            | -     | TIM1_CH1N                                               | WKUP2, RTC_TAMP1,<br>RTC_TS, RTC_OUT |

| 8       | 3      | 3      | PC14 <sup>(2)</sup><br>OSC32_IN<br>(PC14)      | I/O      | тс            | -     | -                                                       | OSC32_IN                             |

| 9       | 4      | 4      | PC15 <sup>(2)</sup><br>OSC32_<br>OUT<br>(PC15) | I/O      | тс            | -     | -                                                       | OSC32_OUT                            |

| 10      | -      | -      | PF9                                            | I/O      | FT            | (1)   | TIM15_CH1, SPI2_SCK,<br>EVENTOUT                        | -                                    |

| 11      | -      | -      | PF10                                           | I/O      | FT            | (1)   | TIM15_CH2, SPI2_SCK,<br>EVENTOUT                        | -                                    |

| 12      | 5      | 5      | PF0-<br>OSC_IN<br>(PF0)                        | I/O      | FTf           | -     | TIM1_CH3N, I2C2_SDA,                                    | OSC_IN                               |

| 13      | 6      | 6      | PF1-<br>OSC_OUT<br>(PF1)                       | I/O      | FTf           | -     | I2C2_SCL                                                | OSC_OUT                              |

| 14      | 7      | 7      | NRST                                           | I/O      | RST           | -     | Device reset input / internal reset output (active low) |                                      |

| 15      | 8      | -      | PC0                                            | I/O      | TTa           | (1)   | EVENTOUT                                                | ADC12_IN6, COMP7_INM                 |

| 16      | 9      | -      | PC1                                            | I/O      | TTa           | (1)   | EVENTOUT                                                | ADC12_IN7, COMP7_INP                 |

| 17      | 10     | -      | PC2                                            | I/O      | TTa           | (1)   | COMP7_OUT, EVENTOUT                                     | ADC12_IN8                            |

| 18      | 11     | -      | PC3                                            | I/O      | TTa           | (1)   | TIM1_BKIN2, EVENTOUT                                    | ADC12_IN9                            |

| 19      | -      | -      | PF2                                            | I/O      | TTa           | (1)   | EVENTOUT                                                | ADC12_IN10                           |

| 20      | 12     | 8      | VSSA/<br>VREF-                                 | S        | -             | -     | Analog ground/Negative reference voltage                |                                      |

|         | Table 13. STM32F358xC pin definitions (continued) |        |                                          |          |               |       |                                                                                                                                      |                      |  |

|---------|---------------------------------------------------|--------|------------------------------------------|----------|---------------|-------|--------------------------------------------------------------------------------------------------------------------------------------|----------------------|--|

| Pir     | n numl                                            | ber    |                                          |          |               |       | Pin functions                                                                                                                        |                      |  |

| LQFP100 | LQFP64                                            | LQFP48 | Pin name<br>(function<br>after<br>reset) | Pin type | I/O structure | Notes | Alternate functions                                                                                                                  | Additional functions |  |

| 78      | 51                                                | -      | PC10                                     | I/O      | FT            | (1)   | SPI3_SCK, I2S3_CK,<br>USART3_TX, UART4_TX,<br>TIM8_CH1N, EVENTOUT                                                                    | _                    |  |

| 79      | 52                                                | -      | PC11                                     | I/O      | FT            | (1)   | SPI3_MISO, I2S3ext_SD,<br>USART3_RX, UART4_RX,<br>TIM8_CH2N, EVENTOUT                                                                | -                    |  |

| 80      | 53                                                | -      | PC12                                     | I/O      | FT            | (1)   | SPI3_MOSI, I2S3_SD,<br>USART3_CK, UART5_TX,<br>TIM8_CH3N, EVENTOUT                                                                   | -                    |  |

| 81      | -                                                 | -      | PD0                                      | I/O      | FT            | (1)   | CAN_RX, EVENTOUT                                                                                                                     | -                    |  |

| 82      | -                                                 | -      | PD1                                      | I/O      | FT            | (1)   | CAN_TX, TIM8_CH4,<br>TIM8_BKIN2, EVENTOUT                                                                                            | -                    |  |

| 83      | 54                                                | -      | PD2                                      | I/O      | FT            | (1)   | UART5_RX, TIM3_ETR,<br>TIM8_BKIN, EVENTOUT                                                                                           | -                    |  |

| 84      | -                                                 | -      | PD3                                      | I/O      | FT            | (1)   | USART2_CTS,<br>TIM2_CH1_ETR, EVENTOUT                                                                                                | -                    |  |

| 85      | -                                                 | -      | PD4                                      | I/O      | FT            | (1)   | USART2_RTS_DE,<br>TIM2_CH2, EVENTOUT                                                                                                 | -                    |  |

| 86      | -                                                 | -      | PD5                                      | I/O      | FT            | (1)   | USART2_TX, EVENTOUT                                                                                                                  | -                    |  |

| 87      | -                                                 | -      | PD6                                      | I/O      | FT            | (1)   | USART2_RX, TIM2_CH4,<br>EVENTOUT                                                                                                     | -                    |  |

| 88      | -                                                 | -      | PD7                                      | I/O      | FT            | (1)   | USART2_CK, TIM2_CH3,<br>EVENTOUT                                                                                                     | -                    |  |

| 89      | 55                                                | 39     | PB3                                      | I/O      | FT            | -     | SPI3_SCK, I2S3_CK,<br>SPI1_SCK, USART2_TX,<br>TIM2_CH2, TIM3_ETR,<br>TIM4_ETR, TIM8_CH1N,<br>TSC_G5_IO1, JTDO-<br>TRACESWO, EVENTOUT | -                    |  |

| 90      | 56                                                | 40     | PB4                                      | I/O      | FT            | -     | SPI3_MISO, I2S3ext_SD,<br>SPI1_MISO, USART2_RX,<br>TIM3_CH1, TIM16_CH1,<br>TIM17_BKIN, TIM8_CH2N,<br>TSC_G5_IO2, NJTRST,<br>EVENTOUT | -                    |  |

| 91      | 57                                                | 41     | PB5                                      | I/O      | FT            | -     | SPI3_MOSI, SPI1_MOSI,<br>I2S3_SD, I2C1_SMBA,<br>USART2_CK, TIM16_BKIN,<br>TIM3_CH2, TIM8_CH3N,<br>TIM17_CH1, EVENTOUT                | -                    |  |

Table 13. STM32F358xC pin definitions (continued)

# 6.2 Absolute maximum ratings

Stresses above the absolute maximum ratings listed in *Table 21: Voltage characteristics*, *Table 22: Current characteristics*, and *Table 23: Thermal characteristics* may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these conditions is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

| Symbol                                             | Ratings                                                            | Min                   | Max                    | Unit |

|----------------------------------------------------|--------------------------------------------------------------------|-----------------------|------------------------|------|

| V <sub>DD</sub> -V <sub>SS</sub>                   | External digital supply voltage (including $V_{DD}$ and $V_{BAT})$ | -0.3                  | 1.95                   |      |

| $V_{DDA} - V_{SS}$                                 | External analog supply voltage                                     | -0.3                  | 4.0                    |      |

| V <sub>DD</sub> – V <sub>DDA</sub>                 | Allowed voltage difference for $V_{DD} > V_{DDA}$                  | -                     | 0.4                    |      |

| V <sub>REF+</sub> -V <sub>DDA</sub> <sup>(2)</sup> | Allowed voltage difference for $V_{REF+} > V_{DDA}$                | -                     | 0.4                    |      |

|                                                    | Input voltage on FT and FTf pins                                   | V <sub>SS</sub> -0.3  | V <sub>DD</sub> + 4.0  | V    |

|                                                    | Input voltage on TTa pins                                          | V <sub>SS</sub> - 0.3 | 4.0                    |      |

| V <sub>IN</sub> <sup>(3)</sup>                     | Input voltage on any other pin                                     | V <sub>SS</sub> - 0.3 | 4.0                    |      |

|                                                    | Input voltage on POR pin                                           | $V_{SS} - 0.3$        | V <sub>DDA</sub> + 4.0 |      |

|                                                    | Input Voltage on B Pin                                             | 0                     | 9                      |      |

| $ \Delta V_{DDx} $                                 | Variations between different V <sub>DD</sub> power pins            | -                     | 50                     | m\/  |

| V <sub>SSX</sub> –V <sub>SS</sub>                  | Variations between all the different ground pins                   | -                     | 50                     | - mV |

| V <sub>ESD(HBM)</sub>                              | Electrostatic discharge voltage (human body model)                 |                       |                        | -    |

| Table 21. | Voltage | characteristics <sup>(1)</sup> |

|-----------|---------|--------------------------------|

|-----------|---------|--------------------------------|

1. All main power (V<sub>DD</sub>, V<sub>DDA</sub>) and ground (V<sub>SS</sub>, V<sub>SSA</sub>) pins must always be connected to the external power supply, in the permitted range. The following relationship must be respected between V<sub>DDA</sub> and V<sub>DD</sub>: V<sub>DDA</sub> must power on before or at the same time as V<sub>DD</sub> in the power up sequence. V<sub>DDA</sub> must be greater than or equal to V<sub>DD</sub>.

2.  $V_{REF+}$  must be always lower or equal than  $V_{DDA}$  ( $V_{REF+} \le V_{DDA}$ ). If unused then it must be connected to  $V_{DDA}$ .

3. V<sub>IN</sub> maximum must always be respected. Refer to *Table 22: Current characteristics* for the maximum allowed injected current values.

### On-chip peripheral current consumption

The MCU is placed under the following conditions:

- all I/O pins are in analog input configuration

- all peripherals are disabled unless otherwise mentioned

- the given value is calculated by measuring the current consumption

- with all peripherals clocked off

- with only one peripheral clocked on

- ambient operating temperature at 25°C and  $V_{DD}$  = 1.8 V,  $V_{DDA}$  = 3.3 V.

#### Table 36. Peripheral current consumption

| Derinherel                 | Typical consumption <sup>(1)</sup> | l leit |

|----------------------------|------------------------------------|--------|

| Peripheral                 | I <sub>DD</sub>                    | Unit   |

| BusMatrix <sup>(2)</sup>   | 12.6                               |        |

| DMA1                       | 7.6                                |        |

| DMA2                       | 6.1                                |        |

| CRC                        | 2.1                                |        |

| GPIOA                      | 10.0                               |        |

| GPIOB                      | 10.3                               |        |

| GPIOC                      | 2.2                                |        |

| GPIOD                      | 8.8                                |        |

| GPIOE                      | 3.3                                |        |

| GPIOF                      | 3.0                                |        |

| TSC                        | 5.5                                |        |

| ADC1&2                     | 17.3                               |        |

| ADC3&4                     | 18.8                               |        |

| APB2-Bridge <sup>(3)</sup> | 3.6                                | μA/MHz |

| SYSCFG                     | 7.3                                |        |

| TIM1                       | 40.0                               |        |

| SPI1                       | 8.8                                |        |

| TIM8                       | 36.4                               |        |

| USART1                     | 23.3                               |        |

| TIM15                      | 17.1                               |        |

| TIM16                      | 10.1                               |        |

| TIM17                      | 11.0                               |        |

| APB1-Bridge <sup>(3)</sup> | 6.1                                |        |

| TIM2                       | 49.1                               |        |

| TIM3                       | 38.8                               |        |

| TIM4                       | 38.3                               |        |

| Derinheral | Typical consumption <sup>(1)</sup> | l la it |

|------------|------------------------------------|---------|

| Peripheral | I <sub>DD</sub>                    | — Unit  |

| TIM6       | 9.7                                |         |

| TIM7       | 12.1                               |         |

| WWDG       | 6.4                                |         |

| SPI2       | 40.4                               |         |

| SPI3       | 40.0                               |         |

| USART2     | 41.9                               |         |

| USART3     | 40.2                               |         |

| UART4      | 36.5                               | μA/MHz  |

| UART5      | 30.8                               |         |

| I2C1       | 10.5                               |         |

| I2C2       | 10.4                               |         |

| CAN        | 33.4                               |         |

| PWR        | 5.7                                |         |

| DAC        | 15.4                               |         |

| Table 36. Peripheral current consumption (continued) | Table 36. Pe | eripheral cu | urrent consu | motion | (continued) |

|------------------------------------------------------|--------------|--------------|--------------|--------|-------------|

|------------------------------------------------------|--------------|--------------|--------------|--------|-------------|

1. The power consumption of the analog part (I<sub>DDA</sub>) of peripherals such as ADC, DAC, Comparators, OpAmp etc. is not included. Refer to the tables of characteristics in the subsequent sections.

2. BusMatrix is automatically active when at least one master is ON (CPU, DMA1 or DMA2).

3. The APBx bridge is automatically active when at least one peripheral is ON on the same bus.

## 6.3.9 Memory characteristics

### Flash memory

The characteristics are given at  $T_{\text{A}}$  = –40 to 105  $^{\circ}\text{C}$  unless otherwise specified.

| Symbol             | Parameter               | Conditions                      | Min | Тур  | Max <sup>(1)</sup> | Unit |  |

|--------------------|-------------------------|---------------------------------|-----|------|--------------------|------|--|

| t <sub>prog</sub>  | 16-bit programming time | T <sub>A</sub> = -40 to +105 °C | 40  | 53.5 | 60                 | μs   |  |

| t <sub>ERASE</sub> | Page (2 KB) erase time  | $T_A = -40$ to +105 °C          | 20  | -    | 40                 | ms   |  |

| t <sub>ME</sub>    | Mass erase time         | $T_A = -40$ to +105 °C          | 20  | -    | 40                 | ms   |  |

|                    | Supply current          | Write mode                      | -   | -    | 10                 | mA   |  |

| IDD                |                         | Erase mode                      | -   | -    | 12                 | mA   |  |

## Table 45. Flash memory characteristics

1. Guaranteed by design, not tested in production.

| Querrahal        | Deveneter      | Conditions                                                                              | Value              | 11:::4  |

|------------------|----------------|-----------------------------------------------------------------------------------------|--------------------|---------|

| Symbol           | Parameter      | Conditions                                                                              | Min <sup>(1)</sup> | Unit    |

| N <sub>END</sub> | Endurance      | $T_A = -40$ to +85 °C (6 suffix versions)<br>$T_A = -40$ to +105 °C (7 suffix versions) | 10                 | kcycles |

|                  |                | 1 kcycle <sup>(2)</sup> at T <sub>A</sub> = 85 °C                                       | 30                 |         |

| t <sub>RET</sub> | Data retention | 1 kcycle <sup>(2)</sup> at T <sub>A</sub> = 105 °C                                      | 10                 | Years   |

|                  |                | 10 kcycles <sup>(2)</sup> at T <sub>A</sub> = 55 °C                                     | 20                 |         |

### Table 46. Flash memory endurance and data retention

1. Data based on characterization results, not tested in production.

2. Cycling performed over the whole temperature range.

#### Static latch-up

Two complementary static tests are required on six parts to assess the latch-up performance:

- A supply overvoltage is applied to each power supply pin

- A current injection is applied to each input, output and configurable I/O pin

These tests are compliant with EIA/JESD 78A IC latch-up standard.

| Table | 50.         | <b>Electrical sensitivities</b> |

|-------|-------------|---------------------------------|

| Table | <b>UU</b> . |                                 |

|   | Symbol | Parameter             | Conditions                                    | Class      |

|---|--------|-----------------------|-----------------------------------------------|------------|

| ĺ | LU     | Static latch-up class | $T_A = +105 \text{ °C conforming to JESD78A}$ | II level A |

### 6.3.12 I/O current injection characteristics

As a general rule, current injection to the I/O pins, due to external voltage below  $V_{SS}$  or above  $V_{DD}$  (for standard, 3 V-capable I/O pins) should be avoided during normal product operation. However, in order to give an indication of the robustness of the microcontroller in cases when abnormal injection accidentally happens, susceptibility tests are performed on a sample basis during device characterization.

#### Functional susceptibility to I/O current injection

While a simple application is executed on the device, the device is stressed by injecting current into the I/O pins programmed in floating input mode. While current is injected into the I/O pin, one at a time, the device is checked for functional failures.

The failure is indicated by an out of range parameter: ADC error above a certain limit (higher than 5 LSB TUE), out of conventional limits of induced leakage current on adjacent pins (out of  $-5 \mu A/+0 \mu A$  range), or other functional failure (for example reset occurrence or oscillator frequency deviation).

The test results are given in Table 51

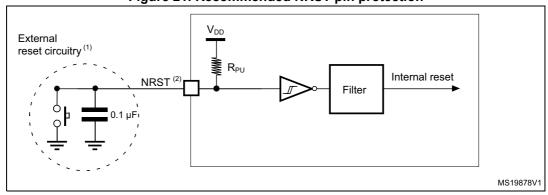

## 6.3.14 NRST pin characteristics

The NRST pin input driver uses CMOS technology. It is connected to a permanent pull-up resistor,  $R_{PU}$  (see *Table 52*).

Unless otherwise specified, the parameters given in *Table 55* are derived from tests performed under ambient temperature and  $V_{DD}$  supply voltage conditions summarized in *Table 24*.

| Symbol                               | Parameter                                       | Conditions        | Min                                            | Тур | Max                                         | Unit |

|--------------------------------------|-------------------------------------------------|-------------------|------------------------------------------------|-----|---------------------------------------------|------|

| V <sub>IL(NRST)</sub> <sup>(1)</sup> | NRST Input low level voltage                    | -                 | -                                              | -   | 0.3V <sub>DD</sub> +<br>0.07 <sup>(1)</sup> | V    |

| V <sub>IH(NRST)</sub> <sup>(1)</sup> | NRST Input high level voltage                   | -                 | 0.445V <sub>DD</sub> +<br>0.398 <sup>(1)</sup> | -   | -                                           | v    |

| V <sub>hys(NRST)</sub>               | NRST Schmitt trigger voltage hysteresis         | -                 | -                                              | 200 | -                                           | mV   |

| R <sub>PU</sub>                      | Weak pull-up equivalent resistor <sup>(2)</sup> | $V_{IN} = V_{SS}$ | 25                                             | 40  | 55                                          | kΩ   |

| V <sub>F(NRST)</sub> <sup>(1)</sup>  | NRST Input filtered pulse                       | -                 | -                                              | -   | 100 <sup>(1)</sup>                          | ns   |

| V <sub>NF(NRST)</sub> <sup>(1)</sup> | NRST Input not filtered pulse                   | -                 | 700 <sup>(1)</sup>                             | -   | -                                           | ns   |

Table 55. NRST pin characteristics

1. Guaranteed by design, not tested in production.

2. The pull-up is designed with a true resistance in series with a switchable PMOS. This PMOS contribution to the series resistance must be minimum (~10% order).

Figure 21. Recommended NRST pin protection

1. The reset network protects the device against parasitic resets.

The user must ensure that the level on the NRST pin can go below the V<sub>IL(NRST)</sub> max level specified in Table 55. Otherwise the reset will not be taken into account by the device.

### 6.3.15 NPOR pin characteristics

The NPOR pin input driver uses CMOS technology. It is connected to a permanent pull-up resistor, Rpu (see *Table 56*) connected to  $V_{DDA}$  supply.

Unless otherwise specified, the parameters given in *Table 56* are derived from tests performed under ambient temperature and  $V_{DDA}$  supply voltage conditions summarized in *Table 24*.

| Symbol <sup>(1)</sup>  | Parameter                                       | Conditions        | Min                          | Тур | Мах                            | Unit |  |  |

|------------------------|-------------------------------------------------|-------------------|------------------------------|-----|--------------------------------|------|--|--|

| V <sub>IL(NPOR)</sub>  | NPOR Input low level voltage                    | -                 | -                            | -   | 0.475V <sub>DDA</sub><br>- 0.2 | v    |  |  |

| V <sub>IH(NPOR)</sub>  | NPOR Input high level voltage                   | -                 | 0.5V <sub>DDA</sub><br>+ 0.2 | -   | -                              | v    |  |  |

| V <sub>hys(NPOR)</sub> | NPOR Schmitt trigger voltage<br>hysteresis      | -                 | -                            | 100 | -                              | mV   |  |  |

| R <sub>PU</sub>        | Weak pull-up equivalent resistor <sup>(2)</sup> | $V_{IN} = V_{SS}$ | 25                           | 40  | 55                             | kΩ   |  |  |

Table 56. NPOR pin characteristics

1. Guaranteed by design, not tested in production.

2. The pull-up is designed with a true resistance in series with a switchable PMOS. This PMOS contribution to the series resistance is minimal (~10% order).

## 6.3.16 Timer characteristics

The parameters given in *Table 57* are guaranteed by design.

Refer to *Section 6.3.13: I/O port characteristics* for details on the input/output alternate function characteristics (output compare, input capture, external clock, PWM output).

| Symbol                 | Parameter                   | Conditions                                | Min    | Мах                     | Unit                 |

|------------------------|-----------------------------|-------------------------------------------|--------|-------------------------|----------------------|

|                        |                             | -                                         | 1      | -                       | t <sub>TIMxCLK</sub> |

| t <sub>res(TIM)</sub>  | Timer resolution time       | f <sub>TIMxCLK</sub> = 72 MHz             | 13.9   | -                       | ns                   |

| ,                      |                             | f <sub>TIMxCLK</sub> = 144 MHz,<br>x= 1.8 | 6.95   | -                       | ns                   |

| f <sub>EXT</sub>       | Timer external clock        | -                                         | 0      | f <sub>TIMxCLK</sub> /2 | MHz                  |

| 'EXT                   | frequency on CH1 to CH4     | f <sub>TIMxCLK</sub> = 72 MHz             | 0      | 36                      | MHz                  |

| Res <sub>TIM</sub>     | Timer resolution            | TIMx (except TIM2)                        | -      | 16                      | bit                  |

| TC31M                  |                             | TIM2                                      | -      | 32                      | DIL                  |

|                        |                             | -                                         | 1      | 65536                   | t <sub>TIMxCLK</sub> |

| t <sub>COUNTER</sub>   | 16-bit counter clock period | f <sub>TIMxCLK</sub> = 72 MHz             | 0.0139 | 910                     | μs                   |

|                        |                             | f <sub>TIMxCLK</sub> = 144 MHz,<br>x= 1.8 | 0.0069 | 455                     | μs                   |

|                        |                             | -                                         | -      | 65536 × 65536           | t <sub>TIMxCLK</sub> |

| t <sub>MAX_COUNT</sub> | Maximum possible count      | f <sub>TIMxCLK</sub> = 72 MHz             | -      | 59.65                   | S                    |

| MAX_COUNT              | with 32-bit counter         | f <sub>TIMxCLK</sub> = 144 MHz,<br>x= 1.8 | -      | 29.825                  | S                    |

Table 57. TIMx<sup>(1)(2)</sup> characteristics

1. TIMx is used as a general term to refer to the TIM1, TIM2, TIM3, TIM4, TIM6, TIM15, TIM16 and TIM17 timers.

2. Guaranteed by design, not tested in production.

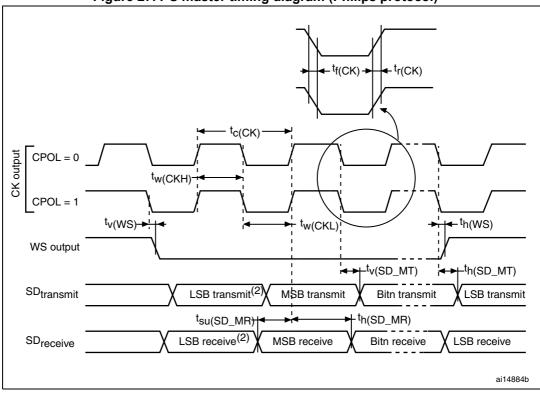

Figure 27. I<sup>2</sup>S master timing diagram (Philips protocol)<sup>(1)</sup>

1. Measurement points are done at  $0.5V_{\text{DD}}$  and with external C\_L=30 pF.

2. LSB transmit/receive of the previously transmitted byte. No LSB transmit/receive is sent before the first byte.

#### CAN (controller area network) interface

Refer to Section 6.3.13: I/O port characteristics for more details on the input/output alternate function characteristics (CAN\_TX and CAN\_RX).

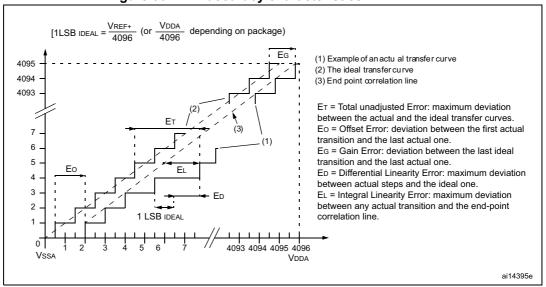

## 6.3.18 ADC characteristics

Unless otherwise specified, the parameters given in *Table 64* to *Table 67* are guaranteed by design, with conditions summarized in *Table 24*.

| Symbol                        | Parameter                           | Conditions                            | Min    | Тур       | Max              | Unit |  |

|-------------------------------|-------------------------------------|---------------------------------------|--------|-----------|------------------|------|--|

| V <sub>DDA</sub>              | Analog supply voltage for ADC       | -                                     | 1.8    | -         | 3.6              | V    |  |

|                               |                                     | Single-ended mode,<br>5 MSPS          | -      | 907       | 1033.0           |      |  |

|                               |                                     | Single-ended mode,<br>1 MSPS          | -      | 194       | 285.5            |      |  |

| 1                             | ADC current consumption on VDDA     | Single-ended mode,<br>200 KSPS        | -      | 51.5      | 70               | μA   |  |

| I <sub>DDA</sub>              | pin<br>(see <i>Figur</i> e 28)      | Differential mode,<br>5 MSPS          | -      | 887.<br>5 | 1009             | μΑ   |  |

|                               |                                     | Differential mode,<br>1 MSPS          | -      | 212       | 285              |      |  |

|                               |                                     | Differential mode,<br>200 KSPS        | -      | 51        | 69.5             |      |  |

| V <sub>REF+</sub>             | Positive reference voltage          | -                                     | 2      | -         | V <sub>DDA</sub> | V    |  |

|                               | ADC current<br>consumption on VREF+ | Single-ended mode,<br>5 MSPS          | -      | 104       | 139              |      |  |

|                               |                                     | Single-ended mode,<br>1 MSPS          | -      | 20.4      | 37               |      |  |

| 1                             |                                     | Single-ended mode,<br>200 KSPS        | -      | 3.3       | 11.3             | μA   |  |

| I <sub>REF</sub>              | pin<br>(see <i>Figure 2</i> 9)      | Differential mode,<br>5 MSPS          | -      | 174       | 235              | μΛ   |  |

|                               |                                     | Differential mode,<br>1 MSPS          | -      | 34.6      | 52.6             |      |  |

|                               |                                     | Differential mode,<br>200 KSPS        | -      | 6         | 13.6             |      |  |

| f <sub>ADC</sub>              | ADC clock frequency                 |                                       | 0.14   | -         | 72               | MHz  |  |

|                               |                                     | Resolution = 12 bits,<br>Fast Channel | 0.01   | -         | 5.14             |      |  |

| f <sub>S</sub> <sup>(1)</sup> | Sampling rate                       | Resolution = 10 bits,<br>Fast Channel | 0.012  | -         | 6                | MSPS |  |

| IS, ,                         | Sampling rate                       | Resolution = 8 bits,<br>Fast Channel  | 0.014  | -         | 7.2              |      |  |

|                               |                                     | Resolution = 6 bits,<br>Fast Channel  | 0.0175 | -         | 9                |      |  |

| •                                   |             |                                                      | coonditionio | ree pin packages    | (00        | mina | 04, |    |

|-------------------------------------|-------------|------------------------------------------------------|--------------|---------------------|------------|------|-----|----|

| Symbol                              | Parameter   | C                                                    | Min<br>(3)   | Тур                 | Max<br>(3) | Unit |     |    |

|                                     |             |                                                      | Cingle ended | Fast channel 5.1 Ms | 66         | 67   | -   |    |

|                                     | Signal-to-  |                                                      | Single ended | Slow channel 4.8 Ms | 66         | 67   | -   |    |

| SNR noise ratio                     | noise ratio | Sampling freq $\leq$ 5 Msps                          | Differential | Fast channel 5.1 Ms | 69         | 70   | -   |    |

|                                     |             |                                                      |              | Slow channel 4.8 Ms | 69         | 70   | -   | dB |

|                                     |             | V <sub>DDA</sub> = V <sub>REF+</sub> = 3.3 V<br>25°C | Cingle and d | Fast channel 5.1 Ms | -          | -76  | -76 | uв |

| Total<br>THD harmonic<br>distortion |             | 100-pin package                                      | Single ended | Slow channel 4.8 Ms | -          | -76  | -76 |    |

|                                     |             |                                                      | Differential | Fast channel 5.1 Ms | -          | -80  | -80 |    |

|                                     |             |                                                      | Dillerential | Slow channel 4.8 Ms | -          | -80  | -80 |    |

## Table 66. ADC accuracy - limited test conditions 100-pin packages<sup>(1)(2)</sup> (continued)

1. ADC DC accuracy values are measured after internal calibration.

ADC accuracy vs. negative Injection Current: Injecting negative current on any analog input pins should be avoided as this significantly reduces the accuracy of the conversion being performed on another analog input. It is recommended to add a Schottky diode (pin to ground) to analog pins which may potentially inject negative current. Any positive injection current within the limits specified for I<sub>INJ(PIN)</sub> and ΣI<sub>INJ(PIN)</sub> in Section 6.3.13 does not affect the ADC accuracy.

3. Data based on characterization results, not tested in production.

1

1

| Symbol        | Parameter              | Conditions                                                                                                                                                                                                          |                     |                     |      | Max <sup>(4)</sup> | Unit |

|---------------|------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|---------------------|------|--------------------|------|

|               |                        |                                                                                                                                                                                                                     | Single Ended        | Fast channel 5.1 Ms | -    | ±6.5               |      |

| ET            | Total                  |                                                                                                                                                                                                                     | Single Ended        | Slow channel 4.8 Ms | -    | ±6.5               |      |

|               | unadjusted<br>error    |                                                                                                                                                                                                                     | Differential        | Fast channel 5.1 Ms | -    | ±4                 |      |

|               |                        |                                                                                                                                                                                                                     | Dillerential        | Slow channel 4.8 Ms | -    | ±4.5               |      |

|               |                        |                                                                                                                                                                                                                     | Single Ended        | Fast channel 5.1 Ms | -    | £3                 |      |

| EO            | Offset error           |                                                                                                                                                                                                                     |                     | Slow channel 4.8 Ms | -    | ±3                 |      |

| EO            | Oliset el loi          |                                                                                                                                                                                                                     | Differential        | Fast channel 5.1 Ms | -    | ±2.5               |      |

|               | Differe                | Dillerential                                                                                                                                                                                                        | Slow channel 4.8 Ms | -                   | ±2.5 |                    |      |

|               |                        |                                                                                                                                                                                                                     | Single Ended        | Fast channel 5.1 Ms | -    | ±6                 |      |

| EG            |                        |                                                                                                                                                                                                                     |                     | Slow channel 4.8 Ms | -    | <b>±</b> 6         | LSB  |

| EG Gain error | Gainenoi               | $\label{eq:ADC clock freq. } \begin{array}{l} \mbox{ADC clock freq. } \le 72 \mbox{ MHz}, \\ \mbox{Sampling freq. } \le 5 \mbox{ Msps} \\ \mbox{1.8V} \le V_{DDA} \mbox{, } V_{REF+} \le 3.6 \mbox{ V} \end{array}$ | Differential        | Fast channel 5.1 Ms | -    | ±3.5               | LOD  |

|               |                        |                                                                                                                                                                                                                     | Differential        | Slow channel 4.8 Ms | -    | ±4                 | 1    |

|               |                        |                                                                                                                                                                                                                     | Single Ended        | Fast channel 5.1 Ms | -    | ±1.5               |      |

| ED            | Differential linearity | 64-pin package                                                                                                                                                                                                      |                     | Slow channel 4.8 Ms | -    | ±1.5               |      |

| LD            | error                  |                                                                                                                                                                                                                     | Differential        | Fast channel 5.1 Ms | -    | ±1.5               |      |

|               |                        |                                                                                                                                                                                                                     | Differential        | Slow channel 4.8 Ms | -    | ±1.5               |      |

|               |                        |                                                                                                                                                                                                                     | Single Ended        | Fast channel 5.1 Ms | -    | <del>13</del>      |      |

| EL            | Integral<br>linearity  |                                                                                                                                                                                                                     |                     | Slow channel 4.8 Ms | -    | ±3.5               |      |

| LL            | error                  |                                                                                                                                                                                                                     | Differential        | Fast channel 5.1 Ms | -    | ±2                 |      |

|               |                        |                                                                                                                                                                                                                     | Differentia         | Slow channel 4.8 Ms | -    | ±2.5               |      |

|               |                        |                                                                                                                                                                                                                     | Single Ended        | Fast channel 5.1 Ms | 10.4 | -                  |      |

| ENOB          | Effective number of    |                                                                                                                                                                                                                     |                     | Slow channel 4.8 Ms | 10.4 | -                  | bits |

| 21100         | bits                   |                                                                                                                                                                                                                     | Differential        | Fast channel 5.1 Ms | 10.8 | -                  |      |

|               |                        |                                                                                                                                                                                                                     | Billerential        | Slow channel 4.8 Ms | 10.8 | -                  |      |

Table 69. ADC accuracy, 64-pin packages<sup>(1)(2)(3)</sup>

#### Figure 30. ADC accuracy characteristics

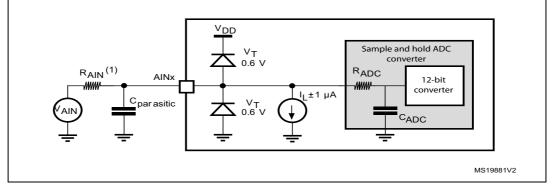

#### Figure 31. Typical connection diagram using the ADC

1. Refer to *Table 64* for the values of R<sub>AIN</sub>.

C<sub>parasitic</sub> represents the capacitance of the PCB (dependent on soldering and PCB layout quality) plus the pad capacitance (roughly 7 pF). A high C<sub>parasitic</sub> value will downgrade conversion accuracy. To remedy this, f<sub>ADC</sub> should be reduced.

#### General PCB design guidelines

Power supply decoupling should be performed as shown in *Figure 10*. The 10 nF capacitor should be ceramic (good quality) and it should be placed as close as possible to the chip.

# 6.3.21 Operational amplifier characteristics

| Symbol               | Param                                                                                                   | neter             | Condition                                                                                       | Min | Тур | Max              | Unit  |

|----------------------|---------------------------------------------------------------------------------------------------------|-------------------|-------------------------------------------------------------------------------------------------|-----|-----|------------------|-------|

| V <sub>DDA</sub>     | Analog supply voltage                                                                                   |                   | -                                                                                               | 2.4 | -   | 3.6              | V     |

| CMIR                 | Common mode inpu                                                                                        | t range           | -                                                                                               | 0   | -   | V <sub>DDA</sub> | V     |

|                      |                                                                                                         | Maximum           | 25°C, No Load on output.                                                                        | -   | -   | 4                |       |

| \/I                  | Input offset voltage                                                                                    | calibration range | All<br>voltage/Temp.                                                                            | -   | -   | 6                | mV    |

| VI <sub>OFFSET</sub> | input onset voltage                                                                                     | After offset      | 25°C, No Load on output.                                                                        | -   | -   | 1.6              | IIIV  |

|                      |                                                                                                         | calibration       | All<br>voltage/Temp.                                                                            | -   | -   | 3                |       |

| $\Delta VI_{OFFSET}$ | Input offset voltage drift                                                                              |                   | -                                                                                               | -   | 5   | -                | µV/°C |

| I <sub>LOAD</sub>    | Drive current                                                                                           |                   | -                                                                                               | -   | -   | 500              | μA    |

| IDDOPAMP             |                                                                                                         |                   | No load,<br>quiescent mode                                                                      | -   | 690 | 1450             | μA    |

| CMRR                 | Common mode reject                                                                                      | ction ratio       | -                                                                                               | -   | 90  | -                | dB    |

| PSRR                 | Power supply rejection ratio                                                                            |                   | DC                                                                                              | 73  | 117 | -                | dB    |

| GBW                  | Bandwidth                                                                                               |                   | -                                                                                               | -   | 8.2 | -                | MHz   |

| SR                   | Slew rate                                                                                               |                   | -                                                                                               | -   | 4.7 | -                | V/µs  |

| R <sub>LOAD</sub>    | Resistive load                                                                                          |                   | -                                                                                               | 4   | -   | -                | kΩ    |

| C <sub>LOAD</sub>    | Capacitive load                                                                                         |                   | -                                                                                               | -   | -   | 50               | pF    |

| VOH                  | High saturation voltage                                                                                 |                   | R <sub>load</sub> = min,<br>Input at V <sub>DDA</sub> .                                         | -   | -   | 100              |       |

| VOH <sub>SAT</sub>   |                                                                                                         |                   | R <sub>load</sub> = 20K,<br>Input at V <sub>DDA</sub> .                                         | -   | -   | 20               | mV    |

|                      | Low saturation voltage                                                                                  | 20                | Rload = min,<br>input at 0V                                                                     | -   | -   | 100              | IIIV  |

| VOL <sub>SAT</sub>   |                                                                                                         | ye                | Rload = 20K,<br>input at 0V.                                                                    | -   | -   | 20               |       |

| φm                   | Phase margin                                                                                            |                   | -                                                                                               | -   | 62  | -                | 0     |

| t <sub>offtrim</sub> | Offset trim time: during calibration,<br>minimum time needed between two<br>steps to have 1 mV accuracy |                   | -                                                                                               | -   | -   | 2                | ms    |

| t <sub>wakeup</sub>  | Wake up time from C                                                                                     | DFF state.        | $C_{LOAD} \le 50 \text{ pf},$<br>$R_{LOAD} \ge 4 \text{ k}\Omega,$<br>Follower<br>configuration | -   | 2.8 | 5                | μs    |

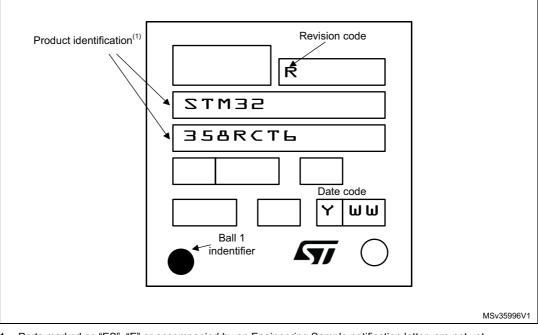

### **Device marking**

The following figure gives an example of topside marking orientation versus pin 1 identifier location.

Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter, are not yet qualified and therefore not yet ready to be used in production and any consequences deriving from such usage will not be at ST charge. In no event, ST will be liable for any customer usage of these engineering samples in production. ST Quality has to be contacted prior to any decision to use these Engineering samples to run qualification activity.