Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFl

| 2000                       |                                                              |

|----------------------------|--------------------------------------------------------------|

| Product Status             | Active                                                       |

| Core Processor             | S12Z                                                         |

| Core Size                  | 16-Bit                                                       |

| Speed                      | 32MHz                                                        |

| Connectivity               | CANbus, I <sup>2</sup> C, LINbus, SCI, SPI                   |

| Peripherals                | DMA, LCD, POR, PWM, WDT                                      |

| Number of I/O              | 78                                                           |

| Program Memory Size        | 128KB (128K x 8)                                             |

| Program Memory Type        | FLASH                                                        |

| EEPROM Size                | 4K x 8                                                       |

| RAM Size                   | 8K x 8                                                       |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 5.5V                                                  |

| Data Converters            | A/D 4x10b                                                    |

| Oscillator Type            | Internal                                                     |

| Operating Temperature      | -40°C ~ 85°C (TA)                                            |

| Mounting Type              | Surface Mount                                                |

| Package / Case             | 100-LQFP                                                     |

| Supplier Device Package    | 100-LQFP (14x14)                                             |

| Purchase URL               | https://www.e-xfl.com/pro/item?MUrl=&PartUrl=s912zvh128f2cll |

|                            |                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Chapter 2 Port Integration Module (S12ZVHPIMV0)

| Port | Pin Name | Pin Function<br>& Priority <sup>(1)</sup> | I/O | Description Routing Register     | Pin<br>Function<br>after Reset |

|------|----------|-------------------------------------------|-----|----------------------------------|--------------------------------|

| U    | PU[7]    | M1SINP                                    | I/O | SSD1 Sine+ Node                  | GPIO                           |

|      |          | M1C1P                                     | 0   | Motor control output for motor 1 |                                |

|      |          | PTU[7]                                    | I/O | General purpose                  |                                |

|      | PU[6]    | M1SINM                                    | I/O | SSD1 Sine- Node                  |                                |

|      |          | M1C1M                                     | 0   | Motor control output for motor 1 |                                |

|      |          | IOC0_3                                    | I/O | TIM0 channel 3                   |                                |

|      |          | PTU[6]                                    | I/O | General purpose                  |                                |

|      | PU[5]    | M1COSP                                    | I/O | SSD1 Cosine+ Node                |                                |

|      |          | M1C0P                                     | 0   | Motor control output for motor 1 |                                |

|      |          | PTU[5]                                    | I/O | General purpose                  |                                |

|      | PU[4]    | M1COSM                                    | I/O | SSD1 Cosine- Node                |                                |

|      |          | M1C0M                                     | 0   | Motor control output for motor 1 |                                |

|      |          | IOC0_2 I/O                                |     | TIM0 channel2                    |                                |

|      |          | PTU[4]                                    | I/O | General purpose                  |                                |

|      | PU[3]    | MOSINP                                    | I/O | SSD0 Sine+ Node                  |                                |

|      |          | M0C1P                                     | 0   | Motor control output for motor 0 |                                |

|      |          | PTU[3]                                    | I/O | General purpose                  |                                |

|      | PU[2]    | MOSINM                                    | I/O | SSD0 Sine- Node                  |                                |

|      |          | M0C1M                                     | 0   | Motor control output for motor 0 |                                |

|      |          | IOC0_1                                    | I/O | TIM0 channel 1                   |                                |

|      |          | PTU[2]                                    | I/O | General purpose                  |                                |

|      | PU[1]    | M0COSP                                    | I/O | SSD0 Cosine+ Node                |                                |

|      |          | M0C0P                                     | 0   | Motor control output for motor 0 |                                |

|      |          | PTU[1]                                    | I/O | General purpose                  |                                |

|      | PU[0]    | M0COSM                                    | I/O | SSD0 Cosine- Node                |                                |

|      |          | MOCOM                                     | 0   | Motor control output for motor 0 |                                |

|      |          | IOC0_0                                    | I/O | TIM0 channel 0                   |                                |

|      |          | PTU[0]                                    | I/O | General purpose                  |                                |

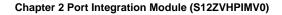

## 2.3.2.12 Data Direction Register

Figure 2-14. Data Direction Register

1. Read: Anytime Write: Anytime

#### Table 2-13. Data Direction Register Field Descriptions

| Field       | Description                                                                         |

|-------------|-------------------------------------------------------------------------------------|

| 7-0<br>DDRx | Data Direction — Select general-purpose data direction                              |

|             | This bit determines whether the pin is a general-purpose input or output.           |

|             | 1 Associated pin is configured as output<br>0 Associated pin is configured as input |

#### NOTE

Due to internal synchronization circuits, it can take up to two bus clock cycles until the correct value is read on port data and port input registers, when changing the data direction register.

The general-purpose data direction configuration can be overruled by an enabled peripheral function shared on the same pin (Table 2-22). If more then one peripheral function is available and enabled at the same time, the highest ranked module according the predefined priority scheme in Table 2-1 will take precedence on the pin.

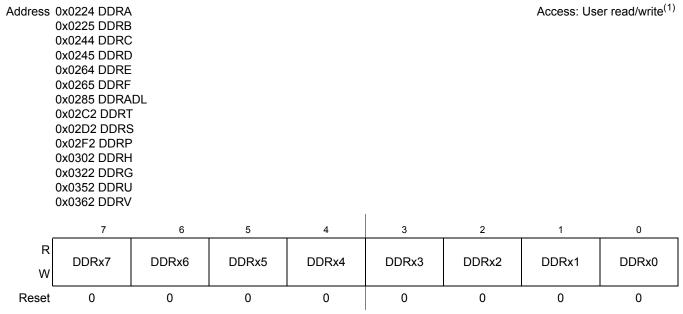

# 2.3.2.18 Port Interrupt Flag Register

1. Read: Anytime Write: Anytime

#### Table 2-19. Port Interrupt Flag Register Field Descriptions

| Field       | Description                                                                                                                                                                                                             |

|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7-0<br>PIFx | Port Interrupt Flag — Signal pin event                                                                                                                                                                                  |

|             | The flag asserts after a valid active edge was detected on the related pin (see Section 2.4.4, "Pin interrupts and Wakeup"). This can be a rising or a falling edge based on the state of the polarity select register. |

|             | Writing a logic "1" to the corresponding bit field clears the flag.                                                                                                                                                     |

|             | 1 Active edge on the associated bit has occurred (an interrupt will occur if the associated enable bit is set)<br>0 No active edge occurred                                                                             |

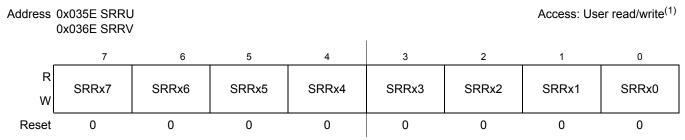

## 2.3.2.19 Port Slew Rate Register

Figure 2-21. Port Slew Rate Register

1. Read: Anytime

Write: Anytime

#### Table 2-20. Port Interrupt Flag Register Field Descriptions

| Field       | Description                                                                                                                                |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------------|

| 7-0<br>SRRx | Port Slew Rate— Slew Rate control <sup>(1)</sup>                                                                                           |

|             | 1 Enable the slew rate control and disable the digital input buffer<br>0 Disable the slew rate control and enable the digital input buffer |

1. To use the digital input function the related bit in Digital Input Enable Register (DIENADx) must be set to logic level "1". To use the digital input function the related bit in Slew Rate Register (SRRx) must be set to logic level "0".

## 2.4.2.1 Data register (PTx)

This register holds the value driven out to the pin if the pin is used as a general-purpose I/O.

Writing to this register has only an effect on the pin if the pin is used as general-purpose output. When reading this address, the synchronized state of the pin is returned if the associated data direction register bits are configured as input.

If the data direction register bits are configured as output, the contents of the data register is returned. This is independent of any other configuration (Figure 2-23).

## 2.4.2.2 Input register (PTIx)

This register is read-only and always returns the synchronized state of the pin (Figure 2-23).

## 2.4.2.3 Data direction register (DDRx)

This register defines whether the pin is used as an general-purpose input or an output.

If a peripheral module controls the pin the contents of the data direction register is ignored (Figure 2-23).

Independent of the pin usage with a peripheral module this register determines the source of data when reading the associated data register address (Section 2.4.2.1, "Data register (PTx)").

## NOTE

Due to internal synchronization circuits, it can take up to 2 bus clock cycles until the correct value is read on port data or port input registers, when changing the data direction register.

#### Chapter 3 Memory Mapping Control (S12ZMMCV1)

• All illegal accesses performed by the ADC module trigger error interrupts. See ADC section for details.

## NOTE

Illegal accesses caused by S12ZCPU opcode prefetches will also trigger machine exceptions, even if those opcodes might not be executed in the program flow. To avoid these machine exceptions, S12ZCPU instructions must not be executed from the last (high addresses) 8 bytes of RAM, EEPROM, and Flash.

# 3.4.3 Uncorrectable ECC Faults

RAM and flash use error correction codes (ECC) to detect and correct memory corruption. Each uncorrectable memory corruption, which is detected during a S12ZCPU or ADC access triggers a machine exception. Uncorrectable memory corruptions which are detected during a S12ZBDC access, are captured in the RAMWF or the RDINV bit of the BDCCSRL register.

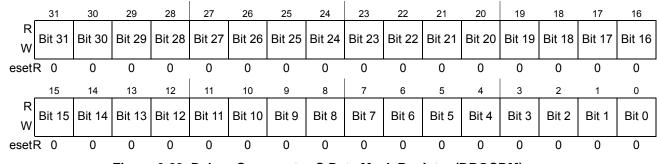

## 6.3.2.20 Debug Comparator C Data Register (DBGCD)

|        | 31         | 30     | 29     | 28     | 27     | 26     | 25     | 24     | 23     | 22     | 21     | 20     | 19     | 18     | 17     | 16     |

|--------|------------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|

| R<br>W | Bit 31     | Bit 30 | Bit 29 | Bit 28 | Bit 27 | Bit 26 | Bit 25 | Bit 24 | Bit 23 | Bit 22 | Bit 21 | Bit 20 | Bit 19 | Bit 18 | Bit 17 | Bit 16 |

| esetF  | R 0        | 0      | 0      | 0      | 0      | 0      | 0      | 0      | 0      | 0      | 0      | 0      | 0      | 0      | 0      | 0      |

|        | 15         | 14     | 13     | 12     | 11     | 10     | 9      | 8      | 7      | 6      | 5      | 4      | 3      | 2      | 1      | 0      |

| R<br>W | Bit 15     | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9  | Bit 8  | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  |

| esetF  | <b>२</b> 0 | 0      | 0      | 0      | 0      | 0      | 0      | 0      | 0      | 0      | 0      | 0      | 0      | 0      | 0      | 0      |

Address: 0x0138, 0x0139, 0x013A, 0x013B

Figure 6-22. Debug Comparator C Data Register (DBGCD)

Read: Anytime.

Write: If DBG not armed and PTACT is clear.

This register can be accessed with a byte resolution, whereby DBGCD0, DBGCD1, DBGCD2, DBGCD3 map to DBGCD[31:0] respectively.

XGATE data accesses have a maximum width of 16-bits and are mapped to DBGCD[15:0].

#### Table 6-36. DBGCD Field Descriptions

| Field                                       | Description                                                                                                                                                                                                                                                                                                                                                      |

|---------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31–16<br>Bits[31:16]<br>(DBGCD0,<br>DBGCD1) | <ul> <li>Comparator Data Bits — These bits control whether the comparator compares the data bus bits to a logic one or logic zero. The comparator data bits are only used in comparison if the corresponding data mask bit is logic 1.</li> <li>Compare corresponding data bit to a logic zero</li> <li>Compare corresponding data bit to a logic one</li> </ul> |

| 15–0<br>Bits[15:0]<br>(DBGCD2,<br>DBGCD3)   | <ul> <li>Comparator Data Bits — These bits control whether the comparator compares the data bus bits to a logic one or logic zero. The comparator data bits are only used in comparison if the corresponding data mask bit is logic 1.</li> <li>Compare corresponding data bit to a logic zero</li> <li>Compare corresponding data bit to a logic one</li> </ul> |

## 6.3.2.21 Debug Comparator C Data Mask Register (DBGCDM)

Address: 0x013C, 0x013D, 0x013E, 0x013F

Figure 6-23. Debug Comparator C Data Mask Register (DBGCDM)

Read: Anytime.

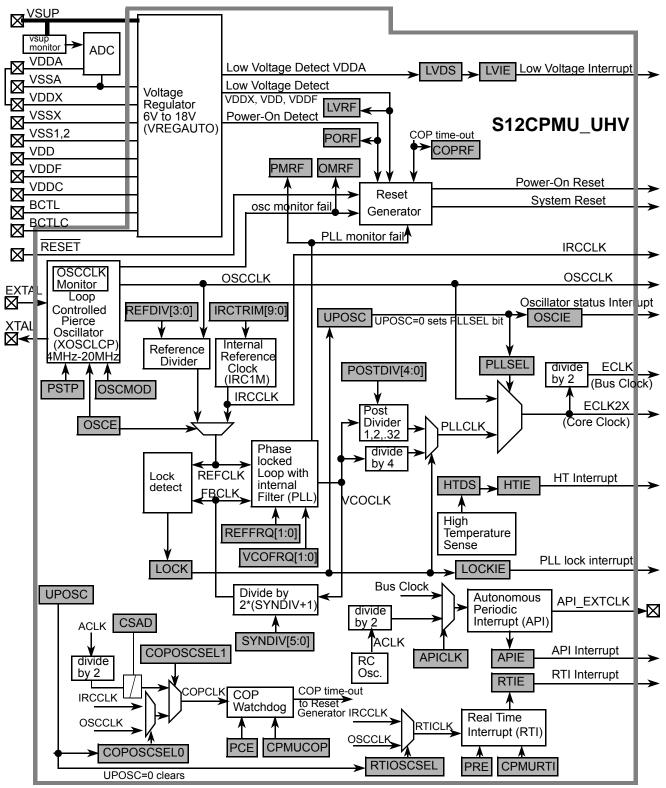

# 7.1.3 S12CPMU\_UHV\_V6 Block Diagram

Figure 7-1. Block diagram of S12CPMU\_UHV\_V6

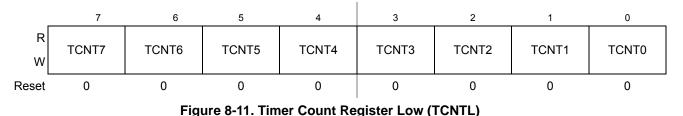

Chapter 8 Timer Module (TIM16B8CV3) Block Description

The 16-bit main timer is an up counter.

A full access for the counter register should take place in one clock cycle. A separate read/write for high byte and low byte will give a different result than accessing them as a word.

Read: Anytime

Write: Has no meaning or effect in the normal mode; only writable in special modes .

The period of the first count after a write to the TCNT registers may be a different size because the write is not synchronized with the prescaler clock.

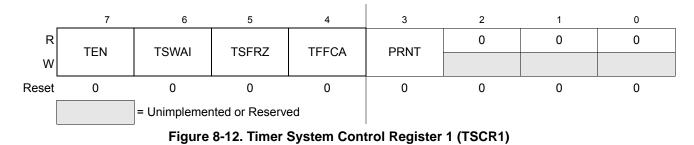

## 8.3.2.6 Timer System Control Register 1 (TSCR1)

#### Read: Anytime

Write: Anytime

| Field      | Description                                                                                                                                                                                                                                                                                                                                        |

|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>TEN   | <ul> <li>Timer Enable</li> <li>0 Disables the main timer, including the counter. Can be used for reducing power consumption.</li> <li>1 Allows the timer to function normally.</li> <li>If for any reason the timer is not active, there is no ÷64 clock for the pulse accumulator because the ÷64 is generated by the timer prescaler.</li> </ul> |

| 6<br>TSWAI | <ul> <li>Timer Module Stops While in Wait</li> <li>0 Allows the timer module to continue running during wait.</li> <li>1 Disables the timer module when the MCU is in the wait mode. Timer interrupts cannot be used to get the MCU out of wait.</li> <li>TSWAI also affects pulse accumulator.</li> </ul>                                         |

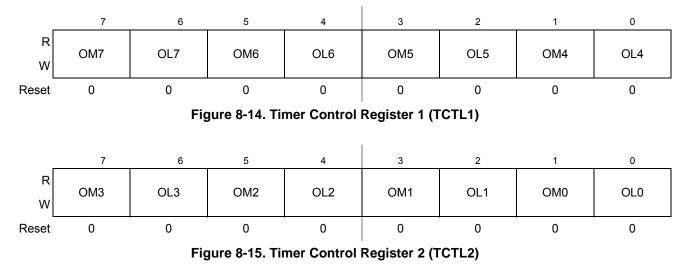

# 8.3.2.8 Timer Control Register 1/Timer Control Register 2 (TCTL1/TCTL2)

Read: Anytime

Write: Anytime

#### Table 8-8. TCTL1/TCTL2 Field Descriptions

Note: Writing to unavailable bits has no effect. Reading from unavailable bits return a zero

| Field      | Description                                                                                                                                                                                                                                                                                                                                                                                                                  |

|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0<br>OMx | Output Mode — These eight pairs of control bits are encoded to specify the output action to be taken as a result of a successful OCx compare. When either OMx or OLx is 1, the pin associated with OCx becomes an output tied to OCx.         Note: To enable output action by OMx bits on timer port, the corresponding bit in OC7M should be cleared. For an output line to be driven by an OCx the OCPDx must be cleared. |

| 7:0<br>OLx | Output Level — These eightpairs of control bits are encoded to specify the output action to be taken as a result of a successful OCx compare. When either OMx or OLx is 1, the pin associated with OCx becomes an output tied to OCx.         Note: To enable output action by OLx bits on timer port, the corresponding bit in OC7M should be cleared. For an output line to be driven by an OCx the OCPDx must be cleared. |

#### Table 8-9. Compare Result Output Action

| ОМх | OLx | Action                                                 |

|-----|-----|--------------------------------------------------------|

| 0   | 0   | No output compare<br>action on the timer output signal |

| 0   | 1   | Toggle OCx output line                                 |

| 1   | 0   | Clear OCx output line to zero                          |

| 1   | 1   | Set OCx output line to one                             |

Note: To enable output action using the OM7 and OL7 bits on the timer port, the corresponding bit OC7M7 in the OC7M register must also be cleared. The settings for these bits can be seen inTable 8-10.

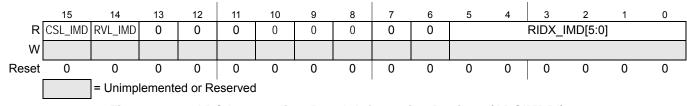

## 10.4.2.13 ADC Intermediate Result Information Register (ADCIMDRI)

This register is cleared when bit ADC\_SR is set or bit ADC\_EN is clear.

Module Base + 0x000E

#### Figure 10-16. ADC Intermediate Result Information Register (ADCIMDRI)

#### Read: Anytime

Write: Never

#### Table 10-17. ADCIMDRI Field Descriptions

| Field                | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15<br>CSL_IMD        | Active CSL At Intermediate Event — This bit indicates the active (used) CSL at the occurrence of a conversion interrupt flag (CON_IF[15:1]) (occurrence of an intermediate result buffer fill event) or when a Sequence Abort Event gets executed.<br>0 CSL_0 active (used) when a conversion interrupt flag (CON_IF[15:1]) got set.<br>1 CSL_1 active (used) when a conversion interrupt flag (CON_IF[15:1]) got set.                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 14<br>RVL_IMD        | <ul> <li>Active RVL At Intermediate Event — This bit indicates the active (used) RVL buffer at the occurrence of a conversion interrupt flag (CON_IF[15:1]) (occurrence of an intermediate result buffer fill event) or when a Sequence Abort Event gets executed.</li> <li>0 RVL_0 active (used) when a conversion interrupt flag (CON_IF[15:1]) got set.</li> <li>1 RVL_1 active (used) when a conversion interrupt flag (CON_IF[15:1]) got set.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                |

| 5-0<br>RIDX_IMD[5:0] | <b>RES_IDX Value At Intermediate Event</b> — These bits indicate the result index (RES_IDX) value at the occurrence of a conversion interrupt flag (CON_IF[15:1]) (occurrence of an intermediate result buffer fill event) or occurrence of EOL_IF flag or when a Sequence Abort Event gets executed to abort an ongoing conversion (the result index RES_IDX is captured at the occurrence of a result data store).                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                      | <ul> <li>When a Sequence Abort Event has been processed flag SEQAD_IF is set and the RES_IDX value of the last stored result is provided. Hence in case an ongoing conversion is aborted the RES_IDX value captured in RIDX_IMD bits depends on bit STORE_SEQA:</li> <li>STORE_SEQA =1: The result index of the aborted conversion is provided</li> <li>STORE_SEQA =0: The result index of the last stored result at abort execution time is provided In case a CSL is aborted while no conversion is ongoing (ADC waiting for a Trigger Event) the last captured result index is provided.</li> <li>In case a Sequence Abort Event was initiated by hardware due to MCU entering Stop Mode or Wait Mode with bit SWAI set, the result index of the last stored result is captured by bits RIDX_IMD but flag SEQAD_IF is not set.</li> </ul> |

## NOTE

The register ADCIMDRI is updated and simultaneously a conversion interrupt flag CON\_IF[15:1] occurs when the corresponding conversion command (conversion command with INTFLG\_SEL[3:0] set) has been processed and related data has been stored to RAM.

Please note that there is always a pump phase of two ADC\_CLK cycles before the sample phase begins, hence glitches during the pump phase could impact the conversion accuracy for short sample times.

# 10.5.3 Digital Sub-Block

The digital sub-block contains a list-based programmer's model and the control logic for the analog subblock circuits.

## 10.5.3.1 Analog-to-Digital (A/D) Machine

The A/D machine performs the analog-to-digital conversion. The resolution is program selectable to be either 8- or 10- or 12 bits. The A/D machine uses a successive approximation architecture. It functions by comparing the sampled and stored analog voltage with a series of binary coded discrete voltages.

By following a binary search algorithm, the A/D machine identifies the discrete voltage that is nearest to the sampled and stored voltage.

Only analog input signals within the potential range of VRL\_0/1 to VRH\_0/1 (A/D reference potentials) will result in a non-railed digital output code.

## 10.5.3.2 Introduction of the Programmer's Model

The ADC\_LBA provides a programmer's model that uses a system memory list-based architecture for definition of the conversion command sequence and conversion result handling.

The Command Sequence List (CSL) and Result Value List (RVL) are implemented in double buffered manner and the buffer mode is user selectable for each list (bits CSL\_BMOD, RVL\_BMOD). The 32-bit wide conversion command is double buffered and the currently active command is visible in the ADC register map at ADCCMD register space.

| TSEG22 | TSEG21 | TSEG20 | Time Segment 2                  |  |  |

|--------|--------|--------|---------------------------------|--|--|

| 0      | 0      | 0      | 1 Tq clock cycle <sup>(1)</sup> |  |  |

| 0      | 0      | 1      | 2 Tq clock cycles               |  |  |

| :      | :      | :      | :                               |  |  |

| 1      | 1      | 0      | 7 Tq clock cycles               |  |  |

| 1      | 1      | 1      | 8 Tq clock cycles               |  |  |

Table 11-8. Time Segment 2 Values

1. This setting is not valid. Please refer to Table 11-36 for valid settings.

Table 11-9. Time Segment 1 Values

| TSEG13 | TSEG12 | TSEG11 | TSEG10 | Time segment 1                  |

|--------|--------|--------|--------|---------------------------------|

| 0      | 0      | 0      | 0      | 1 Tq clock cycle <sup>(1)</sup> |

| 0      | 0      | 0      | 1      | 2 Tq clock cycles <sup>1</sup>  |

| 0      | 0      | 1      | 0      | 3 Tq clock cycles <sup>1</sup>  |

| 0      | 0      | 1      | 1      | 4 Tq clock cycles               |

| :      | :      | :      | :      | :                               |

| 1      | 1      | 1      | 0      | 15 Tq clock cycles              |

| 1      | 1      | 1      | 1      | 16 Tq clock cycles              |

1. This setting is not valid. Please refer to Table 11-36 for valid settings.

The bit time is determined by the oscillator frequency, the baud rate prescaler, and the number of time quanta (Tq) clock cycles per bit (as shown in Table 11-8 and Table 11-9).

Eqn. 11-1

# Bit Time= $\frac{(Prescaler value)}{f_{CANCLK}} \bullet (1 + TimeSegment1 + TimeSegment2)$

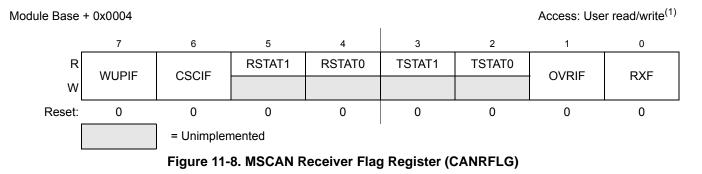

## 11.3.2.5 MSCAN Receiver Flag Register (CANRFLG)

A flag can be cleared only by software (writing a 1 to the corresponding bit position) when the condition which caused the setting is no longer valid. Every flag has an associated interrupt enable bit in the CANRIER register.

#### Chapter 12 Serial Peripheral Interface (S12SPIV5)

The main element of the SPI system is the SPI data register. The n-bit<sup>1</sup> data register in the master and the n-bit<sup>1</sup> data register in the slave are linked by the MOSI and MISO pins to form a distributed 2n-bit<sup>1</sup> register. When a data transfer operation is performed, this 2n-bit<sup>1</sup> register is serially shifted n<sup>1</sup> bit positions by the S-clock from the master, so data is exchanged between the master and the slave. Data written to the master SPI data register becomes the output data for the slave, and data read from the master SPI data register a transfer operation is the input data from the slave.

A read of SPISR with SPTEF = 1 followed by a write to SPIDR puts data into the transmit data register. When a transfer is complete and SPIF is cleared, received data is moved into the receive data register. This data register acts as the SPI receive data register for reads and as the SPI transmit data register for writes. A common SPI data register address is shared for reading data from the read data buffer and for writing data to the transmit data register.

The clock phase control bit (CPHA) and a clock polarity control bit (CPOL) in the SPI control register 1 (SPICR1) select one of four possible clock formats to be used by the SPI system. The CPOL bit simply selects a non-inverted or inverted clock. The CPHA bit is used to accommodate two fundamentally different protocols by sampling data on odd numbered SCK edges or on even numbered SCK edges (see Section 12.4.3, "Transmission Formats").

The SPI can be configured to operate as a master or as a slave. When the MSTR bit in SPI control register1 is set, master mode is selected, when the MSTR bit is clear, slave mode is selected.

## NOTE

A change of CPOL or MSTR bit while there is a received byte pending in the receive shift register will destroy the received byte and must be avoided.

## 12.4.1 Master Mode

The SPI operates in master mode when the MSTR bit is set. Only a master SPI module can initiate transmissions. A transmission begins by writing to the master SPI data register. If the shift register is empty, data immediately transfers to the shift register. Data begins shifting out on the MOSI pin under the control of the serial clock.

Serial clock

The SPR2, SPR1, and SPR0 baud rate selection bits, in conjunction with the SPPR2, SPPR1, and SPPR0 baud rate preselection bits in the SPI baud rate register, control the baud rate generator and determine the speed of the transmission. The SCK pin is the SPI clock output. Through the SCK pin, the baud rate generator of the master controls the shift register of the slave peripheral.

• MOSI, MISO pin

In master mode, the function of the serial data output pin (MOSI) and the serial data input pin (MISO) is determined by the SPC0 and BIDIROE control bits.

• <u>SS</u> pin

If MODFEN and SSOE are set, the  $\overline{SS}$  pin is configured as slave select output. The  $\overline{SS}$  output becomes low during each transmission and is high when the SPI is in idle state.

If MODFEN is set and SSOE is cleared, the  $\overline{SS}$  pin is configured as input for detecting mode fault error. If the  $\overline{SS}$  input becomes low this indicates a mode fault error where another master tries to 1. n depends on the selected transfer width, please refer to Section 12.3.2.2, "SPI Control Register 2 (SPICR2)

#### Chapter 15 Serial Communication Interface (S12SCIV6)

| Field   | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |  |  |  |

|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|

| 3<br>OR | <ul> <li>Overrun Flag — OR is set when software fails to read the SCI data register before the receive shift register receives the next frame. The OR bit is set immediately after the stop bit has been completely received for the second frame. The data in the shift register is lost, but the data already in the SCI data registers is not affected. Clear OR by reading SCI status register 1 (SCISR1) with OR set and then reading SCI data register low (SCIDRL).</li> <li>0 No overrun</li> <li>1 Overrun</li> <li>Note: OR flag may read back as set when RDRF flag is clear. This may happen if the following sequence of events occurs:</li> </ul> |  |  |  |  |  |  |  |  |

|         | <ol> <li>After the first frame is received, read status register SCISR1 (returns RDRF set and OR flag clea</li> <li>Receive second frame without reading the first frame in the data register (the second frame is no received and OR flag is set);</li> <li>Read data register SCIDRL (returns first frame and clears RDRF flag in the status register);</li> <li>Read status register SCISR1 (returns RDRF clear and OR set).</li> <li>Event 3 may be at exactly the same time as event 2 or any time after. When this happens, a dummy SCIDRL read following event 4 will be required to clear the OR flag if further frames are to be received</li> </ol>   |  |  |  |  |  |  |  |  |

| 2<br>NF | <ul> <li>Noise Flag — NF is set when the SCI detects noise on the receiver input. NF bit is set during the same cycle as the RDRF flag but does not get set in the case of an overrun. Clear NF by reading SCI status register 1(SCISR1), and then reading SCI data register low (SCIDRL).</li> <li>0 No noise</li> <li>1 Noise</li> </ul>                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |  |  |  |

| 1<br>FE | <ul> <li>Framing Error Flag — FE is set when a logic 0 is accepted as the stop bit. FE bit is set during the same cycle as the RDRF flag but does not get set in the case of an overrun. FE inhibits further data reception until it is cleared. Clear FE by reading SCI status register 1 (SCISR1) with FE set and then reading the SCI data register low (SCIDRL).</li> <li>0 No framing error</li> <li>1 Framing error</li> </ul>                                                                                                                                                                                                                            |  |  |  |  |  |  |  |  |

| 0<br>PF | <ul> <li>Parity Error Flag — PF is set when the parity enable bit (PE) is set and the parity of the received data does not match the parity type bit (PT). PF bit is set during the same cycle as the RDRF flag but does not get set in the case of an overrun. Clear PF by reading SCI status register 1 (SCISR1), and then reading SCI data register low (SCIDRL).</li> <li>0 No parity error</li> <li>1 Parity error</li> </ul>                                                                                                                                                                                                                              |  |  |  |  |  |  |  |  |

### Table 15-11. SCISR1 Field Descriptions (continued)

Chapter 16 Motor Controller (MC10B8CV1)

# 16.2 External Signal Description

The motor controller is associated with 16 pins. Table 16-2 lists the relationship between the PWM channels and signal pins as well as PWM channel pair (motor number), coils, and nodes they are supposed to drive if all channels are set to dual full H-bridge configuration.

| Pin Name | PWM Channel | PWM Channel Pair <sup>(1)</sup> | Coil | Node  |

|----------|-------------|---------------------------------|------|-------|

| MOCOM    | 0           | 0                               | 0    | Minus |

| M0C0P    |             |                                 |      | Plus  |

| M0C1M    | 1           |                                 | 1    | Minus |

| M0C1P    |             |                                 |      | Plus  |

| M1C0M    | 2           | 1                               | 0    | Minus |

| M1C0P    |             |                                 |      | Plus  |

| M1C1M    | 3           |                                 | 1    | Minus |

| M1C1P    |             |                                 |      | Plus  |

| M2C0M    | 4           | 2                               | 0    | Minus |

| M2C0P    |             |                                 |      | Plus  |

| M2C1M    | 5           |                                 | 1    | Minus |

| M2C1P    |             |                                 |      | Plus  |

| M3C0M    | 6           | 3                               | 0    | Minus |

| M3C0P    |             |                                 |      | Plus  |

| M3C1M    | 7           |                                 | 1    | Minus |

| M3C1P    |             |                                 |      | Plus  |

Table 16-2. PWM Channel and Pin Assignment

1. A PWM Channel Pair always consists of PWM channel x and PWM channel x+1 ( $x = 2 \cdot n$ ). The term "PWM Channel Pair" is equivalent to the term "Motor". E.g. Channel Pair 0 is equivalent to Motor 0

# 16.2.1 M0C0M/M0C0P/M0C1M/M0C1P — PWM Output Pins for Motor 0

High current PWM output pins that can be used for motor drive. These pins interface to the coils of motor 0. PWM output on M0C0M results in a positive current flow through coil 0 when M0C0P is driven to a logic high state. PWM output on M0C1M results in a positive current flow through coil 1 when M0C1P is driven to a logic high state.

# 16.2.2 M1C0M/M1C0P/M1C1M/M1C1P — PWM Output Pins for Motor 1

High current PWM output pins that can be used for motor drive. These pins interface to the coils of motor 1. PWM output on M1C0M results in a positive current flow through coil 0 when M1C0P is driven to a logic high state. PWM output on M1C1M results in a positive current flow through coil 1 when M1C1P is driven to a logic high state.

# 16.2.3 M2C0M/M2C0P/M2C1M/M2C1P — PWM Output Pins for Motor 2

High current PWM output pins that can be used for motor drive. These pins interface to the coils of motor 2. PWM output on M2C0M results in a positive current flow through coil 0 when M2C0P is driven

## 21.3.2.9.1 P-Flash Protection Restrictions

In Normal Single Chip Mode the general guideline is that P-Flash protection can only be added and not removed. Table 21-23 specifies all valid transitions between P-Flash protection scenarios. Any attempt to write an invalid scenario to the FPROT register will be ignored. The contents of the FPROT register reflect the active protection scenario. See the FPHS and FPLS bit descriptions for additional restrictions.

| From                   | To Protection Scenario <sup>(1)</sup> |   |   |   |   |   |   |   |  |  |  |

|------------------------|---------------------------------------|---|---|---|---|---|---|---|--|--|--|

| Protection<br>Scenario | 0                                     | 1 | 2 | 3 | 4 | 5 | 6 | 7 |  |  |  |

| 0                      | Х                                     | Х | Х | Х |   |   |   |   |  |  |  |

| 1                      |                                       | Х |   | Х |   |   |   |   |  |  |  |

| 2                      |                                       |   | Х | Х |   |   |   |   |  |  |  |

| 3                      |                                       |   |   | Х |   |   |   |   |  |  |  |

| 4                      |                                       |   |   | Х | Х |   |   |   |  |  |  |

| 5                      |                                       |   | Х | Х | Х | Х |   |   |  |  |  |

| 6                      |                                       | Х |   | Х | Х |   | х |   |  |  |  |

| 7                      | Х                                     | Х | Х | Х | Х | Х | Х | Х |  |  |  |

Table 21-23. P-Flash Protection Scenario Transitions

1. Allowed transitions marked with X, see Figure 21-14 for a definition of the scenarios.

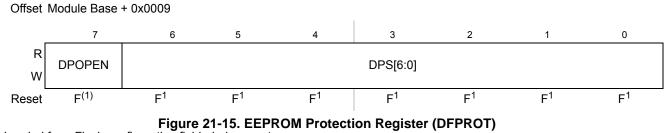

## 21.3.2.10 EEPROM Protection Register (DFPROT)

The DFPROT register defines which EEPROM sectors are protected against program and erase operations.

1. Loaded from Flash configuration field, during reset sequence.

The (unreserved) bits of the DFPROT register are writable in Normal Single Chip Mode with the restriction that protection can be added but not removed. Writes in Normal Single Chip Mode must increase the DPS value and the DPOPEN bit can only be written from 1 (protection disabled) to 0 (protection enabled). If the DPOPEN bit is set, the state of the DPS bits is irrelevant.All DPOPEN/DPS bit registers are writable without restriction in Special Single Chip Mode.

During the reset sequence, fields DPOPEN and DPS of the DFPROT register are loaded with the contents of the EEPROM protection byte in the Flash configuration field at global address 0xFF\_FE0D located in

Chapter 21 128 KB Flash Module (S12ZFTMRZ128K4KV2)

## 21.4.7.3 Erase Verify P-Flash Section Command

The Erase Verify P-Flash Section command will verify that a section of code in the P-Flash memory is erased. The Erase Verify P-Flash Section command defines the starting point of the code to be verified and the number of phrases.

| Register | FCCOB Parameters                                         |                                              |  |  |  |  |  |

|----------|----------------------------------------------------------|----------------------------------------------|--|--|--|--|--|

| FCCOB0   | 0x03                                                     | Global address [23:16] of<br>a P-Flash block |  |  |  |  |  |

| FCCOB1   | Global address [15:0] of the first phrase to be verified |                                              |  |  |  |  |  |

| FCCOB2   | Number of phrases to be verified                         |                                              |  |  |  |  |  |

Table 21-37. Erase Verify P-Flash Section Command FCCOB Requirements

Upon clearing CCIF to launch the Erase Verify P-Flash Section command, the Memory Controller will verify the selected section of Flash memory is erased. The CCIF flag will set after the Erase Verify P-Flash Section operation has completed. If the section is not erased, it means blank check failed, both MGSTAT bits will be set.

| Register | Error Bit | Error Condition                                                                                  |  |  |  |

|----------|-----------|--------------------------------------------------------------------------------------------------|--|--|--|

|          |           | Set if CCOBIX[2:0] != 010 at command launch                                                      |  |  |  |

|          |           | Set if command not available in current mode (see Table 21-29)                                   |  |  |  |

|          | ACCERR    | Set if an invalid global address [23:0] is supplied see Table 21-3)                              |  |  |  |

|          |           | Set if a misaligned phrase address is supplied (global address [2:0] != 000)                     |  |  |  |

| FSTAT    |           | Set if the requested section crosses a the P-Flash address boundary                              |  |  |  |

|          | FPVIOL    | None                                                                                             |  |  |  |

|          | MGSTAT1   | Set if any errors have been encountered during the read or if blank check failed.                |  |  |  |

|          | MGSTAT0   | Set if any non-correctable errors have been encountered during the read or i blank check failed. |  |  |  |

Table 21-38. Erase Verify P-Flash Section Command Error Handling

## 21.4.7.4 Read Once Command

The Read Once command provides read access to a reserved 64 byte field (8 phrases) located in the nonvolatile information register of P-Flash. The Read Once field is programmed using the Program Once command described in Section 21.4.7.6. The Read Once command must not be executed from the Flash block containing the Program Once reserved field to avoid code runaway.

| Register | FCCOB Parameters                         |              |  |  |  |  |  |  |

|----------|------------------------------------------|--------------|--|--|--|--|--|--|

| FCCOB0   | 0x04                                     | Not Required |  |  |  |  |  |  |

| FCCOB1   | Read Once phrase index (0x0000 - 0x0007) |              |  |  |  |  |  |  |

| FCCOB2   | Read Once word 0 value                   |              |  |  |  |  |  |  |

Appendix K Electrical Characteristics for the Oscillator (OSCLCPcr)

## 0x03C0-0x03CF SRAM ECC Generator(SRAM\_ECC)

| Address           | Name     |          | Bit 7         | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|-------------------|----------|----------|---------------|-------|-------|-------|-------|-------|-------|-------|

| 0x03C3-<br>0x03C6 | Reserved | R<br>W   | 0             | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

| 0x03C7            | ECCDPTRH | R<br>W   | DPTR[23:16]   |       |       |       |       |       |       |       |

| 0x03C8            | ECCDPTRM | R<br>W   | DPTR[15:8]    |       |       |       |       |       |       |       |

| 0x03C9            | ECCDPTRL | R<br>W   | DPTR[7:1]     |       |       |       |       |       |       |       |

| 0x03CA-<br>0x3CB  | Reserved | R<br>W   | 0             | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

| 0x03CC            | ECCDDH   | R<br>W   | DDATA[15:8]   |       |       |       |       |       |       |       |

| 0x03CD            | ECCDDL   | R<br>W   | DDATA[7:0]    |       |       |       |       |       |       |       |

| 0x03CE            | ECCDE    | R<br>W   | 0 0 DECC[5:0] |       |       |       |       |       |       |       |

| 0x03CF            | ECCDCMD  | R<br>W E | CCDRR         | 0     | 0     | 0     | 0     | 0     | ECCDW | ECCDR |

#### 0x03D0–0x03FF Reserved

| Address                   | Name     |   | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|---------------------------|----------|---|-------|-------|-------|-------|-------|-------|-------|-------|

| 0x03D0-<br>0x03FF Reserve | Reserved | R | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

|                           | Reserved | W |       |       |       |       |       |       |       |       |

## 0x0400–0x042F Timer Module (TIM1)

| Address | Name      |        | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|---------|-----------|--------|-------|-------|-------|-------|-------|-------|-------|-------|

| 0x0400  | TIM1TIOS  | R<br>W | IOS7  | IOS6  | IOS5  | IOS4  | IOS3  | IOS2  | IOS1  | IOS0  |

| 0.0401  |           | R      | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

| 0x0401  | TIM1CFORC | W      | FOC7  | FOC6  | FOC5  | FOC4  | FOC3  | FOC2  | FOC1  | FOC0  |

| 0x0402  | TIM10C7M  | R<br>W | OC7M7 | OC7M6 | OC7M5 | OC7M4 | OC7M3 | OC7M2 | OC7M1 | OC7M0 |

| 0x0403  | TIM10C7D  | R<br>W | OC7D7 | OC7D6 | OC7D5 | OC7D4 | OC7D3 | OC7D2 | OC7D1 | OC7D0 |

Appendix P Detailed Register Address Map

## 0x05C0–0x05EF Timer Module (TIM0)

| 0x05ED | Reserved  | R<br>W |       |       |       |       |       |       |       |       |

|--------|-----------|--------|-------|-------|-------|-------|-------|-------|-------|-------|

| 0x05EE | TIM0PTPSR | R<br>W | PTPS7 | PTPS6 | PTPS5 | PTPS4 | PTPS3 | PTPS2 | PTPS1 | PTPS0 |

| 0x05EF | Reserved  | R<br>W |       |       |       |       |       |       |       |       |

## 0x05F0–0x05FF Reserved

| Address | Name     |   | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|---------|----------|---|-------|-------|-------|-------|-------|-------|-------|-------|

| 0x05F0- | Reserved | R | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

| 0x05FF  |          | W |       |       |       |       |       |       |       |       |

## 0x0600–0x063F Analog to Digital Converter (ADC)

| Address | Name             |        | Bit 7        | Bit 6        | Bit 5         | Bit 4    | Bit 3    | Bit 2                  | Bit 1    | Bit 0 |  |

|---------|------------------|--------|--------------|--------------|---------------|----------|----------|------------------------|----------|-------|--|

| 0x0600  | ADC0CTL_0        | R<br>W | ADC_EN       | ADC_SR       | FRZ_MOD       | SWAI     | ACC_C    | FG[1:0] STR_SEQA MOD_C |          |       |  |

| 0x0601  | ADC0CTL_1        | R<br>W | CSL_BMOD     | RVL_BMOD     | SMOD_ACC      | AUT_RSTA | 0        | 0                      | 0        | 0     |  |

| 0x0602  | ADC0STS          | R<br>W | CSL_SEL      | RVL_SEL      | DBECC_ER<br>R | Reserved | READY    | 0                      | 0        | 0     |  |

| 0x0603  | ADC0TIM          | R<br>W | 0            | 0 PRS[6:0]   |               |          |          |                        |          |       |  |

| 0x0604  | ADC0FMT          | R<br>W | DJM          | 0            | 0             | 0        | 0        | SRES[2:0]              |          |       |  |

| 0x0605  | ADC0FLWCTL       | R<br>W | SEQA         | TRIG         | RSTA          | LDOK     | 0        | 0                      | 0        | 0     |  |

| 0x0606  | ADC0EIE          | R<br>W | IA_EIE       | CMD_EIE      | EOL_EIE       | Reserved | TRIG_EIE | RSTAR_EIE              | LDOK_EIE | 0     |  |

| 0x0607  | ADC0IE           | R<br>W | SEQAD_I<br>E | CONIF_OIE    | Reserved      | 0        | 0        | 0                      | 0        | 0     |  |

| 0x0608  | ADC0EiF          | R<br>W | IA_EIF       | CMD_EIF      | EOL_EIF       | Reserved | TRIG_EIF | RSTAR_EIF              | LDOK_EIF | 0     |  |

| 0x0609  | ADC0IF           | R<br>W | SEQAD_IF     | CONIF_OIF    | Reserved      | 0        | 0        | 0                      | 0        | 0     |  |

| 0x060A  | ADC0CO-<br>NIE_0 | R<br>W |              | CON_IE[15:8] |               |          |          |                        |          |       |  |