Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Active                                                                           |

| Core Processor             | R8C                                                                              |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 20MHz                                                                            |

| Connectivity               | LINbus, SIO, UART/USART                                                          |

| Peripherals                | POR, PWM, Voltage Detect, WDT                                                    |

| Number of I/O              | 25                                                                               |

| Program Memory Size        | 8KB (8K x 8)                                                                     |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 1K x 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 2.2V ~ 5.5V                                                                      |

| Data Converters            | A/D 9x10b                                                                        |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -20°C ~ 85°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 32-LQFP                                                                          |

| Supplier Device Package    | 32-LQFP (7x7)                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/r5f212l2snfp-x6 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 1.1.2 Specifications

Tables 1.1 and 1.2 outlines the Specifications for R8C/2K Group and Tables 1.3 and 1.4 outlines the Specifications for R8C/2L Group.

Table 1.1 Specifications for R8C/2K Group (1)

| Item         | Function           | Specification                                                                              |

|--------------|--------------------|--------------------------------------------------------------------------------------------|

| CPU          | Central processing | R8C/Tiny series core                                                                       |

|              | unit               | Number of fundamental instructions: 89                                                     |

|              |                    | Minimum instruction execution time:                                                        |

|              |                    | 50 ns (f(XIN) = 20 MHz, VCC = 3.0 to 5.5 V)                                                |

|              |                    | 100 ns (f(XIN) = 10 MHz, VCC = 2.7 to 5.5 V)                                               |

|              |                    | 200 ns (f(XIN) = 5 MHz, VCC = 2.2 to 5.5 V)                                                |

|              |                    | Multiplier: 16 bits × 16 bits → 32 bits                                                    |

|              |                    | <ul> <li>Multiply-accumulate instruction: 16 bits x 16 bits + 32 bits → 32 bits</li> </ul> |

|              |                    | Operation mode: Single-chip mode (address space: 1 Mbyte)                                  |

| Memory       | ROM, RAM           | Refer to Table 1.5 Product List for R8C/2K Group.                                          |

| Power Supply | Voltage detection  | Power-on reset                                                                             |

| Voltage      | circuit            | Voltage detection 3                                                                        |

| Detection    |                    |                                                                                            |

| I/O Ports    | Programmable I/O   | Input-only: 3 pins                                                                         |

|              | ports              | CMOS I/O ports: 25, selectable pull-up resistor                                            |

|              |                    | High current drive ports: 8                                                                |

| Clock        | Clock generation   | 2 circuits: XIN clock oscillation circuit (with on-chip feedback resistor),                |

|              | circuits           | On-chip oscillator (high-speed, low-speed)                                                 |

|              |                    | (high-speed on-chip oscillator has a frequency adjustment function)                        |

|              |                    | Oscillation stop detection: XIN clock oscillation stop detection function                  |

|              |                    | • Frequency divider circuit: Dividing selectable 1, 2, 4, 8, and 16                        |

|              |                    | • Low power consumption modes:                                                             |

|              |                    | Standard operating mode (high-speed clock, high-speed on-chip oscillator,                  |

|              |                    | low-speed on-chip oscillator), wait mode, stop mode                                        |

| Interrupts   |                    | External: 4 sources, Internal: 15 sources, Software: 4 sources                             |

| monapio      |                    | Priority levels: 7 levels                                                                  |

| Watchdog Tim | er                 | 15 bits × 1 (with prescaler), reset start selectable                                       |

| Timer        | Timer RA           | 8 bits × 1 (with 8-bit prescaler)                                                          |

| 111101       |                    | Timer mode (period timer), pulse output mode (output level inverted every                  |

|              |                    | period), event counter mode, pulse width measurement mode, pulse period                    |

|              |                    | measurement mode                                                                           |

|              | Timer RB           | 8 bits x 1 (with 8-bit prescaler)                                                          |

|              |                    | Timer mode (period timer), programmable waveform generation mode (PWM                      |

|              |                    | output), programmable one-shot generation mode, programmable wait one-                     |

|              |                    | shot generation mode                                                                       |

|              | Timer RC           | 16 bits x 1 (with 4 capture/compare registers)                                             |

|              |                    | Timer mode (input capture function, output compare function), PWM mode                     |

|              |                    | (output 3 pins), PWM2 mode (PWM output pin)                                                |

|              | Timer RD           | 16 bits × 2 (with 4 capture/compare registers)                                             |

|              |                    | Timer mode (input capture function, output compare function), PWM mode                     |

|              |                    | (output 6 pins), reset synchronous PWM mode (output three-phase                            |

|              |                    | waveforms (6 pins), sawtooth wave modulation), complementary PWM mode                      |

|              |                    | (output three-phase waveforms (6 pins), triangular wave modulation), PWM3                  |

|              |                    | mode (PWM output 2 pins with fixed period)                                                 |

# 1.2 Product List

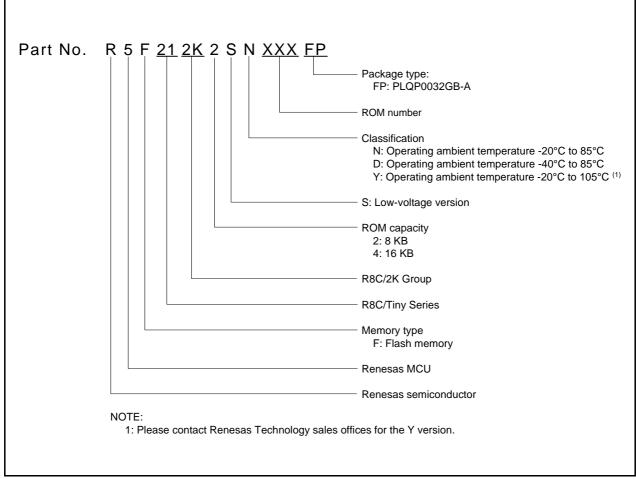

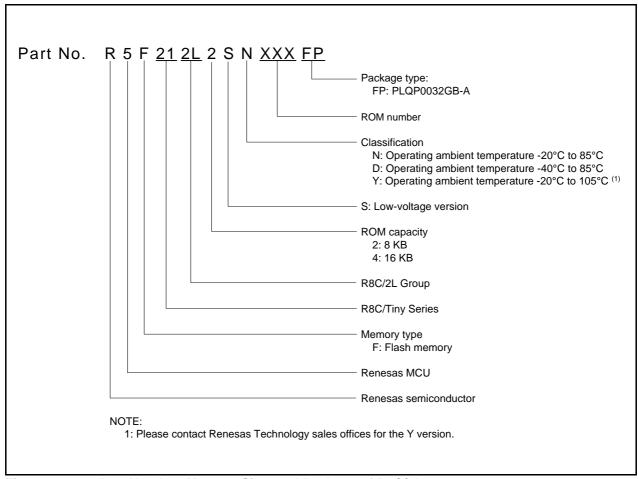

Table 1.5 lists the Product List for R8C/2K Group, Figure 1.1 shows a Part Number, Memory Size, and Package of R8C/2K Group, Table 1.6 lists the Product List for R8C/2L Group, and Figure 1.2 shows a Part Number, Memory Size, and Package of R8C/2L Group.

Table 1.5 Product List for R8C/2K Group

Current of Dec. 2007

| Part No.            | ROM Capacity | RAM Capacity | Package Type | Remarks                                    |

|---------------------|--------------|--------------|--------------|--------------------------------------------|

| R5F212K2SNFP        | 8 Kbytes     | 1 Kbyte      | PLQP0032GB-A | N version                                  |

| R5F212K4SNFP        | 16 Kbytes    | 1.5 Kbytes   | PLQP0032GB-A |                                            |

| R5F212K2SDFP        | 8 Kbytes     | 1 Kbyte      | PLQP0032GB-A | D version                                  |

| R5F212K4SDFP        | 16 Kbytes    | 1.5 Kbytes   | PLQP0032GB-A |                                            |

| R5F212K2SNXXXFP (D) | 8 Kbytes     | 1 Kbyte      | PLQP0032GB-A | N version                                  |

| R5F212K4SNXXXFP (D) | 16 Kbytes    | 1.5 Kbytes   | PLQP0032GB-A | Factory programming product <sup>(1)</sup> |

| R5F212K2SDXXXFP (D) | 8 Kbytes     | 1 Kbyte      | PLQP0032GB-A | D version                                  |

| R5F212K4SDXXXFP (D) | 16 Kbytes    | 1.5 Kbytes   | PLQP0032GB-A | Factory programming product <sup>(1)</sup> |

(D): Under development

NOTE:

1. The user ROM is programmed before shipment.

Figure 1.1 Part Number, Memory Size, and Package of R8C/2K Group

Table 1.6 Product List for R8C/2L Group

Current of Dec. 2007

| Part No.            | ROM Capacity |             | RAM        | Package Type  | Remarks                                          |

|---------------------|--------------|-------------|------------|---------------|--------------------------------------------------|

| - arriver           | Program ROM  | Data flash  | Capacity   | r donago rypo | rtomanto                                         |

| R5F212L2SNFP        | 8 Kbytes     | 1 Kbyte x 2 | 1 Kbyte    | PLQP0032GB-A  | N version                                        |

| R5F212L4SNFP        | 16 Kbytes    | 1 Kbyte x 2 | 1.5 Kbytes | PLQP0032GB-A  |                                                  |

| R5F212L2SDFP        | 8 Kbytes     | 1 Kbyte x 2 | 1 Kbyte    | PLQP0032GB-A  | D version                                        |

| R5F212L4SDFP        | 16 Kbytes    | 1 Kbyte x 2 | 1.5 Kbytes | PLQP0032GB-A  |                                                  |

| R5F212L2SNXXXFP (D) | 8 Kbytes     | 1 Kbyte x 2 | 1 Kbyte    | PLQP0032GB-A  | N version                                        |

| R5F212L4SNXXXFP (D) | 16 Kbytes    | 1 Kbyte × 2 | 1.5 Kbytes | PLQP0032GB-A  | Factory<br>programming<br>product <sup>(1)</sup> |

| R5F212L2SDXXXFP (D) | 8 Kbytes     | 1 Kbyte x 2 | 1 Kbyte    | PLQP0032GB-A  | D version                                        |

| R5F212L4SDXXXFP (D) | 16 Kbytes    | 1 Kbyte × 2 | 1.5 Kbytes | PLQP0032GB-A  | Factory<br>programming<br>product <sup>(1)</sup> |

(D): Under development

NOTE:

1. The user ROM is programmed before shipment.

Figure 1.2 Part Number, Memory Size, and Package of R8C/2L Group

Table 1.7 Pin Name Information by Pin Number

| Pin    | Control Pin | Port | I/O Pin Functions for of Peripheral Modules |                        |                  |               |  |

|--------|-------------|------|---------------------------------------------|------------------------|------------------|---------------|--|

| Number | Control Pin | Polt | Interrupt                                   | Timer                  | Serial Interface | A/D Converter |  |

| 1      | VREF        | P4_2 |                                             |                        |                  |               |  |

| 2      | MODE        |      |                                             |                        |                  |               |  |

| 3      | RESET       |      |                                             |                        |                  |               |  |

| 4      | XOUT        | P4_7 |                                             |                        |                  |               |  |

| 5      | VSS/AVSS    |      |                                             |                        |                  |               |  |

| 6      | XIN         | P4_6 |                                             |                        |                  |               |  |

| 7      | VCC/AVCC    |      |                                             |                        |                  |               |  |

| 8      |             | P3_3 | ĪNT3                                        | TRCCLK                 |                  |               |  |

| 9      |             | P2_7 |                                             | TRDIOD1                |                  |               |  |

| 10     |             | P2_6 |                                             | TRDIOC1                |                  |               |  |

| 11     |             | P2_5 |                                             | TRDIOB1                |                  |               |  |

| 12     |             | P2_4 |                                             | TRDIOA1                |                  |               |  |

| 13     |             | P2_3 |                                             | TRDIOD0                |                  |               |  |

| 14     |             | P2_1 |                                             | TRDIOB0                |                  |               |  |

| 15     |             | P2_2 |                                             | TRDIOC0                |                  |               |  |

| 16     |             | P2_0 |                                             | TRDIOA0/TRDCLK         |                  |               |  |

| 17     |             | P4_5 | ĪNT0                                        |                        |                  |               |  |

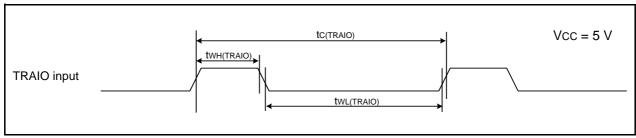

| 18     |             | P1_7 | INT1                                        | TRAIO                  |                  |               |  |

| 19     |             | P1_6 |                                             |                        | CLK0             |               |  |

| 20     |             | P1_5 | ( <del>INT1</del> ) <sup>(1)</sup>          | (TRAIO) <sup>(1)</sup> | RXD0             |               |  |

| 21     |             | P1_4 |                                             |                        | TXD0             |               |  |

| 22     |             | P1_3 | KI3                                         | TRBO                   |                  | AN11          |  |

| 23     |             | P1_2 | KI2                                         | TRCIOB                 |                  | AN10          |  |

| 24     |             | P1_1 | KI1                                         | TRCIOA/TRCTRG          |                  | AN9           |  |

| 25     |             | P1_0 | KI0                                         |                        |                  | AN8           |  |

| 26     |             | P3_4 |                                             | TRCIOC                 |                  |               |  |

| 27     |             | P3_5 |                                             | TRCIOD                 |                  |               |  |

| 28     |             | P0_5 |                                             |                        |                  | AN2           |  |

| 29     |             | P0_3 |                                             |                        | CLK2             | AN4           |  |

| 30     |             | P0_2 |                                             |                        | RXD2             | AN5           |  |

| 31     |             | P0_1 |                                             |                        | TXD2             | AN6           |  |

| 32     |             | P0_0 |                                             |                        |                  | AN7           |  |

1. Can be assigned to the pin in parentheses by a program.

### 2.1 Data Registers (R0, R1, R2, and R3)

R0 is a 16-bit register for transfer, arithmetic, and logic operations. The same applies to R1 to R3. R0 can be split into high-order bits (R0H) and low-order bits (R0L) to be used separately as 8-bit data registers. R1H and R1L are analogous to R0H and R0L. R2 can be combined with R0 and used as a 32-bit data register (R2R0). R3R1 is analogous to R2R0.

### 2.2 Address Registers (A0 and A1)

A0 is a 16-bit register for address register indirect addressing and address register relative addressing. It is also used for transfer, arithmetic, and logic operations. A1 is analogous to A0. A1 can be combined with A0 and as a 32bit address register (A1A0).

### 2.3 Frame Base Register (FB)

FB is a 16-bit register for FB relative addressing.

### 2.4 **Interrupt Table Register (INTB)**

INTB is a 20-bit register that indicates the start address of an interrupt vector table.

### 2.5 **Program Counter (PC)**

PC is 20 bits wide and indicates the address of the next instruction to be executed.

### 2.6 User Stack Pointer (USP) and Interrupt Stack Pointer (ISP)

The stack pointers (SP), USP, and ISP, are each 16 bits wide. The U flag of FLG is used to switch between USP and ISP.

### 2.7 Static Base Register (SB)

SB is a 16-bit register for SB relative addressing.

### 2.8 Flag Register (FLG)

FLG is an 11-bit register indicating the CPU state.

### 2.8.1 Carry Flag (C)

The C flag retains carry, borrow, or shift-out bits that have been generated by the arithmetic and logic unit.

### 2.8.2 Debug Flag (D)

The D flag is for debugging only. Set it to 0.

### 2.8.3 Zero Flag (Z)

The Z flag is set to 1 when an arithmetic operation results in 0; otherwise to 0.

### 2.8.4 Sign Flag (S)

The S flag is set to 1 when an arithmetic operation results in a negative value; otherwise to 0.

#### 2.8.5 Register Bank Select Flag (B)

Register bank 0 is selected when the B flag is 0. Register bank 1 is selected when this flag is set to 1.

#### 2.8.6 Overflow Flag (O)

The O flag is set to 1 when an operation results in an overflow; otherwise to 0.

# 2.8.7 Interrupt Enable Flag (I)

The I flag enables maskable interrupts.

Interrupt are disabled when the I flag is set to 0, and are enabled when the I flag is set to 1. The I flag is set to 0 when an interrupt request is acknowledged.

# 2.8.8 Stack Pointer Select Flag (U)

ISP is selected when the U flag is set to 0; USP is selected when the U flag is set to 1.

The U flag is set to 0 when a hardware interrupt request is acknowledged or the INT instruction of software interrupt numbers 0 to 31 is executed.

# 2.8.9 Processor Interrupt Priority Level (IPL)

IPL is 3 bits wide and assigns processor interrupt priority levels from level 0 to level 7. If a requested interrupt has higher priority than IPL, the interrupt is enabled.

# 2.8.10 Reserved Bit

If necessary, set to 0. When read, the content is undefined.

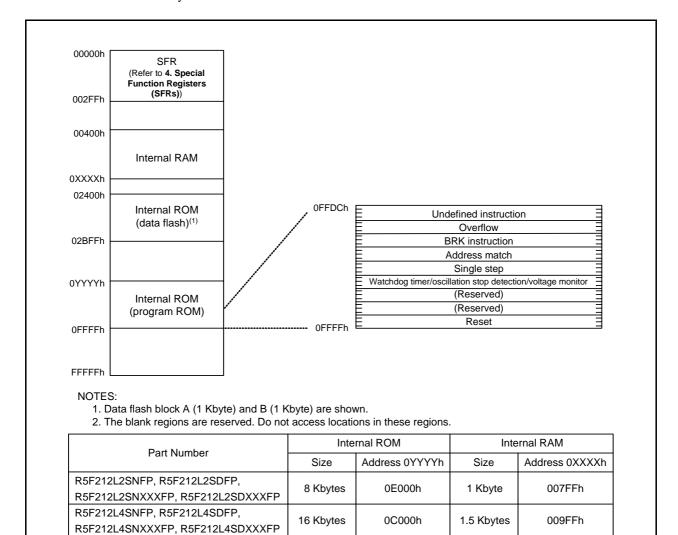

# 3.2 R8C/2L Group

Figure 3.2 is a Memory Map of R8C/2L Group. The R8C/2L Group has 1 Mbyte of address space from addresses 00000h to FFFFFh.

The internal ROM (program ROM) is allocated lower addresses, beginning with address 0FFFFh. For example, a 16-Kbyte internal ROM area is allocated addresses 0C000h to 0FFFFh.

The fixed interrupt vector table is allocated addresses 0FFDCh to 0FFFFh. They store the starting address of each interrupt routine.

The internal ROM (data flash) is allocated addresses 02400h to 02BFFh.

The internal RAM area is allocated higher addresses, beginning with address 00400h. For example, a 1.5-Kbyte internal RAM is allocated addresses 00400h to 009FFh. The internal RAM is used not only for storing data but also for calling subroutines and as stacks when interrupt requests are acknowledged.

Special function registers (SFRs) are allocated addresses 00000h to 002FFh. The peripheral function control registers are allocated here. All addresses within the SFR, which have nothing allocated are reserved for future use and cannot be accessed by users.

Figure 3.2 Memory Map of R8C/2L Group

SFR Information (2)<sup>(1)</sup> Table 4.2

| Address         | Register                                   | Symbol   | After reset |

|-----------------|--------------------------------------------|----------|-------------|

| 0040h           |                                            |          |             |

| 0041h           |                                            |          |             |

| 0042h           |                                            |          |             |

| 0043h           |                                            |          |             |

| 0044h           |                                            |          |             |

| 0045h           |                                            |          |             |

| 0046h           |                                            |          |             |

| 0047h           | Timer RC Interrupt Control Register        | TRCIC    | XXXXX000b   |

| 0048h           | Timer RD0 Interrupt Control Register       | TRD0IC   | XXXXX000b   |

| 0049h           | Timer RD1 Interrupt Control Register       | TRD1IC   | XXXXX000b   |

| 004Ah           |                                            |          |             |

| 004Bh           | UART2 Transmit Interrupt Control Register  | S2TIC    | XXXXX000b   |

| 004Ch           | UART2 Receive Interrupt Control Register   | S2RIC    | XXXXX000b   |

| 004Dh           | Key Input Interrupt Control Register       | KUPIC    | XXXXX000b   |

| 004Eh           | A/D Conversion Interrupt Control Register  | ADIC     | XXXXX000b   |

| 004Eh           | 77D CONVERSION INTERPRETATION REGISTER     | 7 IBIO   | 7000000000  |

| 0050h           |                                            | +        |             |

| 0050H           | UART0 Transmit Interrupt Control Register  | SOTIC    | XXXXX000b   |

| 0051h           | UARTO Transmit interrupt Control Register  | SORIC    | XXXXX000b   |

| 0052H           | Oractio receive interrupt Control register | SUNIC    | AAAAA000D   |

| 0053h           |                                            |          |             |

| 0055h           |                                            |          |             |

| 0056h           | Timor PA Interrupt Control Pogister        | TRAIC    | XXXXX000b   |

|                 | Timer RA Interrupt Control Register        | TRAIC    | AAAAAUUD    |

| 0057h           | Times DD Intervent Control Degister        | TDDIO    | VVVVVOCCE   |

| 0058h           | Timer RB Interrupt Control Register        | TRBIC    | XXXXX000b   |

| 0059h           | INT1 Interrupt Control Register            | INT1IC   | XX00X000b   |

| 005Ah           | INT3 Interrupt Control Register            | INT3IC   | XX00X000b   |

| 005Bh           |                                            |          |             |

| 005Ch           |                                            |          |             |

| 005Dh           | INT0 Interrupt Control Register            | INT0IC   | XX00X000b   |

| 005Eh           |                                            |          |             |

| 005Fh           |                                            |          |             |

| 0060h           |                                            |          |             |

| 0061h           |                                            |          |             |

| 0062h           |                                            |          |             |

| 0063h           |                                            |          |             |

| 0064h           |                                            |          |             |

| 0065h           |                                            |          |             |

| 0066h           |                                            |          |             |

| 0067h           |                                            |          |             |

| 0068h           |                                            |          |             |

| 0069h           |                                            |          |             |

| 006Ah           |                                            | 1        |             |

| 006Bh           |                                            | 1        |             |

| 006Ch           |                                            | 1        |             |

| 006Dh           |                                            |          |             |

| 006Eh           |                                            | 1        |             |

| 006Fh           |                                            |          |             |

| 0070h           |                                            | <u> </u> | <u> </u>    |

| 0071h           |                                            | <u> </u> | <u> </u>    |

| 0071h           |                                            | +        |             |

| 0072h           |                                            | +        |             |

| 0074h           |                                            | -        |             |

| 0075h           |                                            |          | -           |

| 0075h           |                                            | +        | +           |

| 0077h           |                                            | +        | +           |

| 007711<br>0078h |                                            |          |             |

| 0078h           |                                            |          |             |

| 0079h           |                                            |          |             |

|                 |                                            |          |             |

| 007Bh           |                                            |          |             |

| 007Ch           |                                            |          |             |

| 007Dh           |                                            |          |             |

| 007Eh           |                                            |          |             |

| 007Fh           | 1                                          | 1        | 1           |

X: Undefined

NOTE:

1. The blank regions are reserved. Do not access locations in these regions.

SFR Information (3)<sup>(1)</sup> Table 4.3

| Address                                                                                                                                               | Register                                                                            | Symbol       | After reset                          |

|-------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|--------------|--------------------------------------|

| 0080h                                                                                                                                                 | rtegister                                                                           | Gymbol       | Aitel Teset                          |

| 0081h                                                                                                                                                 |                                                                                     |              |                                      |

| 0081H                                                                                                                                                 |                                                                                     |              |                                      |

| 0082h                                                                                                                                                 |                                                                                     |              |                                      |

| 0084h                                                                                                                                                 |                                                                                     |              |                                      |

| 0085h                                                                                                                                                 |                                                                                     |              |                                      |

|                                                                                                                                                       |                                                                                     |              |                                      |

| 0086h                                                                                                                                                 |                                                                                     |              |                                      |

| 0087h<br>0088h                                                                                                                                        |                                                                                     |              |                                      |

|                                                                                                                                                       |                                                                                     |              |                                      |

| 0089h                                                                                                                                                 |                                                                                     |              |                                      |

| 008Ah                                                                                                                                                 |                                                                                     |              |                                      |

| 008Bh                                                                                                                                                 |                                                                                     |              |                                      |

| 008Ch                                                                                                                                                 |                                                                                     |              |                                      |

| 008Dh                                                                                                                                                 |                                                                                     |              |                                      |

| 008Eh                                                                                                                                                 |                                                                                     |              |                                      |

| 008Fh                                                                                                                                                 |                                                                                     |              |                                      |

| 0090h                                                                                                                                                 |                                                                                     |              |                                      |

| 0091h                                                                                                                                                 |                                                                                     |              |                                      |

| 0092h                                                                                                                                                 |                                                                                     |              |                                      |

| 0093h                                                                                                                                                 |                                                                                     |              |                                      |

| 0094h                                                                                                                                                 |                                                                                     |              |                                      |

| 0095h                                                                                                                                                 |                                                                                     |              |                                      |

| 0096h                                                                                                                                                 |                                                                                     |              |                                      |

| 0097h                                                                                                                                                 |                                                                                     |              |                                      |

| 0098h                                                                                                                                                 |                                                                                     |              |                                      |

| 0099h                                                                                                                                                 |                                                                                     |              |                                      |

| 009Ah                                                                                                                                                 |                                                                                     |              |                                      |

| 009Bh                                                                                                                                                 |                                                                                     |              |                                      |

| 009Ch                                                                                                                                                 |                                                                                     |              |                                      |

| 009Dh                                                                                                                                                 |                                                                                     |              |                                      |

| 009Eh                                                                                                                                                 |                                                                                     |              |                                      |

| 009Fh                                                                                                                                                 |                                                                                     |              |                                      |

| 00A0h                                                                                                                                                 | UART0 Transmit/Receive Mode Register                                                | U0MR         | 00h                                  |

| 00A1h                                                                                                                                                 | UART0 Bit Rate Register                                                             | U0BRG        | XXh                                  |

| 00A2h                                                                                                                                                 | UART0 Transmit Buffer Register                                                      | U0TB         | XXh                                  |

|                                                                                                                                                       |                                                                                     | 0010         | 70/01                                |

| 00A3h                                                                                                                                                 |                                                                                     | 0016         | XXh                                  |

| 00A3h<br>00A4h                                                                                                                                        | UART0 Transmit/Receive Control Register 0                                           | U0C0         | XXh<br>00001000b                     |

| 00A3h<br>00A4h                                                                                                                                        | UART0 Transmit/Receive Control Register 0 UART0 Transmit/Receive Control Register 1 |              | XXh<br>00001000b<br>00000010b        |

| 00A3h                                                                                                                                                 | UART0 Transmit/Receive Control Register 0 UART0 Transmit/Receive Control Register 1 | U0C0         | XXh<br>00001000b<br>00000010b<br>XXh |

| 00A3h<br>00A4h<br>00A5h<br>00A6h<br>00A7h                                                                                                             | UART0 Transmit/Receive Control Register 0                                           | U0C0<br>U0C1 | XXh<br>00001000b<br>00000010b        |

| 00A3h<br>00A4h<br>00A5h<br>00A6h<br>00A7h<br>00A8h                                                                                                    | UART0 Transmit/Receive Control Register 0 UART0 Transmit/Receive Control Register 1 | U0C0<br>U0C1 | XXh<br>00001000b<br>00000010b<br>XXh |

| 00A3h<br>00A4h<br>00A5h<br>00A6h<br>00A7h<br>00A8h<br>00A9h                                                                                           | UART0 Transmit/Receive Control Register 0 UART0 Transmit/Receive Control Register 1 | U0C0<br>U0C1 | XXh<br>00001000b<br>00000010b<br>XXh |

| 00A3h<br>00A4h<br>00A5h<br>00A6h<br>00A7h<br>00A8h<br>00A9h                                                                                           | UART0 Transmit/Receive Control Register 0 UART0 Transmit/Receive Control Register 1 | U0C0<br>U0C1 | XXh<br>00001000b<br>00000010b<br>XXh |

| 00A3h<br>00A4h<br>00A5h<br>00A6h<br>00A7h<br>00A8h<br>00A9h<br>00AAh                                                                                  | UART0 Transmit/Receive Control Register 0 UART0 Transmit/Receive Control Register 1 | U0C0<br>U0C1 | XXh<br>00001000b<br>00000010b<br>XXh |

| 00A3h<br>00A4h<br>00A5h<br>00A6h<br>00A7h<br>00A8h<br>00A9h<br>00AAh<br>00ABh                                                                         | UART0 Transmit/Receive Control Register 0 UART0 Transmit/Receive Control Register 1 | U0C0<br>U0C1 | XXh<br>00001000b<br>00000010b<br>XXh |

| 00A3h<br>00A4h<br>00A5h<br>00A6h<br>00A7h<br>00A8h<br>00A9h<br>00AAh                                                                                  | UART0 Transmit/Receive Control Register 0 UART0 Transmit/Receive Control Register 1 | U0C0<br>U0C1 | XXh<br>00001000b<br>00000010b<br>XXh |

| 00A3h<br>00A4h<br>00A5h<br>00A6h<br>00A7h<br>00A8h<br>00A9h<br>00AAh<br>00ABh<br>00ACh                                                                | UART0 Transmit/Receive Control Register 0 UART0 Transmit/Receive Control Register 1 | U0C0<br>U0C1 | XXh<br>00001000b<br>00000010b<br>XXh |

| 00A3h<br>00A4h<br>00A5h<br>00A6h<br>00A7h<br>00A8h<br>00A9h<br>00AAh<br>00ABh<br>00ACh<br>00ADh                                                       | UART0 Transmit/Receive Control Register 0 UART0 Transmit/Receive Control Register 1 | U0C0<br>U0C1 | XXh<br>00001000b<br>00000010b<br>XXh |

| 00A3h<br>00A4h<br>00A5h<br>00A6h<br>00A6h<br>00A7h<br>00A8h<br>00A9h<br>00AAh<br>00ABh<br>00ACh<br>00ADh                                              | UART0 Transmit/Receive Control Register 0 UART0 Transmit/Receive Control Register 1 | U0C0<br>U0C1 | XXh<br>00001000b<br>00000010b<br>XXh |

| 00A3h<br>00A4h<br>00A5h<br>00A6h<br>00A7h<br>00A8h<br>00A9h<br>00AAh<br>00ABh<br>00ACh<br>00ADh<br>00AEh<br>00AFh                                     | UART0 Transmit/Receive Control Register 0 UART0 Transmit/Receive Control Register 1 | U0C0<br>U0C1 | XXh<br>00001000b<br>00000010b<br>XXh |

| 00A3h<br>00A4h<br>00A5h<br>00A6h<br>00A7h<br>00A8h<br>00A9h<br>00AAh<br>00ABh<br>00ACh<br>00ADh<br>00AEh<br>00AEh                                     | UART0 Transmit/Receive Control Register 0 UART0 Transmit/Receive Control Register 1 | U0C0<br>U0C1 | XXh<br>00001000b<br>00000010b<br>XXh |

| 00A3h<br>00A4h<br>00A5h<br>00A6h<br>00A7h<br>00A8h<br>00A9h<br>00AAh<br>00ABh<br>00ACh<br>00ADh<br>00AEh<br>00AEh<br>00B1h                            | UART0 Transmit/Receive Control Register 0 UART0 Transmit/Receive Control Register 1 | U0C0<br>U0C1 | XXh<br>00001000b<br>00000010b<br>XXh |

| 00A3h<br>00A4h<br>00A5h<br>00A5h<br>00A6h<br>00A7h<br>00A8h<br>00A9h<br>00AAh<br>00ABh<br>00ACh<br>00ADh<br>00AFh<br>00B0h<br>00B1h<br>00B2h          | UART0 Transmit/Receive Control Register 0 UART0 Transmit/Receive Control Register 1 | U0C0<br>U0C1 | XXh<br>00001000b<br>00000010b<br>XXh |

| 00A3h<br>00A4h<br>00A5h<br>00A6h<br>00A7h<br>00A8h<br>00A9h<br>00AAh<br>00ACh<br>00ACh<br>00ACh<br>00AFh<br>00B1h<br>00B2h<br>00B3h                   | UART0 Transmit/Receive Control Register 0 UART0 Transmit/Receive Control Register 1 | U0C0<br>U0C1 | XXh<br>00001000b<br>00000010b<br>XXh |

| 00A3h<br>00A4h<br>00A5h<br>00A6h<br>00A6h<br>00A7h<br>00A8h<br>00A9h<br>00AAh<br>00ACh<br>00ACh<br>00ACh<br>00B1h<br>00B2h<br>00B2h<br>00B3h          | UART0 Transmit/Receive Control Register 0 UART0 Transmit/Receive Control Register 1 | U0C0<br>U0C1 | XXh<br>00001000b<br>00000010b<br>XXh |

| 00A3h 00A4h 00A5h 00A6h 00A6h 00A7h 00A8h 00A9h 00AAh 00ABh 00ACh 00ACh 00ACh 00AFh 00B6h 00B1h 00B2h 00B3h 00B4h 00B5h 00B6h                         | UART0 Transmit/Receive Control Register 0 UART0 Transmit/Receive Control Register 1 | U0C0<br>U0C1 | XXh<br>00001000b<br>00000010b<br>XXh |

| 00A3h 00A4h 00A5h 00A6h 00A7h 00A8h 00A9h 00AAh 00ABh 00ACh 00ACh 00ACh 00AEh 00B1h 00B2h 00B3h 00B4h 00B5h 00B6h 00B7h                               | UART0 Transmit/Receive Control Register 0 UART0 Transmit/Receive Control Register 1 | U0C0<br>U0C1 | XXh<br>00001000b<br>00000010b<br>XXh |

| 00A3h 00A4h 00A5h 00A5h 00A6h 00A7h 00A8h 00A9h 00AAh 00ABh 00ACh 00ACh 00ACh 00B1h 00B2h 00B3h 00B4h 00B5h 00B6h 00B7h 00B8h                         | UART0 Transmit/Receive Control Register 0 UART0 Transmit/Receive Control Register 1 | U0C0<br>U0C1 | XXh<br>00001000b<br>00000010b<br>XXh |

| 00A3h 00A4h 00A4h 00A5h 00A6h 00A7h 00A8h 00A9h 00AAh 00ABh 00ACh 00ACh 00ACh 00AFh 00B6h 00B1h 00B2h 00B3h 00B4h 00B5h 00B6h 00B7h 00B8h 00B9h       | UART0 Transmit/Receive Control Register 0 UART0 Transmit/Receive Control Register 1 | U0C0<br>U0C1 | XXh<br>00001000b<br>00000010b<br>XXh |

| 00A3h 00A4h 00A4h 00A5h 00A6h 00A7h 00A8h 00A9h 00AAh 00ACh 00ACh 00ACh 00ACh 00B1h 00B2h 00B3h 00B4h 00B5h 00B6h 00B7h 00B6h 00B7h 00B8h 00B9h       | UART0 Transmit/Receive Control Register 0 UART0 Transmit/Receive Control Register 1 | U0C0<br>U0C1 | XXh<br>00001000b<br>00000010b<br>XXh |

| 00A3h 00A4h 00A4h 00A5h 00A6h 00A7h 00A8h 00A9h 00AAh 00ABh 00ACh 00ACh 00ACh 00ACh 00B1h 00B2h 00B3h 00B4h 00B5h 00B6h 00B7h 00B8h 00B8h 00B8h       | UART0 Transmit/Receive Control Register 0 UART0 Transmit/Receive Control Register 1 | U0C0<br>U0C1 | XXh<br>00001000b<br>00000010b<br>XXh |

| 00A3h 00A4h 00A5h 00A6h 00A6h 00A7h 00A8h 00A9h 00AAh 00ABh 00ACh 00ACh 00ACh 00B1h 00B1h 00B3h 00B4h 00B5h 00B6h 00B7h 00B8h 00B8h 00BAh 00BBh       | UART0 Transmit/Receive Control Register 0 UART0 Transmit/Receive Control Register 1 | U0C0<br>U0C1 | XXh<br>00001000b<br>00000010b<br>XXh |

| 00A3h 00A4h 00A4h 00A5h 00A6h 00A7h 00A8h 00A9h 00AAh 00ABh 00ACh 00ACh 00ACh 00B1h 00B2h 00B3h 00B4h 00B5h 00B6h 00B7h 00B8h 00B9h 00BAh 00BAh 00BAh | UART0 Transmit/Receive Control Register 0 UART0 Transmit/Receive Control Register 1 | U0C0<br>U0C1 | XXh<br>00001000b<br>00000010b<br>XXh |

| 00A3h 00A4h 00A5h 00A6h 00A6h 00A7h 00A8h 00A9h 00AAh 00ABh 00ACh 00ACh 00ACh 00B1h 00B2h 00B3h 00B5h 00B6h 00B7h 00B8h 00B8h 00B8h 00B8h 00B8h       | UART0 Transmit/Receive Control Register 0 UART0 Transmit/Receive Control Register 1 | U0C0<br>U0C1 | XXh<br>00001000b<br>00000010b<br>XXh |

X: Undefined

NOTE:

1. The blank regions are reserved. Do not access locations in these regions.

**Recommended Operating Conditions** Table 5.2

| Symbol    | Parameter                             |                                                  | Conditions                                                                          |         | Standard |         | Unit |

|-----------|---------------------------------------|--------------------------------------------------|-------------------------------------------------------------------------------------|---------|----------|---------|------|

| Symbol    | '                                     | rafametei                                        | Conditions                                                                          | Min.    | Тур.     | Max.    | Oill |

| Vcc       | Supply voltage                        |                                                  |                                                                                     | 2.2     | -        | 5.5     | V    |

| AVcc      | Supply voltage                        |                                                  |                                                                                     | 2.7     | -        | 5.5     |      |

| Vss/AVss  | Supply voltage                        |                                                  |                                                                                     | -       | 0        | -       | V    |

| VIH       | Input "H" voltage                     |                                                  |                                                                                     | 0.8 Vcc | _        | Vcc     | V    |

| VIL       | Input "L" voltage                     |                                                  |                                                                                     | 0       | _        | 0.2 Vcc | V    |

| IOH(sum)  | Peak sum output<br>"H" current        | Sum of all pins IOH(peak)                        |                                                                                     | =       | =        | -160    | mA   |

| IOH(sum)  | Average sum output "H" current        | Sum of all pins IOH(avg)                         |                                                                                     | -       | _        | -80     | mA   |

| IOH(peak) | Peak output "H"                       | Except P2_0 to P2_7                              |                                                                                     | _       | _        | -10     | mA   |

|           | current                               | P2_0 to P2_7                                     |                                                                                     | -       | -        | -40     | mA   |

| IOH(avg)  | Average output                        | Except P2_0 to P2_7                              |                                                                                     | -       | -        | -5      | mA   |

|           | "H" current                           | P2_0 to P2_7                                     |                                                                                     | _       | =        | -20     | mA   |

| IOL(sum)  | Peak sum output<br>"L" currents       | Sum of all pins IOL(peak)                        |                                                                                     | -       | -        | 160     | mA   |

| IOL(sum)  | Average sum output "L" currents       | Sum of all pins IOL(avg)                         |                                                                                     | -       | -        | 80      | mA   |

| IOL(peak) | Peak output "L"                       | Except P2_0 to P2_7                              |                                                                                     | -       | -        | 10      | mA   |

|           | currents                              | P2_0 to P2_7                                     |                                                                                     | -       | =        | 40      | mA   |

| IOL(avg)  | Average output                        | Except P2_0 to P2_7                              |                                                                                     | -       | =        | 5       | mA   |

|           | "L" current                           | P2_0 to P2_7                                     |                                                                                     | -       | =        | 20      | mA   |

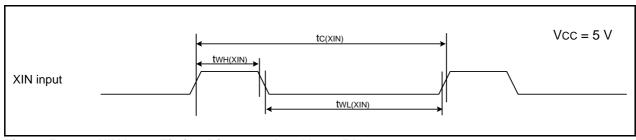

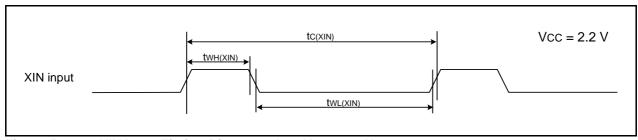

| f(XIN)    | XIN clock input oscillation frequency |                                                  | 3.0 V ≤ Vcc ≤ 5.5 V                                                                 | 0       | _        | 20      | MHz  |

|           | ·                                     |                                                  | 2.7 V ≤ Vcc < 3.0 V                                                                 | 0       | -        | 10      | MHz  |

|           |                                       |                                                  | 2.2 V ≤ Vcc < 2.7 V                                                                 | 0       | =        | 5       | MHz  |

| _         | System clock                          | OCD2 = 0                                         | 3.0 V ≤ Vcc ≤ 5.5 V                                                                 | 0       | =        | 20      | MHz  |

|           |                                       | XIN clock selected                               | 2.7 V ≤ Vcc < 3.0 V                                                                 | 0       | =        | 10      | MHz  |

|           |                                       |                                                  | 2.2 V ≤ Vcc < 2.7 V                                                                 | 0       | =        | 5       | MHz  |

|           |                                       | OCD2 = 1<br>On-chip oscillator clock<br>selected | FRA01 = 0<br>Low-speed on-chip<br>oscillator clock selected                         | -       | 125      | =       | kHz  |

|           |                                       | SSIGGE                                           | FRA01 = 1<br>High-speed on-chip<br>oscillator clock selected<br>3.0 V ≤ Vcc ≤ 5.5 V | _       | -        | 20      | MHz  |

|           |                                       |                                                  | FRA01 = 1<br>High-speed on-chip<br>oscillator clock selected<br>2.7 V ≤ Vcc ≤ 5.5 V | _       | -        | 10      | MHz  |

|           |                                       |                                                  | FRA01 = 1<br>High-speed on-chip<br>oscillator clock selected<br>2.2 V ≤ Vcc ≤ 5.5 V | _       | =        | 5       | MHz  |

Vcc = 2.2 to 5.5 V at T<sub>opr</sub> = -20 to 85°C (N version) / -40 to 85°C (D version), unless otherwise specified.

The average output current indicates the average value of current measured during 100 ms.

Table 5.4 Flash Memory (Program ROM) Electrical Characteristics

| Cymphal    | Dorometer                                                           | Conditions                 |          | Unit |                            |       |  |

|------------|---------------------------------------------------------------------|----------------------------|----------|------|----------------------------|-------|--|

| Symbol     | Parameter                                                           | Conditions                 | Min.     | Тур. | Max.                       | Unit  |  |

| _          | Program/erase endurance <sup>(2)</sup>                              | R8C/2K Group               | 100(3)   | -    | -                          | times |  |

|            |                                                                     | R8C/2L Group               | 1,000(3) | -    | -                          | times |  |

| -          | Byte program time                                                   |                            | ī        | 50   | 400                        | μS    |  |

| _          | Block erase time                                                    |                            | =        | 0.4  | 9                          | S     |  |

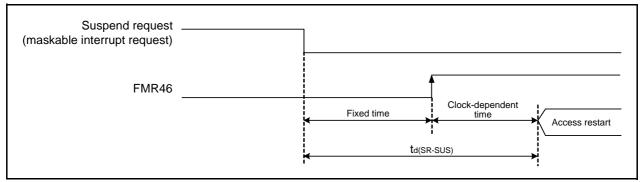

| td(SR-SUS) | Time delay from suspend request until suspend                       |                            | -        | _    | 97+CPU clock<br>× 6 cycles | μS    |  |

| _          | Interval from erase start/restart until following suspend request   |                            | 650      | _    | _                          | μS    |  |

| =          | Interval from program start/restart until following suspend request |                            | 0        | =    | -                          | ns    |  |

| _          | Time from suspend until program/erase restart                       |                            | -        | _    | 3+CPU clock<br>× 4 cycles  | μS    |  |

| _          | Program, erase voltage                                              |                            | 2.7      | -    | 5.5                        | V     |  |

| -          | Read voltage                                                        |                            | 2.2      | -    | 5.5                        | V     |  |

| _          | Program, erase temperature                                          |                            | 0        | -    | 60                         | °C    |  |

| -          | Data hold time <sup>(7)</sup>                                       | Ambient temperature = 55°C | 20       | =    | =                          | year  |  |

- NOTES:

1. Vcc = 2.7 to 5.5 V at Topr = 0 to 60°C, unless otherwise specified.

- 2. Definition of programming/erasure endurance

The programming and erasure endurance is defined on a per-block basis.

If the programming and erasure endurance is n (n = 100 or 10,000), each block can be erased n times. For example, if 1,024 1-byte writes are performed to block A, a 1 Kbyte block, and then the block is erased, the programming/erasure endurance still stands at one.

However, the same address must not be programmed more than once per erase operation (overwriting prohibited).

- 3. Endurance to guarantee all electrical characteristics after program and erase. (1 to Min. value can be guaranteed).

- 4. In a system that executes multiple programming operations, the actual erasure count can be reduced by writing to sequential addresses in turn so that as much of the block as possible is used up before performing an erase operation. For example, when programming groups of 16 bytes, the effective number of rewrites can be minimized by programming up to 128 groups before erasing them all in one operation. It is also advisable to retain data on the erase count of each block and limit the number of erase operations to a certain number.

- 5. If an error occurs during block erase, attempt to execute the clear status register command, then execute the block erase command at least three times until the erase error does not occur.

- 6. Customers desiring program/erase failure rate information should contact their Renesas technical support representative.

- 7. The data hold time includes time that the power supply is off or the clock is not supplied.

Table 5.5 Flash Memory (Data flash Block A, Block B) Electrical Characteristics(4)

| Symbol     | Parameter                                                           | Conditions                  |                    | Unit |                            |       |

|------------|---------------------------------------------------------------------|-----------------------------|--------------------|------|----------------------------|-------|

| Symbol     | Parameter                                                           | Conditions                  | Min.               | Тур. | Max.                       | Unit  |

| _          | Program/erase endurance <sup>(2)</sup>                              |                             | 10,000(3)          | -    | -                          | times |

| _          | Byte program time (program/erase endurance ≤ 1,000 times)           |                             | _                  | 50   | 400                        | μS    |

| _          | Byte program time (program/erase endurance > 1,000 times)           |                             | _                  | 65   | _                          | μS    |

| _          | Block erase time (program/erase endurance ≤ 1,000 times)            |                             | _                  | 0.2  | 9                          | S     |

| _          | Block erase time (program/erase endurance > 1,000 times)            |                             | _                  | 0.3  | -                          | S     |

| td(SR-SUS) | Time delay from suspend request until suspend                       |                             | =                  | -    | 97+CPU clock<br>× 6 cycles | μS    |

| _          | Interval from erase start/restart until following suspend request   |                             | 650                | -    | _                          | μS    |

| _          | Interval from program start/restart until following suspend request |                             | 0                  | -    | -                          | ns    |

| _          | Time from suspend until program/erase restart                       |                             | _                  | -    | 3+CPU clock<br>× 4 cycles  | μS    |

| -          | Program, erase voltage                                              |                             | 2.7                | _    | 5.5                        | V     |

| _          | Read voltage                                                        |                             | 2.2                | _    | 5.5                        | V     |

| =          | Program, erase temperature                                          |                             | -20 <sup>(8)</sup> | -    | 85                         | °C    |

| _          | Data hold time <sup>(9)</sup>                                       | Ambient temperature = 55 °C | 20                 | _    | -                          | year  |

- 1. Vcc = 2.7 to 5.5 V at Topr = -20 to 85°C (N version) / -40 to 85°C (D version), unless otherwise specified.

- 2. Definition of programming/erasure endurance

The programming and erasure endurance is defined on a per-block basis.

If the programming and erasure endurance is n (n = 100 or 10,000), each block can be erased n times. For example, if 1,024 1-byte writes are performed to block A, a 1 Kbyte block, and then the block is erased, the programming/erasure endurance

However, the same address must not be programmed more than once per erase operation (overwriting prohibited).

- Endurance to guarantee all electrical characteristics after program and erase. (1 to Min. value can be guaranteed).

- Standard of block A and block B when program and erase endurance exceeds 1,000 times. Byte program time to 1,000 times is the same as that in program ROM.

- 5. In a system that executes multiple programming operations, the actual erasure count can be reduced by writing to sequential addresses in turn so that as much of the block as possible is used up before performing an erase operation. For example, when programming groups of 16 bytes, the effective number of rewrites can be minimized by programming up to 128 groups before erasing them all in one operation. It is also advisable to retain data on the erase count of each block and limit the number of erase operations to a certain number.

- 6. If an error occurs during block erase, attempt to execute the clear status register command, then execute the block erase command at least three times until the erase error does not occur.

- 7. Customers desiring program/erase failure rate information should contact their Renesas technical support representative.

- 8. -40°C for D version.

- 9. The data hold time includes time that the power supply is off or the clock is not supplied.

Figure 5.2 Time delay until Suspend

Table 5.6 Voltage Detection 0 Circuit Electrical Characteristics

| Symbol  | Parameter                                                                    | Condition              |      | Unit |      |       |

|---------|------------------------------------------------------------------------------|------------------------|------|------|------|-------|

| Symbol  | Farameter                                                                    | Condition              | Min. | Тур. | Max. | Offic |

| Vdet0   | Voltage detection level                                                      |                        | 2.2  | 2.3  | 2.4  | V     |

| -       | Voltage detection circuit self power consumption                             | VCA25 = 1, Vcc = 5.0 V | -    | 0.9  | -    | μΑ    |

| td(E-A) | Waiting time until voltage detection circuit operation starts <sup>(2)</sup> |                        | =    | =    | 300  | μS    |

| Vccmin  | MCU operating voltage minimum value                                          |                        | 2.2  | =    | =    | V     |

- 1. The measurement condition is Vcc = 2.2 to 5.5 V and Topr = -20 to  $85^{\circ}C$  (N version) / -40 to  $85^{\circ}C$  (D version).

- 2. Necessary time until the voltage detection circuit operates when setting to 1 again after setting the VCA25 bit in the VCA2 register to 0.

Table 5.7 Voltage Detection 1 Circuit Electrical Characteristics

| Symbol   | Parameter                                                                    | Condition              |      | Unit |      |       |

|----------|------------------------------------------------------------------------------|------------------------|------|------|------|-------|

| Syllibol | Faranietei                                                                   | Condition              | Min. | Тур. | Max. | Offic |

| Vdet1    | Voltage detection level <sup>(4)</sup>                                       |                        | 2.70 | 2.85 | 3.00 | V     |

| =        | Voltage monitor 1 interrupt request generation time <sup>(2)</sup>           |                        | -    | 40   | _    | μS    |

| =        | Voltage detection circuit self power consumption                             | VCA26 = 1, Vcc = 5.0 V | =    | 0.6  | =    | μΑ    |

| td(E-A)  | Waiting time until voltage detection circuit operation starts <sup>(3)</sup> |                        | -    | -    | 100  | μS    |

## NOTES:

- 1. The measurement condition is Vcc = 2.2 to 5.5 V and Topr = -20 to 85°C (N version) / -40 to 85°C (D version).

- 2. Time until the voltage monitor 1 interrupt request is generated after the voltage passes Vdet1.

- 3. Necessary time until the voltage detection circuit operates when setting to 1 again after setting the VCA26 bit in the VCA2 register to 0.

- 4. This parameter shows the voltage detection level when the power supply drops. The voltage detection level when the power supply rises is higher than the voltage detection level when the power supply drops by approximately 0.1 V.

Table 5.8 Voltage Detection 2 Circuit Electrical Characteristics

| Symbol  | Parameter                                                                    | Condition              |      | Unit |      |       |

|---------|------------------------------------------------------------------------------|------------------------|------|------|------|-------|

| Symbol  | Farameter                                                                    | Condition              | Min. | Тур. | Max. | Offic |

| Vdet2   | Voltage detection level                                                      |                        | 3.3  | 3.6  | 3.9  | V     |

| -       | Voltage monitor 2 interrupt request generation time <sup>(2)</sup>           |                        | _    | 40   | _    | μS    |

| =       | Voltage detection circuit self power consumption                             | VCA27 = 1, Vcc = 5.0 V | =    | 0.6  | =    | μΑ    |

| td(E-A) | Waiting time until voltage detection circuit operation starts <sup>(3)</sup> |                        | =    | =    | 100  | μ\$   |

### NOTES:

- 1. The measurement condition is Vcc = 2.2 to 5.5 V and Topr = -20 to 85°C (N version) / -40 to 85°C (D version).

- $2. \quad \text{Time until the voltage monitor 2 interrupt request is generated after the voltage passes $V_{\text{det}2}$.}$

- 3. Necessary time until the voltage detection circuit operates after setting to 1 again after setting the VCA27 bit in the VCA2 register to 0.

**Table 5.10 High-speed On-Chip Oscillator Circuit Electrical Characteristics**

| Cumbal  | Parameter                                                                       | Condition                                                                                 |      | Unit   |      |      |

|---------|---------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|------|--------|------|------|

| Symbol  | Parameter                                                                       | Condition                                                                                 | Min. | Тур.   | Max. | Unit |

| fOCO40M | High-speed on-chip oscillator frequency temperature • supply voltage dependence | Vcc = 2.7  V to  5.5  V<br>-20°C \le Topr \le 85°C <sup>(2)</sup>                         | 39.2 | 40     | 40.8 | MHz  |

|         |                                                                                 | Vcc = 2.7 V to 5.5 V<br>$-40^{\circ}$ C $\leq$ Topr $\leq$ 85 $^{\circ}$ C <sup>(2)</sup> | 39.0 | 40     | 41.0 | MHz  |

|         |                                                                                 | Vcc = 2.2 V to 5.5 V<br>$-20^{\circ}$ C $\leq$ Topr $\leq$ 85 $^{\circ}$ C <sup>(3)</sup> | 35.2 | 40     | 44.8 | MHz  |

|         |                                                                                 | Vcc = 2.2 V to 5.5 V<br>$-40^{\circ}$ C $\leq$ Topr $\leq$ 85 $^{\circ}$ C <sup>(3)</sup> | 34.0 | 40     | 46.0 | MHz  |

|         | High-speed on-chip oscillator frequency when                                    | Vcc = 5.0 V, Topr = 25°C                                                                  | _    | 36.864 | _    | MHz  |

|         | correction value in FRA7 register is written to FRA1 register <sup>(4)</sup>    | Vcc = 2.7 V to 5.5 V<br>-20°C ≤ Topr ≤ 85°C                                               | -3%  | =      | 3%   | %    |

| _       | Value in FRA1 register after reset                                              |                                                                                           | 08h  | _      | F7h  | -    |

| _       | Oscillation frequency adjustment unit of high-<br>speed on-chip oscillator      | Adjust FRA1 register (value after reset) to -1                                            | -    | +0.3   | -    | MHz  |

| _       | Oscillation stability time                                                      | Vcc = 5.0 V, Topr = 25°C                                                                  | _    | 10     | 100  | μS   |

| =       | Self power consumption at oscillation                                           | Vcc = 5.0 V, Topr = 25°C                                                                  | _    | 550    | _    | μΑ   |

- Vcc = 2.2 to 5.5 V, T<sub>opr</sub> = -20 to 85°C (N version) / -40 to 85°C (D version), unless otherwise specified.

These standard values show when the FRA1 register value after reset is assumed.

- 3. These standard values show when the corrected value of the FRA6 register is written to the FRA1 register.

- 4. This enables the setting errors of bit rates such as 9600 bps and 38400 bps to be 0% when the serial interface is used in UART mode.

**Table 5.11 Low-speed On-Chip Oscillator Circuit Electrical Characteristics**

| Symbol | Parameter                              | Condition                |      | Unit |      |       |

|--------|----------------------------------------|--------------------------|------|------|------|-------|

| Symbol | Farameter                              | Condition                | Min. | Тур. | Max. | Offic |

| fOCO-S | Low-speed on-chip oscillator frequency |                          | 30   | 125  | 250  | kHz   |

| _      | Oscillation stability time             |                          | =    | 10   | 100  | μS    |

| =      | Self power consumption at oscillation  | Vcc = 5.0 V, Topr = 25°C | -    | 15   | -    | μΑ    |

# NOTE:

1. Vcc = 2.2 to 5.5 V,  $T_{opr} = -20$  to 85°C (N version) / -40 to 85°C (D version), unless otherwise specified.

**Table 5.12 Power Supply Circuit Timing Characteristics**

| Symbol  | Parameter                                                                   | Condition | ,    | d    | Unit |       |

|---------|-----------------------------------------------------------------------------|-----------|------|------|------|-------|

| Symbol  | r alametel                                                                  | Condition | Min. | Тур. | Max. | Offic |

| td(P-R) | Time for internal power supply stabilization during power-on <sup>(2)</sup> |           | 1    | =    | 2000 | μS    |

| td(R-S) | STOP exit time <sup>(3)</sup>                                               |           | -    | -    | 150  | μS    |

## NOTES:

- 1. The measurement condition is Vcc = 2.2 to 5.5 V and Topr = 25°C.

- Waiting time until the internal power supply generation circuit stabilizes during power-on.

- 3. Time until system clock supply starts after the interrupt is acknowledged to exit stop mode.

Table 5.14 Electrical Characteristics (2) [Vcc = 5 V] (Topr = -20 to 85°C (N version) / -40 to 85°C (D version), unless otherwise specified.)

| Symbol | Parameter Condition                                                 | Standard                           |                                                                                                                             |      | Unit |      |      |

|--------|---------------------------------------------------------------------|------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|------|------|------|------|

| Symbol | Parameter                                                           |                                    | Condition                                                                                                                   | Min. | Тур. | Max. | Unii |

| Icc    | current<br>(Vcc = 3.3 to 5.5 V)                                     | High-speed clock mode              | XIN = 20 MHz (square wave) High-speed on-chip oscillator off Low-speed on-chip oscillator on = 125 kHz No division          | -    | 10   | 17   | mA   |

|        | Single-chip mode,<br>output pins are<br>open, other pins<br>are Vss |                                    | XIN = 16 MHz (square wave)<br>High-speed on-chip oscillator off<br>Low-speed on-chip oscillator on = 125 kHz<br>No division | -    | 9    | 15   | mA   |

|        |                                                                     |                                    | XIN = 10 MHz (square wave)<br>High-speed on-chip oscillator off<br>Low-speed on-chip oscillator on = 125 kHz<br>No division | -    | 6    | -    | mA   |

|        |                                                                     |                                    | XIN = 20 MHz (square wave) High-speed on-chip oscillator off Low-speed on-chip oscillator on = 125 kHz Divide-by-8          | -    | 5    | -    | mA   |

|        |                                                                     |                                    | XIN = 16 MHz (square wave)<br>High-speed on-chip oscillator off<br>Low-speed on-chip oscillator on = 125 kHz<br>Divide-by-8 | -    | 4    |      | mA   |

|        |                                                                     |                                    | XIN = 10 MHz (square wave) High-speed on-chip oscillator off Low-speed on-chip oscillator on = 125 kHz Divide-by-8          | -    | 2.5  |      | mA   |

|        |                                                                     | High-speed on-chip oscillator mode | XIN clock off High-speed on-chip oscillator on fOCO = 20 MHz Low-speed on-chip oscillator on = 125 kHz No division          | -    | 10   | 15   | mA   |