#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Not For New Designs                                                              |

|----------------------------|----------------------------------------------------------------------------------|

| Core Processor             | SH2A                                                                             |

| Core Size                  | 32-Bit Single-Core                                                               |

| Speed                      | 160MHz                                                                           |

| Connectivity               | CANbus, EBI/EMI, SCI, SPI, UART/USART                                            |

| Peripherals                | DMA, POR, PWM, WDT                                                               |

| Number of I/O              | 85                                                                               |

| Program Memory Size        | 256KB (256K x 8)                                                                 |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 32K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 16x12b                                                                       |

| Oscillator Type            | External                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 120-LQFP                                                                         |

| Supplier Device Package    | -                                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/r5f72374adfp-v0 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### Table 2.5 T Bit

| SH2-A/SH2A-FPU CPU |        | Description                                     | Examp | Example of Other CPU |  |

|--------------------|--------|-------------------------------------------------|-------|----------------------|--|

| CMP/GE             | R1,R0  | T bit is set when $R0 \ge R1$ .                 | CMP.W | R1,R0                |  |

| BT                 | TRGET0 | The program branches to TRGET0                  | BGE   | TRGET0               |  |

| BF                 | TRGET1 | when $R0 \ge R1$ and to TRGET1 when $R0 < R1$ . | BLT   | TRGET1               |  |

| ADD                | #−1,R0 | T bit is not changed by ADD.                    | SUB.W | #1,R0                |  |

| CMP/EQ             | #0,R0  | T bit is set when $R0 = 0$ .                    | BEQ   | TRGET                |  |

| BT                 | TRGET  | The program branches if $R0 = 0$ .              |       |                      |  |

#### (10) Immediate Data

Byte immediate data is located in an instruction code. Word or longword immediate data is not located in instruction codes but in a memory table. The memory table is accessed by an immediate data transfer instruction (MOV) using the PC relative addressing mode with displacement.

With the SH-2A/SH2A-FPU, 17- to 28-bit immediate data can be located in an instruction code. However, for 21- to 28-bit immediate data, an OR instruction must be executed after the data is transferred to a register.

| Classification   | SH-2A/SH2A-FPU CPU          |               | Exampl | e of Other CPU |

|------------------|-----------------------------|---------------|--------|----------------|

| 8-bit immediate  | MOV                         | #H'12,R0      | MOV.B  | #H'12,R0       |

| 16-bit immediate | MOVI20                      | #H'1234,R0    | MOV.W  | #H'1234,R0     |

| 20-bit immediate | MOVI20                      | #H'12345,R0   | MOV.L  | #H'12345,R0    |

| 28-bit immediate | mediate MOVI20S #H'12345,R0 |               | MOV.L  | #H'1234567,R0  |

|                  | OR                          | #H'67,R0      |        |                |

| 32-bit immediate | MOV.L                       | @(disp,PC),R0 | MOV.L  | #H'12345678,R0 |

|                  |                             |               |        |                |

|                  | .DATA.L                     | H'12345678    |        |                |

#### Table 2.6 Immediate Data Accessing

Note: @(disp, PC) accesses the immediate data.

## 4.2 Input/Output Pins

Table 4.1 lists the clock pulse generator pins and their functions.

#### Table 4.1 Pin Configuration and Functions of the Clock Pulse Generator

| Pin Name          | Symbol       | I/O    | Function                                                                                            |

|-------------------|--------------|--------|-----------------------------------------------------------------------------------------------------|

| pins (clock input | XTAL         | Output | Connected to the crystal resonator. (Leave this pin open when the crystal resonator is not in use.) |

| pins)             | EXTAL        | Input  | Connected to the crystal resonator or used to input an external clock.                              |

| Clock output pin  | CK*          | Output | Clock output pin. This pin can be placed in high-impedance state.                                   |

| Note: * Can be    | used for the | SH723  | 9A and SH7237A only.                                                                                |

To use the clock output (CK) pin, appropriate settings may be needed in the pin function controller (PFC) in some cases. For details, refer to section 21, Pin Function Controller (PFC).

# 5.3 Address Errors

#### 5.3.1 Address Error Sources

Address errors occur when instructions are fetched or data read or written, as shown in table 5.6.

### Table 5.6 Bus Cycles and Address Errors

| Bus Cycle   |                            |                                                                          |                      |

|-------------|----------------------------|--------------------------------------------------------------------------|----------------------|

| Туре        | Bus<br>Master              | Bus Cycle Description                                                    | Address Errors       |

| Instruction | CPU                        | Instruction fetched from even address                                    | None (normal)        |

| fetch       |                            | Instruction fetched from odd address                                     | Address error occurs |

|             |                            | Instruction fetched from other than on-chip peripheral module space*     | None (normal)        |

|             |                            | Instruction fetched from on-chip peripheral module space*                | Address error occurs |

|             |                            | Instruction fetched from external memory space in single-chip mode       | Address error occurs |

| Data        | CPU, DMAC,<br>vrite or DTC | Word data accessed from even address                                     | None (normal)        |

| read/write  |                            | Word data accessed from odd address                                      | Address error occurs |

|             |                            | Longword data accessed from a longword boundary                          | None (normal)        |

|             |                            | Longword data accessed from other than a long-word boundary              | Address error occurs |

|             |                            | Byte or word data accessed in on-chip<br>peripheral module space*        | None (normal)        |

|             |                            | Double longword data accessed from a double longword boundary            | None (normal)        |

|             |                            | Double Longword data accessed from other than a double longword boundary | Address error occurs |

#### 6.10.4 Notes on Canceling Software Standby Mode with an IRQx Interrupt Request

When canceling software standby mode using an IRQx interrupt request, change the IRQ sense select setting of ICRx in a state in which no IRQx interrupt requests are generated and clear the IRQxF flag in IRQRRx to 0 by the automatic clearing function of the IRQx interrupt processing.

If the IRQxF flag in the IRQ interrupt request register x (IRQRRx) is 1, changing the setting of the IRQ sense select bits in the interrupt control register x (ICRx) or clearing the IRQxF flag in IRQRRx to 0 will clear the relevant IRQx interrupt request but will not clear the software standby cancellation request.

### Table 11.34 TIOC4B Output Level Select Function

| Bit 4 | Function       |              |                      |            |  |  |  |

|-------|----------------|--------------|----------------------|------------|--|--|--|

|       |                |              | Compare Match Output |            |  |  |  |

| OLS3P | Initial Output | Active Level | Up Count             | Down Count |  |  |  |

| 0     | High level     | Low level    | Low level            | High level |  |  |  |

| 1     | Low level      | High level   | High level           | Low level  |  |  |  |

### Table 11.35 TIOC4C Output Level Select Function

| Bit 3    | Function       |                     |                      |                                     |  |  |

|----------|----------------|---------------------|----------------------|-------------------------------------|--|--|

|          |                |                     | Compare Match Output |                                     |  |  |

| OLS2N    | Initial Output | Active Level        | Up Count             | Down Count                          |  |  |

| 0        | High level     | Low level           | High level           | Low level                           |  |  |

| 1        | Low level      | High level          | Low level            | High level                          |  |  |

| Notes Th |                | voveform initial or | tout value shanges   | to the estive level ofter elence of |  |  |

Note: The reverse phase waveform initial output value changes to the active level after elapse of the dead time after count start.

### Table 11.36 TIOC4A Output Level Select Function

| Bit 2 | Function       |              |                      |            |  |  |  |

|-------|----------------|--------------|----------------------|------------|--|--|--|

|       |                |              | Compare Match Output |            |  |  |  |

| OLS2P | Initial Output | Active Level | Up Count             | Down Count |  |  |  |

| 0     | High level     | Low level    | Low level            | High level |  |  |  |

| 1     | Low level      | High level   | High level           | Low level  |  |  |  |

### Table 11.37 TIOC3D Output Level Select Function

| Bit 1 | Function       |                      |            |            |  |  |  |

|-------|----------------|----------------------|------------|------------|--|--|--|

|       |                | Compare Match Output |            |            |  |  |  |

| OLS1N | Initial Output | Active Level         | Up Count   | Down Count |  |  |  |

| 0     | High level     | Low level            | High level | Low level  |  |  |  |

| 1     | Low level      | High level           | Low level  | High level |  |  |  |

Note: The reverse phase waveform initial output value changes to the active level after elapse of the dead time after count start.

| Μφ                      |         |  |

|-------------------------|---------|--|

| TCNT input clock        |         |  |

| TCNT                    | N N + 1 |  |

| TGR                     | N       |  |

| Compare<br>match signal |         |  |

| TIOC pin                | χ       |  |

## Figure 11.98 Output Compare Output Timing (Complementary PWM Mode/Reset Synchronous PWM Mode)

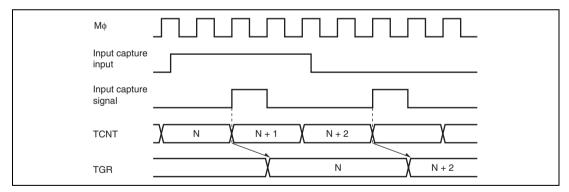

#### (3) Input Capture Signal Timing

Figure 11.99 shows input capture signal timing.

Figure 11.99 Input Capture Input Signal Timing

| Bit | Bit Name   | Initial<br>Value | R/W     | Description                                                                                                                                                                                                                                                                                   |

|-----|------------|------------------|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 12  | MTU2P3CZE  | 1                | R/(W)*1 | MTU2 Port 3 Output Comparison/High-Impedance<br>Enable                                                                                                                                                                                                                                        |

|     |            |                  |         | Specifies whether to compare output levels for the MTU2 high-current PE13/TIOC4B and PE15/TIOC4D pins and to place them in high-impedance state when the OSF1 bit is set to 1 while the OCE1 bit is 1 or when either the selected POE pin flag* <sup>2</sup> or MTU2CH34HIZ bits is set to 1. |

|     |            |                  |         | 0: Does not compare output levels or place the pins in high-impedance state                                                                                                                                                                                                                   |

|     |            |                  |         | 1: Compares output levels and places the pins in<br>high-impedance state                                                                                                                                                                                                                      |

| 11  | —          | 0                | R       | Reserved                                                                                                                                                                                                                                                                                      |

|     |            |                  |         | This bit is always read as 0. The write value should always be 0.                                                                                                                                                                                                                             |

| 10  | MTU2SP1CZE | 1                | R/(W)*1 | MTU2S Port 1 Output Comparison/High-Impedance<br>Enable                                                                                                                                                                                                                                       |

|     |            |                  |         | Specifies whether to compare output levels for the MTU2S high-current PE5/TIOC3BS and PE6/TIOC3DS pins and to place them in high-impedance state when the OSF2 bit is set to 1 while the OCE2 bit is 1 or when either the selected POE pin flag* <sup>2</sup> or MTU2SHIZ bits is set to 1.   |

|     |            |                  |         | 0: Does not compare output levels or place the pins in high-impedance state.                                                                                                                                                                                                                  |

|     |            |                  |         | 1: Compares output levels and places the pins in<br>high-impedance state.                                                                                                                                                                                                                     |

### 13.4.1 Input Level Detection Operation

If the input conditions set by ICSR1 to ICSR3 occur on the POE0, POE4 and POE8 pins, the highcurrent pins and the pins for channel 0 of the MTU2 are placed in high-impedance state. Note however, that these high-current and MTU2 pins enter high-impedance state only when general input/output function, MTU2 function, or MTU2S function is selected for these pins.

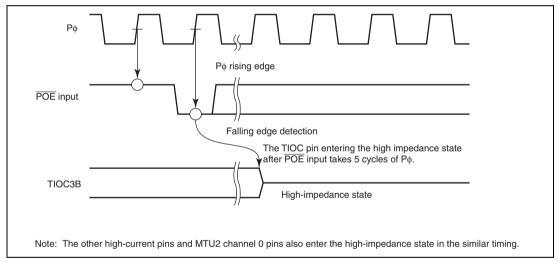

#### (1) Falling Edge Detection

When a change from a high to low level is input to the POE0, POE4 and POE8 pins, the highcurrent pins and the pins for channel 0 of the MTU2 are placed in high-impedance state.

Figure 13.2 shows the sample timing after the level changes in input to the  $\overline{POE0}$ ,  $\overline{POE4}$  and  $\overline{POE8}$  pins until the respective pins enter high-impedance state.

Figure 13.2 Falling Edge Detection

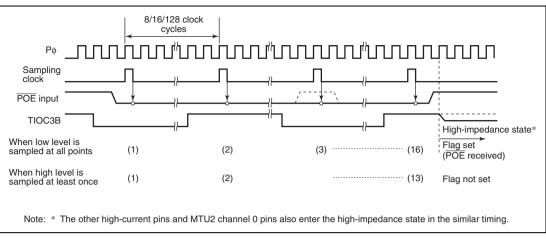

### (2) Low-Level Detection

Figure 13.3 shows the low-level detection operation. Sixteen continuous low levels are sampled with the sampling clock selected by ICSR1 to ICSR3. If even one high level is detected during this interval, the low level is not accepted.

The timing when the high-current pins enter the high-impedance state after the sampling clock is input is the same in both falling-edge detection and in low-level detection.

Figure 13.3 Low-Level Detection Operation

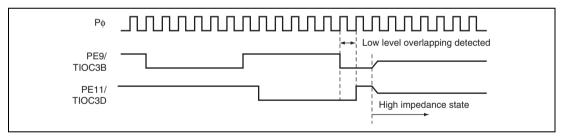

### 13.4.2 Output-Level Compare Operation

Figure 13.4 shows an example of the output-level compare operation for the combination of TIOC3B and TIOC3D. The operation is the same for the other pin combinations.

Figure 13.4 Output-Level Compare Operation

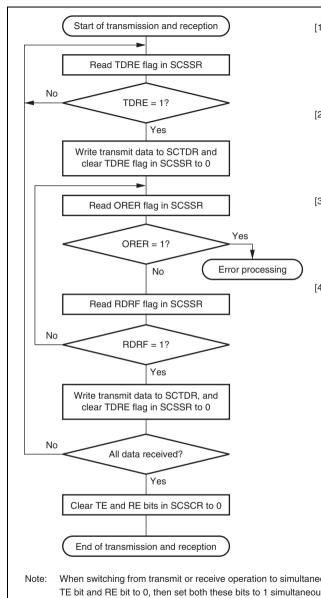

- [1] SCI status check and transmit data write: Read SCSSR and check that the TDRE flag is set to 1, then write transmit data to SCTDR and clear the TDRE flag to 0. Transition of the TDRE flag from 0 to 1 can also be identified by a TXI interrupt.

- [2] Receive error processing: If a receive error occurs, read the ORER flag in SCSSR, and after performing the appropriate error processing, clear the ORER flag to 0. Reception cannot be resumed if the ORER flag is set to 1.

- [3] SCI status check and receive data read: Read SCSSR and check that the RDRF flag is set to 1, then read the receive data in SCRDR and clear the RDRF flag to 0. Transition of the RDRF flag from 0 to 1 can also be identified by an RXI interrupt.

- [4] Serial transmission/reception continuation procedure:

To continue serial transmission/reception. before the MSB (bit 7) of the current frame is received, finish reading the RDRF flag, reading SCRDR, and clearing the RDRF flag to 0. Also, before the MSB (bit 7) of the current frame is transmitted, read 1 from the TDRE flag to confirm that writing is possible. Then write data to SCTDR and clear the TDRE flag to 0. Checking and clearing of the TDRE flag is automatic when the DTC is activated by a transmit data empty interrupt (TXI) request and data is written to SCTDR. Also, the RDRF flag is cleared automatically when the DTC is activated by a receive data full interrupt (RXI) request and the SCRDR value is read.

When switching from transmit or receive operation to simultaneous transmit and receive operations, first clear the TE bit and RE bit to 0, then set both these bits to 1 simultaneously.

### Figure 16.15 Sample Flowchart for Transmitting/Receiving Serial Data

## 16.7 Usage Notes

#### 16.7.1 SCTDR Writing and TDRE Flag

The TDRE flag in the serial status register (SCSSR) is a status flag indicating transferring of transmit data from SCTDR into SCTSR. The SCI sets the TDRE flag to 1 when it transfers data from SCTDR to SCTSR.

Data can be written to SCTDR regardless of the TDRE bit status.

If new data is written in SCTDR when TDRE is 0, however, the old data stored in SCTDR will be lost because the data has not yet been transferred to SCTSR. Before writing transmit data to SCTDR, be sure to check that the TDRE flag is set to 1.

### 16.7.2 Multiple Receive Error Occurrence

If multiple receive errors occur at the same time, the status flags in SCSSR are set as shown in table 16.18. When an overrun error occurs, data is not transferred from the receive shift register (SCRSR) to the receive data register (SCRDR) and the received data will be lost.

#### Table 16.19 SCSSR Status Flag Values and Transfer of Received Data

|                                              | SCSSR Status Flags |      |     |     | Receive Data<br>Transfer from<br>SCRSR to |

|----------------------------------------------|--------------------|------|-----|-----|-------------------------------------------|

| Receive Errors Generated                     | RDRF               | ORER | FER | PER | SCRDR                                     |

| Overrun error                                | 1                  | 1    | 0   | 0   | Not transferred                           |

| Framing error                                | 0                  | 0    | 1   | 0   | Transferred                               |

| Parity error                                 | 0                  | 0    | 0   | 1   | Transferred                               |

| Overrun error + framing error                | 1                  | 1    | 1   | 0   | Not transferred                           |

| Overrun error + parity error                 | 1                  | 1    | 0   | 1   | Not transferred                           |

| Framing error + parity error                 | 0                  | 0    | 1   | 1   | Transferred                               |

| Overrun error + framing error + parity error | 1                  | 1    | 1   | 1   | Not transferred                           |

## 17.3.13 Serial Extended Mode Register (SCSEMR)

SCSEMR is an 8-bit register that extends the SCIF functions. The transfer rate can be doubled by setting the basic clock in asynchronous mode.

Be sure to set this register to H'00 in clocked synchronous mode. SCSEMR is initialized to H'00 by a power-on reset.

| Bit:                   | 7        | 6        | 5        | 4        | 3        | 2        | 1        | 0        |

|------------------------|----------|----------|----------|----------|----------|----------|----------|----------|

|                        | ABCS     | -        | -        | -        | -        | -        | -        | -        |

| Initial value:<br>B/W: | 0<br>B/W | 0<br>B/W | 0<br>R/W | 0<br>R/W | 0<br>R/W | 0<br>B/W | 0<br>B/W | 0<br>B/W |

| n/w.                   |          |          |          |          |          |          |          |          |

|        |          | Initial |     |                                                                                           |

|--------|----------|---------|-----|-------------------------------------------------------------------------------------------|

| Bit    | Bit Name | Value   | R/W | Description                                                                               |

| 7      | ABCS     | 0       | R/W | Asynchronous Basic Clock Select                                                           |

|        |          |         |     | Selects the basic clock for 1-bit period in asynchronous mode.                            |

|        |          |         |     | Setting of ABCS is valid when the asynchronous mode bit (C/ $\overline{A}$ in SCSMR) = 0. |

|        |          |         |     | 0: Basic clock with a frequency of 16 times the<br>transfer rate                          |

|        |          |         |     | 1: Basic clock with a frequency of 8 times the transfer<br>rate                           |

| 6 to 0 | _        | All 0   | R/W | Reserved                                                                                  |

|        |          |         |     | These bits are always read as 0. The write value should always be 0.                      |

|        |          |         |     |                                                                                           |

### 18.4.3 RSPI System Configuration Example

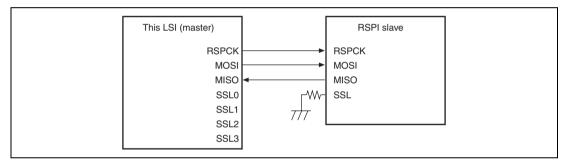

### (1) Single Master/Single Slave (with This LSI Acting as Master)

Figure 18.2 shows a single-master/single-slave RSPI system configuration example when this LSI is used as a master. In the single-master/single-slave configuration, the SSL0 to SSL3 outputs of this LSI (master) are not used. The SSL input of the RSPI slave is fixed to 0, and the RSPI slave is always maintained in a select state. In the transfer format corresponding to the case where the CPHA bit in the RSPI control register (SPCR) is 0, there are slave devices for which the SSL signal cannot be fixed to the active level. In situations where the SSL signal cannot be fixed, the SSL output of this LSI should be connected to the SSL input of the slave device.

This LSI (master) always drives the RSPCK and MOSI signals. The RSPI slave always drives the MISO signal.

Figure 18.2 Single-Master/Single-Slave Configuration Example (This LSI = Master)

## (1) Master Control Register (MCR)

The Master Control Register (MCR) is a 16-bit read/write register that controls RCAN-ET.

### • MCR (Address = H'000)

| Bit: 15          | 14       | 13 | 12 | 11 | 10  | 9        | 8   | 7    | 6    | 5    | 4 | 3 | 2    | 1    | 0    |

|------------------|----------|----|----|----|-----|----------|-----|------|------|------|---|---|------|------|------|

| MCR              | 15 MCR14 | -  | -  | -  |     | TST[2:0] |     | MCR7 | MCR6 | MCR5 | - | - | MCR2 | MCR1 | MCR0 |

| Initial value: 1 | 0        | 0  | 0  | 0  | 0   | 0        | 0   | 0    | 0    | 0    | 0 | 0 | 0    | 0    | 1    |

| R/W: R/W         | / R/W    | R  | R  | R  | R/W | R/W      | R/W | R/W  | R/W  | R/W  | R | R | R/W  | R/W  | R/W  |

Bit 15 — ID Reorder (MCR15): This bit changes the order of STDID, RTR, IDE and EXTID of both message control and LAFM.

| Bit15 : MCR15 | Description                                      |

|---------------|--------------------------------------------------|

| 0             | RCAN-ET is the same as HCAN2                     |

| 1             | RCAN-ET is not the same as HCAN2 (Initial value) |

| MCR15 (ID Reord                 | er) = 0       |                                 |    |    |    |      |        |                 |              |     |   |         |           |              |              |               |                    |              |  |  |  |

|---------------------------------|---------------|---------------------------------|----|----|----|------|--------|-----------------|--------------|-----|---|---------|-----------|--------------|--------------|---------------|--------------------|--------------|--|--|--|

|                                 | 15            | 14                              | 13 | 12 | 11 | 10   | 9      | 8               | 7            | 6   | 5 | 4       | 3         | 2            | 1            | 0             |                    |              |  |  |  |

| H'100 + N*32                    | 0             | STDID[10:0] RTR IDE EXTID[17:16 |    |    |    |      |        |                 |              |     |   | [17:16] | Word/LW   | Control 0    |              |               |                    |              |  |  |  |

| H'102 + N*32                    |               | EXTID[15:0]                     |    |    |    |      |        |                 |              |     |   | Word    | Control 0 |              |              |               |                    |              |  |  |  |

| H'104 + N*32                    | 0             |                                 |    |    |    | STDI | D_LAFN | A[10:0]         |              |     |   |         | 0         | IDE_<br>LAFM | EXTID<br>[17 | _LAFM<br>:16] | Word/LW LAFM Field |              |  |  |  |

| H'106 + N*32                    |               |                                 |    |    |    |      | F      | XTID_L          | AEM[15       | -01 |   |         |           |              |              |               | 144.001            | LAFINI FIEID |  |  |  |

|                                 |               |                                 |    |    |    |      |        |                 | su intro     | .0] |   |         |           |              |              |               | Word               |              |  |  |  |

|                                 | er) = 1<br>15 | 14                              | 13 | 12 | 11 | 10   | 9      | 8               | 7            | 6   | 5 | 4       | 3         | 2            | 1            | 0             | wora               | I            |  |  |  |

|                                 | ,             | 14<br>RTR                       | 13 | 12 | 11 | 10   |        | 8               | 7<br>TDID[10 | 6   | 5 | 4       | 3         | 2            | 1<br>EXTID   | 0<br>[17:16]  | Word/LW            | Castal       |  |  |  |

| MCR15 (ID Reord                 | 15            |                                 | -  | 12 | 11 | 10   |        | 8<br>S          | 7            | 6   | 5 | 4       | 3         | 2            | 1<br>EXTID   | -             |                    | Control 0    |  |  |  |

| MCR15 (ID Reord<br>H'100 + N*32 | 15            |                                 | -  | 12 | 11 | 10   |        | 8<br>S<br>EXTII | 7<br>TDID[10 | 6   | 5 | 4       | 3         | 2            | EXTID        | -             | Word/LW            | Control 0    |  |  |  |

## Figure 20.6 ID Reorder

This bit can be modified only in reset mode.

**Bit 2**— **Message Transmission in progress Flag (GSR2):** Flag that indicates to the CPU if the RCAN-ET is in Bus Off or transmitting a message or an error/overload flag due to error detected during transmission. The timing to set TXACK is different from the time to clear GSR2. TXACK is set at the 7<sup>th</sup> bit of End Of Frame. GSR2 is set at the 3<sup>rd</sup> bit of intermission if there are no more messages ready to be transmitted. It is also set by arbitration lost, bus idle, reception, reset or halt transition.

| Bit 2 : GSR2 | Description                                                                        |

|--------------|------------------------------------------------------------------------------------|

| 0            | RCAN-ET is in Bus Off or a transmission is in progress                             |

| 1            | [Setting condition] Not in Bus Off and no transmission in progress (Initial value) |

Bit 1—Transmit/Receive Warning Flag (GSR1): Flag that indicates an error warning.

| Bit 1 : GSR1 | Description                                                               |

|--------------|---------------------------------------------------------------------------|

| 0            | [Reset condition] When (TEC < 96 and REC < 96) or Bus Off (Initial value) |

| 1            | [Setting condition] When $96 \le TEC < 256$ or $96 \le REC < 256$         |

Note: REC is incremented during Bus Off to count the recurrences of 11 recessive bits as requested by the Bus Off recovery sequence. However the flag GSR1 is not set in Bus Off.

Bit 0—Bus Off Flag (GSR0): Flag that indicates that RCAN-ET is in the bus off state.

| Bit 0 : GSR0 | Description                                                                             |

|--------------|-----------------------------------------------------------------------------------------|

| 0            | [Reset condition] Recovery from bus off state or after a HW or SW reset (Initial value) |

| 1            | [Setting condition] When TEC $\ge$ 256 (bus off state)                                  |

Note: Only the lower 8 bits of TEC are accessible from the user interface. The 9<sup>th</sup> bit is equivalent to GSR0.

The following table shows conditions to access registers.

|                                           |            | HOAR-ET Hegisters |      |       |               |                          |       |                                    |  |  |  |  |  |

|-------------------------------------------|------------|-------------------|------|-------|---------------|--------------------------|-------|------------------------------------|--|--|--|--|--|

| Status Mode                               | MCR<br>GSR | IRR<br>IMR        | BCR  | MBIMR | Flag_register | mailbox<br>(ctrl0, LAFM) |       | mailbox<br>(ctrl1)                 |  |  |  |  |  |

| Reset                                     | yes        | yes               | yes  | yes   | yes           | yes                      | yes   | yes                                |  |  |  |  |  |

| Transmission<br>Reception<br>Halt Request | yes        | yes               | no*1 | yes   | yes           | no*1 yes*2               | yes*2 | no* <sup>1</sup> yes* <sup>2</sup> |  |  |  |  |  |

| Halt                                      | yes        | yes               | no*1 | yes   | yes           | yes                      | yes   | yes                                |  |  |  |  |  |

| Sleep                                     | yes        | yes               | no   | no    | no            | no                       | no    | no                                 |  |  |  |  |  |

**RCAN-ET Registers**

Notes: 1. No hardware protection

2. When TXPR is not set.

| Bit | Bit Name | Initial<br>Value | R/W | Description                                                                                                                                      |

|-----|----------|------------------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------|

| 3   | SUSRDY   | 0                | R   | Suspend Ready                                                                                                                                    |

|     |          |                  |     | Indicates whether the FCU is ready to accept a P/E suspend command.                                                                              |

|     |          |                  |     | 0: The FCU cannot accept a P/E suspend command                                                                                                   |

|     |          |                  |     | 1: The FCU can accept a P/E suspend command                                                                                                      |

|     |          |                  |     | [Setting condition]                                                                                                                              |

|     |          |                  |     | <ul> <li>After initiating programming/erasure, the FCU has<br/>entered a state where it is ready to accept a P/E<br/>suspend command.</li> </ul> |

|     |          |                  |     | [Clearing conditions]                                                                                                                            |

|     |          |                  |     | • The FCU has accepted a P/E suspend command.                                                                                                    |

|     |          |                  |     | The FCU has entered a command-locked state                                                                                                       |

|     |          |                  |     | during programming or erasure.                                                                                                                   |

| 2   | _        | 0                | R   | Reserved                                                                                                                                         |

|     |          |                  |     | This bit is always read as 0. Correct operation is not guaranteed if 1 is written to this bit.                                                   |

| 1   | ERSSPD   | 0                | R   | Erasure-Suspended Status                                                                                                                         |

|     |          |                  |     | Indicates that the FCU has entered an erasure suspension process or an erasure-suspended status (see section 23.6.4, Suspending Operation).      |

|     |          |                  |     | 0: The FCU is in a status other than the below-<br>mentioned.                                                                                    |

|     |          |                  |     | 1: The FCU is in an erasure suspension process or an<br>erasure-suspended status.                                                                |

|     |          |                  |     | [Setting condition]                                                                                                                              |

|     |          |                  |     | The FCU has initiated an erasure suspend<br>command.                                                                                             |

|     |          |                  |     | [Clearing condition]                                                                                                                             |

|     |          |                  |     | • The FCU has accepted a resume command.                                                                                                         |

## (3) 256-Byte Programming

In response to a 256-byte programming command sent from the host, this LSI programs the ROM. After completing ROM programming successfully, this LSI returns a response (H'06). If an error has occurred during ROM programming, this LSI returns an error response (H'D0).

| Command           | H'50            |                       | Programmi         | ng Address       |                    |        |

|-------------------|-----------------|-----------------------|-------------------|------------------|--------------------|--------|

|                   | Data            | Data                  |                   | Data             |                    |        |

|                   | SUM             |                       |                   |                  |                    |        |

|                   |                 |                       |                   |                  |                    |        |

| Response          | H'06            |                       |                   |                  |                    |        |

|                   | ГТ              |                       | I                 |                  |                    |        |

| Error response    | H'D0            | Error                 |                   |                  |                    |        |

|                   |                 |                       |                   |                  |                    |        |

| [Legend]          |                 |                       |                   |                  |                    |        |

| Programming add   | ress (4 bytes): | Target add            | lress of progra   | mming            |                    |        |

|                   |                 | To program specified. | m the ROM, a      | 256-byte bour    | ndary address shou | ld be  |

|                   |                 | To termina            | ate programmi     | ng, H'FFFFFF     | FF should be spec  | ified. |

| Data (256 bytes): | Programming     | data                  |                   |                  |                    |        |

|                   | H'FF should b   | e specified for       | or the bytes that | at do not need   | to be programmed   | l.     |

|                   |                 | • • •                 | -                 | -                | ecified (only the  |        |

|                   | programming     | address and           | SUM should b      | e sent in that c | order).            |        |

| SUM (1 byte):     | Checksum        |                       |                   |                  |                    |        |

| Error (1 byte):   | Error code      |                       |                   |                  |                    |        |

|                   | H'11: Checks    | um error              |                   |                  |                    |        |

|                   | H'2A: Addres    | s error (the sp       | pecified addres   | ss is not in the | target MAT)        |        |

|                   | H'53: Program   | nming cannot          | be done due t     | o a programm     | ing error          |        |

|                   |                 |                       |                   |                  |                    |        |

| Module<br>Name | Register<br>Abbreviation | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3       | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|----------------|--------------------------|-------------------|-------------------|-------------------|-------------------|-------------------------|-------------------|------------------|------------------|--|--|

| MTU2           | TGRB_1                   |                   |                   |                   |                   |                         |                   |                  |                  |  |  |

|                |                          |                   |                   |                   |                   |                         |                   |                  |                  |  |  |

|                | TICCR                    | —                 | _                 | —                 | —                 | I2BE                    | I2AE              | I1BE             | I1AE             |  |  |

|                | TCR_2                    | —                 | CCL               | R[1:0]            | CKE               | G[1:0]                  |                   | TPSC[2:0]        |                  |  |  |

|                | TMDR_2<br>TIOR_2         | —                 |                   | —                 | —                 | MD[3:0]                 |                   |                  |                  |  |  |

|                |                          |                   | IOB               | [3:0]             |                   |                         | IOA[3             | :0]              |                  |  |  |

|                | TIER_2                   | TTGE              |                   | TCIEU             | TCIEV             | _                       | —                 | TGIEB            | TGIEA            |  |  |

|                | TSR_2                    | TCFD              | _                 | TCFU              | TCFV              | —                       | —                 | TGFB             | TGFA             |  |  |

|                | TCNT_2                   |                   |                   |                   |                   |                         |                   |                  |                  |  |  |

|                | TGRA_2                   |                   |                   |                   |                   |                         |                   |                  |                  |  |  |

|                | TGRB_2                   |                   |                   |                   |                   |                         |                   |                  |                  |  |  |

|                | TCR_3                    |                   | CCLR[2:0]         |                   | CKE               | G[1:0]                  |                   | TPSC[2:0]        |                  |  |  |

|                | TMDR_3                   | _                 | _                 | BFB               | BFA               |                         | MD[3              |                  |                  |  |  |

|                | TIORH_3                  |                   | IOB               | [3:0]             |                   |                         | IOA[3             |                  |                  |  |  |

|                | TIORL_3                  |                   |                   | [3:0]             |                   | IOC[3:0]                |                   |                  |                  |  |  |

|                | TIER_3                   | TTGE              | _                 | _                 | TCIEV             | TGIED TGIEC TGIEB TGIEA |                   |                  |                  |  |  |

|                | TSR_3                    | TCFD              |                   | _                 | TCFV              | TGFD                    | TGFC              | TGFB             | TGFA             |  |  |

|                | TCNT_3                   |                   |                   |                   |                   |                         |                   |                  |                  |  |  |

|                | TGRA_3                   |                   |                   |                   |                   |                         |                   |                  |                  |  |  |

|                |                          |                   |                   |                   |                   |                         |                   |                  |                  |  |  |

|                | TGRB_3                   |                   |                   |                   |                   |                         |                   |                  |                  |  |  |

|                | TGRC_3                   |                   |                   |                   |                   |                         |                   |                  |                  |  |  |

|                | TGRD_3                   |                   |                   |                   |                   |                         |                   |                  |                  |  |  |

|                | TBTM_3                   |                   | _                 |                   |                   |                         |                   | TTSB             | TTSA             |  |  |

|                | TCR_4                    |                   | CCLR[2:0]         |                   | CKE               | G[1:0]                  | 1                 | TPSC[2:0]        | 1                |  |  |

|                | TMDR_4                   | _                 | _                 | BFB               | BFA               |                         | MD[3              | :0]              |                  |  |  |

|                | TIORH_4                  |                   | IOB               | [3:0]             | I                 |                         | IOA[3             | :0]              |                  |  |  |

|                | TIORL_4                  |                   | IOD               | [3:0]             |                   |                         | IOC[3             | :0]              |                  |  |  |

#### Table 29.6 Permissible Output Currents

| Item                                      | Symbol                         | Min. | Тур. | Max. | Unit |

|-------------------------------------------|--------------------------------|------|------|------|------|

| Permissible output low current (per pin)  | I <sub>ol</sub>                | _    | —    | 2.0* | mA   |

| Permissible output low current (total)    | $\Sigma I_{_{OL}}$             | _    | —    | 80   | mA   |

| Permissible output high current (per pin) | $-\mathbf{I}_{_{\mathrm{OH}}}$ | _    | —    | 2*   | mA   |

| Permissible output high current (total)   | $\Sigma - I_{_{OH}}$           | _    | _    | 25   | mA   |

Note: \* TIOC3B, TIOC3D, TIOC4A to TIOC4D, TIOC3BS, TIOC3DS, TIOC4AS to TIOC4DS: SH7239B and SH7237B;  $I_{oL} = 15 \text{ mA} (Max.)/-I_{OH} = 5 \text{ mA} (Max.)$ , SH7239A and SH7237A;  $I_{oL} = 10 \text{ mA} (Max.)/-I_{OH} = 5 \text{ mA} (Max.)$ . Of these pins, the number of pins from which current more than 2.0 mA runs evenly should be 3 or less.

Caution: To protect the LSI's reliability, do not exceed the output current values in table 29.6.