#### Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Not For New Designs                                                              |

|----------------------------|----------------------------------------------------------------------------------|

| Core Processor             | SH2A-FPU                                                                         |

| Core Size                  | 32-Bit Single-Core                                                               |

| Speed                      | 100MHz                                                                           |

| Connectivity               | CANbus, SCI, SPI, UART/USART                                                     |

| Peripherals                | DMA, POR, PWM, WDT                                                               |

| Number of I/O              | 85                                                                               |

| Program Memory Size        | 512KB (512K x 8)                                                                 |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | ·                                                                                |

| RAM Size                   | 64K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 5.5V                                                                      |

| Data Converters            | A/D 16x12b                                                                       |

| Oscillator Type            | External                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 120-LQFP                                                                         |

| Supplier Device Package    | -                                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/r5f72395bdfp-v0 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 5.7 When Exception Sources Are Not Accepted

When an address error, register bank error (overflow), or interrupt is generated immediately after a delayed branch instruction, it is sometimes not accepted immediately but stored instead, as shown in table 5.10. When this happens, it will be accepted when an instruction that can accept the exception is decoded.

### Table 5.10 Exception Source Generation Immediately after Delayed Branch Instruction

|                                                              |                    | Excepti                                   | on Source                            |              |  |

|--------------------------------------------------------------|--------------------|-------------------------------------------|--------------------------------------|--------------|--|

| Point of Occurrence                                          | Address Error      | FPU<br>Exception <sup>*<sup>2</sup></sup> | Register Bank<br>Error<br>(Overflow) | Interrupt    |  |

| Immediately after a delayed branch instruction <sup>*1</sup> | Not accepted       | Not accepted                              | Not accepted                         | Not accepted |  |

| Notes: 1. Delayed branch in BRAF                             | structions: JMP, J | SR, BRA, BSR,                             | RTS, RTE, BF/S, I                    | BT/S, BSRF,  |  |

2. Only provided by the SH7239 Group. The operation cannot be guaranteed in the SH7237 Group.

# 6.5 Interrupt Exception Handling Vector Table and Priority

Table 6.4 lists interrupt sources and their vector numbers, vector table address offsets, and interrupt priorities.

Each interrupt source is allocated a different vector number and vector table address offset. Vector table addresses are calculated from the vector numbers and vector table address offsets. In interrupt exception handling, the interrupt exception service routine start address is fetched from the vector table indicated by the vector table address. For details of calculation of the vector table address, see table 5.4 in section 5, Exception Handling.

The priorities of IRQ interrupts and on-chip peripheral module interrupts can be set freely between 0 and 15 for each pin or module by setting interrupt priority registers 01, 02, and 05 to 18 (IPR01, IPR02, and IPR05 to IPR18). However, if two or more interrupts specified by the same IPR among IPR05 to IPR18 occur, the priorities are defined as shown in the IPR setting unit internal priority of table 6.4, and the priorities cannot be changed. A power-on reset assigns priority level 0 to IRQ interrupts and on-chip peripheral module interrupts. If the same priority level is assigned to two or more interrupt sources and interrupts from those sources occur simultaneously, they are processed by the default priorities indicated in table 6.4.

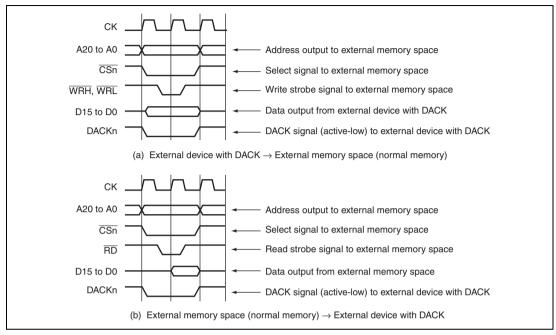

Figure 10.8 shows an example of DMA transfer timing in single address mode.

Figure 10.8 Example of DMA Transfer Timing in Single Address Mode

### (2) Bus Modes

There are two bus modes; cycle steal and burst. Select the mode by the TB bits in the channel control registers (CHCR).

### (a) Cycle Steal Mode

Normal mode

In normal mode of cycle steal, the bus mastership is given to another bus master after a onetransfer-unit (byte, word, longword, or 16-byte unit) DMA transfer. When another transfer request occurs, the bus mastership is obtained from another bus master and a transfer is performed for one transfer unit. When that transfer ends, the bus mastership is passed to another bus master. This is repeated until the transfer end conditions are satisfied.

The cycle-steal normal mode can be used for any transfer section; transfer request source, transfer source, and transfer destination.

Figure 10.9 shows an example of DMA transfer timing in cycle-steal normal mode. Transfer conditions shown in the figure are:

| Bit 1 | Bit 0 |                                                                                                                                                       |

|-------|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------|

| BTE1  | BTE0  | Description                                                                                                                                           |

| 0     | 0     | Enables transfer from the buffer registers to the temporary registers* <sup>1</sup> and does not link the transfer with interrupt skipping operation. |

| 0     | 1     | Disables transfer from the buffer registers to the temporary registers.                                                                               |

| 1     | 0     | Links transfer from the buffer registers to the temporary registers with interrupt skipping operation.* <sup>2</sup>                                  |

| 1     | 1     | Setting prohibited                                                                                                                                    |

| Note: |       | red according to the MD3 to MD0 bit setting in TMDR. For details, refer 3, Complementary PWM Mode.                                                    |

|       |       | skipping is disabled (the T3AEN and T4VEN bits are cleared to 0 in the kipping set register (TITCR) or the skipping count set bits (3ACOR and         |

### Table 11.42 Setting of Bits BTE1 and BTE0

2. When interrupt skipping is disabled (the T3AEN and T4VEN bits are cleared to 0 in the timer interrupt skipping set register (TITCR) or the skipping count set bits (3ACOR and 4VCOR) in TITCR are cleared to 0)), be sure to disable link of buffer transfer with interrupt skipping (clear the BTE1 bit in the timer buffer transfer set register (TBTER) to 0). If link with interrupt skipping is enabled while interrupt skipping is disabled, buffer transfer will not be performed.

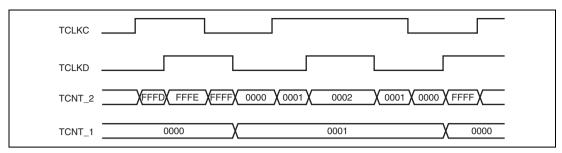

Figure 11.21 Cascaded Operation Example (a)

### (3) Cascaded Operation Example (b)

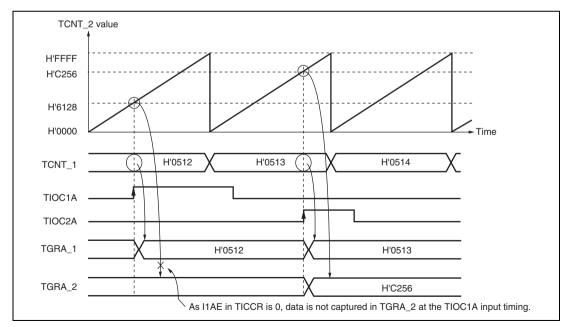

Figure 11.22 illustrates the operation when TCNT\_1 and TCNT\_2 have been cascaded and the I2AE bit in TICCR has been set to 1 to include the TIOC2A pin in the TGRA\_1 input capture conditions. In this example, the IOA0 to IOA3 bits in TIOR\_1 have selected the TIOC1A rising edge for the input capture timing while the IOA0 to IOA3 bits in TIOR\_2 have selected the TIOC2A rising edge for the input capture timing.

Under these conditions, the rising edge of both TIOC1A and TIOC2A is used for the TGRA\_1 input capture condition. For the TGRA\_2 input capture condition, the TIOC2A rising edge is used.

Figure 11.22 Cascaded Operation Example (b)

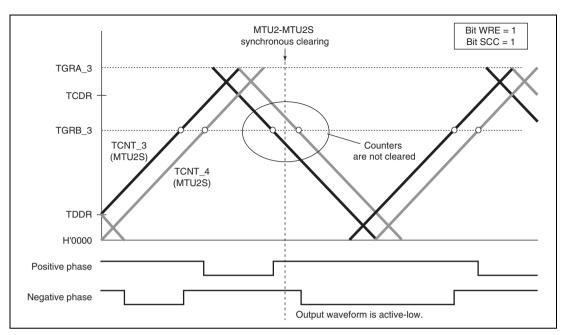

# Figure 11.66 Example of Synchronous Clearing in Dead Time during Down-Counting (Timing (8) in Figure 11.56; Bit WRE is 1 and Bit SCC is 1 in TWCR of MTU2S)

| Pins                                                                           | Conditions                                                                               | Detailed Conditions                                            |

|--------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|----------------------------------------------------------------|

| MTU2S high-current pins<br>(PD12/TIOC4AS and<br>PD14/TIOC4CS)                  | Input level detection of the selected POE pin, output level comparison, or SPOER setting | MTU2SP5CZE •<br>(MTU2s_hiz_1) + (OSF2 • OCE2) +<br>(MTU2SHIZ)) |

| MTU2S high-current pins<br>(PD13/TIOC4BS and<br>PD15/TIOC4DS)                  | Input level detection of the selected POE pin, output level comparison, or SPOER setting | MTU2SP6CZE •<br>(MTU2s_hiz_1) + (OSF2 • OCE2) +<br>(MTU2SHIZ)) |

| MTU2 CH0 pins<br>(PE0/TIOC0A,<br>PE1/TIOC0B,<br>PE2/TIOC0C, and<br>PE3/TIOC0D) | Input level detection of the selected POE pin detection or SPOER setting                 | MTU2PE0ZE to MTU2PE3ZE •<br>(MTU2ch0_hiz_1) +(MTU2CH0HIZ)      |

| MTU2 CH0 pins<br>(PB1/TIOC0A,<br>PB2/TIOC0B,<br>PB3/TIOC0C, and<br>PB4/TIOC0D) | Input level detection of the selected POE pin or SPOER setting                           | MTU2PB1ZE to MTU2PB4ZE •<br>(MTU2ch0_hiz_1) +(MTU2CH0HIZ)      |

|     |          | Initial |        |                                                                                                                                                                                                                      |

|-----|----------|---------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bit | Bit Name | value   | R/W    | Description                                                                                                                                                                                                          |

| 3   | PER      | 0       | R/(W)* | Parity Error                                                                                                                                                                                                         |

|     |          |         |        | Indicates that a parity error occurred during data reception in asynchronous mode, causing abnormal termination.                                                                                                     |

|     |          |         |        | 0: Indicates that reception is in progress or was<br>completed successfully* <sup>1</sup>                                                                                                                            |

|     |          |         |        | [Clearing conditions]                                                                                                                                                                                                |

|     |          |         |        | • By a power-on reset or in module standby mode                                                                                                                                                                      |

|     |          |         |        | • When 0 is written to PER after reading PER = 1                                                                                                                                                                     |

|     |          |         |        | 1: Indicates that a parity error occurred during reception* <sup>2</sup>                                                                                                                                             |

|     |          |         |        | [Setting condition]                                                                                                                                                                                                  |

|     |          |         |        | • When the number of 1s in the received data and                                                                                                                                                                     |

|     |          |         |        | parity does not match the even or odd parity specified by the $O/\overline{E}$ bit in the serial mode register (SCSMR).                                                                                              |

|     |          |         |        | Notes: 1. The PER flag is not affected and retains<br>its previous value when the RE bit in<br>SCSCR is cleared to 0.                                                                                                |

|     |          |         |        | <ol> <li>If a parity error occurs, the receive data is<br/>transferred to SCRDR but the RDRF flag<br/>is not set. Subsequent serial reception<br/>cannot be continued while the PER flag is<br/>set to 1.</li> </ol> |

|      |          | Initial |     |                                                                                                                                                                                                                                                               |

|------|----------|---------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bit  | Bit Name | Value   | R/W | Description                                                                                                                                                                                                                                                   |

| 3    | STOP     | 0       | R/W | Stop Bit Length                                                                                                                                                                                                                                               |

|      |          |         |     | Selects one or two bits as the stop bit length in<br>asynchronous mode. This setting is used only in<br>asynchronous mode. It is ignored in clocked<br>synchronous mode because no stop bits are added.                                                       |

|      |          |         |     | When receiving, only the first stop bit is checked,<br>regardless of the STOP bit setting. If the second stop<br>bit is 1, it is treated as a stop bit, but if the second stop<br>bit is 0, it is treated as the start bit of the next incoming<br>character. |

|      |          |         |     | <ol> <li>One stop bit<br/>When transmitting, a single 1-bit is added at the end<br/>of each transmitted character.</li> </ol>                                                                                                                                 |

|      |          |         |     | 1: Two stop bits<br>When transmitting, two 1 bits are added at the end of<br>each transmitted character.                                                                                                                                                      |

| 2    | _        | 0       | R   | Reserved                                                                                                                                                                                                                                                      |

|      |          |         |     | This bit is always read as 0. The write value should always be 0.                                                                                                                                                                                             |

| 1, 0 | CKS[1:0] | 00      | R/W | Clock Select                                                                                                                                                                                                                                                  |

|      |          |         |     | Select the internal clock source of the on-chip baud rate<br>generator. For further information on the clock source,<br>bit rate register settings, and baud rate, see section<br>17.3.8, Bit Rate Register (SCBRR).                                          |

|      |          |         |     | 00: Pø                                                                                                                                                                                                                                                        |

|      |          |         |     | 01: P <sub>\$\phi</sub> /4                                                                                                                                                                                                                                    |

|      |          |         |     | 10: Pø/16                                                                                                                                                                                                                                                     |

|      |          |         |     | 11: Pø/64                                                                                                                                                                                                                                                     |

|      |          |         |     | Note: Po: Peripheral clock                                                                                                                                                                                                                                    |

|                  |   |     |                |   |     |              |   |                          | Ρφ           | (MH                      | lz) |                          |   |     |              |   |     |              |

|------------------|---|-----|----------------|---|-----|--------------|---|--------------------------|--------------|--------------------------|-----|--------------------------|---|-----|--------------|---|-----|--------------|

| Bit              |   | 10  | * <sup>1</sup> |   | 12  | *1           |   | <b>14</b> * <sup>1</sup> |              | <b>16</b> * <sup>1</sup> |     | <b>18</b> * <sup>1</sup> |   | *1  | 20           |   |     |              |

| Rate<br>(bits/s) | n | N   | Error<br>(%)   | n | N   | Error<br>(%) | n | N                        | Error<br>(%) | n                        | N   | Error<br>(%)             | n | N   | Error<br>(%) | n | N   | Error<br>(%) |

| 110              | 2 | 177 | -0.25          | 2 | 212 | 0.03         | 2 | 248                      | -0.17        | 3                        | 70  | 0.03                     | 3 | 79  | -0.12        | 3 | 88  | -0.25        |

| 150              | 2 | 129 | 0.16           | 2 | 155 | 0.16         | 2 | 181                      | 0.16         | 2                        | 207 | 0.16                     | 2 | 233 | 0.16         | 3 | 64  | 0.16         |

| 300              | 2 | 64  | 0.16           | 2 | 77  | 0.16         | 2 | 90                       | 0.16         | 2                        | 103 | 0.16                     | 2 | 116 | 0.16         | 2 | 129 | 0.16         |

| 600              | 1 | 129 | 0.16           | 1 | 155 | 0.16         | 1 | 181                      | 0.16         | 1                        | 207 | 0.16                     | 1 | 233 | 0.16         | 2 | 64  | 0.16         |

| 1200             | 1 | 64  | 0.16           | 1 | 77  | 0.16         | 1 | 90                       | 0.16         | 1                        | 103 | 0.16                     | 1 | 116 | 0.16         | 1 | 129 | 0.16         |

| 2400             | 0 | 129 | 0.16           | 0 | 155 | 0.16         | 0 | 181                      | 0.16         | 0                        | 207 | 0.16                     | 0 | 233 | 0.16         | 1 | 64  | 0.16         |

| 4800             | 0 | 64  | 0.16           | 0 | 77  | 0.16         | 0 | 90                       | 0.16         | 0                        | 103 | 0.16                     | 0 | 116 | 0.16         | 0 | 129 | 0.16         |

| 9600             | 0 | 32  | -1.36          | 0 | 38  | 0.16         | 0 | 45                       | -0.93        | 0                        | 51  | 0.16                     | 0 | 58  | -0.69        | 0 | 64  | 0.16         |

| 14400            | 0 | 21  | -1.36          | 0 | 25  | 0.16         | 0 | 29                       | 1.27         | 0                        | 34  | -0.79                    | 0 | 38  | 0.16         | 0 | 42  | 0.94         |

| 19200            | 0 | 15  | 1.73           | 0 | 19  | -2.34        | 0 | 22                       | -0.93        | 0                        | 25  | 0.16                     | 0 | 28  | 1.02         | 0 | 32  | -1.36        |

| 28800            | 0 | 10  | -1.36          | 0 | 12  | 0.16         | 0 | 14                       | 1.27         | 0                        | 16  | 2.12                     | 0 | 19  | -2.34        | 0 | 21  | -1.36        |

| 31250            | 0 | 9   | 0.00           | 0 | 11  | 0.00         | 0 | 13                       | 0.00         | 0                        | 15  | 0.00                     | 0 | 17  | 0.00         | 0 | 19  | 0.00         |

| 38400            | 0 | 7   | 1.73           | 0 | 9   | -2.34        | 0 | 10                       | 3.57         | 0                        | 12  | 0.16                     | 0 | 14  | -2.34        | 0 | 15  | 1.73         |

### Table 17.4 Bit Rates and SCBRR Settings in Asynchronous Mode (1)

- 7. Interrupt Sources

- Maskable interrupt sources are provided.

- RSPI receive interrupt (receive buffer full)

- RSPI transmit interrupt (transmit buffer empty)

- RSPI error interrupt (mode fault and overrun)

- 8. Other Features

- Loopback mode is provided.

- The CMOS/open drain output switchover function is provided.

- The RSPI disable (initialization) function is provided.

Figure 18.1 shows an RSPI block diagram for one channel. When the CPU accesses the RSPI control registers, a peripheral bus (P-bus) is used.

| Bit | Bit Name | Initial<br>Value | R/W    | Description                                                                                                                                                                                                                                                                                                                                                                                        |

|-----|----------|------------------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | SPRF     | 0                | R/(W)* | RSPI Receive Buffer Full Flag                                                                                                                                                                                                                                                                                                                                                                      |

|     |          |                  |        | Indicates the status of the receive buffer for the RSPI<br>data register (SPDR). Upon completion of a serial<br>transfer with the SPRF bit 0, the RSPI transfers the<br>receive data from the shift register to SPDR, and<br>sets this bit to 1. This also means that the last bit of<br>transmit data has been sent because the RSPI<br>performs full-duplex synchronous serial<br>communication. |

|     |          |                  |        | If a serial transfer ends while the SPRF bit is 1, the<br>RSPI does not transfer the received data from the<br>shift register to SPDR. When the OVRF bit in SPSR<br>is 1, the SPRF bit cannot be changed from 0 to 1<br>(see section 18.4.7, Error Detection).                                                                                                                                     |

|     |          |                  |        | 0: No valid data in SPDR                                                                                                                                                                                                                                                                                                                                                                           |

|     |          |                  |        | 1: Valid data found in SPDR                                                                                                                                                                                                                                                                                                                                                                        |

|     |          |                  |        | [Clearing conditions]                                                                                                                                                                                                                                                                                                                                                                              |

|     |          |                  |        | <ul> <li>When 0 is written in SPRF after reading SPRF =<br/>1.</li> </ul>                                                                                                                                                                                                                                                                                                                          |

|     |          |                  |        | <ul> <li>When the DMAC is activated with an RXI<br/>interrupt and the DMAC reads data from SPDR<br/>as many as the number of states specified in<br/>SPFC.</li> </ul>                                                                                                                                                                                                                              |

|     |          |                  |        | • When the DTC is activated with an RXI interrupt<br>and the DTC reads data from SPDR as many as<br>the number of states specified in SPFC (except<br>when the transfer counter value of the DTC<br>becomes H'0000 and the DISEL bit is 1).                                                                                                                                                        |

|     |          |                  |        | Power-on reset                                                                                                                                                                                                                                                                                                                                                                                     |

|     |          |                  |        | [Setting condition]                                                                                                                                                                                                                                                                                                                                                                                |

|     |          |                  |        | • When serial reception of data as many as the number of states specified in SPFC is normally completed.                                                                                                                                                                                                                                                                                           |

| 6   | _        | 0                | R      | Reserved                                                                                                                                                                                                                                                                                                                                                                                           |

|     |          |                  |        | This bit is always read as 0. The write value should always be 0.                                                                                                                                                                                                                                                                                                                                  |

| Bit  | Bit Name | Initial<br>Value | R/W    | Description                                                                                                                                                                                                                               |

|------|----------|------------------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5    | SPTEF    | 1                | R/(W)* | RSPI Transmit Buffer Empty Flag                                                                                                                                                                                                           |

|      |          |                  |        | Indicates the status of the transmit buffer for the<br>RSPI data register (SPDR). When the SPTEF bit is<br>cleared and the shift register is empty, the data is<br>copied from the transmit buffer to the shift register.                 |

|      |          |                  |        | The CPU, DMAC and DTC can write to SPDR only<br>when the SPTEF bit is 1. If the CPU, the DMAC or<br>the DTC writes to the transmit buffer of SPDR when<br>the SPTEF bit is 0, the data in the transmit buffer is<br>not updated.          |

|      |          |                  |        | 0: Data found in the transmit buffer                                                                                                                                                                                                      |

|      |          |                  |        | 1: No data in the transmit buffer                                                                                                                                                                                                         |

|      |          |                  |        | [Clearing conditions]                                                                                                                                                                                                                     |

|      |          |                  |        | • When 0 is written in SPTEF after reading SPTEF = 1.                                                                                                                                                                                     |

|      |          |                  |        | • When the DMAC is activated with a TXI interrupt<br>and the DMAC writes data to SPDR as many as<br>the number of states specified in SPFC.                                                                                               |

|      |          |                  |        | • When the DTC is activated with a TXI interrupt<br>and the DTC writes data to SPDR as many as<br>the number of states specified in SPFC (except<br>when the transfer counter value of the DTC<br>becomes H'0000 and the DISEL bit is 1). |

|      |          |                  |        | [Setting conditions]                                                                                                                                                                                                                      |

|      |          |                  |        | Power-on reset                                                                                                                                                                                                                            |

|      |          |                  |        | <ul> <li>When serial reception of data as many as the<br/>number of states specified in SPFC is normally<br/>completed.</li> </ul>                                                                                                        |

| 4, 3 | _        | All 0            | R      | Reserved                                                                                                                                                                                                                                  |

|      |          |                  |        | This bit is always read as 0. The write value should always be 0.                                                                                                                                                                         |

# 18.4 Operation

In this section, the serial transfer period means a period from the beginning of driving valid data to the fetching of the final valid data.

### 18.4.1 Overview of RSPI Operations

The RSPI is capable of synchronous serial transfers in slave (SPI), single-master (SPI), and multimaster (SPI), slave (clock synchronous), and master (clock synchronous) modes. A particular mode of the RSPI can be selected by using the MSTR, MODFEN, and SPMS bits in the RSPI control register (SPCR). Table 18.5 gives the relationship between RSPI modes and SPCR settings, and a description of each mode.

| Item                                     | Slave<br>(SPI)      | Single-Master<br>(SPI)      | Multi-Master<br>(SPI)       | Slave<br>(Clock<br>Synchronous) | Master<br>(Clock<br>Synchronous) |

|------------------------------------------|---------------------|-----------------------------|-----------------------------|---------------------------------|----------------------------------|

| MSTR bit setting                         | 0                   | 1                           | 1                           | 0                               | 1                                |

| MODFEN bit setting                       | 0, 1                | 0                           | 1                           | 0                               | 0                                |

| SPMS bit setting                         | 0                   | 0                           | 0                           | 1                               | 1                                |

| RSPCK signal                             | Input               | Output                      | Output/Hi-Z                 | Input                           | Output                           |

| MOSI signal                              | Input               | Output                      | Output/Hi-Z                 | Input                           | Output                           |

| MISO signal                              | Output/Hi-Z         | Input                       | Input                       | Output/Hi-Z                     | Input                            |

| SSL0 signal                              | Input               | Output                      | Input                       | Hi-Z                            | Hi-Z                             |

| SSL1 to SSL3<br>signals                  | Hi-Z                | Output                      | Output/Hi-Z                 | Hi-Z                            | Hi-Z                             |

| Output pin mode                          | CMOS/<br>open-drain | CMOS/<br>open-drain         | CMOS/<br>open-drain         | CMOS/<br>open-drain             | CMOS/<br>open-drain              |

| SSL polarity<br>modification<br>function | Supported           | Supported                   | Supported                   | —                               | _                                |

| Clock source                             | RSPCK input         | On-chip baud rate generator | On-chip baud rate generator | RSPCK input                     | On-chip baud rate generator      |

### Table 18.5 Relationship between RSPI Modes and SPCR and Description of Each Mode

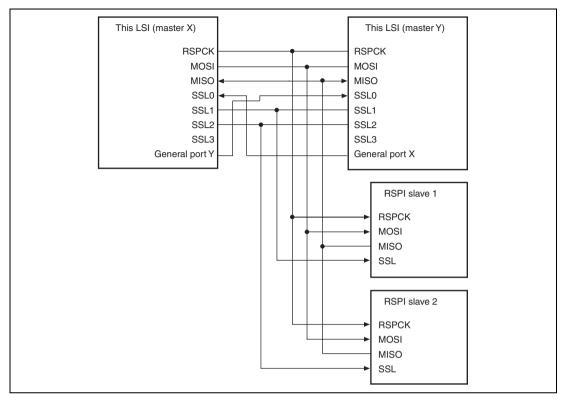

Figure 18.7 Multi-Master/Multi-Slave Configuration Example (This LSI = Master)

# Section 19 A/D Converter (ADC)

This LSI includes a successive approximation type 12-bit A/D converter.

## **19.1** Features

- 12-bit resolution

- Input channels: 16 channels

- High-speed conversion

When  $A\phi = 50$  MHz: Minimum 1.0 µs per channel

AD clock = 50 MHz, 50 conversion states

When  $A\phi = 40$  MHz: Minimum 1.25 µs per channel

AD clock = 40 MHz, 50 conversion states

- Three operating modes

- 2-channel scan mode: Performs a single A/D conversion on a maximum of two channels

- Single-cycle scan mode: Performs a single A/D conversion on the specified channel

- Continuous scan mode: Performs repetitive A/D conversion on the specified channel

- 16 A/D data registers

A/D conversion results are stored in 16-bit A/D data registers (ADDR) that correspond to the input channels.

• Sample-and-hold function

Sample-and-hold circuits are built into the A/D converter of this LSI, simplifying the configuration of the external analog input circuitry. Multiple channels can be sampled simultaneously because sample-and-hold circuits can be dedicated to channels 0 to 2.

- Group A (GrA): Analog input pins selected from channels 0, 1, and 2 can be simultaneously sampled.

- Three methods for starting A/D conversion Software: Setting of the ADST bit in ADCR Timer: TRGAN, TRG0N, TRG4AN, and TRG4BN from the MTU2 TRGAN, TRG4AN, and TRG4BN from the MTU2S External trigger: ADTRG (LSI pin)

- A/D synchronous conversion

A/D 2 can be started synchronously with A/D 1.

# 21.2 Pull-Up MOS Control by Pin Function

Table 21.9 shows the pull-up MOS control by pin function and the pull-up MOS control in each operating mode.

### Table 21.9Pull-Up MOS Control

|                                                                   |                   |                 |                     |        | When<br>Oscillation | When POE            |                     |

|-------------------------------------------------------------------|-------------------|-----------------|---------------------|--------|---------------------|---------------------|---------------------|

| Pin Function                                                      | Power-On<br>Reset | Manual<br>Reset | Software<br>Standby | Sleep  | Stop is<br>Detected | Function is<br>Used | Normal<br>Operation |

| I/O port input                                                    | Off               | On/off          | On/off              | On/off | On/off              | On/off              | On/off              |

| $\overline{\text{BREQ}}$ and $\overline{\text{WAIT}}$ input (BSC) |                   |                 |                     |        |                     |                     |                     |

| DREQ0 to DREQ3 input (DMAC)                                       |                   |                 |                     |        |                     |                     |                     |

| IRQ0 to IRQ6 input (INTC)                                         |                   |                 |                     |        |                     |                     |                     |

| MRES input (System control)                                       |                   |                 |                     |        |                     |                     |                     |

| POE0, POE4, and POE8 input (POE2)                                 |                   |                 |                     |        |                     |                     |                     |

| RXD0 to RXD3 input (SCI, SCIF)                                    |                   |                 |                     |        |                     |                     |                     |

| SCK0 to SCK3 input (SCI, SCIF)                                    |                   |                 |                     |        |                     |                     |                     |

| CRx0 input (RCAN-ET)                                              |                   |                 |                     |        |                     |                     |                     |

| ADTRG input (ADC)                                                 |                   |                 |                     |        |                     |                     |                     |

| SSLO and RSPCR input (RSPI)                                       |                   |                 |                     |        |                     |                     |                     |

| MISO and MOSI input (RSPI)                                        |                   |                 |                     |        |                     |                     |                     |

# 23.10 Usage Notes

### 23.10.1 Switching between User MAT and User Boot MAT

The user MAT and user boot MAT are allocated to the same address area. If the ROM area is accessed during switching between the user MAT and user boot MAT, an unexpected MAT may be accessed because the number of cycles required to access the ROM area depends on the internal bus status. When the ROM cache function is enabled, the previously stored data is left in the ROM cache even after MAT switching; note that a cache hit may occur when a newly selected MAT is accessed at the same address as the data stored in the cache. To avoid such unexpected behavior, take the following steps before and after MAT switching.

1. Modifying interrupt settings before MAT switching

There are two ways to avoid ROM area access due to an interrupt during MAT switching: one is to specify the interrupt vector fetch destination outside the ROM area through the vector base register (VBR) setting in the CPU, and the other is to mask interrupts. Note that NMI interrupts cannot be masked in this LSI; when masking interrupts to avoid ROM area access in this LSI, design the system so that no NMI is generated during MAT switching.

- Switching between MATs through a program outside the ROM area To avoid CPU instruction fetch in the ROM area during MAT switching, execute the MAT switching processing outside the ROM area.

- Performing dummy read of ROMMAT After writing to ROMMAT to switch between MATs, perform a dummy read of ROMMAT to ensure that the register write is completed.

- Flushing the ROM cache after MAT switching Disable (flush) the instructions or data in the ROM cache by writing a 1 to the RCF bit in RCCR.

### 26.3.2 Standby Control Register 2 (STBCR2)

STBCR2 is an 8-bit readable/writable register that controls the operation of modules in powerdown modes. STBCR2 is initialized to H'00 by a power-on reset but retains its previous value by a manual reset or in software standby mode. Only byte access is possible.

| Bit:           | 7          | 6         | 5         | 4 | 3 | 2 | 1         | 0 |

|----------------|------------|-----------|-----------|---|---|---|-----------|---|

|                | MSTP<br>10 | MSTP<br>9 | MSTP<br>8 | - | - | - | MSTP<br>4 | - |

| Initial value: | 0          | 0         | 0         | 0 | 0 | 0 | 0         | 0 |

| R/W:           | R/W        | R/W       | R/W       | R | R | R | R/W       | R |

| Bit    | Bit Name | Initial<br>Value | R/W | Description                                                                      |

|--------|----------|------------------|-----|----------------------------------------------------------------------------------|

| 7      | MSTP10   | 0                | R/W | Module Stop 10                                                                   |

|        |          |                  |     | When the MSTP10 bit is set to 1, the supply of the clock to the H-UDI is halted. |

|        |          |                  |     | 0: H-UDI runs.                                                                   |

|        |          |                  |     | 1: Clock supply to H-UDI halted.                                                 |

| 6      | MSTP9    | 0                | R/W | Module Stop 9                                                                    |

|        |          |                  |     | When the MSTP9 bit is set to 1, the supply of the clock to the UBC is halted.    |

|        |          |                  |     | 0: UBC runs.                                                                     |

|        |          |                  |     | 1: Clock supply to UBC halted.                                                   |

| 5      | MSTP8    | 0                | R/W | Module Stop 8                                                                    |

|        |          |                  |     | When the MSTP8 bit is set to 1, the supply of the clock to the DMAC is halted.   |

|        |          |                  |     | 0: DMAC runs.                                                                    |

|        |          |                  |     | 1: Clock supply to DMAC halted.                                                  |

| 4 to 2 |          | All 0            | R   | Reserved                                                                         |

|        |          |                  |     | These bits are always read as 0. The write value should always be 0.             |

| 1      | MSTP4    | 0                | R/W | Module Stop 4                                                                    |

|        |          |                  |     | When the MSTP4 bit is set to 1, the supply of the clock to the DTC is halted.    |

|        |          |                  |     | 0: DTC runs.                                                                     |

|        |          |                  |     | 1: Clock supply to DTC halted.                                                   |

| 0      | _        | 0                | R   | Reserved                                                                         |

| _      |          |                  |     | This bit is always read as 0. The write value should always be 0.                |

| Pin Function |                         | Pin State                              |             |        |                                             |       |                                             |                                 |                         |  |  |  |

|--------------|-------------------------|----------------------------------------|-------------|--------|---------------------------------------------|-------|---------------------------------------------|---------------------------------|-------------------------|--|--|--|

|              |                         | R                                      | eset State  |        | Power-Down State                            |       |                                             |                                 |                         |  |  |  |

|              |                         | Power-On                               |             |        |                                             |       | _                                           | <b>A W W</b>                    |                         |  |  |  |

| Туре         | Pin Name                | MCU Extension<br>Mode 2* <sup>10</sup> | Single Chip | Manual | Software<br>Standby                         | Sleep | Bus<br>Mastership<br>Release* <sup>10</sup> | Oscillation<br>Stop<br>Detected | POE<br>Function<br>Used |  |  |  |

| I/O port     | PD10 to PD15            | Z                                      |             | I/O    | Z<br>(MZIZDL in<br>HCPCR = 0)               | I/O   | I/O                                         | I/O*⁵                           | Z                       |  |  |  |

|              |                         |                                        |             |        | K* <sup>1</sup><br>(MZIZDL in<br>HCPCR = 1) |       |                                             |                                 |                         |  |  |  |

|              | PE4, PE7,<br>PE8, PE10  | Z                                      |             | I/O    | K*1                                         | I/O   | I/O                                         | I/O                             | I/O                     |  |  |  |

|              | PE0 to PE3,<br>PE5, PE6 | Z                                      |             | I/O    | Z<br>(MZIZEL in<br>HCPCR = 0)               | I/O   | I/O                                         | I/O* <sup>7</sup>               | Z                       |  |  |  |

|              |                         |                                        |             |        | K* <sup>1</sup><br>(MZIZEL in<br>HCPCR = 1) |       |                                             |                                 |                         |  |  |  |

|              | PE9, PE11 to Z<br>PE15  |                                        |             | I/O    | Z<br>(MZIZEH in<br>HCPCR = 0)               | I/O   | I/O                                         | I/O* <sup>6</sup>               | Z                       |  |  |  |

|              |                         |                                        |             |        | K* <sup>1</sup><br>(MZIZEH in<br>HCPCR = 1) |       |                                             |                                 |                         |  |  |  |

|              | PF0 to PF15             | Z                                      |             | I      | z                                           | I     | I                                           | I                               | I                       |  |  |  |

[Legend]

- I: Input

- O: Output

- H: High-level output

- L: Low-level output

- Z: High-impedance

- K: Input pins become high-impedance, and output pins retain their state.

- Notes: 1. Output pins become high-impedance when the HIZ bit in standby control register 3 (STBCR3) is set to 1.

- 2. Becomes output when the HIZCNT bit in the common control register (CMNCR) is set to 1.

- 3. Becomes output when the HIZMEM bit in the common control register (CMNCR) is set to 1.