# Microchip Technology - PIC16F688-E/P Datasheet

# E·XFL

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                  |  |  |  |  |  |

|----------------------------|-------------------------------------------------------------------------|--|--|--|--|--|

| Core Processor             | PIC                                                                     |  |  |  |  |  |

| Core Size                  | 8-Bit                                                                   |  |  |  |  |  |

| Speed                      | 20MHz                                                                   |  |  |  |  |  |

| Connectivity               | UART/USART                                                              |  |  |  |  |  |

| Peripherals                | Brown-out Detect/Reset, POR, WDT                                        |  |  |  |  |  |

| Number of I/O              | 12                                                                      |  |  |  |  |  |

| Program Memory Size        | 7KB (4K x 14)                                                           |  |  |  |  |  |

| Program Memory Type        | FLASH                                                                   |  |  |  |  |  |

| EEPROM Size                | 256 x 8                                                                 |  |  |  |  |  |

| RAM Size                   | 256 x 8                                                                 |  |  |  |  |  |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                               |  |  |  |  |  |

| Data Converters            | A/D 8x10b                                                               |  |  |  |  |  |

| Oscillator Type            | Internal                                                                |  |  |  |  |  |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                      |  |  |  |  |  |

| Mounting Type              | Through Hole                                                            |  |  |  |  |  |

| Package / Case             | 14-DIP (0.300", 7.62mm)                                                 |  |  |  |  |  |

| Supplier Device Package    | 14-PDIP                                                                 |  |  |  |  |  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f688-e-p |  |  |  |  |  |

|                            |                                                                         |  |  |  |  |  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### **Table of Contents**

| 1.0    | Device Overview                                               | 5    |

|--------|---------------------------------------------------------------|------|

| 2.0    | Memory Organization                                           | 7    |

| 3.0    | Clock Sources                                                 | . 21 |

| 4.0    | I/O Ports                                                     | . 33 |

| 5.0    | Timer0 Module                                                 |      |

| 6.0    | Timer1 Module with Gate Control                               | . 49 |

| 7.0    | Comparator Module                                             | . 55 |

| 8.0    | Analog-to-Digital Converter (A/D) Module                      | . 65 |

| 9.0    | Data EEPROM and Flash Program Memory Control                  |      |

| 10.0   | Enhanced Universal Asynchronous Receiver Transmitter (EUSART) | . 83 |

| 11.0   | Special Features of the CPU                                   | 109  |

| 12.0   | Instruction Set Summary                                       | 129  |

| 13.0   | Development Support                                           |      |

| 14.0   | Electrical Specifications                                     | 143  |

| 15.0   | DC and AC Characteristics Graphs and Tables                   | 163  |

| 16.0   | Packaging Information                                         | 185  |

| Appe   | ndix A: Data Sheet Revision History                           | 193  |

| Appe   | ndix B: Migrating from other PIC <sup>®</sup> Devices         | 193  |

|        |                                                               |      |

| On-lir | e Support                                                     | 199  |

|        | ms Information and Upgrade Hot Line                           |      |

|        | er Response                                                   |      |

|        |                                                               |      |

|        |                                                               |      |

# TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at **docerrors@microchip.com** or fax the **Reader Response Form** in the back of this data sheet to (480) 792-4150. We welcome your feedback.

#### Most Current Data Sheet

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000A is version A of document DS30000).

#### Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

Microchip's Worldwide Web site; http://www.microchip.com

Your local Microchip sales office (see last page)

When contacting a sales office, please specify which device, revision of silicon and data sheet (include literature number) you are using.

#### **Customer Notification System**

Register on our web site at www.microchip.com to receive the most current information on all of our products.

# **PIC16F688**

| Addr   | Name              | Bit 7        | Bit 6         | Bit 5        | Bit 4          | Bit 3         | Bit 2        | Bit 1        | Bit 0               | Value on<br>POR/BOR | Page                |

|--------|-------------------|--------------|---------------|--------------|----------------|---------------|--------------|--------------|---------------------|---------------------|---------------------|

| Bank 3 |                   |              |               |              |                |               |              |              |                     |                     |                     |

| 180h   | INDF              | Addressing   | this location | uses conte   | ents of FSR to | o address da  | ata memory ( | not a physic | al register)        | xxxx xxxx           | 20, 117             |

| 181h   | OPTION_REG        | RAPU         | INTEDG        | TOCS         | TOSE           | PSA           | PS2          | PS1          | PS0                 | 1111 1111           | 14, 117             |

| 182h   | PCL               | Program Co   | ounter's (PC  | ) Least Sigr | nificant Byte  |               |              |              |                     | 0000 0000           | 19, 117             |

| 183h   | STATUS            | IRP          | RP1           | RP0          | TO             | PD            | Z            | DC           | С                   | 0001 1xxx           | 13, 11              |

| 184h   | FSR               | Indirect Dat | ta Memory A   | ddress Poir  | nter           |               |              |              |                     | xxxx xxxx           | 20, 11              |

| 185h   | TRISA             | _            | _             | TRISA5       | TRISA4         | TRISA3        | TRISA2       | TRISA1       | TRISA0              | 11 1111             | 33, 11              |

| 186h   | _                 | Unimpleme    | ented         |              |                |               |              |              |                     | _                   | _                   |

| 187h   | TRISC             | _            | _             | TRISC5       | TRISC4         | TRISC3        | TRISC2       | TRISC1       | TRISC0              | 11 1111             | 42, 11              |

| 188h   | —                 | Unimpleme    | ented         |              |                |               |              |              |                     | _                   | _                   |

| 189h   | _                 | Unimpleme    | ented         |              |                |               |              |              |                     | _                   | _                   |

| 18Ah   | PCLATH            | _            | _             |              | Write Buffe    | r for upper 5 | bits of Prog | ram Countei  |                     | 0 0000              | 19, 11 <sup>-</sup> |

| 18Bh   | INTCON            | GIE          | PEIE          | T0IE         | INTE           | RAIE          | T0IF         | INTF         | RAIF <sup>(2)</sup> | 0000 000x           | 15, 11 <sup>-</sup> |

| 18Ch   | _                 | Unimpleme    | ented         |              |                |               |              |              |                     | _                   | _                   |

| 18Dh   | —                 | Unimpleme    | ented         |              |                |               |              |              |                     | _                   | _                   |

| 190h   | _                 | Unimpleme    | ented         |              |                |               |              |              |                     | _                   | _                   |

| 191h   | _                 | Unimpleme    | ented         |              |                |               |              |              |                     | _                   | _                   |

| 192h   | —                 | Unimpleme    | ented         |              |                |               |              |              |                     | _                   | _                   |

| 193h   | _                 | Unimpleme    | ented         |              |                |               |              |              |                     | _                   | _                   |

| 194h   | _                 | Unimpleme    | ented         |              |                |               |              |              |                     | _                   | _                   |

| 195h   | —                 | Unimpleme    | ented         |              |                |               |              |              |                     | _                   | _                   |

| 196h   | _                 | Unimpleme    | ented         |              |                |               |              |              |                     | _                   | _                   |

| 19Ah   | —                 | Unimpleme    | ented         |              |                |               |              |              |                     | _                   | _                   |

| 19Bh   | —                 | Unimpleme    | ented         |              |                |               |              |              |                     | _                   | _                   |

| 199h   | —                 | Unimpleme    | ented         |              |                |               |              |              |                     | _                   | _                   |

| 19Ah   | —                 | Unimpleme    | Unimplemented |              |                |               |              |              | _                   | _                   |                     |

| 19Bh   | —                 | Unimpleme    | Unimplemented |              |                |               |              |              |                     | _                   | _                   |

| 19Ch   |                   | Unimpleme    | Jnimplemented |              |                |               |              |              |                     | _                   | _                   |

| 19Dh   | _                 | Unimpleme    | ented         |              |                |               |              |              |                     | _                   | _                   |

| 19Eh   | _                 | Unimpleme    | ented         |              |                |               |              |              |                     | _                   | _                   |

| 19Fh   | — Unimplemented — |              |               |              |                |               |              | _            |                     |                     |                     |

#### PIC16F688 SPECIAL FUNCTION REGISTERS SUMMARY BANK 3 **TABLE 2-4:**

Note 1:

Other (non Power-up) Resets include MCLR Reset and Watchdog Timer Reset during normal operation. MCLR and WDT Reset does not affect the previous value data latch. The RAIF bit will be cleared upon Reset but will set again if the 2: mismatched exists.

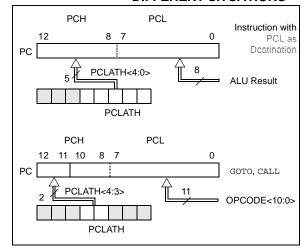

# 2.3 PCL and PCLATH

The Program Counter (PC) is 13 bits wide. The low byte comes from the PCL register, which is a readable and writable register. The high byte (PC<12:8>) is not directly readable or writable and comes from PCLATH. On any Reset, the PC is cleared. Figure 2-3 shows the two situations for the loading of the PC. The upper example in Figure 2-3 shows how the PC is loaded on a write to PCL (PCLATH<4:0>  $\rightarrow$  PCH). The lower example in Figure 2-3 shows how the PC is loaded during a CALL or GOTO instruction (PCLATH<4:3>  $\rightarrow$  PCH).

#### FIGURE 2-3: LOADING OF PC IN DIFFERENT SITUATIONS

### 2.3.1 COMPUTED GOTO

A computed GOTO is accomplished by adding an offset to the program counter (ADDWF PCL). When performing a table read using a computed GOTO method, care should be exercised if the table location crosses a PCL memory boundary (each 256-byte block). Refer to the Application Note AN556, *"Implementing a Table Read"* (DS00556).

# 2.3.2 STACK

The PIC16F688 family has an 8-level x 13-bit wide hardware stack (see Figure 2-1). The stack space is not part of either program or data space and the Stack Pointer is not readable or writable. The PC is PUSHed onto the stack when a CALL instruction is executed or an interrupt causes a branch. The stack is POPed in the event of a RETURN, RETLW or a RETFIE instruction execution. PCLATH is not affected by a PUSH or POP operation.

The stack operates as a circular buffer. This means that after the stack has been PUSHed eight times, the ninth push overwrites the value that was stored from the first push. The tenth push overwrites the second push (and so on).

Note 1: There are no Status bits to indicate Stack Overflow or Stack Underflow conditions.

2: There are no instructions/mnemonics called PUSH or POP. These are actions that occur from the execution of the CALL, RETURN, RETLW and RETFIE instructions or the vectoring to an interrupt address.

# 3.3 Clock Source Modes

Clock source modes can be classified as external or internal.

- External Clock modes rely on external circuitry for the clock source. Examples are: oscillator modules (EC mode), quartz crystal resonators or ceramic resonators (LP, XT and HS modes) and Resistor-Capacitor (RC) mode circuits.

- Internal clock sources are contained internally within the oscillator module. The oscillator module has two internal oscillators: the 8 MHz High-Frequency Internal Oscillator (HFINTOSC) and the 31 kHz Low-Frequency Internal Oscillator (LFINTOSC).

The system clock can be selected between external or internal clock sources via the System Clock Select (SCS) bit of the OSCCON register. See **Section 3.6 "Clock Switching"** for additional information.

# 3.4 External Clock Modes

# 3.4.1 OSCILLATOR START-UP TIMER (OST)

If the oscillator module is configured for LP, XT or HS modes, the Oscillator Start-up Timer (OST) counts 1024 oscillations from OSC1. This occurs following a Power-on Reset (POR) and when the Power-up Timer (PWRT) has expired (if configured), or a wake-up from Sleep. During this time, the program counter does not increment and program execution is suspended. The OST ensures that the oscillator circuit, using a quartz crystal resonator or ceramic resonator, has started and is providing a stable system clock to the oscillator module. When switching between clock sources, a delay is required to allow the new clock to stabilize. These oscillator delays are shown in Table 3-1.

In order to minimize latency between external oscillator start-up and code execution, the Two-Speed Clock Start-up mode can be selected (see Section 3.7 "Two-Speed Clock Start-up Mode").

| Switch From       | Switch To            | Frequency                  | Oscillator Delay                 |

|-------------------|----------------------|----------------------------|----------------------------------|

| Sleep/POR         | LFINTOSC<br>HFINTOSC | 31 kHz<br>125 kHz to 8 MHz | Oscillator Warm-Up Delay (Twarm) |

| Sleep/POR         | EC, RC               | DC – 20 MHz                | 2 instruction cycles             |

| LFINTOSC (31 kHz) | EC, RC               | DC – 20 MHz                | 1 cycle of each                  |

| Sleep/POR         | LP, XT, HS           | 32 kHz to 20 MHz           | 1024 Clock Cycles (OST)          |

| LFINTOSC (31 kHz) | HFINTOSC             | 125 kHz to 8 MHz           | 1 μs (approx.)                   |

#### TABLE 3-1: OSCILLATOR DELAY EXAMPLES

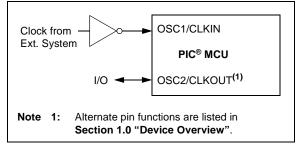

### 3.4.2 EC MODE

The External Clock (EC) mode allows an externally generated logic level as the system clock source. When operating in this mode, an external clock source is connected to the OSC1 input and the OSC2 is available for general purpose I/O. Figure 3-2 shows the pin connections for EC mode.

The Oscillator Start-up Timer (OST) is disabled when EC mode is selected. Therefore, there is no delay in operation after a Power-on Reset (POR) or wake-up from Sleep. Because the PIC<sup>®</sup> MCU design is fully static, stopping the external clock input will have the effect of halting the device while leaving all data intact. Upon restarting the external clock, the device will resume operation as if no time had elapsed.

### FIGURE 3-2:

#### EXTERNAL CLOCK (EC) MODE OPERATION

#### 3.5.3 LFINTOSC

The Low-Frequency Internal Oscillator (LFINTOSC) is an uncalibrated 31 kHz internal clock source.

The output of the LFINTOSC connects to a postscaler and multiplexer (see Figure 3-1). Select 31 kHz, via software, using the IRCF<2:0> bits of the OSCCON register. See **Section 3.5.4 "Frequency Select Bits (IRCF)**" for more information. The LFINTOSC is also the frequency for the Power-up Timer (PWRT), Watchdog Timer (WDT) and Fail-Safe Clock Monitor (FSCM).

The LFINTOSC is enabled by selecting 31 kHz (IRCF<2:0> bits of the OSCCON register = 000) as the system clock source (SCS bit of the OSCCON register = 1), or when any of the following are enabled:

- Two-Speed Start-up IESO bit of the Configuration Word register = 1 and IRCF<2:0> bits of the OSCCON register = 000

- Power-up Timer (PWRT)

- Watchdog Timer (WDT)

- Fail-Safe Clock Monitor (FSCM)

The LF Internal Oscillator (LTS) bit of the OSCCON register indicates whether the LFINTOSC is stable or not.

#### 3.5.4 FREQUENCY SELECT BITS (IRCF)

The output of the 8 MHz HFINTOSC and 31 kHz LFINTOSC connects to a postscaler and multiplexer (see Figure 3-1). The Internal Oscillator Frequency Select bits IRCF<2:0> of the OSCCON register select the frequency output of the internal oscillators. One of eight frequencies can be selected via software:

- 8 MHz

- 4 MHz (Default after Reset)

- 2 MHz

- 1 MHz

- 500 kHz

- 250 kHz

- 125 kHz

- 31 kHz (LFINTOSC)

| Note: | Following any Reset, the IRCF<2:0> bits of<br>the OSCCON register are set to '110' and<br>the frequency selection is set to 4 MHz. |  |  |  |  |

|-------|------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

|       | The user can modify the IRCF bits to select a different frequency.                                                                 |  |  |  |  |

### 3.5.5 HF AND LF INTOSC CLOCK SWITCH TIMING

When switching between the LFINTOSC and the HFINTOSC, the new oscillator may already be shut down to save power (see Figure 3-6). If this is the case, there is a delay after the IRCF<2:0> bits of the OSCCON register are modified before the frequency selection takes place. The LTS and HTS bits of the OSCCON register will reflect the current active status of the LFINTOSC and HFINTOSC oscillators. The timing of a frequency selection is as follows:

- 1. IRCF<2:0> bits of the OSCCON register are modified.

- 2. If the new clock is shut down, a clock start-up delay is started.

- 3. Clock switch circuitry waits for a falling edge of the current clock.

- 4. CLKOUT is held low and the clock switch circuitry waits for a rising edge in the new clock.

- CLKOUT is now connected with the new clock. LTS and HTS bits of the OSCCON register are updated as required.

- 6. Clock switch is complete.

See Figure 3-1 for more details.

If the internal oscillator speed selected is between 8 MHz and 125 kHz, there is no start-up delay before the new frequency is selected. This is because the old and new frequencies are derived from the HFINTOSC via the postscaler and multiplexer.

Start-up delay specifications are located in the **Section 14.0 "Electrical Specifications"**, under the AC Specifications (Oscillator Module).

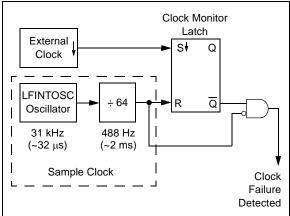

# 3.8 Fail-Safe Clock Monitor

The Fail-Safe Clock Monitor (FSCM) allows the device to continue operating should the external oscillator fail. The FSCM can detect oscillator failure any time after the Oscillator Start-up Timer (OST) has expired. The FSCM is enabled by setting the FCMEN bit in the Configuration Word register (CONFIG). The FSCM is applicable to all external oscillator modes (LP, XT, HS, EC, RC and RCIO).

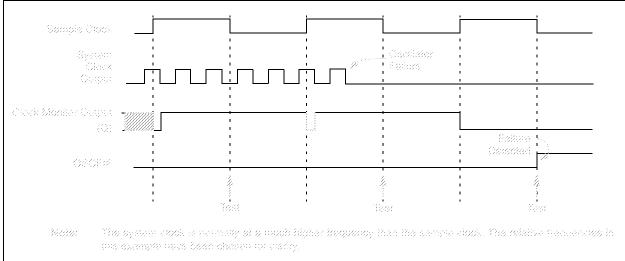

FIGURE 3-8: FSCM BLOCK DIAGRAM

# 3.8.1 FAIL-SAFE DETECTION

The FSCM module detects a failed oscillator by comparing the external oscillator to the FSCM sample clock. The sample clock is generated by dividing the LFINTOSC by 64. See Figure 3-8. Inside the fail detector block is a latch. The external clock sets the latch on each falling edge of the external clock. The sample clock clears the latch on each rising edge of the sample clock. A failure is detected when an entire half-cycle of the sample clock elapses before the primary clock goes low.

### 3.8.2 FAIL-SAFE OPERATION

When the external clock fails, the FSCM switches the device clock to an internal clock source and sets the bit flag OSFIF of the PIR2 register. Setting this flag will generate an interrupt if the OSFIE bit of the PIE2 register is also set. The device firmware can then take steps to mitigate the problems that may arise from a failed clock. The system clock will continue to be sourced from the internal clock source until the device firmware successfully restarts the external oscillator and switches back to external operation.

The internal clock source chosen by the FSCM is determined by the IRCF<2:0> bits of the OSCCON register. This allows the internal oscillator to be configured before a failure occurs.

# 3.8.3 FAIL-SAFE CONDITION CLEARING

The Fail-Safe condition is cleared after a Reset, executing a SLEEP instruction or toggling the SCS bit of the OSCCON register. When the SCS bit is toggled, the OST is restarted. While the OST is running, the device continues to operate from the INTOSC selected in OSCCON. When the OST times out, the Fail-Safe condition is cleared and the device will be operating from the external clock source. The Fail-Safe condition must be cleared before the OSFIF flag can be cleared.

# 3.8.4 RESET OR WAKE-UP FROM SLEEP

The FSCM is designed to detect an oscillator failure after the Oscillator Start-up Timer (OST) has expired. The OST is used after waking up from Sleep and after any type of Reset. The OST is not used with the EC or RC Clock modes so that the FSCM will be active as soon as the Reset or wake-up has completed. When the FSCM is enabled, the Two-Speed Start-up is also enabled. Therefore, the device will always be executing code while the OST is operating.

Note: Due to the wide range of oscillator start-up times, the Fail-Safe circuit is not active during oscillator start-up (i.e., after exiting Reset or Sleep). After an appropriate amount of time, the user should check the OSTS bit of the OSCCON register to verify the oscillator start-up and that the system clock switchover has successfully completed.

# **PIC16F688**

| Name                  | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0  | Value on<br>POR, BOR | Value on<br>all other<br>Resets <sup>(1)</sup> |

|-----------------------|-------|-------|-------|-------|-------|-------|-------|--------|----------------------|------------------------------------------------|

| CONFIG <sup>(2)</sup> | CPD   | CP    | MCLRE | PWRTE | WDTE  | FOSC2 | FOSC1 | FOSC0  | -                    | _                                              |

| INTCON                | GIE   | PEIE  | TOIE  | INTE  | RAIE  | T0IF  | INTF  | RAIF   | 0000 000x            | 0000 000x                                      |

| OSCCON                | _     | IRCF2 | IRCF1 | IRCF0 | OSTS  | HTS   | LTS   | SCS    | -110 x000            | -110 x000                                      |

| OSCTUNE               | _     | _     | —     | TUN4  | TUN3  | TUN2  | TUN1  | TUN0   | 0 0000               | u uuuu                                         |

| PIE1                  | EEIE  | ADIE  | RCIE  | C2IE  | C1IE  | OSFIE | TXIE  | TMR1IE | 0000 0000            | 0000 0000                                      |

| PIR1                  | EEIF  | ADIF  | RCIF  | C2IF  | C1IF  | OSFIF | TXIF  | TMR1IF | 0000 0000            | 0000 0000                                      |

$\label{eq:local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_$

Note 1: Other (non Power-up) Resets include MCLR Reset and Watchdog Timer Reset during normal operation.

2: See Configuration Word register (CONFIG) for operation of all register bits.

# 4.2.5.2 RA1/AN1/C1IN-/VREF/ICSPCLK

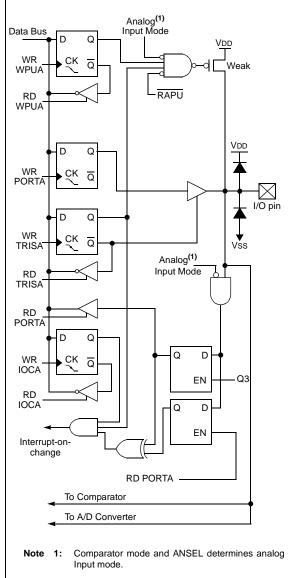

Figure 4-2 shows the diagram for this pin. The RA1 pin is configurable to function as one of the following:

- a general purpose I/O

- an analog input for the A/D

- an analog input to the comparator

- a voltage reference input for the A/D

- In-Circuit Serial Programming<sup>™</sup> clock

# FIGURE 4-2: BLOCK DIAGRAM OF RA1

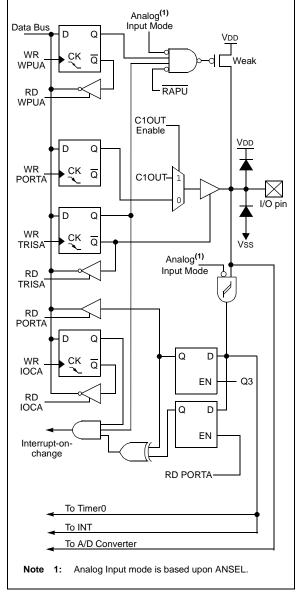

# 4.2.5.3 RA2/AN2/T0CKI/INT/C1OUT

Figure 4-3 shows the diagram for this pin. The RA2 pin is configurable to function as one of the following:

- a general purpose I/O

- an analog input for the A/D

- the clock input for Timer0

- an external edge triggered interrupt

- a digital output from the comparator

# FIGURE 4-3: BLOCK DIAGRAM OF RA2

### 7.10 Comparator Voltage Reference

The Comparator Voltage Reference module provides an internally generated voltage reference for the comparators. The following features are available:

- Independent from Comparator operation

- Two 16-level voltage ranges

- Output clamped to Vss

- Ratiometric with VDD

The VRCON register (Figure 7-3) controls the Voltage Reference module shown in Figure 7-8.

#### 7.10.1 INDEPENDENT OPERATION

The comparator voltage reference is independent of the comparator configuration. Setting the VREN bit of the VRCON register will enable the voltage reference.

#### 7.10.2 OUTPUT VOLTAGE SELECTION

The CVREF voltage reference has 2 ranges with 16 voltage levels in each range. Range selection is controlled by the VRR bit of the VRCON register. The 16 levels are set with the VR<3:0> bits of the VRCON register.

The CVREF output voltage is determined by the following equations:

#### EQUATION 7-1: CVREF OUTPUT VOLTAGE

```

V_{RR} = 1 (low range):

CV_{REF} = (VR < 3:0 > /24) \times VDD

V_{RR} = 0 (high range):

CV_{REF} = (VDD/4) + (VR < 3:0 > \times VDD/32)

```

The full range of VSS to VDD cannot be realized due to the construction of the module. See Figure 7-8.

#### 7.10.3 OUTPUT CLAMPED TO Vss

The CVREF output voltage can be set to Vss with no power consumption by configuring VRCON as follows:

- VREN = 0

- VRR = 1

- VR<3:0> = 0000

This allows the comparator to detect a zero-crossing while not consuming additional CVREF module current.

#### 7.10.4 OUTPUT RATIOMETRIC TO VDD

The comparator voltage reference is VDD derived and therefore, the CVREF output changes with fluctuations in VDD. The tested absolute accuracy of the Comparator Voltage Reference can be found in **Section 14.0 "Electrical Specifications"**.

#### REGISTER 7-3: VRCON: VOLTAGE REFERENCE CONTROL REGISTER

| R/W-0 | U-0 | R/W-0 | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|-------|-----|-------|-----|-------|-------|-------|-------|

| VREN  | —   | VRR   | —   | VR3   | VR2   | VR1   | VR0   |

| bit 7 |     |       |     |       |       |       | bit 0 |

|       |     |       |     |       |       |       |       |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

| bit 7   | VREN: CVREF Enable bit                                                                                                                                                                   |

|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | 1 = CVREF circuit powered on<br>0 = CVREF circuit powered down, no IDD drain and CVREF = VSS.                                                                                            |

| bit 6   | Unimplemented: Read as '0'                                                                                                                                                               |

| bit 5   | VRR: CVREF Range Selection bit                                                                                                                                                           |

|         | 1 = Low range<br>0 = High range                                                                                                                                                          |

| bit 4   | Unimplemented: Read as '0'                                                                                                                                                               |

| bit 3-0 | <b>VR&lt;3:0&gt;:</b> CVREF Value Selection bits $(0 \le VR<3:0>\le 15)$<br><u>When VRR = 1</u> : CVREF = (VR<3:0>/24) * VDD<br><u>When VRR = 0</u> : CVREF = VDD/4 + (VR<3:0>/32) * VDD |

|         |                                                                                                                                                                                          |

### 10.3 EUSART Baud Rate Generator (BRG)

The Baud Rate Generator (BRG) is an 8-bit or 16-bit timer that is dedicated to the support of both the asynchronous and synchronous EUSART operation. By default, the BRG operates in 8-bit mode. Setting the BRG16 bit of the BAUDCTL register selects 16-bit mode.

The SPBRGH, SPBRG register pair determines the period of the free running baud rate timer. In Asynchronous mode the multiplier of the baud rate period is determined by both the BRGH bit of the TXSTA register and the BRG16 bit of the BAUDCTL register. In Synchronous mode, the BRGH bit is ignored.

Table 10-3 contains the formulas for determining the baud rate. Example 10-1 provides a sample calculation for determining the baud rate and baud rate error.

Typical baud rates and error values for various asynchronous modes have been computed for your convenience and are shown in Table 10-3. It may be advantageous to use the high baud rate (BRGH = 1), or the 16-bit BRG (BRG16 = 1) to reduce the baud rate error. The 16-bit BRG mode is used to achieve slow baud rates for fast oscillator frequencies.

Writing a new value to the SPBRGH, SPBRG register pair causes the BRG timer to be reset (or cleared). This ensures that the BRG does not wait for a timer overflow before outputting the new baud rate. If the system clock is changed during an active receive operation, a receive error or data loss may result. To avoid this problem, check the status of the RCIDL bit to make sure that the receive operation is Idle before changing the system clock.

#### EXAMPLE 10-1: CALCULATING BAUD RATE ERROR

| For a device with Fosc of 16 MHz, desired baud rate of 9600, Asynchronous mode, 8-bit BRG: |

|--------------------------------------------------------------------------------------------|

| Desired Baud Rate = $\frac{FOSC}{64([SPBRGH:SPBRG] + 1)}$                                  |

| Solving for SPBRGH:SPBRG:                                                                  |

| $X = \frac{FOSC}{\frac{Desired Baud Rate}{64} - 1}$                                        |

| $=\frac{\frac{16000000}{9600}}{64}-1$                                                      |

| = [25.042] = 25                                                                            |

| Calculated Baud Rate = $\frac{16000000}{64(25+1)}$                                         |

| = 9615                                                                                     |

| Error = $\frac{Calc. Baud Rate - Desired Baud Rate}{Desired Baud Rate}$                    |

| $=\frac{(9615-9600)}{9600} = 0.16\%$                                                       |

| C    | onfiguration Bits |      | Configuration Bits<br>BRG/EUSART Mode |                   |  | Baud Rate Formula |  |  |

|------|-------------------|------|---------------------------------------|-------------------|--|-------------------|--|--|

| SYNC | BRG16             | BRGH | BRG/EUSART Mode                       | Bauu Kale Formula |  |                   |  |  |

| 0    | 0                 | 0    | 8-bit/Asynchronous                    | Fosc/[64 (n+1)]   |  |                   |  |  |

| 0    | 0                 | 1    | 8-bit/Asynchronous                    |                   |  |                   |  |  |

| 0    | 1                 | 0    | 16-bit/Asynchronous                   | Fosc/[16 (n+1)]   |  |                   |  |  |

| 0    | 1                 | 1    | 16-bit/Asynchronous                   |                   |  |                   |  |  |

| 1    | 0                 | х    | 8-bit/Synchronous                     | Fosc/[4 (n+1)]    |  |                   |  |  |

| 1    | 1                 | x    | 16-bit/Synchronous                    |                   |  |                   |  |  |

### TABLE 10-3: BAUD RATE FORMULAS

**Legend:** x = Don't care, n = value of SPBRGH, SPBRG register pair

#### TABLE 10-4: REGISTERS ASSOCIATED WITH THE BAUD RATE GENERATOR

| Name    | Bit 7  | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Value on<br>POR, BOR | Value on<br>all other<br>Resets |

|---------|--------|-------|-------|-------|-------|-------|-------|-------|----------------------|---------------------------------|

| BAUDCTL | ABDOVF | RCIDL | _     | SCKP  | BRG16 | _     | WUE   | ABDEN | 01-0 0-00            | 01-0 0-00                       |

| RCSTA   | SPEN   | RX9   | SREN  | CREN  | ADDEN | FERR  | OERR  | RX9D  | x000 000x            | 0000 000x                       |

| SPBRG   | BRG7   | BRG6  | BRG5  | BRG4  | BRG3  | BRG2  | BRG1  | BRG0  | 0000 0000            | 0000 0000                       |

| SPBRGH  | BRG15  | BRG14 | BRG13 | BRG12 | BRG11 | BRG10 | BRG9  | BRG8  | 0000 0000            | 0000 0000                       |

| TXSTA   | CSRC   | TX9   | TXEN  | SYNC  | SENDB | BRGH  | TRMT  | TX9D  | 0000 0010            | 0000 0010                       |

Legend: x = unknown, - = unimplemented read as '0'. Shaded cells are not used for the Baud Rate Generator.

| U-0             | U-0                                 | U-0              | R/W-0          | R/W-1            | R/W-0              | R/W-0           | R/W-0  |  |  |  |  |

|-----------------|-------------------------------------|------------------|----------------|------------------|--------------------|-----------------|--------|--|--|--|--|

| _               | _                                   | —                | WDTPS3         | WDTPS2           | WDTPS1             | WDTPS0          | SWDTEN |  |  |  |  |

| bit 7           |                                     |                  |                | 1                |                    |                 | bit C  |  |  |  |  |

|                 |                                     |                  |                |                  |                    |                 |        |  |  |  |  |

| Legend:         |                                     |                  |                |                  |                    |                 |        |  |  |  |  |

| R = Readable    | bit                                 | W = Writable     | bit            | U = Unimpler     | mented bit, read   | d as '0'        |        |  |  |  |  |

| -n = Value at I | POR                                 | '1' = Bit is set |                | '0' = Bit is cle |                    | x = Bit is unkr | nown   |  |  |  |  |

|                 |                                     |                  |                |                  |                    |                 |        |  |  |  |  |

| bit 7-5         | Unimplemen                          | ted: Read as '   | )'             |                  |                    |                 |        |  |  |  |  |

| oit 4-1         | -                                   | >: Watchdog Tir  |                | elect bits       |                    |                 |        |  |  |  |  |

|                 | Bit Value = F                       | -                |                |                  |                    |                 |        |  |  |  |  |

|                 | 0000 = 1:32                         | 2                |                |                  |                    |                 |        |  |  |  |  |

|                 | 0001 = 1:64                         | Ļ                |                |                  |                    |                 |        |  |  |  |  |

|                 | 0010 = 1:128                        |                  |                |                  |                    |                 |        |  |  |  |  |

|                 | 0011 = 1:25                         | 56               |                |                  |                    |                 |        |  |  |  |  |

|                 | 0100 = 1:51                         | 2 (Reset value)  |                |                  |                    |                 |        |  |  |  |  |

|                 | 0101 = 1:10                         | )24              |                |                  |                    |                 |        |  |  |  |  |

|                 | 0110 = 1:20                         | )48              |                |                  |                    |                 |        |  |  |  |  |

|                 | 0111 = 1:40                         | 96               |                |                  |                    |                 |        |  |  |  |  |

|                 | 1000 = 1:81                         | 92               |                |                  |                    |                 |        |  |  |  |  |

|                 | 1001 = 1:16                         |                  |                |                  |                    |                 |        |  |  |  |  |

|                 | 1010 = 1:32                         |                  |                |                  |                    |                 |        |  |  |  |  |

|                 | 1011 = 1:65                         |                  |                |                  |                    |                 |        |  |  |  |  |

|                 | 1100 = Res                          |                  |                |                  |                    |                 |        |  |  |  |  |

|                 | 1101 = Res                          |                  |                |                  |                    |                 |        |  |  |  |  |

|                 | 1110 = Res                          |                  |                |                  |                    |                 |        |  |  |  |  |

|                 | 1111 = Res                          |                  |                |                  |                    |                 |        |  |  |  |  |

| bit 0           | SWDTEN: So                          | oftware Enable   | or Disable the | e Watchdog Tir   | mer <sup>(1)</sup> |                 |        |  |  |  |  |

|                 | 1 = WDT is tu                       |                  |                |                  |                    |                 |        |  |  |  |  |

|                 | 0 = WDT is tu                       | urned off (Rese  | t value)       |                  |                    |                 |        |  |  |  |  |

|                 | VDTE Configura<br>nfiguration bit = |                  |                |                  |                    |                 | f WDTE |  |  |  |  |

# **REGISTER 11-2: WDTCON: WATCHDOG TIMER CONTROL REGISTER**

#### TABLE 11-8: SUMMARY OF REGISTERS ASSOCIATED WITH WATCHDOG TIMER

| Name       | Bit 7 | Bit 6  | Bit 5 | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Value on<br>POR, BOR | Value on<br>all other<br>Resets |

|------------|-------|--------|-------|--------|--------|--------|--------|--------|----------------------|---------------------------------|

| WDTCON     | _     | —      | _     | WDTPS3 | WDTPS2 | WSTPS1 | WDTPS0 | SWDTEN | 0 1000               | 0 1000                          |

| OPTION_REG | RAPU  | INTEDG | TOCS  | TOSE   | PSA    | PS2    | PS1    | PS0    | 1111 1111            | 1111 1111                       |

| CONFIG     | CPD   | CP     | MCLRE | PWRTE  | WDTE   | FOSC2  | FOSC1  | FOSC0  | —                    | —                               |

Legend: Shaded cells are not used by the Watchdog Timer.

Note 1: See Register 11.0 for operation of all Configuration Word register bits.

# **PIC16F688**

| MOVF             | Move f                                                                                                                                                                                                                                                                               |  |  |  |  |  |  |  |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| Syntax:          | [ <i>label</i> ] MOVF f,d                                                                                                                                                                                                                                                            |  |  |  |  |  |  |  |

| Operands:        | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                                                                                                                                                   |  |  |  |  |  |  |  |

| Operation:       | (f) $\rightarrow$ (dest)                                                                                                                                                                                                                                                             |  |  |  |  |  |  |  |

| Status Affected: | Z                                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |  |

| Description:     | The contents of register f is<br>moved to a destination dependent<br>upon the status of d. If $d = 0$ ,<br>destination is W register. If $d = 1$ ,<br>the destination is file register f<br>itself. $d = 1$ is useful to test a file<br>register since status flag Z is<br>affected. |  |  |  |  |  |  |  |

| Words:           | 1                                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |  |

| Cycles:          | 1                                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |  |

| Example:         | MOVF FSR, 0                                                                                                                                                                                                                                                                          |  |  |  |  |  |  |  |

|                  | After Instruction<br>W = value in FSR<br>register<br>Z = 1                                                                                                                                                                                                                           |  |  |  |  |  |  |  |

| MOVWF            | Move W to f                                |

|------------------|--------------------------------------------|

| Syntax:          | [label] MOVWF f                            |

| Operands:        | $0 \le f \le 127$                          |

| Operation:       | $(W) \to (f)$                              |

| Status Affected: | None                                       |

| Description:     | Move data from W register to register 'f'. |

| Words:           | 1                                          |

| Cycles:          | 1                                          |

| Example:         | MOVW OPTION<br>F                           |

|                  | Before Instruction                         |

|                  | OPTION = 0xFF                              |

|                  | W = 0x4F<br>After Instruction              |

|                  | OPTION = 0x4F                              |

|                  | W = 0x4F                                   |

|                  |                                            |

| MOVLW            | Move literal to W                                                                                   |  |  |  |  |  |  |

|------------------|-----------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Syntax:          | [ <i>label</i> ] MOVLW k                                                                            |  |  |  |  |  |  |

| Operands:        | $0 \leq k \leq 255$                                                                                 |  |  |  |  |  |  |

| Operation:       | $k \rightarrow (W)$                                                                                 |  |  |  |  |  |  |

| Status Affected: | None                                                                                                |  |  |  |  |  |  |

| Description:     | The eight-bit literal 'k' is loaded into<br>W register. The "don't cares" will<br>assemble as '0's. |  |  |  |  |  |  |

| Words:           | 1                                                                                                   |  |  |  |  |  |  |

| Cycles:          | 1                                                                                                   |  |  |  |  |  |  |

| Example:         | MOVLW 0x5A                                                                                          |  |  |  |  |  |  |

|                  | After Instruction<br>W = 0x5A                                                                       |  |  |  |  |  |  |

| NOP              | No Operation  |

|------------------|---------------|

| Syntax:          | [label] NOP   |

| Operands:        | None          |

| Operation:       | No operation  |

| Status Affected: | None          |

| Description:     | No operation. |

| Words:           | 1             |

| Cycles:          | 1             |

| Example:         | NOP           |

# 13.2 MPASM Assembler

The MPASM Assembler is a full-featured, universal macro assembler for all PIC MCUs.

The MPASM Assembler generates relocatable object files for the MPLINK Object Linker, Intel<sup>®</sup> standard HEX files, MAP files to detail memory usage and symbol reference, absolute LST files that contain source lines and generated machine code and COFF files for debugging.

The MPASM Assembler features include:

- Integration into MPLAB IDE projects

- User-defined macros to streamline assembly code

- Conditional assembly for multi-purpose source files

- Directives that allow complete control over the assembly process

# 13.3 MPLAB C18 and MPLAB C30 C Compilers

The MPLAB C18 and MPLAB C30 Code Development Systems are complete ANSI C compilers for Microchip's PIC18 and PIC24 families of microcontrollers and the dsPIC30 and dsPIC33 family of digital signal controllers. These compilers provide powerful integration capabilities, superior code optimization and ease of use not found with other compilers.

For easy source level debugging, the compilers provide symbol information that is optimized to the MPLAB IDE debugger.

# 13.4 MPLINK Object Linker/ MPLIB Object Librarian

The MPLINK Object Linker combines relocatable objects created by the MPASM Assembler and the MPLAB C18 C Compiler. It can link relocatable objects from precompiled libraries, using directives from a linker script.

The MPLIB Object Librarian manages the creation and modification of library files of precompiled code. When a routine from a library is called from a source file, only the modules that contain that routine will be linked in with the application. This allows large libraries to be used efficiently in many different applications.

The object linker/library features include:

- Efficient linking of single libraries instead of many smaller files

- Enhanced code maintainability by grouping related modules together

- Flexible creation of libraries with easy module listing, replacement, deletion and extraction

# 13.5 MPLAB ASM30 Assembler, Linker and Librarian

MPLAB ASM30 Assembler produces relocatable machine code from symbolic assembly language for dsPIC30F devices. MPLAB C30 C Compiler uses the assembler to produce its object file. The assembler generates relocatable object files that can then be archived or linked with other relocatable object files and archives to create an executable file. Notable features of the assembler include:

- Support for the entire dsPIC30F instruction set

- · Support for fixed-point and floating-point data

- · Command line interface

- Rich directive set

- Flexible macro language

- MPLAB IDE compatibility

# 13.6 MPLAB SIM Software Simulator

The MPLAB SIM Software Simulator allows code development in a PC-hosted environment by simulating the PIC MCUs and dsPIC<sup>®</sup> DSCs on an instruction level. On any given instruction, the data areas can be examined or modified and stimuli can be applied from a comprehensive stimulus controller. Registers can be logged to files for further run-time analysis. The trace buffer and logic analyzer display extend the power of the simulator to record and track program execution, actions on I/O, most peripherals and internal registers.

The MPLAB SIM Software Simulator fully supports symbolic debugging using the MPLAB C18 and MPLAB C30 C Compilers, and the MPASM and MPLAB ASM30 Assemblers. The software simulator offers the flexibility to develop and debug code outside of the hardware laboratory environment, making it an excellent, economical software development tool.

| DC CHARACTERISTICS           |                             |     | ard Oper<br>ting temp |       |       | nditions (unless otherwise stated) $-40^{\circ}C \le T_A \le +85^{\circ}C$ for industrial |                                               |  |  |

|------------------------------|-----------------------------|-----|-----------------------|-------|-------|-------------------------------------------------------------------------------------------|-----------------------------------------------|--|--|

| Param Device Characteristics |                             | Min | Typt                  | Max   | Units | Conditions                                                                                |                                               |  |  |

| No.                          | Device Characteristics      |     | Тур†                  | IVIAX | Units | Vdd                                                                                       | Note                                          |  |  |

| D020                         | Power-down Base             | _   | 0.05                  | 1.2   | μA    | 2.0                                                                                       | WDT, BOR, Comparators, VREF and               |  |  |

|                              | Current(IPD) <sup>(2)</sup> |     | 0.15                  | 1.5   | μA    | 3.0                                                                                       | T1OSC disabled                                |  |  |

|                              |                             | _   | 0.35                  | 1.8   | μA    | 5.0                                                                                       |                                               |  |  |

|                              |                             | _   | 150                   | 500   | nA    | 3.0                                                                                       | $-40^{\circ}C \le TA \le +25^{\circ}C$        |  |  |

| D021                         |                             | _   | 1.0                   | 2.2   | μA    | 2.0                                                                                       | WDT Current <sup>(1)</sup>                    |  |  |

|                              |                             | _   | 2.0                   | 4.0   | μA    | 3.0                                                                                       |                                               |  |  |

|                              |                             | _   | 3.0                   | 7.0   | μA    | 5.0                                                                                       |                                               |  |  |

| D022                         |                             |     | 42                    | 60    | μA    | 3.0                                                                                       | BOR Current <sup>(1)</sup>                    |  |  |

|                              |                             | _   | 85                    | 122   | μA    | 5.0                                                                                       |                                               |  |  |

| D023                         |                             | _   | 32                    | 45    | μA    | 2.0                                                                                       | Comparator Current <sup>(1)</sup> , both      |  |  |

|                              |                             | _   | 60                    | 78    | μA    | 3.0                                                                                       | comparators enabled                           |  |  |

|                              |                             | _   | 120                   | 160   | μA    | 5.0                                                                                       |                                               |  |  |

| D024                         |                             | _   | 30                    | 36    | μA    | 2.0                                                                                       | CVREF Current <sup>(1)</sup> (high range)     |  |  |

|                              |                             | _   | 45                    | 55    | μA    | 3.0                                                                                       |                                               |  |  |

|                              |                             | _   | 75                    | 95    | μA    | 5.0                                                                                       |                                               |  |  |

| D025*                        |                             | _   | 39                    | 47    | μA    | 2.0                                                                                       | CVREF Current <sup>(1)</sup> (low range)      |  |  |

|                              |                             | —   | 59                    | 72    | μΑ    | 3.0                                                                                       |                                               |  |  |

|                              |                             |     | 98                    | 124   | μA    | 5.0                                                                                       |                                               |  |  |

| D026                         |                             | —   | 4.5                   | 7.0   | μΑ    | 2.0                                                                                       | T1OSC Current <sup>(1)</sup> , 32.768 kHz     |  |  |

|                              |                             | —   | 5.0                   | 8.0   | μΑ    | 3.0                                                                                       |                                               |  |  |

|                              |                             | —   | 6.0                   | 12    | μA    | 5.0                                                                                       |                                               |  |  |

| D027                         |                             | —   | 0.30                  | 1.6   | μΑ    | 3.0                                                                                       | A/D Current <sup>(1)</sup> , no conversion in |  |  |

|                              |                             | —   | 0.36                  | 1.9   | μΑ    | 5.0                                                                                       | progress                                      |  |  |

# 14.3 DC Characteristics: PIC16F688-I (Industrial)

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

**Note 1:** The peripheral current is the sum of the base IDD or IPD and the additional current consumed when this peripheral is enabled. The peripheral ∆ current can be determined by subtracting the base IDD or IPD current from this limit. Max values should be used when calculating total current consumption.

**2:** The power-down current in Sleep mode does not depend on the oscillator type. Power-down current is measured with the part in Sleep mode, with all I/O pins in high-impedance state and tied to VDD.

# 14.7 Timing Parameter Symbology

The timing parameter symbols have been created with one of the following formats:

- 1. TppS2ppS

- 2. TppS

| <u>z. rppo</u> |                                      |     |                |

|----------------|--------------------------------------|-----|----------------|

| т              |                                      |     |                |

| F              | Frequency                            | Т   | Time           |

| Lowerc         | ase letters (pp) and their meanings: |     |                |

| рр             |                                      |     |                |

| сс             | CCP1                                 | OSC | OSC1           |

| ck             | CLKOUT                               | rd  | RD             |

| cs             | CS                                   | rw  | RD or WR       |

| di             | SDI                                  | sc  | SCK            |

| do             | SDO                                  | SS  | SS             |

| dt             | Data in                              | tO  | TOCKI          |

| io             | I/O PORT                             | t1  | T1CKI          |

| mc             | MCLR                                 | wr  | WR             |

| Upperc         | ase letters and their meanings:      |     |                |

| S              |                                      |     |                |

| F              | Fall                                 | Р   | Period         |

| н              | High                                 | R   | Rise           |

| I              | Invalid (High-impedance)             | V   | Valid          |

| L              | Low                                  | Z   | High-impedance |

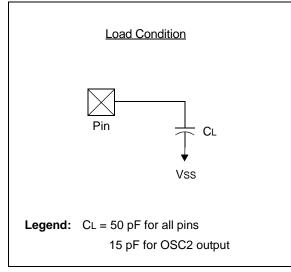

#### FIGURE 14-3: LOAD CONDITIONS

# TABLE 14-8: PIC16F688 A/D CONVERTER (ADC) CHARACTERISTICS

|               | Standard Operating Conditions (unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +125^{\circ}C$ |                                                      |            |      |          |       |                                                                     |  |  |  |

|---------------|----------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|------------|------|----------|-------|---------------------------------------------------------------------|--|--|--|

| Param<br>No.  | Sym                                                                                                                  | Characteristic                                       | Min        | Тур† | Max      | Units | Conditions                                                          |  |  |  |

| AD01          | NR                                                                                                                   | Resolution                                           | —          | _    | 10 bits  | bit   |                                                                     |  |  |  |

| AD02          | EIL                                                                                                                  | Integral Error                                       | —          | _    | ±1       | LSb   | VREF = 5.12V                                                        |  |  |  |

| AD03          | Edl                                                                                                                  | Differential Error                                   | —          | _    | ±1       | LSb   | No missing codes to 10 bits<br>VREF = 5.12V                         |  |  |  |

| AD04          | EOFF                                                                                                                 | Offset Error                                         | —          | _    | ±1       | LSb   | VREF = 5.12V                                                        |  |  |  |

| AD07          | Egn                                                                                                                  | Gain Error                                           |            | _    | ±1       | LSb   | VREF = 5.12V                                                        |  |  |  |

| AD06<br>AD06A | Vref                                                                                                                 | Reference Voltage <sup>(1)</sup>                     | 2.2<br>2.7 | _    | –<br>Vdd | V     | Absolute minimum to ensure 1 LSb accuracy                           |  |  |  |

| AD07          | VAIN                                                                                                                 | Full-Scale Range                                     | Vss        | _    | Vref     | V     |                                                                     |  |  |  |

| AD08          | ZAIN                                                                                                                 | Recommended<br>Impedance of Analog<br>Voltage Source | —          | _    | 10       | kΩ    |                                                                     |  |  |  |

| AD09*         | IREF                                                                                                                 | VREF Input Current <sup>(1)</sup>                    | 10         | _    | 1000     | μA    | During VAIN acquisition.<br>Based on differential of VHOLD to VAIN. |  |  |  |

|               |                                                                                                                      |                                                      |            | _    | 50       | μA    | During A/D conversion cycle.                                        |  |  |  |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

**Note 1:** ADC VREF is from external VREF or VDD pin, whichever is selected as reference input.

#### TABLE 14-9: PIC16F688 A/D CONVERSION REQUIREMENTS

|              | Standard Operating Conditions (unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +125^{\circ}C$ |                                                                       |     |              |     |       |                                                                                                                                                           |  |  |  |

|--------------|----------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------|-----|--------------|-----|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Param<br>No. | Sym                                                                                                                  | Characteristic                                                        | Min | Тур†         | Max | Units | Conditions                                                                                                                                                |  |  |  |

| AD130*       | Tad                                                                                                                  | A/D Clock Period                                                      | 1.6 |              | 9.0 | μS    | Tosc-based, VREF $\geq$ 3.0V                                                                                                                              |  |  |  |

|              |                                                                                                                      |                                                                       | 3.0 | —            | 9.0 | μS    | Tosc-based, VREF full range                                                                                                                               |  |  |  |

|              |                                                                                                                      | A/D Internal RC<br>Oscillator Period                                  | 3.0 | 6.0          | 9.0 | μS    | ADCS<1:0> = 11 (ADRC mode)<br>At VDD = 2.5V                                                                                                               |  |  |  |

|              |                                                                                                                      |                                                                       | 1.6 | 4.0          | 6.0 | μS    | At VDD = 5.0V                                                                                                                                             |  |  |  |

| AD131        | TCNV                                                                                                                 | Conversion Time<br>(not including<br>Acquisition Time) <sup>(1)</sup> | _   | 11           |     | TAD   | Set GO/DONE bit to new data in A/D<br>Result register                                                                                                     |  |  |  |

| AD132*       | TACQ                                                                                                                 | Acquisition Time                                                      |     | 11.5         | _   | μS    |                                                                                                                                                           |  |  |  |

| AD133*       | TAMP                                                                                                                 | Amplifier Settling Time                                               | _   | —            | 5   | μS    |                                                                                                                                                           |  |  |  |

| AD134        | Tgo                                                                                                                  | Q4 to A/D Clock Start                                                 | _   | Tosc/2       | _   | —     |                                                                                                                                                           |  |  |  |

|              |                                                                                                                      |                                                                       |     | Tosc/2 + Tcy |     |       | If the A/D clock source is selected as<br>RC, a time of TCY is added before the<br>A/D clock starts. This allows the SLEEP<br>instruction to be executed. |  |  |  |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

**Note 1:** ADRESH and ADRESL registers may be read on the following TCY cycle.

2: See Section 8.3 "A/D Acquisition Requirements" for minimum conditions.

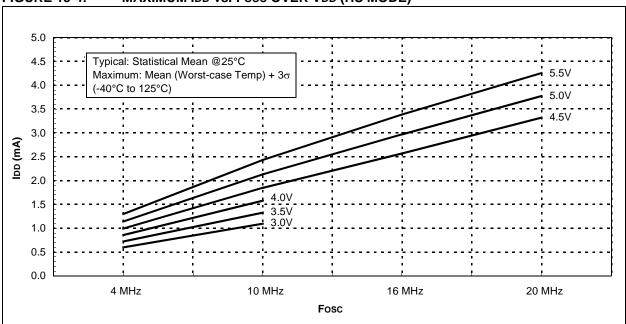

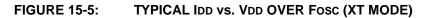

FIGURE 15-4: MAXIMUM IDD vs. Fosc OVER VDD (HS MODE)

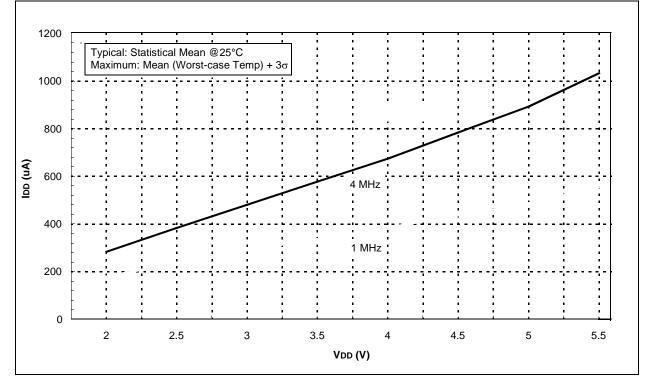

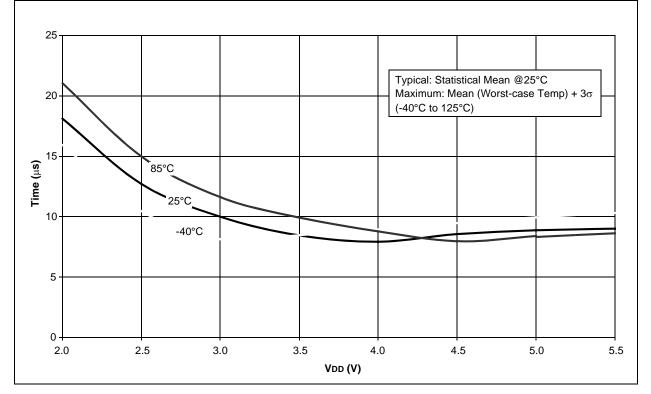

#### FIGURE 15-34: TYPICAL HFINTOSC START-UP TIMES vs. VDD OVER TEMPERATURE

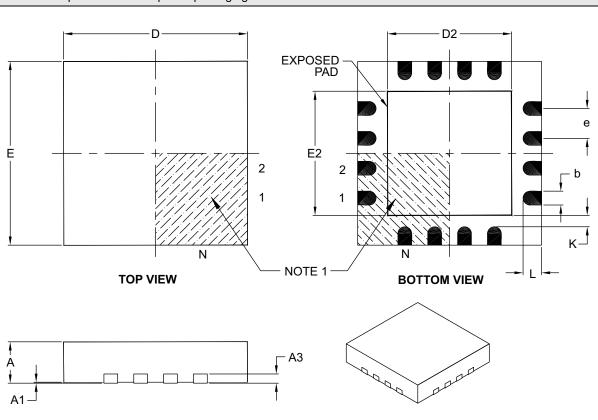

### 16-Lead Plastic Quad Flat, No Lead Package (ML) – 4x4x0.9 mm Body [QFN]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                        | Units            |      | MILLIMETERS | 6    |  |  |

|------------------------|------------------|------|-------------|------|--|--|

|                        | Dimension Limits | MIN  | NOM         | MAX  |  |  |

| Number of Pins         | N                |      | 16          |      |  |  |

| Pitch                  | e                |      | 0.65 BSC    |      |  |  |

| Overall Height         | A                | 0.80 | 0.90        | 1.00 |  |  |

| Standoff               | A1               | 0.00 | 0.02        | 0.05 |  |  |

| Contact Thickness      | A3               |      | 0.20 REF    |      |  |  |

| Overall Width          | E                |      | 4.00 BSC    |      |  |  |

| Exposed Pad Width      | E2               | 2.50 | 2.65        | 2.80 |  |  |

| Overall Length         | D                |      | 4.00 BSC    |      |  |  |

| Exposed Pad Length     | D2               | 2.50 | 2.65        | 2.80 |  |  |

| Contact Width          | b                | 0.25 | 0.30        | 0.35 |  |  |

| Contact Length         | L                | 0.30 | 0.40        | 0.50 |  |  |

| Contact-to-Exposed Pad | К                | 0.20 | -           | -    |  |  |

#### Notes:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. Package is saw singulated.