# E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                   |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 20MHz                                                                    |

| Connectivity               | UART/USART                                                               |

| Peripherals                | Brown-out Detect/Reset, POR, WDT                                         |

| Number of I/O              | 12                                                                       |

| Program Memory Size        | 7KB (4K × 14)                                                            |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | 256 x 8                                                                  |

| RAM Size                   | 256 x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                |

| Data Converters            | A/D 8x10b                                                                |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 16-VQFN Exposed Pad                                                      |

| Supplier Device Package    | 16-QFN (4x4)                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f688-i-ml |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

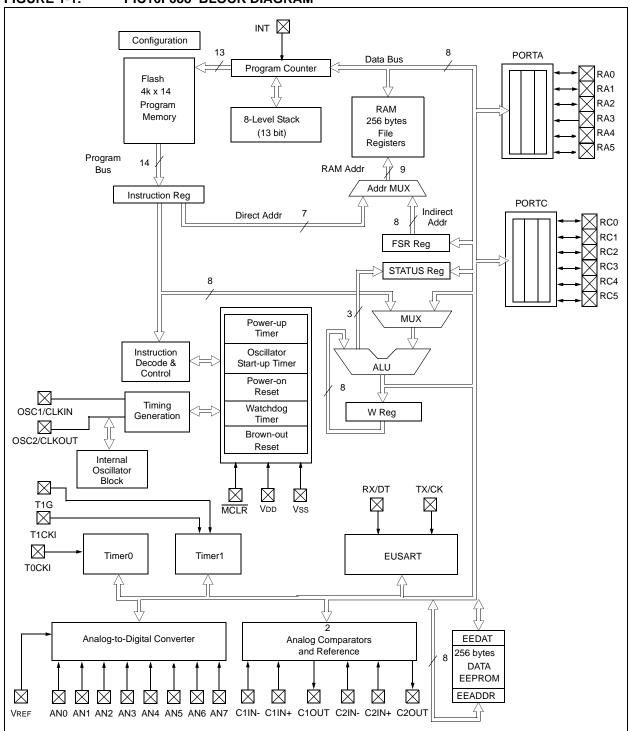

# 1.0 DEVICE OVERVIEW

The PIC16F688 is covered by this data sheet. It is available in 14-pin PDIP, SOIC, TSSOP and QFN packages. Figure 1-1 shows a block diagram of the PIC16F688 device. Table 1-1 shows the pinout description.

FIGURE 1-1: PIC16F688 BLOCK DIAGRAM

# TABLE 1-1: PIC16F688 PINOUT DESCRIPTION

| Name                        | Function | Input<br>Type | Output<br>Type | Description                                      |

|-----------------------------|----------|---------------|----------------|--------------------------------------------------|

| RA0/AN0/C1IN+/ICSPDAT/ULPWU | RA0      | TTL           | CMOS           | PORTA I/O w/prog pull-up and interrupt-on-change |

|                             | AN0      | AN            | _              | A/D Channel 0 input                              |

|                             | C1IN+    | AN            | —              | Comparator 1 input                               |

|                             | ICSPDAT  | TTL           | CMOS           | Serial Programming Data I/O                      |

|                             | ULPWU    | AN            | —              | Ultra Low-Power Wake-up input                    |

| RA1/AN1/C1IN-/VREF/ICSPCLK  | RA1      | TTL           | CMOS           | PORTA I/O w/prog pull-up and interrupt-on-change |

|                             | AN1      | AN            | _              | A/D Channel 1 input                              |

|                             | C1IN-    | AN            |                | Comparator 1 input                               |

|                             | VREF     | AN            | —              | External Voltage Reference for A/D               |

|                             | ICSPCLK  | ST            | —              | Serial Programming Clock                         |

| RA2/AN2/T0CKI/INT/C1OUT     | RA2      | ST            | CMOS           | PORTA I/O w/prog pull-up and interrupt-on-change |

|                             | AN2      | AN            |                | A/D Channel 2 input                              |

|                             | T0CKI    | ST            |                | Timer0 clock input                               |

|                             | INT      | ST            | —              | External Interrupt                               |

|                             | C1OUT    | —             | CMOS           | Comparator 1 output                              |

| RA3/MCLR/VPP                | RA3      | TTL           | —              | PORTA input with interrupt-on-change             |

|                             | MCLR     | ST            | —              | Master Clear w/internal pull-up                  |

|                             | Vpp      | HV            | —              | Programming voltage                              |

| RA4/AN3/T1G/OSC2/CLKOUT     | RA4      | TTL           | CMOS           | PORTA I/O w/prog pull-up and interrupt-on-change |

|                             | AN3      | AN            | —              | A/D Channel 3 input                              |

|                             | T1G      | ST            | _              | Timer1 gate                                      |

|                             | OSC2     | _             | XTAL           | Crystal/Resonator                                |

|                             | CLKOUT   |               | CMOS           | Fosc/4 output                                    |

| RA5/T1CKI/OSC1/CLKIN        | RA5      | TTL           | CMOS           | PORTA I/O w/prog pull-up and interrupt-on-change |

|                             | T1CKI    | ST            | —              | Timer1 clock                                     |

|                             | OSC1     | XTAL          | —              | Crystal/Resonator                                |

|                             | CLKIN    | ST            | —              | External clock input/RC oscillator connection    |

| RC0/AN4/C2IN+               | RC0      | TTL           | CMOS           | PORTC I/O                                        |

|                             | AN4      | AN            | _              | A/D Channel 4 input                              |

|                             | C2IN+    | AN            |                | Comparator 2 input                               |

| RC1/AN5/C2IN-               | RC1      | TTL           | CMOS           | PORTC I/O                                        |

|                             | AN5      | AN            | _              | A/D Channel 5 input                              |

|                             | C2IN-    | AN            |                | Comparator 2 input                               |

| RC2/AN6                     | RC2      | TTL           | CMOS           | PORTC I/O                                        |

|                             | AN6      | AN            | _              | A/D Channel 6 input                              |

| RC3/AN7                     | RC3      | TTL           | CMOS           | PORTC I/O                                        |

|                             | AN7      | AN            | —              | A/D Channel 7 input                              |

| RC4/C2OUT/TX/CK             | RC4      | TTL           | CMOS           | PORTC I/O                                        |

|                             | C2OUT    | _             | CMOS           | Comparator 2 output                              |

|                             | TX       |               | CMOS           | USART asynchronous output                        |

|                             | СК       | ST            | CMOS           | USART asynchronous clock                         |

| RC5/RX/DT                   | RC5      | TTL           | CMOS           | Port C I/O                                       |

|                             | RX       | ST            | CMOS           | USART asynchronous input                         |

|                             | DT       | ST            | CMOS           | USART asynchronous data                          |

| Vss                         | Vss      | Power         | _              | Ground reference                                 |

| VDD                         | VDD      | Power         |                | Positive supply                                  |

Legend: AN = Analog input or output TTL = TTL compatible input CMOS = CMOS compatible input or output

OC = Open collector output

HV = High Voltage

ST = Schmitt Trigger input with CMOS levels XTAL = Crystal

# 2.2.2.6 PCON Register

The Power Control (PCON) register (see Register 2-6) contains flag bits to differentiate between a:

- Power-on Reset (POR)

- Brown-out Reset (BOR)

- Watchdog Timer Reset (WDT)

- External MCLR Reset

The PCON register also controls the Ultra Low-Power Wake-up and software enable of the BOR.

# REGISTER 2-6: PCON: POWER CONTROL REGISTER

| U-0   | U-0 | R/W-0  | R/W-1                 | U-0 | U-0 | R/W-0 | R/W-x |

|-------|-----|--------|-----------------------|-----|-----|-------|-------|

| —     | —   | ULPWUE | SBOREN <sup>(1)</sup> | -   | —   | POR   | BOR   |

| bit 7 |     |        |                       |     |     |       | bit 0 |

| Legend:           |             |                                      |                                    |                       |  |  |  |  |

|-------------------|-------------|--------------------------------------|------------------------------------|-----------------------|--|--|--|--|

| R = Readal        | ble bit     | W = Writable bit                     | U = Unimplemented bit, read as '0' |                       |  |  |  |  |

| -n = Value at POR |             | '1' = Bit is set                     | '0' = Bit is cleared               | x = Bit is unknown    |  |  |  |  |

|                   |             |                                      |                                    |                       |  |  |  |  |

| bit 7-6           | Unimple     | mented: Read as '0'                  |                                    |                       |  |  |  |  |

| bit 5             | ULPWUI      | E: Ultra Low-Power Wake-up           | o Enable bit                       |                       |  |  |  |  |

| 1 = Ultra low-p   |             | low-power wake-up enabled            | 1                                  |                       |  |  |  |  |

|                   | 0 = Ultra   | low-power wake-up disable            | d                                  |                       |  |  |  |  |

| bit 4 SBOREN: S   |             | Software BOR Enable bit <sup>(</sup> | 1)                                 |                       |  |  |  |  |

| 1 = BOR ena       |             | enabled                              |                                    |                       |  |  |  |  |

|                   | 0 = BOR     | disabled                             |                                    |                       |  |  |  |  |

| bit 3-2           | Unimple     | mented: Read as '0'                  |                                    |                       |  |  |  |  |

| bit 1             | POR: Po     | wer-on Reset Status bit              |                                    |                       |  |  |  |  |

|                   | 1 = No P    | ower-on Reset occurred               |                                    |                       |  |  |  |  |

|                   | 0 = A Po    | wer-on Reset occurred (mus           | t be set in software after a Po    | wer-on Reset occurs)  |  |  |  |  |

| bit 0             | BOR: Br     | own-out Reset Status bit             |                                    |                       |  |  |  |  |

|                   | 1 = No B    | rown-out Reset occurred              |                                    |                       |  |  |  |  |

|                   | 0 = A Brown | own-out Reset occurred (mu           | st be set in software after a Br   | own-out Reset occurs) |  |  |  |  |

# 3.4.4 EXTERNAL RC MODES

The external Resistor-Capacitor (RC) modes support the use of an external RC circuit. This allows the designer maximum flexibility in frequency choice while keeping costs to a minimum when clock accuracy is not required. There are two modes: RC and RCIO.

In RC mode, the RC circuit connects to OSC1. OSC2/ CLKOUT outputs the RC oscillator frequency divided by 4. This signal may be used to provide a clock for external circuitry, synchronization, calibration, test or other application requirements. Figure 3-5 shows the external RC mode connections.

VDD PIC<sup>®</sup> MCU REXT OSC1/CLKIN Internal Clock CEXT Vss -Fosc/4 or OSC2/CLKOUT(1) I/O<sup>(2)</sup> Recommended values: 10 k $\Omega \leq \text{REXT} \leq 100 \text{ k}\Omega$ , <3V  $3 \text{ k}\Omega \leq \text{Rext} \leq 100 \text{ k}\Omega, 3-5 \text{V}$ CEXT > 20 pF, 2-5V Note 1: Alternate pin functions are listed in Section 1.0 "Device Overview". 2: Output depends upon RC or RCIO clock mode

FIGURE 3-5: EXTERNAL RC MODES

In RCIO mode, the RC circuit is connected to OSC1. OSC2 becomes an additional general purpose I/O pin.

The RC oscillator frequency is a function of the supply voltage, the resistor (REXT) and capacitor (CEXT) values and the operating temperature. Other factors affecting the oscillator frequency are:

- threshold voltage variation

- component tolerances

- packaging variations in capacitance

The user also needs to take into account variation due to tolerance of external RC components used.

## 3.5 Internal Clock Modes

The oscillator module has two independent, internal oscillators that can be configured or selected as the system clock source.

- 1. The **HFINTOSC** (High-Frequency Internal Oscillator) is factory calibrated and operates at 8 MHz. The frequency of the HFINTOSC can be user-adjusted via software using the OSCTUNE register (Register 3-2).

- 2. The **LFINTOSC** (Low-Frequency Internal Oscillator) is uncalibrated and operates at 31 kHz.

The system clock speed can be selected via software using the Internal Oscillator Frequency Select bits IRCF<2:0> of the OSCCON register.

The system clock can be selected between external or internal clock sources via the System Clock Selection (SCS) bit of the OSCCON register. See **Section 3.6 "Clock Switching"** for more information.

## 3.5.1 INTOSC AND INTOSCIO MODES

The INTOSC and INTOSCIO modes configure the internal oscillators as the system clock source when the device is programmed using the oscillator selection or the FOSC<2:0> bits in the Configuration Word register (CONFIG). See Section 11.0 "Special Features of the CPU" for more information.

In **INTOSC** mode, OSC1/CLKIN is available for general purpose I/O. OSC2/CLKOUT outputs the selected internal oscillator frequency divided by 4. The CLKOUT signal may be used to provide a clock for external circuitry, synchronization, calibration, test or other application requirements.

In **INTOSCIO** mode, OSC1/CLKIN and OSC2/CLKOUT are available for general purpose I/O.

## 3.5.2 HFINTOSC

The High-Frequency Internal Oscillator (HFINTOSC) is a factory calibrated 8 MHz internal clock source. The frequency of the HFINTOSC can be altered via software using the OSCTUNE register (Register 3-2).

The output of the HFINTOSC connects to a postscaler and multiplexer (see Figure 3-1). One of seven frequencies can be selected via software using the IRCF<2:0> bits of the OSCCON register. See **Section 3.5.4 "Frequency Select Bits (IRCF)"** for more information.

The HFINTOSC is enabled by selecting any frequency between 8 MHz and 125 kHz by setting the IRCF<2:0> bits of the OSCCON register  $\neq$  000. Then, set the System Clock Source (SCS) bit of the OSCCON register to '1' or enable Two-Speed Start-up by setting the IESO bit in the Configuration Word register (CONFIG) to '1'.

The HF Internal Oscillator (HTS) bit of the OSCCON register indicates whether the HFINTOSC is stable or not.

# **PIC16F688**

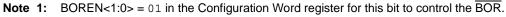

# 4.2.5.6 RA5/T1CKI/OSC1/CLKIN

Figure 4-6 shows the diagram for this pin. The RA5 pin is configurable to function as one of the following:

- a general purpose I/O

- a Timer1 clock input

- a crystal/resonator connection

- a clock input

FIGURE 4-6: BLOCK DIAGRAM OF RA5

| R/W-1         | R/W-1                     | R/W-1          | R/W-1                       | R/W-1            | R/W-1           | R/W-1           | R/W-1 |

|---------------|---------------------------|----------------|-----------------------------|------------------|-----------------|-----------------|-------|

| RAPU          | INTEDG                    | TOCS           | TOSE                        | PSA              | PS2             | PS1             | PS0   |

| bit 7         | ł                         |                |                             |                  |                 |                 | bit C |

| Legend:       |                           |                |                             |                  |                 |                 |       |

| R = Readable  | e bit                     | W = Writab     | le bit                      | U = Unimple      | mented bit, rea | ad as '0'       |       |

| -n = Value at | POR                       | '1' = Bit is s | set                         | '0' = Bit is cle |                 | x = Bit is unki | nown  |

|               |                           |                |                             |                  |                 |                 |       |

| bit 7         | RAPU: POR                 | TA Pull-up Er  | nable bit                   |                  |                 |                 |       |

|               | 1 = PORTA p               |                |                             |                  |                 |                 |       |

|               | 0 = PORTA p               | oull-ups are e | nabled by indivi            | dual PORT lat    | ch values       |                 |       |

| bit 6         | INTEDG: Inte              | errupt Edge S  | Select bit                  |                  |                 |                 |       |

|               | 1 = Interrupt             | on rising edg  | e of INT pin                |                  |                 |                 |       |

|               | 0 = Interrupt             | on falling edg | ge of INT pin               |                  |                 |                 |       |

| bit 5         | TOCS: TMRC                | Clock Source   | e Select bit                |                  |                 |                 |       |

|               | 1 = Transitio             | n on TOCKI p   | in                          |                  |                 |                 |       |

|               |                           |                | cle clock (Fosc/            | 4)               |                 |                 |       |

| bit 4         | TOSE: TMRO                | Source Eda     | e Select bit                |                  |                 |                 |       |

|               |                           | •              | low transition or           | TOCKI pin        |                 |                 |       |

|               |                           |                | igh transition or           |                  |                 |                 |       |

| bit 3         | PSA: Presca               |                | •                           | •                |                 |                 |       |

|               | 1 = Prescale              | •              |                             |                  |                 |                 |       |

|               |                           |                | to the Timer0 m             | nodule           |                 |                 |       |

| bit 2-0       | <b>PS&lt;2:0&gt;:</b> Pre | escaler Rate   | Select bits                 |                  |                 |                 |       |

|               | BIT                       | VALUE TMRC     | RATE WDT RA                 | TE               |                 |                 |       |

|               | (                         | 000 1:         | :2 1:1                      |                  |                 |                 |       |

|               | (                         | 001 1:         | :4 1:2                      |                  |                 |                 |       |

|               |                           |                | :8 1:4                      |                  |                 |                 |       |

|               |                           |                | :16 1:8                     |                  |                 |                 |       |

|               |                           |                | : 32 1 : 16                 |                  |                 |                 |       |

|               |                           |                | : 64 1 : 32<br>: 128 1 : 64 |                  |                 |                 |       |

|               | -                         | -              | 128 1:64                    |                  |                 |                 |       |

## REGISTER 5-1: OPTION\_REG: OPTION REGISTER

Note 1: A dedicated 16-bit WDT postscaler is available. See Section 11.5 "Watchdog Timer (WDT)" for more information.

1 : 128

# TABLE 5-1: SUMMARY OF REGISTERS ASSOCIATED WITH TIMER0

1 : 256

111

| Name       | Bit 7    | Bit 6      | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Value on<br>POR, BOR | Value on<br>all other<br>Resets |

|------------|----------|------------|--------|--------|--------|--------|--------|--------|----------------------|---------------------------------|

| TMR0       | Timer0 N | /lodule Re | gister |        |        |        |        |        | xxxx xxxx            | uuuu uuuu                       |

| INTCON     | GIE      | PEIE       | TOIE   | INTE   | RAIE   | T0IF   | INTF   | RAIF   | 0000 000x            | 0000 000x                       |

| OPTION_REG | RAPU     | INTEDG     | TOCS   | T0SE   | PSA    | PS2    | PS1    | PS0    | 1111 1111            | 1111 1111                       |

| TRISA      | —        | —          | TRISA5 | TRISA4 | TRISA3 | TRISA2 | TRISA1 | TRISA0 | 11 1111              | 11 1111                         |

**Legend:** -= Unimplemented locations, read as '0', u = unchanged, x = unknown. Shaded cells are not used by the Timer0 module.

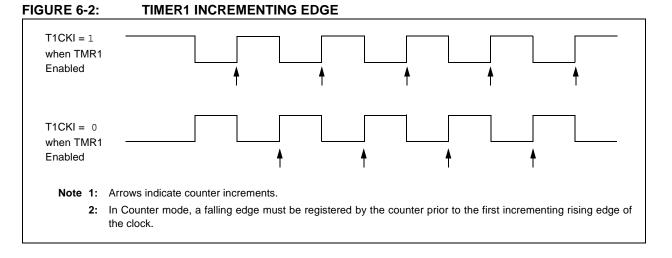

# 6.7 Timer1 Interrupt

The Timer1 register pair (TMR1H:TMR1L) increments to FFFFh and rolls over to 0000h. When Timer1 rolls over, the Timer1 interrupt flag bit of the PIR1 register is set. To enable the interrupt on rollover, you must set these bits:

- Timer1 interrupt enable bit of the PIE1 register

- PEIE bit of the INTCON register

- GIE bit of the INTCON register

The interrupt is cleared by clearing the TMR1IF bit in the Interrupt Service Routine.

Note: The TMR1H:TTMR1L register pair and the TMR1IF bit should be cleared before enabling interrupts.

# 6.8 Timer1 Operation During Sleep

Timer1 can only operate during Sleep when setup in Asynchronous Counter mode. In this mode, an external crystal or clock source can be used to increment the counter. To set up the timer to wake the device:

- TMR1ON bit of the T1CON register must be set

- TMR1IE bit of the PIE1 register must be set

- PEIE bit of the INTCON register must be set

The device will wake-up on an overflow and execute the next instruction. If the GIE bit of the INTCON register is set, the device will call the Interrupt Service Routine (0004h).

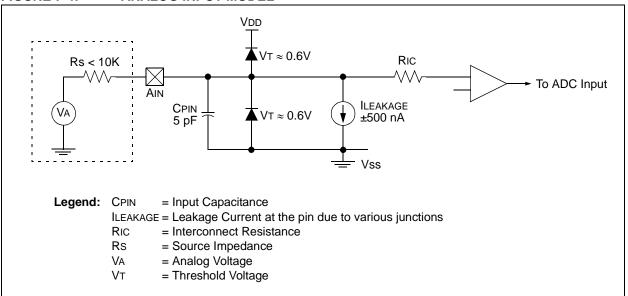

# 7.1.1 ANALOG INPUT CONNECTION CONSIDERATIONS

A simplified circuit for an analog input is shown in Figure 7-4. Since the analog input pins share their connection with a digital input, they have reverse biased ESD protection diodes to VDD and Vss. The analog input, therefore, must be between Vss and VDD. If the input voltage deviates from this range by more than 0.6V in either direction, one of the diodes is forward biased and a latch-up may occur.

A maximum source impedance of  $10 \text{ k}\Omega$  is recommended for the analog sources. Also, any external component connected to an analog input pin, such as a capacitor or a Zener diode, should have very little leakage current to minimize inaccuracies introduced.

- Note 1: When reading a PORT register, all pins configured as analog inputs will read as a '0'. Pins configured as digital inputs will convert as an analog input, according to the input specification.

- 2: Analog levels on any pin defined as a digital input, may cause the input buffer to consume more current than is specified.

### FIGURE 7-4: ANALOG INPUT MODEL

## 10.1.2.4 Receive Framing Error

Each character in the receive FIFO buffer has a corresponding framing error Status bit. A framing error indicates that a Stop bit was not seen at the expected time. The framing error status is accessed via the FERR bit of the RCSTA register. The FERR bit represents the status of the top unread character in the receive FIFO. Therefore, the FERR bit must be read before reading the RCREG.

The FERR bit is read-only and only applies to the top unread character in the receive FIFO. A framing error (FERR = 1) does not preclude reception of additional characters. It is not necessary to clear the FERR bit. Reading the next character from the FIFO buffer will advance the FIFO to the next character and the next corresponding framing error.

The FERR bit can be forced clear by clearing the SPEN bit of the RCSTA register which resets the EUSART. Clearing the CREN bit of the RCSTA register does not affect the FERR bit. A framing error by itself does not generate an interrupt.

| Note: | If all receive characters in the receive  |

|-------|-------------------------------------------|

|       | FIFO have framing errors, repeated reads  |

|       | of the RCREG will not clear the FERR bit. |

## 10.1.2.5 Receive Overrun Error

The receive FIFO buffer can hold two characters. An overrun error will be generated If a third character, in its entirety, is received before the FIFO is accessed. When this happens the OERR bit of the RCSTA register is set. The characters already in the FIFO buffer can be read but no additional characters will be received until the error is cleared. The error must be cleared by either clearing the CREN bit of the RCSTA register or by resetting the EUSART by clearing the SPEN bit of the RCSTA register.

## 10.1.2.6 Receiving 9-bit Characters

The EUSART supports 9-bit character reception. When the RX9 bit of the RCSTA register is set the EUSART will shift 9 bits into the RSR for each character received. The RX9D bit of the RCSTA register is the ninth and Most Significant data bit of the top unread character in the receive FIFO. When reading 9-bit data from the receive FIFO buffer, the RX9D data bit must be read before reading the 8 Least Significant bits from the RCREG.

## 10.1.2.7 Address Detection

A special Address Detection mode is available for use when multiple receivers share the same transmission line, such as in RS-485 systems. Address detection is enabled by setting the ADDEN bit of the RCSTA register.

Address detection requires 9-bit character reception. When address detection is enabled, only characters with the ninth data bit set will be transferred to the receive FIFO buffer, thereby setting the RCIF interrupt bit. All other characters will be ignored.

Upon receiving an address character, user software determines if the address matches its own. Upon address match, user software must disable address detection by clearing the ADDEN bit before the next Stop bit occurs. When user software detects the end of the message, determined by the message protocol used, software places the receiver back into the Address Detection mode by setting the ADDEN bit.

|        |                  |            |                             |                | SYNC       | <b>C</b> = 0, BRGH          | l = 1, BRC     | <b>616 =</b> 0 |                             |                |            |                             |

|--------|------------------|------------|-----------------------------|----------------|------------|-----------------------------|----------------|----------------|-----------------------------|----------------|------------|-----------------------------|

| BAUD   | Fosc = 4.000 MHz |            | Fosc = 3.6864 MHz           |                |            | Fosc = 2.000 MHz            |                |                | Fosc = 1.000 MHz            |                |            |                             |

| RATE   | Actual<br>Rate   | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate | %<br>Error     | SPBRG<br>value<br>(decimal) | Actual<br>Rate | %<br>Error | SPBRG<br>value<br>(decimal) |

| 300    |                  |            | _                           | _              |            | _                           | _              | _              | _                           | 300            | 0.16       | 207                         |

| 1200   | 1202             | 0.16       | 207                         | 1200           | 0.00       | 191                         | 1202           | 0.16           | 103                         | 1202           | 0.16       | 51                          |

| 2400   | 2404             | 0.16       | 103                         | 2400           | 0.00       | 95                          | 2404           | 0.16           | 51                          | 2404           | 0.16       | 25                          |

| 9600   | 9615             | 0.16       | 25                          | 9600           | 0.00       | 23                          | 9615           | 0.16           | 12                          | _              | _          | —                           |

| 10417  | 10417            | 0.00       | 23                          | 10473          | 0.53       | 21                          | 10417          | 0.00           | 11                          | 10417          | 0.00       | 5                           |

| 19.2k  | 19.23k           | 0.16       | 12                          | 19.2k          | 0.00       | 11                          | _              | _              | _                           | —              | _          | _                           |

| 57.6k  | _                | _          | _                           | 57.60k         | 0.00       | 3                           | _              | _              | _                           | —              | _          | _                           |

| 115.2k | —                | _          | —                           | 115.2k         | 0.00       | 1                           | _              | _              | _                           |                | —          | —                           |

# TABLE 10-5: BAUD RATES FOR ASYNCHRONOUS MODES (CONTINUED)

|        |                   | SYNC = 0, BRGH = 0, BRG16 = 1 |                             |                   |            |                             |                |            |                             |                  |            |                             |  |

|--------|-------------------|-------------------------------|-----------------------------|-------------------|------------|-----------------------------|----------------|------------|-----------------------------|------------------|------------|-----------------------------|--|

| BAUD   | Fosc = 20.000 MHz |                               |                             | Fosc = 18.432 MHz |            |                             | Fosc           | = 11.059   | 92 MHz                      | Fosc = 8.000 MHz |            |                             |  |

| RATE   | Actual<br>Rate    | %<br>Error                    | SPBRG<br>value<br>(decimal) | Actual<br>Rate    | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate   | %<br>Error | SPBRG<br>value<br>(decimal) |  |

| 300    | 300.0             | -0.01                         | 4166                        | 300.0             | 0.00       | 3839                        | 300.0          | 0.00       | 2303                        | 299.9            | -0.02      | 1666                        |  |

| 1200   | 1200              | -0.03                         | 1041                        | 1200              | 0.00       | 959                         | 1200           | 0.00       | 575                         | 1199             | -0.08      | 416                         |  |

| 2400   | 2399              | -0.03                         | 520                         | 2400              | 0.00       | 479                         | 2400           | 0.00       | 287                         | 2404             | 0.16       | 207                         |  |

| 9600   | 9615              | 0.16                          | 129                         | 9600              | 0.00       | 119                         | 9600           | 0.00       | 71                          | 9615             | 0.16       | 51                          |  |

| 10417  | 10417             | 0.00                          | 119                         | 10378             | -0.37      | 110                         | 10473          | 0.53       | 65                          | 10417            | 0.00       | 47                          |  |

| 19.2k  | 19.23k            | 0.16                          | 64                          | 19.20k            | 0.00       | 59                          | 19.20k         | 0.00       | 35                          | 19.23k           | 0.16       | 25                          |  |

| 57.6k  | 56.818            | -1.36                         | 21                          | 57.60k            | 0.00       | 19                          | 57.60k         | 0.00       | 11                          | 55556            | -3.55      | 8                           |  |

| 115.2k | 113.636           | -1.36                         | 10                          | 115.2k            | 0.00       | 9                           | 115.2k         | 0.00       | 5                           | —                | _          | _                           |  |

|        |                  |            |                             |                | SYNC       | <b>C</b> = 0, BRGH          | <b>i =</b> 0, <b>BR</b> | G16 = 1    |                             |                |            |                             |

|--------|------------------|------------|-----------------------------|----------------|------------|-----------------------------|-------------------------|------------|-----------------------------|----------------|------------|-----------------------------|

| BAUD   | Fosc = 4.000 MHz |            | Fosc = 3.6864 MHz           |                |            | Fosc = 2.000 MHz            |                         |            | Fosc = 1.000 MHz            |                |            |                             |

| RATE   | Actual<br>Rate   | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate          | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate | %<br>Error | SPBRG<br>value<br>(decimal) |

| 300    | 300.1            | 0.04       | 832                         | 300.0          | 0.00       | 767                         | 299.8                   | -0.108     | 416                         | 300.5          | 0.16       | 207                         |

| 1200   | 1202             | 0.16       | 207                         | 1200           | 0.00       | 191                         | 1202                    | 0.16       | 103                         | 1202           | 0.16       | 51                          |

| 2400   | 2404             | 0.16       | 103                         | 2400           | 0.00       | 95                          | 2404                    | 0.16       | 51                          | 2404           | 0.16       | 25                          |

| 9600   | 9615             | 0.16       | 25                          | 9600           | 0.00       | 23                          | 9615                    | 0.16       | 12                          | —              | _          | _                           |

| 10417  | 10417            | 0.00       | 23                          | 10473          | 0.53       | 21                          | 10417                   | 0.00       | 11                          | 10417          | 0.00       | 5                           |

| 19.2k  | 19.23k           | 0.16       | 12                          | 19.20k         | 0.00       | 11                          | —                       | —          | _                           | —              | —          | _                           |

| 57.6k  | —                | —          | _                           | 57.60k         | 0.00       | 3                           | —                       | _          | _                           | —              | _          | _                           |

| 115.2k | _                | _          | _                           | 115.2k         | 0.00       | 1                           | —                       | _          | _                           | —              | _          | _                           |

# 10.3.2 AUTO-BAUD OVERFLOW

During the course of automatic baud detection, the ABDOVF bit of the BAUDCTL register will be set if the baud rate counter overflows before the fifth rising edge is detected on the RX pin. The ABDOVF bit indicates that the counter has exceeded the maximum count that can fit in the 16 bits of the SPBRGH:SPBRG register pair. After the ABDOVF has been set, the counter continues to count until the fifth rising edge is detected on the RX pin. Upon detecting the fifth RX edge, the hardware will set the RCIF interrupt flag and clear the ABDEN bit of the BAUDCTL register. The RCIF flag can be subsequently cleared by reading the RCREG. The ABDOVF flag can be cleared by software directly.

To terminate the auto-baud process before the RCIF flag is set, clear the ABDEN bit then clear the ABDOVF bit. The ABDOVF bit will remain set if the ABDEN bit is not cleared first.

## 10.3.3 AUTO-WAKE-UP ON BREAK

During Sleep mode, all clocks to the EUSART are suspended. Because of this, the Baud Rate Generator is inactive and a proper character reception cannot be performed. The Auto-Wake-up feature allows the controller to wake-up due to activity on the RX/DT line. This feature is available only in Asynchronous mode.

The Auto-Wake-up feature is enabled by setting the WUE bit of the BAUDCTL register. Once set, the normal receive sequence on RX/DT is disabled, and the EUSART remains in an Idle state, monitoring for a wake-up event independent of the CPU mode. A wake-up event consists of a high-to-low transition on the RX/DT line. (This coincides with the start of a Sync Break or a wake-up signal character for the LIN protocol.)

The EUSART module generates an RCIF interrupt coincident with the wake-up event. The interrupt is generated synchronously to the Q clocks in normal CPU operating modes (Figure 10-7), and asynchronously if the device is in Sleep mode (Figure 10-8). The interrupt condition is cleared by reading the RCREG register.

The WUE bit is automatically cleared by the low-to-high transition on the RX line at the end of the Break. This signals to the user that the Break event is over. At this point, the EUSART module is in Idle mode waiting to receive the next character.

## 10.3.3.1 Special Considerations

#### Break Character

To avoid character errors or character fragments during a wake-up event, the wake-up character must be all zeros.

When the wake-up is enabled the function works independent of the low time on the data stream. If the WUE bit is set and a valid non-zero character is received, the low time from the Start bit to the first rising edge will be interpreted as the wake-up event. The remaining bits in the character will be received as a fragmented character and subsequent characters can result in framing or overrun errors.

Therefore, the initial character in the transmission must be all '0's. This must be 10 or more bit times, 13-bit times recommended for LIN bus, or any number of bit times for standard RS-232 devices.

## Oscillator Start-up Time

Oscillator start-up time must be considered, especially in applications using oscillators with longer start-up intervals (i.e., LP, XT or HS mode). The Sync Break (or wake-up signal) character must be of sufficient length, and be followed by a sufficient interval, to allow enough time for the selected oscillator to start and provide proper initialization of the EUSART.

#### WUE Bit

The wake-up event causes a receive interrupt by setting the RCIF bit. The WUE bit is cleared in hardware by a rising edge on RX/DT. The interrupt condition is then cleared in software by reading the RCREG register and discarding its contents.

To ensure that no actual data is lost, check the RCIDL.

## FIGURE 10-7: AUTO-WAKE-UP BIT (WUE) TIMING DURING NORMAL OPERATION

|          | BR set by a | 5 · · · · · · · · · · · · · · · · · · · | www.y | 1 |                 |        |                                       |                   | · · · · · · · · · · · · · · · · · · · |                                       |

|----------|-------------|-----------------------------------------|-------|---|-----------------|--------|---------------------------------------|-------------------|---------------------------------------|---------------------------------------|

| veus bel |             | ·                                       | .)    |   | 2               |        | (                                     |                   | ·····                                 | · · · · · · · · · · · · · · · · · · · |

| AZE LEVA | •           | · · · · · · · · · · · · · · · · · · ·   | (<br> |   | e<br>Millionnes |        |                                       |                   | *<br>                                 | · · · · · · · · · · · · · · · · · · · |

|          |             | , , , , , , , , , , , , , , , , , , ,   |       | 3 |                 | ۶ (    | · · · · · · · · · · · · · · · · · · · | ·····             | с<br>с                                |                                       |

| 808      |             |                                         |       |   | <u>/</u>        | "<br>1 | Şerse due                             | k<br>No Qoes Read | er RCREG -                            |                                       |

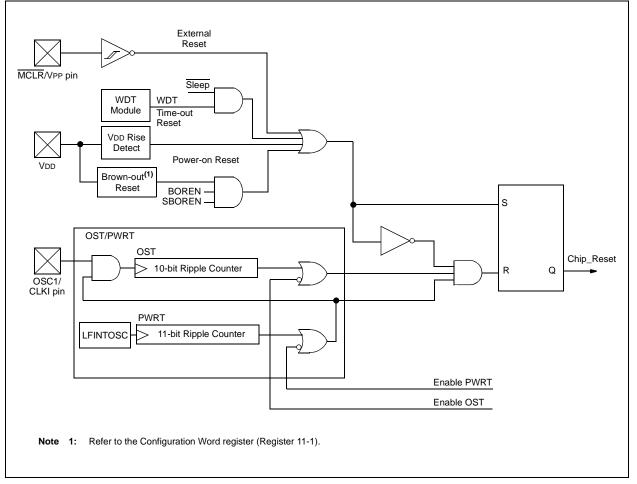

# 11.2 Reset

The PIC16F688 differentiates between various kinds of Reset:

- a) Power-on Reset (POR)

- b) WDT Reset during normal operation

- c) WDT Reset during Sleep

- d) MCLR Reset during normal operation

- e) MCLR Reset during Sleep

- f) Brown-out Reset (BOR)

Some registers are not affected in any Reset condition; their status is unknown on POR and unchanged in any other Reset. Most other registers are reset to a "Reset state" on:

- Power-on Reset

- MCLR Reset

- MCLR Reset during Sleep

- WDT Reset

- Brown-out Reset (BOR)

They are not affected by a WDT wake-up since this is viewed as the resumption of normal operation. TO and PD bits are set or cleared differently in different Reset situations, as indicated in Table 11-2. These bits are used in software to determine the nature of the Reset. See Table 11-4 for a full description of Reset states of all registers.

A simplified block diagram of the On-Chip Reset Circuit is shown in Figure 11-1.

The MCLR Reset path has a noise filter to detect and ignore small pulses. See **Section 14.0** "**Electrical Specifications**" for pulse width specifications.

## FIGURE 11-1: SIMPLIFIED BLOCK DIAGRAM OF ON-CHIP RESET CIRCUIT

# **PIC16F688**

| BTFSS            | Bit Test f, Skip if Set                                                                                                                                                                                           |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ label ] BTFSS f,b                                                                                                                                                                                               |

| Operands:        | $0 \le f \le 127$<br>$0 \le b < 7$                                                                                                                                                                                |

| Operation:       | skip if (f <b>) = 1</b>                                                                                                                                                                                           |

| Status Affected: | None                                                                                                                                                                                                              |

| Description:     | If bit 'b' in register 'f' is '0', the next<br>instruction is executed.<br>If bit 'b' is '1', then the next<br>instruction is discarded and a NOP<br>is executed instead, making this a<br>two-cycle instruction. |

| CLRWDT           | Clear Watchdog Timer                                                                                                                                     |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] CLRWDT                                                                                                                                           |

| Operands:        | None                                                                                                                                                     |

| Operation:       | $\begin{array}{l} 00h \rightarrow WDT \\ 0 \rightarrow WDT \text{ prescaler,} \\ 1 \rightarrow \overline{TO} \\ 1 \rightarrow \overline{PD} \end{array}$ |

| Status Affected: | TO, PD                                                                                                                                                   |

| Description:     | CLRWDT instruction resets the<br>Watchdog Timer. It also resets the<br>prescaler of the WDT.<br>Status bits TO and PD are set.                           |

| CALL             | Call Subroutine                                                                                                                                                                                                                               |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] CALL k                                                                                                                                                                                                                       |

| Operands:        | $0 \le k \le 2047$                                                                                                                                                                                                                            |

| Operation:       | (PC)+ 1 $\rightarrow$ TOS,<br>k $\rightarrow$ PC<10:0>,<br>(PCLATH<4:3>) $\rightarrow$ PC<12:11>                                                                                                                                              |

| Status Affected: | None                                                                                                                                                                                                                                          |

| Description:     | Call Subroutine. First, return<br>address (PC + 1) is pushed onto<br>the stack. The eleven-bit<br>immediate address is loaded into<br>PC bits <10:0>. The upper bits of<br>the PC are loaded from PCLATH.<br>CALL is a two-cycle instruction. |

| COMF             | Complement f                                                                                                                                                   |  |  |  |  |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:          | [label] COMF f,d                                                                                                                                               |  |  |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \end{array}$                                                                                                |  |  |  |  |

| Operation:       | $(\overline{f}) \rightarrow (destination)$                                                                                                                     |  |  |  |  |

| Status Affected: | Z                                                                                                                                                              |  |  |  |  |

| Description:     | The contents of register 'f' are<br>complemented. If 'd' is '0', the<br>result is stored in W. If 'd' is '1',<br>the result is stored back in<br>register 'f'. |  |  |  |  |

| CLRF             | Clear f                                                               |  |

|------------------|-----------------------------------------------------------------------|--|

| Syntax:          | [label] CLRF f                                                        |  |

| Operands:        | $0 \leq f \leq 127$                                                   |  |

| Operation:       | $\begin{array}{l} 00h \rightarrow (f) \\ 1 \rightarrow Z \end{array}$ |  |

| Status Affected: | Z                                                                     |  |

| Description:     | The contents of register 'f' are<br>cleared and the Z bit is set.     |  |

| DECF             | Decrement f                                                                                                                                       |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ label ] DECF f,d                                                                                                                                |

| Operands:        | $\begin{array}{l} 0\leq f\leq 127\\ d\in [0,1] \end{array}$                                                                                       |

| Operation:       | (f) - 1 $\rightarrow$ (destination)                                                                                                               |

| Status Affected: | Z                                                                                                                                                 |

| Description:     | Decrement register 'f'. If 'd' is '0',<br>the result is stored in the W<br>register. If 'd' is '1', the result is<br>stored back in register 'f'. |

| CLRW             | Clear W                                                                                    |

|------------------|--------------------------------------------------------------------------------------------|

| Syntax:          | [label] CLRW                                                                               |

| Operands:        | None                                                                                       |

| Operation:       | $\begin{array}{l} \text{00h} \rightarrow (\text{W}) \\ 1 \rightarrow \text{Z} \end{array}$ |

| Status Affected: | Z                                                                                          |

| Description:     | W register is cleared. Zero bit (Z) is set.                                                |

| RETFIE                      | Return from Interrupt                                                                                                                                            | RETLW            | Return with literal in W                                                                                                                                                            |  |

|-----------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Syntax:                     | [ label ] RETFIE                                                                                                                                                 | Syntax:          | [ <i>label</i> ] RETLW k                                                                                                                                                            |  |

| Operands:                   | None                                                                                                                                                             | Operands:        | $0 \le k \le 255$                                                                                                                                                                   |  |

| Operation:                  | $\begin{array}{l} TOS \to PC, \\ 1 \to GIE \end{array}$                                                                                                          | Operation:       | $k \rightarrow (W);$<br>TOS $\rightarrow PC$                                                                                                                                        |  |

| Status Affected:            | None                                                                                                                                                             | Status Affected: | None                                                                                                                                                                                |  |

| · P<br>lo<br>ei<br>Ir<br>(I | Return from Interrupt. Stack is<br>POPed and Top-of-Stack (TOS) is<br>loaded in the PC. Interrupts are<br>enabled by setting Global<br>Interrupt Enable bit, GIE | Description:     | The W register is loaded with the<br>eight bit literal 'k'. The program<br>counter is loaded from the top of<br>the stack (the return address).<br>This is a two-cycle instruction. |  |

|                             | (INTCON<7>). This is a two-cycle<br>instruction.                                                                                                                 | Words: 1         |                                                                                                                                                                                     |  |

| Words:                      | 1                                                                                                                                                                | Cycles:          | 2                                                                                                                                                                                   |  |

| Cycles:<br>Example:         | 2<br>RETFIE                                                                                                                                                      | Example:         | CALL TABLE;W contains<br>table<br>;offset value                                                                                                                                     |  |

| <u></u>                     | After Interrupt<br>PC = TOS<br>GIE = 1                                                                                                                           | TABLE            | <pre>. ;W now has table value<br/>ADDWF PC ;W = offset<br/>RETLW k1 ;Begin table<br/>RETLW k2 ;</pre>                                                                               |  |

| RETURN           | Return from Subroutine                                                                                                                                     |  |  |  |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Syntax:          | [ label ] RETURN                                                                                                                                           |  |  |  |

| Operands:        | None                                                                                                                                                       |  |  |  |

| Operation:       | $TOS \rightarrow PC$                                                                                                                                       |  |  |  |

| Status Affected: | None                                                                                                                                                       |  |  |  |

| Description:     | Return from subroutine. The stack<br>is POPed and the top of the stack<br>(TOS) is loaded into the program<br>counter. This is a two-cycle<br>instruction. |  |  |  |

**Before Instruction**

After Instruction W =

•

RETLW kn ; End of table

W = 0x07

value of k8

# 14.7 Timing Parameter Symbology

The timing parameter symbols have been created with one of the following formats:

- 1. TppS2ppS

- 2. TppS

| <u>z. rpp3</u> |                                      |     |                |

|----------------|--------------------------------------|-----|----------------|

| т              |                                      |     |                |

| F              | Frequency                            | Т   | Time           |

| Lowerc         | ase letters (pp) and their meanings: |     |                |

| рр             |                                      |     |                |

| сс             | CCP1                                 | OSC | OSC1           |

| ck             | CLKOUT                               | rd  | RD             |

| cs             | CS                                   | rw  | RD or WR       |

| di             | SDI                                  | sc  | SCK            |

| do             | SDO                                  | SS  | SS             |

| dt             | Data in                              | tO  | TOCKI          |

| io             | I/O PORT                             | t1  | T1CKI          |

| mc             | MCLR                                 | wr  | WR             |

| Upperc         | ase letters and their meanings:      |     |                |

| S              |                                      |     |                |

| F              | Fall                                 | Р   | Period         |

| н              | High                                 | R   | Rise           |

| I              | Invalid (High-impedance)             | V   | Valid          |

| L              | Low                                  | Z   | High-impedance |

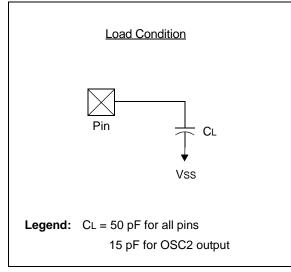

## FIGURE 14-3: LOAD CONDITIONS

# 14.8 AC Characteristics: PIC16F688 (Industrial, Extended)

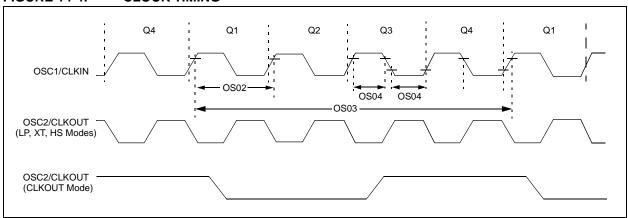

## FIGURE 14-4: CLOCK TIMING

# TABLE 14-1: CLOCK OSCILLATOR TIMING REQUIREMENTS

| Standard Operating Conditions (unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +125^{\circ}C$ |       |                                         |     |        |        |       |                    |

|----------------------------------------------------------------------------------------------------------------------|-------|-----------------------------------------|-----|--------|--------|-------|--------------------|

| Param<br>No.                                                                                                         | Sym   | Characteristic                          | Min | Тур†   | Max    | Units | Conditions         |

| OS01                                                                                                                 | Fosc  | External CLKIN Frequency <sup>(1)</sup> | DC  | _      | 37     | kHz   | LP Oscillator mode |

|                                                                                                                      |       |                                         | DC  | —      | 4      | MHz   | XT Oscillator mode |

|                                                                                                                      |       |                                         | DC  | —      | 20     | MHz   | HS Oscillator mode |

|                                                                                                                      |       |                                         | DC  | —      | 20     | MHz   | EC Oscillator mode |

|                                                                                                                      |       | Oscillator Frequency <sup>(1)</sup>     | —   | 32.768 | —      | kHz   | LP Oscillator mode |

|                                                                                                                      |       |                                         | 0.1 | —      | 4      | MHz   | XT Oscillator mode |

|                                                                                                                      |       |                                         | 1   | —      | 20     | MHz   | HS Oscillator mode |

|                                                                                                                      |       |                                         | DC  | —      | 4      | MHz   | RC Oscillator mode |

| OS02                                                                                                                 | Tosc  | External CLKIN Period <sup>(1)</sup>    | 27  | —      | •      | μS    | LP Oscillator mode |

|                                                                                                                      |       |                                         | 250 | —      | •      | ns    | XT Oscillator mode |

|                                                                                                                      |       |                                         | 50  | —      | •      | ns    | HS Oscillator mode |

|                                                                                                                      |       |                                         | 50  | —      | •      | ns    | EC Oscillator mode |

|                                                                                                                      |       | Oscillator Period <sup>(1)</sup>        | —   | 30.5   | —      | μS    | LP Oscillator mode |

|                                                                                                                      |       |                                         | 250 | —      | 10,000 | ns    | XT Oscillator mode |

|                                                                                                                      |       |                                         | 50  | —      | 1,000  | ns    | HS Oscillator mode |

|                                                                                                                      |       |                                         | 250 | —      | —      | ns    | RC Oscillator mode |

| OS03                                                                                                                 | Тсү   | Instruction Cycle Time <sup>(1)</sup>   | 200 | TCY    | DC     | ns    | TCY = 4/FOSC       |

| OS04*                                                                                                                | TosH, | External CLKIN High,                    | 2   | —      | —      | μS    | LP oscillator      |

|                                                                                                                      | TosL  | External CLKIN Low                      | 100 | —      | —      | ns    | XT oscillator      |

|                                                                                                                      |       |                                         | 20  | —      | —      | ns    | HS oscillator      |

| OS05*                                                                                                                | TosR, | External CLKIN Rise,                    | 0   | —      | ٠      | ns    | LP oscillator      |

|                                                                                                                      | TosF  | External CLKIN Fall                     | 0   | —      | •      | ns    | XT oscillator      |

|                                                                                                                      |       |                                         | 0   |        | •      | ns    | HS oscillator      |

These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

**Note 1:** Instruction cycle period (TCY) equals four times the input oscillator time base period. All specified values are based on characterization data for that particular oscillator type under standard operating conditions with the device executing code. Exceeding these specified limits may result in an unstable oscillator operation and/or higher than expected current consumption. All devices are tested to operate at "min" values with an external clock applied to OSC1 pin. When an external clock input is used, the "max" cycle time limit is "DC" (no clock) for all devices.

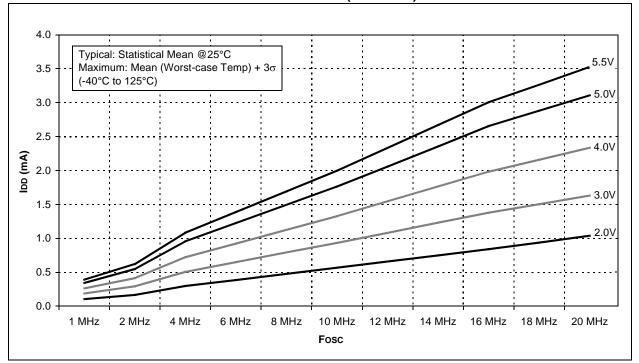

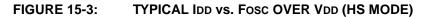

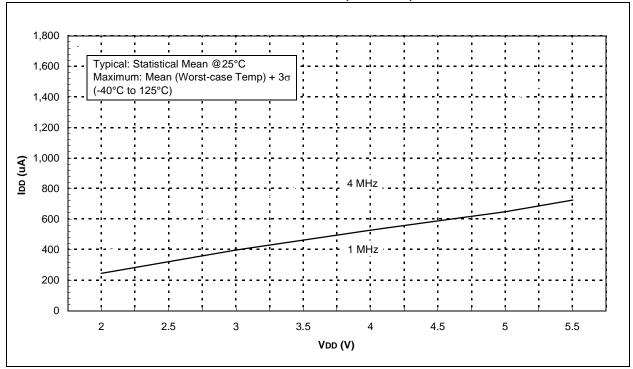

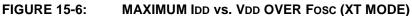

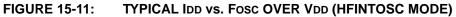

FIGURE 15-2: MAXIMUM IDD vs. Fosc OVER VDD (EC MODE)

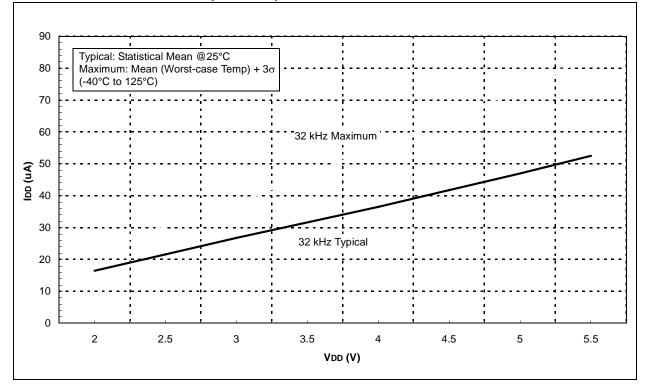

# FIGURE 15-10: IDD vs. VDD (LP MODE)

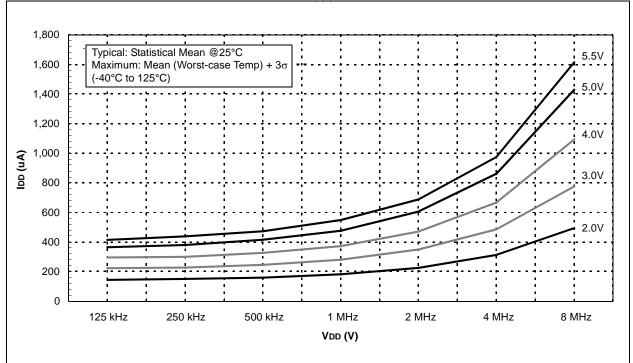

# 16-Lead Plastic Quad Flat, No Lead Package (ML) – 4x4x0.9 mm Body [QFN]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                        | Units |          |          | MILLIMETERS |  |  |  |

|------------------------|-------|----------|----------|-------------|--|--|--|

|                        | MIN   | NOM      | MAX      |             |  |  |  |

| Number of Pins         | N     |          | 16       |             |  |  |  |

| Pitch                  | e     |          | 0.65 BSC |             |  |  |  |

| Overall Height         | A     | 0.80     | 0.90     | 1.00        |  |  |  |

| Standoff               | A1    | 0.00     | 0.02     | 0.05        |  |  |  |

| Contact Thickness      | A3    | 0.20 REF |          |             |  |  |  |

| Overall Width          | E     |          | 4.00 BSC |             |  |  |  |

| Exposed Pad Width      | E2    | 2.50     | 2.65     | 2.80        |  |  |  |

| Overall Length         | D     | 4.00 BSC |          |             |  |  |  |

| Exposed Pad Length     | D2    | 2.50     | 2.65     | 2.80        |  |  |  |

| Contact Width          | b     | 0.25     | 0.30     | 0.35        |  |  |  |

| Contact Length         | L     | 0.30     | 0.40     | 0.50        |  |  |  |

| Contact-to-Exposed Pad | К     | 0.20     | -        | -           |  |  |  |

#### Notes:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. Package is saw singulated.

- 3. Dimensioning and tolerancing per ASME Y14.5M.

- BSC: Basic Dimension. Theoretically exact value shown without tolerances.

- REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-127B