# E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                          |

|----------------------------|--------------------------------------------------------------------------|

| Product Status             | Active                                                                   |

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 20MHz                                                                    |

| Connectivity               | UART/USART                                                               |

| Peripherals                | Brown-out Detect/Reset, POR, WDT                                         |

| Number of I/O              | 12                                                                       |

| Program Memory Size        | 7KB (4K x 14)                                                            |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | 256 x 8                                                                  |

| RAM Size                   | 256 x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                |

| Data Converters            | A/D 8x10b                                                                |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 14-SOIC (0.154", 3.90mm Width)                                           |

| Supplier Device Package    | 14-SOIC                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f688-i-sl |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

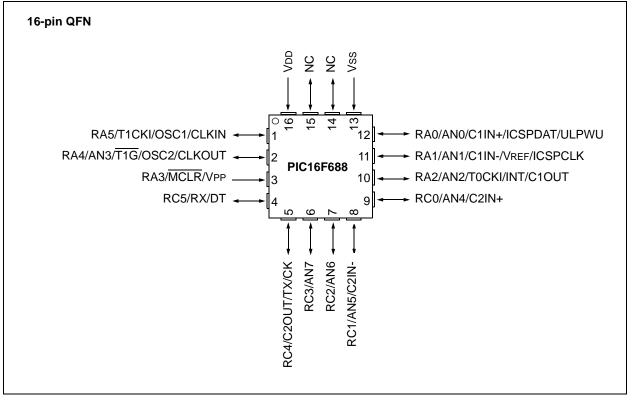

### Pin Diagram (QFN)

| TABLE 2: | PIC16F688 | 16-PIN SUMMARY ( | QFN)      |

|----------|-----------|------------------|-----------|

|          |           |                  | Q 1 1 1 / |

| I/O |     |           |             |        |        |           |         |              |

|-----|-----|-----------|-------------|--------|--------|-----------|---------|--------------|

| 1/0 | Pin | Analog    | Comparators | Timers | EUSART | Interrupt | Pull-up | Basic        |

| RA0 | 12  | AN0/ULPWU | C1IN+       | —      | —      | IOC       | Y       | ICSPDAT      |

| RA1 | 11  | AN1       | C1IN-       | _      | —      | IOC       | Y       | VREF/ICSPCLK |

| RA2 | 10  | AN2       | C1OUT       | T0CKI  | _      | IOC/INT   | Y       | —            |

| RA3 | 3   | —         | —           | _      | —      | IOC       | Y(1)    | MCLR/VPP     |

| RA4 | 2   | AN3       | —           | T1G    | —      | IOC       | Y       | OSC2/CLKOUT  |

| RA5 | 1   | _         | —           | T1CKI  | —      | IOC       | Y       | OSC1/CLKIN   |

| RC0 | 9   | AN4       | C2IN+       |        | —      |           |         | —            |

| RC1 | 8   | AN5       | C2IN-       | —      | _      | _         | _       | —            |

| RC2 | 7   | AN6       | —           | _      | _      |           |         | —            |

| RC3 | 6   | AN7       | —           | _      |        | _         |         | —            |

| RC4 | 5   | —         | C2OUT       | _      | TX/CK  | _         |         | —            |

| RC5 | 4   | _         | —           | _      | RX/DT  |           |         | _            |

| —   | 16  | —         | —           | _      |        | _         |         | Vdd          |

| —   | 13  |           |             | _      | _      | _         | _       | Vss          |

| —   | 14  |           |             | _      | _      | _         | -       | NC           |

| —   | 15  |           |             |        | _      |           | _       | NC           |

**Note 1:** Pull-up activated only with external MCLR configuration.

### 3.2 Oscillator Control

The Oscillator Control (OSCCON) register (Figure 3-1) controls the system clock and frequency selection options. The OSCCON register contains the following bits:

- Frequency selection bits (IRCF)

- Frequency Status bits (HTS, LTS)

- System clock control bits (OSTS, SCS)

### REGISTER 3-1: OSCCON: OSCILLATOR CONTROL REGISTER

| U-0   | R/W-1 | R/W-1 | R/W-0 | R-1                 | R-0 | R-0 | R/W-0 |

|-------|-------|-------|-------|---------------------|-----|-----|-------|

| —     | IRCF2 | IRCF1 | IRCF0 | OSTS <sup>(1)</sup> | HTS | LTS | SCS   |

| bit 7 |       |       |       |                     |     |     | bit 0 |

|       |       |       |       |                     |     |     |       |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

| bit 7   | Unimplemented: Read as '0'                                                                                                                                                                                |

|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 6-4 | IRCF<2:0>: Internal Oscillator Frequency Select bits                                                                                                                                                      |

|         | 111 = 8 MHz                                                                                                                                                                                               |

|         | 110 = 4 MHz (default)                                                                                                                                                                                     |

|         | 101 = 2 MHz                                                                                                                                                                                               |

|         | 100 = 1  MHz                                                                                                                                                                                              |

|         | 011 = 500  kHz                                                                                                                                                                                            |

|         | 010 = 250  kHz                                                                                                                                                                                            |

|         | 001 = 125  kHz                                                                                                                                                                                            |

|         | 000 = 31  kHz (LFINTOSC)                                                                                                                                                                                  |

| bit 3   | <b>OSTS:</b> Oscillator Start-up Time-out Status bit <sup>(1)</sup>                                                                                                                                       |

|         | <ul> <li>1 = Device is running from the external clock defined by FOSC&lt;2:0&gt; of the Configuration Word</li> <li>0 = Device is running from the internal oscillator (HFINTOSC or LFINTOSC)</li> </ul> |

| bit 2   | HTS: HFINTOSC Status bit (High Frequency – 8 MHz to 125 kHz)                                                                                                                                              |

|         | 1 = HFINTOSC is stable                                                                                                                                                                                    |

|         | 0 = HFINTOSC is not stable                                                                                                                                                                                |

| bit 1   | LTS: LFINTOSC Stable bit (Low Frequency – 31 kHz)                                                                                                                                                         |

|         | 1 = LFINTOSC is stable                                                                                                                                                                                    |

|         | 0 = LFINTOSC is not stable                                                                                                                                                                                |

| bit 0   | SCS: System Clock Select bit                                                                                                                                                                              |

|         | 1 = Internal oscillator is used for system clock                                                                                                                                                          |

|         | 0 = Clock source defined by FOSC<2:0> of the Configuration Word                                                                                                                                           |

| Note 4. | Bit resets to '0' with Two-Speed Start-up and LP, XT or HS selected as the Oscillator mode or Eail-Safe                                                                                                   |

**Note 1:** Bit resets to '0' with Two-Speed Start-up and LP, XT or HS selected as the Oscillator mode or Fail-Safe mode is enabled.

#### 3.4.4 EXTERNAL RC MODES

The external Resistor-Capacitor (RC) modes support the use of an external RC circuit. This allows the designer maximum flexibility in frequency choice while keeping costs to a minimum when clock accuracy is not required. There are two modes: RC and RCIO.

In RC mode, the RC circuit connects to OSC1. OSC2/ CLKOUT outputs the RC oscillator frequency divided by 4. This signal may be used to provide a clock for external circuitry, synchronization, calibration, test or other application requirements. Figure 3-5 shows the external RC mode connections.

VDD PIC<sup>®</sup> MCU REXT OSC1/CLKIN Internal Clock CEXT Vss -Fosc/4 or OSC2/CLKOUT(1) I/O<sup>(2)</sup> Recommended values: 10 k $\Omega \leq \text{REXT} \leq 100 \text{ k}\Omega$ , <3V  $3 \text{ k}\Omega \leq \text{Rext} \leq 100 \text{ k}\Omega, 3-5 \text{V}$ CEXT > 20 pF, 2-5V Note 1: Alternate pin functions are listed in Section 1.0 "Device Overview". 2: Output depends upon RC or RCIO clock mode

FIGURE 3-5: EXTERNAL RC MODES

In RCIO mode, the RC circuit is connected to OSC1. OSC2 becomes an additional general purpose I/O pin.

The RC oscillator frequency is a function of the supply voltage, the resistor (REXT) and capacitor (CEXT) values and the operating temperature. Other factors affecting the oscillator frequency are:

- threshold voltage variation

- component tolerances

- packaging variations in capacitance

The user also needs to take into account variation due to tolerance of external RC components used.

#### 3.5 Internal Clock Modes

The oscillator module has two independent, internal oscillators that can be configured or selected as the system clock source.

- 1. The **HFINTOSC** (High-Frequency Internal Oscillator) is factory calibrated and operates at 8 MHz. The frequency of the HFINTOSC can be user-adjusted via software using the OSCTUNE register (Register 3-2).

- 2. The **LFINTOSC** (Low-Frequency Internal Oscillator) is uncalibrated and operates at 31 kHz.

The system clock speed can be selected via software using the Internal Oscillator Frequency Select bits IRCF<2:0> of the OSCCON register.

The system clock can be selected between external or internal clock sources via the System Clock Selection (SCS) bit of the OSCCON register. See **Section 3.6 "Clock Switching"** for more information.

#### 3.5.1 INTOSC AND INTOSCIO MODES

The INTOSC and INTOSCIO modes configure the internal oscillators as the system clock source when the device is programmed using the oscillator selection or the FOSC<2:0> bits in the Configuration Word register (CONFIG). See Section 11.0 "Special Features of the CPU" for more information.

In **INTOSC** mode, OSC1/CLKIN is available for general purpose I/O. OSC2/CLKOUT outputs the selected internal oscillator frequency divided by 4. The CLKOUT signal may be used to provide a clock for external circuitry, synchronization, calibration, test or other application requirements.

In **INTOSCIO** mode, OSC1/CLKIN and OSC2/CLKOUT are available for general purpose I/O.

#### 3.5.2 HFINTOSC

The High-Frequency Internal Oscillator (HFINTOSC) is a factory calibrated 8 MHz internal clock source. The frequency of the HFINTOSC can be altered via software using the OSCTUNE register (Register 3-2).

The output of the HFINTOSC connects to a postscaler and multiplexer (see Figure 3-1). One of seven frequencies can be selected via software using the IRCF<2:0> bits of the OSCCON register. See **Section 3.5.4 "Frequency Select Bits (IRCF)"** for more information.

The HFINTOSC is enabled by selecting any frequency between 8 MHz and 125 kHz by setting the IRCF<2:0> bits of the OSCCON register  $\neq$  000. Then, set the System Clock Source (SCS) bit of the OSCCON register to '1' or enable Two-Speed Start-up by setting the IESO bit in the Configuration Word register (CONFIG) to '1'.

The HF Internal Oscillator (HTS) bit of the OSCCON register indicates whether the HFINTOSC is stable or not.

# PIC16F688

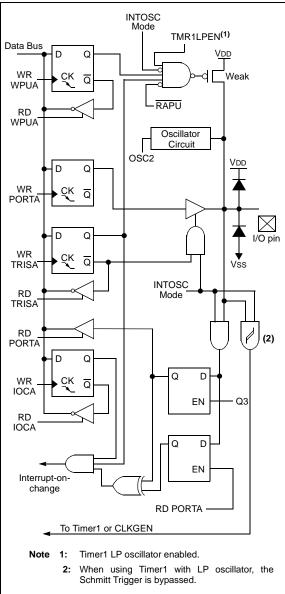

#### 4.2.5.6 RA5/T1CKI/OSC1/CLKIN

Figure 4-6 shows the diagram for this pin. The RA5 pin is configurable to function as one of the following:

- a general purpose I/O

- a Timer1 clock input

- a crystal/resonator connection

- a clock input

FIGURE 4-6: BLOCK DIAGRAM OF RA5

### 4.3 PORTC

PORTC is a general purpose I/O port consisting of 6 bidirectional pins. The pins can be configured for either digital I/O or analog input to A/D converter or comparator. For specific information about individual functions such as the EUSART or the A/D converter, refer to the appropriate section in this data sheet.

| Note: | The ANSEL and CMCON0 registers must         |  |  |  |  |  |  |  |

|-------|---------------------------------------------|--|--|--|--|--|--|--|

|       | be initialized to configure an analog       |  |  |  |  |  |  |  |

|       | channel as a digital input. Pins configured |  |  |  |  |  |  |  |

|       | as analog inputs will read '0'.             |  |  |  |  |  |  |  |

#### EXAMPLE 4-3: INITIALIZING PORTC

| BANKSEL | PORTC  | ;                      |

|---------|--------|------------------------|

| CLRF    | PORTC  | ;Init PORTC            |

| MOVLW   | 07h    | ;Set RC<4,1:0> to      |

| MOVWF   | CMCON0 | ;digital I/O           |

| BANKSEL | ANSEL  | ;                      |

| CLRF    | ANSEL  | ;digital I/O           |

| MOVLW   | 0Ch    | ;Set RC<3:2> as inputs |

| MOVWF   | TRISC  | ;and set RC<5:4,1:0>   |

|         |        | ;as outputs            |

|         |        |                        |

#### REGISTER 4-6: PORTC: PORTC REGISTER

| U-0   | U-0 | R/W-x | R/W-x | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|-------|-----|-------|-------|-------|-------|-------|-------|

| —     | —   | RC5   | RC4   | RC3   | RC2   | RC1   | RC0   |

| bit 7 |     |       |       |       |       |       | bit 0 |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

|                   |                  |                        |                    |

| bit 7-6 | Unimplemented: Read as '0' |

|---------|----------------------------|

|---------|----------------------------|

bit 5-0 **RC<5:0>**: PORTC I/O Pin bit 1 = PORTC pin is > VIH

0 = PORTC pin is < VIL

#### **REGISTER 4-7:** TRISC: PORTC TRI-STATE REGISTER

| U-0   | U-0 | R/W-1  | R/W-1  | R/W-1  | R/W-1  | R/W-1  | R/W-1  |

|-------|-----|--------|--------|--------|--------|--------|--------|

| —     | —   | TRISC5 | TRISC4 | TRISC3 | TRISC2 | TRISC1 | TRISC0 |

| bit 7 |     |        |        |        |        |        | bit 0  |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | l as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

bit 7-6 Unimplemented: Read as '0'

TRISC<5:0>: PORTC Tri-State Control bits

1 = PORTC pin configured as an input (tri-stated)

0 = PORTC pin configured as an output

bit 5-0

### 6.9 Timer1 Control Register

The Timer1 Control register (T1CON), shown in Register 6-1, is used to control Timer1 and select the various features of the Timer1 module.

#### REGISTER 6-1: T1CON: TIMER 1 CONTROL REGISTER

| R/W-0               | R/W-0                                                                                                                                                                                                       | R/W-0                                                                                                                                                                                                                                                                                  | R/W-0           | R/W-0             | R/W-0           | R/W-0           | R/W-0      |  |

|---------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|-------------------|-----------------|-----------------|------------|--|

| T1GINV <sup>(</sup> | <sup>1)</sup> TMR1GE <sup>(2)</sup>                                                                                                                                                                         | T1CKPS1                                                                                                                                                                                                                                                                                | T1CKPS0         | T1OSCEN           | T1SYNC          | TMR1CS          | TMR10N     |  |

| bit 7               |                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                        |                 |                   |                 | ·               | bit 0      |  |

|                     |                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                        |                 |                   |                 |                 |            |  |

| Legend:             |                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                        |                 |                   |                 |                 |            |  |

| R = Reada           | ble bit                                                                                                                                                                                                     | W = Writable                                                                                                                                                                                                                                                                           | bit             | U = Unimplen      | nented bit, rea | d as '0'        |            |  |

| -n = Value          | at POR                                                                                                                                                                                                      | '1' = Bit is set                                                                                                                                                                                                                                                                       |                 | '0' = Bit is clea | ared            | x = Bit is unkr | nown       |  |

| bit 7               | 1 = Timer1 ga                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                        | h (Timer1 cou   | nts when gate i   |                 |                 |            |  |

| bit 6               | TMR1GE: Tin<br>If TMR1ON =<br>This bit is igno<br>If TMR1ON =                                                                                                                                               | <ul> <li>0 = Timer1 gate is active low (Timer1 counts when gate is low)</li> <li>TMR1GE: Timer1 Gate Enable bit<sup>(2)</sup></li> <li><u>If TMR1ON = 0</u>:</li> <li>This bit is ignored</li> <li><u>If TMR1ON = 1</u>:</li> <li>1 = Timer1 is on if Timer1 gate is active</li> </ul> |                 |                   |                 |                 |            |  |

| bit 5-4             | T1CKPS<1:0                                                                                                                                                                                                  | >: Timer1 Inpu                                                                                                                                                                                                                                                                         | t Clock Presca  | ale Select bits   |                 |                 |            |  |

|                     | 10 = 1:4 Pres<br>01 = 1:2 Pres                                                                                                                                                                              | 11 = 1:8 Prescale Value<br>10 = 1:4 Prescale Value<br>01 = 1:2 Prescale Value<br>00 = 1:1 Prescale Value                                                                                                                                                                               |                 |                   |                 |                 |            |  |

| bit 3               | T1OSCEN: LI                                                                                                                                                                                                 | P Oscillator En                                                                                                                                                                                                                                                                        | able Control b  | it                |                 |                 |            |  |

|                     | If INTOSC without CLKOUT oscillator is active:         1 = LP oscillator is enabled for Timer1 clock         0 = LP oscillator is off         Else:         This bit is ignored. LP oscillator is disabled. |                                                                                                                                                                                                                                                                                        |                 |                   |                 |                 |            |  |

| bit 2               |                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                        | lock Input Syn  | chronization Co   | ontrol bit      |                 |            |  |

|                     | $\frac{\text{TMR1CS} = 1}{1}$ 1 = Do not synchronize external clock input 0 = Synchronize external clock input $\frac{\text{TMR1CS} = 0}{1}$ This bit is ignored. Timer1 uses the internal clock            |                                                                                                                                                                                                                                                                                        |                 |                   |                 |                 |            |  |

| bit 1               | •                                                                                                                                                                                                           | ner1 Clock Sou                                                                                                                                                                                                                                                                         |                 |                   |                 |                 |            |  |

|                     |                                                                                                                                                                                                             | clock from T1C                                                                                                                                                                                                                                                                         |                 | rising edge)      |                 |                 |            |  |

| bit 0               | <b>TMR1ON:</b> Tin<br>1 = Enables T<br>0 = Stops Tim                                                                                                                                                        | īmer1                                                                                                                                                                                                                                                                                  |                 |                   |                 |                 |            |  |

| 2:                  | T1GINV bit inverts<br>TMR1GE bit must<br>register, as a Time                                                                                                                                                | be set to use e                                                                                                                                                                                                                                                                        | ither T1G pin o |                   |                 | T1GSS bit of th | ne CM2CON1 |  |

#### 7.3.3 COMPARATOR INPUT SWITCH

The inverting input of the comparators may be switched between two analog pins in the following modes:

- CM<2:0> = 001 (Comparator C1 only)

- CM<2:0> = 010 (Comparators C1 and C2)

In the above modes, both pins remain in analog mode regardless of which pin is selected as the input. The CIS bit of the CMCON0 register controls the comparator input switch.

#### 7.4 Comparator Response Time

The comparator output is indeterminate for a period of time after the change of an input source or the selection of a new reference voltage. This period is referred to as the response time. The response time of the comparator differs from the settling time of the voltage reference. Therefore, both of these times must be considered when determining the total response time to a comparator input change. See the Comparator and Voltage Reference specifications in **Section 14.0 "Electrical Specifications"** for more details.

#### 7.5 Comparator Interrupt Operation

The comparator interrupt flag is set whenever there is a change in the output value of the comparator. Changes are recognized by means of a mismatch circuit which consists of two latches and an exclusiveor gate (see Figure 7-2 and Figure 7-3). One latch is updated with the comparator output level when the CMCON0 register is read. This latch retains the value until the next read of the CMCON0 register or the occurrence of a Reset. The other latch of the mismatch circuit is updated on every Q1 system clock. A mismatch condition will occur when a comparator output change is clocked through the second latch on the Q1 clock cycle. The mismatch condition will persist, holding the CxIF bit of the PIR1 register true, until either the CMCON0 register is read or the comparator output returns to the previous state.

| Note: | A write operation to the CMCON0 register |

|-------|------------------------------------------|

|       | will also clear the mismatch condition   |

|       | because all writes include a read        |

|       | operation at the beginning of the write  |

|       | cycle.                                   |

Software will need to maintain information about the status of the comparator output to determine the actual change that has occurred.

The CxIF bit of the PIR1 register is the comparator interrupt flag. This bit must be reset in software by clearing it to '0'. Since it is also possible to write a '1' to this register, a simulated interrupt may be initiated.

The CxIE bit of the PIE1 register and the PEIE and GIE bits of the INTCON register must all be set to enable comparator interrupts. If any of these bits are cleared, the interrupt is not enabled, although the CxIF bit of the PIR1 register will still be set if an interrupt condition occurs.

The user, in the Interrupt Service Routine, can clear the interrupt in the following manner:

- a) Any read or write of CMCON0. This will end the mismatch condition. See Figures 7-6 and 7-7

- b) Clear the CxIF interrupt flag.

A persistent mismatch condition will preclude clearing the CxIF interrupt flag. Reading CMCON0 will end the mismatch condition and allow the CxIF bit to be cleared.

| R-0           | R-0                                      | R/W-0                             | R/W-0           | R/W-0            | R/W-0           | R/W-0           | R/W-0 |  |

|---------------|------------------------------------------|-----------------------------------|-----------------|------------------|-----------------|-----------------|-------|--|

| C2OUT         | C1OUT                                    | C2INV                             | C1INV           | CIS              | CM2             | CM1             | CM0   |  |

| bit 7         |                                          |                                   |                 |                  |                 |                 | bit 0 |  |

|               |                                          |                                   |                 |                  |                 |                 |       |  |

| Legend:       |                                          |                                   |                 |                  |                 |                 |       |  |

| R = Readabl   |                                          | W = Writable                      |                 | -                | mented bit, rea | ad as '0'       |       |  |

| -n = Value at | POR                                      | '1' = Bit is set                  |                 | '0' = Bit is cle | eared           | x = Bit is unkr | nown  |  |

| L:1 7         | 000117                                   |                                   |                 |                  |                 |                 |       |  |

| bit 7         |                                          | nparator 2 Outp                   | ut dit          |                  |                 |                 |       |  |

|               | <u>When C2INV</u><br>1 = C2 VIN+ :       |                                   |                 |                  |                 |                 |       |  |

|               | 0 = C2 VIN+ .                            | -                                 |                 |                  |                 |                 |       |  |

|               | When C2INV                               |                                   |                 |                  |                 |                 |       |  |

|               | 1 = C2 VIN+ ·                            |                                   |                 |                  |                 |                 |       |  |

|               | 0 = C2 VIN+ :                            | > C2 VIN-                         |                 |                  |                 |                 |       |  |

| bit 6         | C1OUT: Corr                              | nparator 1 Outp                   | ut bit          |                  |                 |                 |       |  |

|               | When C1INV                               | <u>' = 0:</u>                     |                 |                  |                 |                 |       |  |

|               | 1 = C1 VIN+ :                            |                                   |                 |                  |                 |                 |       |  |

|               | $0 = C1 VIN + \cdot$                     |                                   |                 |                  |                 |                 |       |  |

|               | When C1INV                               |                                   |                 |                  |                 |                 |       |  |

|               | 1 = C1 VIN+ ·<br>0 = C1 VIN+ :           |                                   |                 |                  |                 |                 |       |  |

| bit 5         | C2INV: Comparator 2 Output Inversion bit |                                   |                 |                  |                 |                 |       |  |

| bit o         | 1 = C2 outpu                             | -                                 |                 | L                |                 |                 |       |  |

|               |                                          | t not inverted                    |                 |                  |                 |                 |       |  |

| bit 4         | C1INV: Com                               | parator 1 Outpu                   | ut Inversion bi | t                |                 |                 |       |  |

|               | 1 = C1 Outpu                             | ut inverted                       |                 |                  |                 |                 |       |  |

|               | 0 = C1 Outpu                             | ut not inverted                   |                 |                  |                 |                 |       |  |

| bit 3         | CIS: Compar                              | ator Input Swit                   | ch bit          |                  |                 |                 |       |  |

|               | When CM<2:                               | : <b>0&gt; =</b> 010:             |                 |                  |                 |                 |       |  |

|               |                                          | onnects to C1 V                   |                 |                  |                 |                 |       |  |

|               |                                          | onnects to C2                     |                 |                  |                 |                 |       |  |

|               |                                          | nnects to C1 V<br>Innects to C2 V |                 |                  |                 |                 |       |  |

|               | When CM<2:                               |                                   |                 |                  |                 |                 |       |  |

|               | 1 = C1IN+ co                             | onnects to C1 V                   | 'IN-            |                  |                 |                 |       |  |

|               | 0 = C1IN- co                             | nnects to C1 V                    | N-              |                  |                 |                 |       |  |

| bit 2-0       | CM<2:0>: Co                              | omparator Mod                     | e bits (See Fig | gure 7-5)        |                 |                 |       |  |

|               |                                          |                                   | •               | figured as ana   | log             |                 |       |  |

|               |                                          | inputs multiple                   |                 |                  |                 |                 |       |  |

|               |                                          | nputs multiplex<br>common referen |                 |                  |                 |                 |       |  |

|               |                                          | dependent con                     |                 | 15               |                 |                 |       |  |

|               |                                          | dependent cor                     |                 |                  |                 |                 |       |  |

|               | 110 <b>= Two co</b>                      | ommon referen                     | ce comparato    | rs with outputs  |                 |                 |       |  |

|               | 111 <b>= Comp</b> a                      | arators off. CxII                 | N pins are cor  | figured as digit | al I/O          |                 |       |  |

#### REGISTER 7-1: CMCON0: COMPARATOR CONFIGURATION REGISTER

#### 8.1.5 INTERRUPTS

The ADC module allows for the ability to generate an interrupt upon completion of an Analog-to-Digital Conversion. The ADC interrupt flag is the ADIF bit in the PIR1 register. The ADC interrupt enable is the ADIE bit in the PIE1 register. The ADIF bit must be cleared in software.

| Note: | The ADIF bit is set at the completion of |  |  |  |  |

|-------|------------------------------------------|--|--|--|--|

|       | every conversion, regardless of whether  |  |  |  |  |

|       | or not the ADC interrupt is enabled.     |  |  |  |  |

This interrupt can be generated while the device is operating or while in Sleep. If the device is in Sleep, the interrupt will wake-up the device. Upon waking from Sleep, the next instruction following the SLEEP instruction is always executed. If the user is attempting to wake-up from Sleep and resume in-line code execution, the global interrupt must be disabled. If the global interrupt is enabled, execution will switch to the Interrupt Service Routine.

Please see **Section 8.1.5** "Interrupts" for more information.

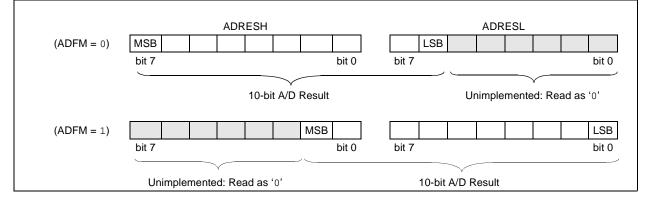

#### FIGURE 8-3: 10-BIT A/D CONVERSION RESULT FORMAT

#### 8.1.6 RESULT FORMATTING

The 10-bit A/D Conversion result can be supplied in two formats, left justified or right justified. The ADFM bit of the ADCON0 register controls the output format.

Figure 8-4 shows the two output formats.

| R/W-x                             | R/W-x  | R/W-x  | R/W-x  | R/W-x                              | R/W-x  | R/W-x  | R/W-x  |  |

|-----------------------------------|--------|--------|--------|------------------------------------|--------|--------|--------|--|

| ADRES9                            | ADRES8 | ADRES7 | ADRES6 | ADRES5                             | ADRES4 | ADRES3 | ADRES2 |  |

| bit 7                             |        |        |        |                                    |        |        | bit 0  |  |

|                                   |        |        |        |                                    |        |        |        |  |

| Legend:                           |        |        |        |                                    |        |        |        |  |

| R = Readable bit W = Writable bit |        |        | t      | U = Unimplemented bit, read as '0' |        |        |        |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

|-------------------|------------------|----------------------|--------------------|

bit 7-0 ADRES<9:2>: ADC Result Register bits Upper 8 bits of 10-bit conversion result

#### **REGISTER 8-4:** ADRESL: ADC RESULT REGISTER LOW (ADRESL) ADFM = 0

| R/W-x                                                                | R/W-x  | R/W-x            | R/W-x | R/W-x                                   | R/W-x | R/W-x | R/W-x |

|----------------------------------------------------------------------|--------|------------------|-------|-----------------------------------------|-------|-------|-------|

| ADRES1                                                               | ADRES0 | —                | —     | —                                       | —     | —     | —     |

| bit 7                                                                |        |                  |       |                                         |       |       | bit 0 |

|                                                                      |        |                  |       |                                         |       |       |       |

| Legend:                                                              |        |                  |       |                                         |       |       |       |

| R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' |        |                  |       |                                         |       |       |       |

| -n = Value at PO                                                     | R      | '1' = Bit is set |       | '0' = Bit is cleared x = Bit is unknown |       |       |       |

| bit 7-6 | <b>ADRES&lt;1:0&gt;</b> : ADC Result Register bits Lower 2 bits of 10-bit conversion result |

|---------|---------------------------------------------------------------------------------------------|

| bit 5-0 | Reserved: Do not use.                                                                       |

#### REGISTER 8-5: ADRESH: ADC RESULT REGISTER HIGH (ADRESH) ADFM = 1

| R/W-x  | R/W-x  |

|-------|-------|-------|-------|-------|-------|--------|--------|

| —     | —     | —     | —     | —     | —     | ADRES9 | ADRES8 |

| bit 7 |       |       |       |       |       |        | bit 0  |

| Legend:                                                              |                  |                      |                    |

|----------------------------------------------------------------------|------------------|----------------------|--------------------|

| R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' |                  |                      |                    |

| -n = Value at POR                                                    | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

bit 7-2 Reserved: Do not use.

bit 1-0 ADRES<9:8>: ADC Result Register bits Upper 2 bits of 10-bit conversion result

#### REGISTER 8-6: ADRESL: ADC RESULT REGISTER LOW (ADRESL) ADFM = 1

| R/W-x  |

|--------|--------|--------|--------|--------|--------|--------|--------|

| ADRES7 | ADRES6 | ADRES5 | ADRES4 | ADRES3 | ADRES2 | ADRES1 | ADRES0 |

| bit 7  |        |        |        |        |        |        | bit 0  |

| Legend:           |                  |                                |                    |

|-------------------|------------------|--------------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as | · '0'              |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared           | x = Bit is unknown |

bit 7-0 ADRES<7:0>: ADC Result Register bits Lower 8 bits of 10-bit conversion result

## **PIC16F688**

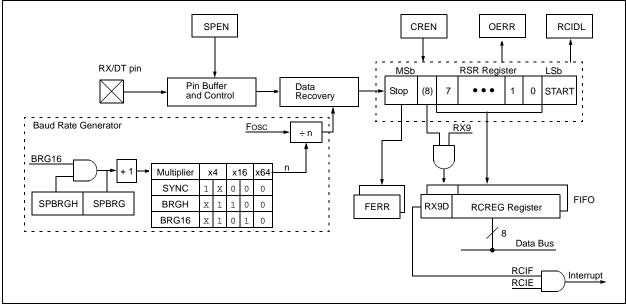

#### FIGURE 10-2: EUSART RECEIVE BLOCK DIAGRAM

The operation of the EUSART module is controlled through three registers:

- Transmit Status and Control (TXSTA)

- Receive Status and Control (RCSTA)

- Baud Rate Control (BAUDCTL)

These registers are detailed in Register 10-1, Register 10-2 and Register 10-3, respectively.

#### 10.3.2 AUTO-BAUD OVERFLOW

During the course of automatic baud detection, the ABDOVF bit of the BAUDCTL register will be set if the baud rate counter overflows before the fifth rising edge is detected on the RX pin. The ABDOVF bit indicates that the counter has exceeded the maximum count that can fit in the 16 bits of the SPBRGH:SPBRG register pair. After the ABDOVF has been set, the counter continues to count until the fifth rising edge is detected on the RX pin. Upon detecting the fifth RX edge, the hardware will set the RCIF interrupt flag and clear the ABDEN bit of the BAUDCTL register. The RCIF flag can be subsequently cleared by reading the RCREG. The ABDOVF flag can be cleared by software directly.

To terminate the auto-baud process before the RCIF flag is set, clear the ABDEN bit then clear the ABDOVF bit. The ABDOVF bit will remain set if the ABDEN bit is not cleared first.

#### 10.3.3 AUTO-WAKE-UP ON BREAK

During Sleep mode, all clocks to the EUSART are suspended. Because of this, the Baud Rate Generator is inactive and a proper character reception cannot be performed. The Auto-Wake-up feature allows the controller to wake-up due to activity on the RX/DT line. This feature is available only in Asynchronous mode.

The Auto-Wake-up feature is enabled by setting the WUE bit of the BAUDCTL register. Once set, the normal receive sequence on RX/DT is disabled, and the EUSART remains in an Idle state, monitoring for a wake-up event independent of the CPU mode. A wake-up event consists of a high-to-low transition on the RX/DT line. (This coincides with the start of a Sync Break or a wake-up signal character for the LIN protocol.)

The EUSART module generates an RCIF interrupt coincident with the wake-up event. The interrupt is generated synchronously to the Q clocks in normal CPU operating modes (Figure 10-7), and asynchronously if the device is in Sleep mode (Figure 10-8). The interrupt condition is cleared by reading the RCREG register.

The WUE bit is automatically cleared by the low-to-high transition on the RX line at the end of the Break. This signals to the user that the Break event is over. At this point, the EUSART module is in Idle mode waiting to receive the next character.

#### 10.3.3.1 Special Considerations

#### Break Character

To avoid character errors or character fragments during a wake-up event, the wake-up character must be all zeros.

When the wake-up is enabled the function works independent of the low time on the data stream. If the WUE bit is set and a valid non-zero character is received, the low time from the Start bit to the first rising edge will be interpreted as the wake-up event. The remaining bits in the character will be received as a fragmented character and subsequent characters can result in framing or overrun errors.

Therefore, the initial character in the transmission must be all '0's. This must be 10 or more bit times, 13-bit times recommended for LIN bus, or any number of bit times for standard RS-232 devices.

#### Oscillator Start-up Time

Oscillator start-up time must be considered, especially in applications using oscillators with longer start-up intervals (i.e., LP, XT or HS mode). The Sync Break (or wake-up signal) character must be of sufficient length, and be followed by a sufficient interval, to allow enough time for the selected oscillator to start and provide proper initialization of the EUSART.

#### WUE Bit

The wake-up event causes a receive interrupt by setting the RCIF bit. The WUE bit is cleared in hardware by a rising edge on RX/DT. The interrupt condition is then cleared in software by reading the RCREG register and discarding its contents.

To ensure that no actual data is lost, check the RCIDL.

#### FIGURE 10-7: AUTO-WAKE-UP BIT (WUE) TIMING DURING NORMAL OPERATION

|          | BR set by a | 5 · · · · · · · · · · · · · · · · · · · | www.y | 1 |                 |        |                                       |                   | · · · · · · · · · · · · · · · · · · · |                                       |

|----------|-------------|-----------------------------------------|-------|---|-----------------|--------|---------------------------------------|-------------------|---------------------------------------|---------------------------------------|

| veus bel |             | ·                                       | .)    |   | 2               |        | (                                     |                   | ·····                                 | · · · · · · · · · · · · · · · · · · · |

| AZE LEVA | •           | · · · · · · · · · · · · · · · · · · ·   | (<br> |   | e<br>Millionnes |        |                                       |                   | *<br>                                 | · · · · · · · · · · · · · · · · · · · |

|          |             | , , , , , , , , , , , , , , , , , , ,   |       | 3 |                 | ۶ (    | · · · · · · · · · · · · · · · · · · · | ·····             | с<br>с                                |                                       |

| 808      |             |                                         |       |   | <u>/</u>        | "<br>1 | Şerse due                             | k<br>No Qoes Read | er RCREG -                            |                                       |

#### 11.2.5 TIME-OUT SEQUENCE

On power-up, the time-out sequence is as follows: first, PWRT time-out is invoked after POR has expired, then OST is activated after the PWRT time-out has expired. The total time-out will vary based on oscillator configuration and PWRTE bit status. For example, in EC mode with PWRTE bit erased (PWRT disabled), there will be no time-out at all. Figure 11.2.1, Figure 11-5 and Figure 11-6 depict time-out sequences. The device can execute code from the INTOSC while OST is active by enabling Two-Speed Start-up or Fail-Safe Monitor (see Section 3.7.2 "Two-Speed Start-up Sequence" and Section 3.8 "Fail-Safe Clock Monitor").

Since the time-outs occur from the POR pulse, if MCLR is kept low long enough, the time-outs will expire. Then, bringing MCLR high will begin execution immediately (see Figure 11-5). This is useful for testing purposes or to synchronize more than one PIC16F688 device operating in parallel.

Table 11-5 shows the Reset conditions for some special registers, while Table 11-4 shows the Reset conditions for all the registers.

#### 11.2.6 POWER CONTROL (PCON) REGISTER

The Power Control (PCON) register (address 8Eh) has two Status bits to indicate what type of Reset that last occurred.

Bit 0 is BOR (Brown-out). BOR is unknown on Power-on Reset. It must then be set by the user and checked on subsequent Resets to see if  $\overline{BOR} = 0$ , indicating that a Brown-out has occurred. The BOR Status bit is a "don't care" and is not necessarily predictable if the brown-out circuit is disabled (BOREN<1:0> = 00 in the Configuration Word register).

Bit 1 is POR (Power-on Reset). It is a '0' on Power-on Reset and unaffected otherwise. The user must write a '1' to this bit following a Power-on Reset. On a subsequent Reset, if POR is '0', it will indicate that a Power-on Reset has occurred (i.e., VDD may have gone too low).

For more information, see Section 4.2.4 "Ultra Low-Power Wake-up" Section 11.2.4 and "Brown-Out Reset (BOR)".

| Oscillator Configuration | Powe                   | er-up       | Brown-o                | Wake-up     |             |

|--------------------------|------------------------|-------------|------------------------|-------------|-------------|

|                          | <b>PWRTE</b> = 0       | PWRTE = 1   | PWRTE = 0              | PWRTE = 1   | from Sleep  |

| XT, HS, LP               | TPWRT + 1024<br>• Tosc | 1024 • Tosc | TPWRT + 1024<br>• Tosc | 1024 • Tosc | 1024 • Tosc |

| RC, EC, INTOSC           | TPWRT                  | _           | TPWRT                  | _           | —           |

#### TIME-OUT IN VARIOUS SITUATIONS **TABLE 11-1:**

| TABLE 11-2: | PCON BITS AND THEIR SIGNIFICANCE |

|-------------|----------------------------------|

|-------------|----------------------------------|

| POR | BOR | ТО | PD | Condition                          |

|-----|-----|----|----|------------------------------------|

| 0   | u   | 1  | 1  | Power-on Reset                     |

| 1   | 0   | 1  | 1  | Brown-out Reset                    |

| u   | u   | 0  | u  | WDT Reset                          |

| u   | u   | 0  | 0  | WDT Wake-up                        |

| u   | u   | u  | u  | MCLR Reset during normal operation |

| u   | u   | 1  | 0  | MCLR Reset during Sleep            |

**Legend:** u = unchanged, x = unknown

#### **TABLE 11-3**: SUMMARY OF REGISTERS ASSOCIATED WITH BROWN-OUT RESET

| Name                  | Bit 9  | Bit 8  | Bit 7 | Bit 6 | Bit 5  | Bit 4  | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Value on<br>POR, BOR | Value on<br>all other<br>Resets <sup>(1)</sup> |

|-----------------------|--------|--------|-------|-------|--------|--------|-------|-------|-------|-------|----------------------|------------------------------------------------|

| CONFIG <sup>(2)</sup> | BOREN1 | BOREN0 | CPD   | CP    | MCLRE  | PWRTE  | WDTE  | FOSC2 | FOSC1 | FOSC0 | _                    | _                                              |

| PCON                  |        |        | _     | _     | ULPWUE | SBOREN | _     | _     | POR   | BOR   | 01qq                 | 0uuu                                           |

| STATUS                |        |        | IRP   | RP1   | RP0    | TO     | PD    | Z     | DC    | С     | 0001 1xxx            | 000q quuu                                      |

u = unchanged, x = unknown, - = unimplemented bit, reads as '0', q = value depends on condition. Shaded cells are not used by BOR. Other (non Power-up) Resets include MCLR Reset and Watchdog Timer Reset during normal operation. Legend: 1:

See Configuration Word register (Register 11-1) for operation of all register bits. 2.

Note

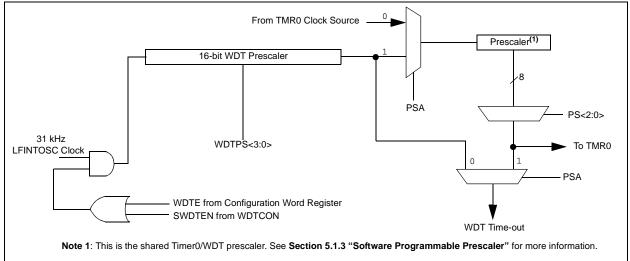

#### 11.5 Watchdog Timer (WDT)

The WDT has the following features:

- Operates from the LFINTOSC (31 kHz)

- Contains a 16-bit prescaler

- Shares an 8-bit prescaler with Timer0

- Time-out period is from 1 ms to 268 seconds

- · Configuration bit and software controlled

WDT is cleared under certain conditions described in Table 11-7.

#### 11.5.1 WDT OSCILLATOR

The WDT derives its time base from the 31 kHz LFINTOSC. The LTS bit does not reflect that the LFINTOSC is enabled.

The value of WDTCON is `---0 1000' on all Resets. This gives a nominal time base of 16 ms, which is compatible with the time base generated with previous PIC16F688 microcontroller versions.

| Note: | When the Oscillator Start-up Timer (OST)   |

|-------|--------------------------------------------|

|       | is invoked, the WDT is held in Reset,      |

|       | because the WDT Ripple Counter is used     |

|       | by the OST to perform the oscillator delay |

|       | count. When the OST count has expired,     |

|       | the WDT will begin counting (if enabled).  |

A new prescaler has been added to the path between the INTRC and the multiplexers used to select the path for the WDT. This prescaler is 16 bits and can be programmed to divide the INTRC by 32 to 65536, giving the WDT a nominal range of 1 ms to 268s.

#### 11.5.2 WDT CONTROL

The WDTE bit is located in the Configuration Word register. When set, the WDT runs continuously.

When the WDTE bit in the Configuration Word register is set, the SWDTEN bit of the WDTCON register has no effect. If WDTE is clear, then the SWDTEN bit can be used to enable and disable the WDT. Setting the bit will enable it and clearing the bit will disable it.

The PSA and PS<2:0> bits of the OPTION register have the same function as in previous versions of the PIC16F688 family of microcontrollers. See **Section 5.0 "Timer0 Module"** for more information.

#### FIGURE 11-9: WATCHDOG TIMER BLOCK DIAGRAM

#### TABLE 11-7: WDT STATUS

| Conditions                                              | WDT                          |

|---------------------------------------------------------|------------------------------|

| WDTE = 0                                                |                              |

| CLRWDT Command                                          | Cleared                      |

| Oscillator Fail Detected                                | Cleared                      |

| Exit Sleep + System Clock = T1OSC, EXTRC, INTRC, EXTCLK |                              |

| Exit Sleep + System Clock = XT, HS, LP                  | Cleared until the end of OST |

| DECFSZ           | Decrement f, Skip if 0                                                                                                                                                                                                                                                                                             |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] DECFSZ f,d                                                                                                                                                                                                                                                                                                 |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \end{array}$                                                                                                                                                                                                                                                    |

| Operation:       | (f) - 1 $\rightarrow$ (destination);<br>skip if result = 0                                                                                                                                                                                                                                                         |

| Status Affected: | None                                                                                                                                                                                                                                                                                                               |

| Description:     | The contents of register 'f' are decremented. If 'd' is '0', the result is placed in the W register. If 'd' is '1', the result is placed back in register 'f'.<br>If the result is '1', the next instruction is executed. If the result is '0', then a NOP is executed instead, making it a two-cycle instruction. |

| INCFSZ           | Increment f, Skip if 0                                                                                                                                                                                                                                                                                                                |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] INCFSZ f,d                                                                                                                                                                                                                                                                                                                    |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \end{array}$                                                                                                                                                                                                                                                                       |

| Operation:       | (f) + 1 $\rightarrow$ (destination),<br>skip if result = 0                                                                                                                                                                                                                                                                            |

| Status Affected: | None                                                                                                                                                                                                                                                                                                                                  |

| Description:     | The contents of register 'f' are<br>incremented. If 'd' is '0', the result<br>is placed in the W register. If 'd' is<br>'1', the result is placed back in<br>register 'f'.<br>If the result is '1', the next<br>instruction is executed. If the<br>result is '0', a NOP is executed<br>instead, making it a two-cycle<br>instruction. |

| GOTO             | Unconditional Branch                                                                                                                                                                             |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] GOTO k                                                                                                                                                                          |

| Operands:        | $0 \leq k \leq 2047$                                                                                                                                                                             |

| Operation:       | $k \rightarrow PC<10:0>$<br>PCLATH<4:3> $\rightarrow$ PC<12:11>                                                                                                                                  |

| Status Affected: | None                                                                                                                                                                                             |

| Description:     | GOTO is an unconditional branch.<br>The eleven-bit immediate value is<br>loaded into PC bits <10:0>. The<br>upper bits of PC are loaded from<br>PCLATH<4:3>. GOTO is a<br>two-cycle instruction. |

| IORLW            | Inclusive OR literal with W                                                                                               |

|------------------|---------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] IORLW k                                                                                                  |

| Operands:        | $0 \leq k \leq 255$                                                                                                       |

| Operation:       | (W) .OR. $k \rightarrow$ (W)                                                                                              |

| Status Affected: | Z                                                                                                                         |

| Description:     | The contents of the W register are<br>OR'ed with the eight-bit literal 'k'.<br>The result is placed in the<br>W register. |

| INCF             | Increment f                                                                                                                                                                |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] INCF f,d                                                                                                                                                           |

| Operands:        | $\begin{array}{l} 0\leq f\leq 127\\ d\in \left[0,1\right] \end{array}$                                                                                                     |

| Operation:       | (f) + 1 $\rightarrow$ (destination)                                                                                                                                        |

| Status Affected: | Z                                                                                                                                                                          |

| Description:     | The contents of register 'f' are<br>incremented. If 'd' is '0', the result<br>is placed in the W register. If 'd' is<br>'1', the result is placed back in<br>register 'f'. |

| IORWF            | Inclusive OR W with f                                                                                                                                                       |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ label ] IORWF f,d                                                                                                                                                         |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \end{array}$                                                                                                             |

| Operation:       | (W) .OR. (f) $\rightarrow$ (destination)                                                                                                                                    |

| Status Affected: | Z                                                                                                                                                                           |

| Description:     | Inclusive OR the W register with<br>register 'f'. If 'd' is '0', the result is<br>placed in the W register. If 'd' is<br>'1', the result is placed back in<br>register 'f'. |

#### 14.5 DC Characteristics: PIC16F688 -I (Industrial) PIC16F688 -E (Extended) (Continued)

| DC CH        | ARACTE | RISTICS                                                             | $\begin{array}{l} \mbox{Standard Operating Conditions (unless otherwise stated Operating temperature } & -40^\circ C \leq T A \leq +85^\circ C \mbox{ for industria} \\ & -40^\circ C \leq T A \leq +125^\circ C \mbox{ for extended} \end{array}$ |      |     |       | +85°C for industrial                                                                                |

|--------------|--------|---------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-----|-------|-----------------------------------------------------------------------------------------------------|

| Param<br>No. | Sym    | Characteristic                                                      | Min                                                                                                                                                                                                                                                | Тур† | Max | Units | Conditions                                                                                          |

| D100         | IULP   | Ultra Low-Power Wake-Up<br>Current                                  | _                                                                                                                                                                                                                                                  | 200  |     | nA    | See Application Note AN879,<br>"Using the Microchip Ultra<br>Low-Power Wake-up Module"<br>(DS00879) |

|              |        | Capacitive Loading Specs on<br>Output Pins                          |                                                                                                                                                                                                                                                    |      |     |       |                                                                                                     |

| D101*        | COSC2  | OSC2 pin                                                            | _                                                                                                                                                                                                                                                  | -    | 15  | pF    | In XT, HS and LP modes when<br>external clock is used to drive<br>OSC1                              |

| D101A*       | Сю     | All I/O pins                                                        | _                                                                                                                                                                                                                                                  | _    | 50  | pF    |                                                                                                     |

|              |        | Data EEPROM Memory                                                  |                                                                                                                                                                                                                                                    |      |     |       |                                                                                                     |

| D120         | ED     | Byte Endurance                                                      | 100K                                                                                                                                                                                                                                               | 1M   | _   | E/W   | $-40^{\circ}C \le TA \le +85^{\circ}C$                                                              |

| D120A        | ED     | Byte Endurance                                                      | 10K                                                                                                                                                                                                                                                | 100K | _   | E/W   | +85°C $\leq$ TA $\leq$ +125°C                                                                       |

| D121         | Vdrw   | VDD for Read/Write                                                  | VMIN                                                                                                                                                                                                                                               | -    | 5.5 | V     | Using EECON1 to read/write<br>VMIN = Minimum operating<br>voltage                                   |

| D122         | TDEW   | Erase/Write Cycle Time                                              | _                                                                                                                                                                                                                                                  | 5    | 6   | ms    |                                                                                                     |

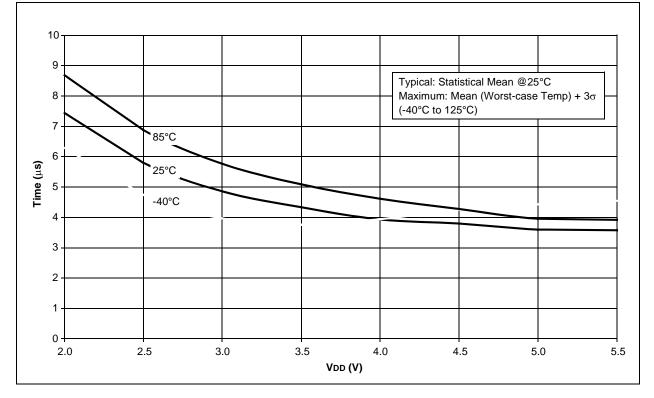

| D123         | Tretd  | Characteristic Retention                                            | 40                                                                                                                                                                                                                                                 | -    | —   | Year  | Provided no other specifications are violated                                                       |