Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 20MHz                                                                     |

| Connectivity               | UART/USART                                                                |

| Peripherals                | Brown-out Detect/Reset, POR, WDT                                          |

| Number of I/O              | 12                                                                        |

| Program Memory Size        | 7KB (4K x 14)                                                             |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 256 x 8                                                                   |

| RAM Size                   | 256 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                 |

| Data Converters            | A/D 8x10b                                                                 |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 14-SOIC (0.154", 3.90mm Width)                                            |

| Supplier Device Package    | 14-SOIC                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f688t-e-sl |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **Table of Contents**

| 1.0    | Device Overview                                               | 5    |

|--------|---------------------------------------------------------------|------|

| 2.0    | Memory Organization                                           | 7    |

| 3.0    | Clock Sources                                                 | . 21 |

| 4.0    | I/O Ports                                                     | . 33 |

| 5.0    | Timer0 Module                                                 |      |

| 6.0    | Timer1 Module with Gate Control                               | . 49 |

| 7.0    | Comparator Module                                             | . 55 |

| 8.0    | Analog-to-Digital Converter (A/D) Module                      | . 65 |

| 9.0    | Data EEPROM and Flash Program Memory Control                  |      |

| 10.0   | Enhanced Universal Asynchronous Receiver Transmitter (EUSART) | . 83 |

| 11.0   | Special Features of the CPU                                   | 109  |

| 12.0   | Instruction Set Summary                                       | 129  |

| 13.0   | Development Support                                           |      |

| 14.0   | Electrical Specifications                                     | 143  |

| 15.0   | DC and AC Characteristics Graphs and Tables                   | 163  |

| 16.0   | Packaging Information                                         | 185  |

| Appe   | ndix A: Data Sheet Revision History                           | 193  |

| Appe   | ndix B: Migrating from other PIC <sup>®</sup> Devices         | 193  |

|        |                                                               |      |

| On-lir | e Support                                                     | 199  |

|        | ms Information and Upgrade Hot Line                           |      |

|        | er Response                                                   |      |

|        |                                                               |      |

|        |                                                               |      |

# TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at **docerrors@microchip.com** or fax the **Reader Response Form** in the back of this data sheet to (480) 792-4150. We welcome your feedback.

### Most Current Data Sheet

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000A is version A of document DS30000).

#### Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

Microchip's Worldwide Web site; http://www.microchip.com

Your local Microchip sales office (see last page)

When contacting a sales office, please specify which device, revision of silicon and data sheet (include literature number) you are using.

### **Customer Notification System**

Register on our web site at www.microchip.com to receive the most current information on all of our products.

| Addr   | Name    | Bit 7         | Bit 6          | Bit 5          | Bit 4          | Bit 3            | Bit 2         | Bit 1         | Bit 0               | Value on<br>POR/BOR | Page     |

|--------|---------|---------------|----------------|----------------|----------------|------------------|---------------|---------------|---------------------|---------------------|----------|

| Bank 0 |         |               |                |                |                |                  |               |               |                     |                     |          |

| 00h    | INDF    | Addressing    | g this locatio | on uses conte  | ents of FSR t  | o address da     | ta memory (   | not a physica | al register)        | xxxx xxxx           | 20, 117  |

| 01h    | TMR0    | Timer0 Mo     | dule's regis   | ter            |                |                  |               |               |                     | xxxx xxxx           | 45, 117  |

| 02h    | PCL     | Program C     | Counter's (P   | C) Least Sigi  | nificant Byte  |                  |               |               |                     | 0000 0000           | 19, 117  |

| 03h    | STATUS  | IRP           | RP1            | RP0            | TO             | PD               | Z             | DC            | С                   | 0001 1xxx           | 13, 117  |

| 04h    | FSR     | Indirect Da   | ata Memory     | Address Poir   | nter           |                  |               |               |                     | xxxx xxxx           | 20, 117  |

| 05h    | PORTA   | -             | —              | RA5            | RA4            | RA3              | RA2           | RA1           | RA0                 | x0 x000             | 33, 117  |

| 06h    | _       | Unimpleme     | ented          |                |                |                  |               |               |                     | —                   | _        |

| 07h    | PORTC   | _             | _              | RC5            | RC4            | RC3              | RC2           | RC1           | RC0                 | xx 0000             | 42, 117  |

| 08h    | _       | Unimpleme     | ented          |                |                |                  |               |               |                     | —                   | _        |

| 09h    | _       | Unimpleme     | ented          |                |                |                  |               |               |                     | —                   | _        |

| 0Ah    | PCLATH  | _             | _              | _              | Write Buffer   | for upper 5 l    | oits of Progr | am Counter    |                     | 0 0000              | 19, 117  |

| 0Bh    | INTCON  | GIE           | PEIE           | TOIE           | INTE           | RAIE             | T0IF          | INTF          | RAIF <sup>(2)</sup> | 0000 000x           | 15, 117  |

| 0Ch    | PIR1    | EEIF          | ADIF           | RCIF           | C2IF           | C1IF             | OSFIF         | TXIF          | TMR1IF              | 0000 0000 17, 11    |          |

| 0Dh    | _       | Unimplemented |                |                |                |                  |               |               |                     | —                   | _        |

| 0Eh    | TMR1L   | Holding Re    | egister for th | e Least Sign   | ificant Byte o | of the 16-bit T  | MR1           |               |                     | xxxx xxxx           | 48, 117  |

| 0Fh    | TMR1H   | Holding Re    | egister for th | e Most Signi   | ificant Byte o | f the 16-bit TI  | MR1           |               |                     | xxxx xxxx           | 48, 117  |

| 10h    | T1CON   | T1GINV        | TMR1GE         | T1CKPS1        | T1CKPS0        | T1OSCEN          | T1SYNC        | TMR1CS        | TMR10N              | 0000 0000           | 51, 117  |

| 11h    | BAUDCTL | ABDOVF        | RCIDL          | _              | SCKP           | BRG16            | _             | WUE           | ABDEN               | 01-0 0-00           | 94, 117  |

| 12h    | SPBRGH  | USART Ba      | aud Rate Hig   | gh Generator   | r              |                  |               |               |                     | 0000 0000           | 95, 117  |

| 13h    | SPBRG   | USART Ba      | aud Rate Ge    | nerator        |                |                  |               |               |                     | 0000 0000           | 95, 117  |

| 14h    | RCREG   | USART Re      | eceive Regis   | ster           |                |                  |               |               |                     | 0000 0000           | 87, 117  |

| 15h    | TXREG   | USART Tra     | ansmit Regi    | ster           |                |                  |               |               |                     | 0000 0000           | 87, 117  |

| 16h    | TXSTA   | CSRC          | TX9            | TXEN           | SYNC           | SENDB            | BRGH          | TRMT          | TX9D                | 0000 0010           | 92, 117  |

| 17h    | RCSTA   | SPEN          | RX9            | SREN           | CREN           | ADDEN            | FERR          | OERR          | RX9D                | 0000 000x           | 93, 117  |

| 18h    | WDTCON  | _             | _              | _              | WDTPS3         | WDTPS2           | WDTPS1        | WDTPS0        | SWDTEN              | 0 1000              | 124, 117 |

| 19h    | CMCON0  | C2OUT         | C1OUT          | C2INV          | C1INV          | CIS              | CM2           | CM1           | CM0                 | 0000 0000           | 61, 117  |

| 1Ah    | CMCON1  | _             | _              | _              | _              | _                | _             | T1GSS         | C2SYNC              | 10                  | 62, 117  |

| 1Bh    | _       | Unimpleme     | ented          |                |                |                  |               |               |                     | —                   | _        |

| 1Ch    | _       | Unimpleme     | ented          |                |                |                  |               |               |                     | —                   | _        |

| 1Dh    | —       | Unimpleme     | ented          |                |                |                  |               |               |                     | —                   | _        |

| 1Eh    | ADRESH  | Most Signi    | ficant 8 bits  | of the left sh | ifted A/D res  | ult or 2 bits of | right shifted | d result      |                     | xxxx xxxx           | 72, 117  |

| 1Fh    | ADCON0  | ADFM          | VCFG           | —              | CHS2           | CHS1             | CHS0          | GO/DONE       | ADON                | 00-0 0000           | 71, 117  |

TABLE 2-1. PIC16F688 SPECIAL REGISTERS SUMMARY BANK 0

Legend: - = Unimplemented locations read as  $\frac{0'}{0}$ , u = unchanged, x = unknown, q = value depends on condition, shaded = unimplemented Note

1:

Other (non Power-up) Resets include MCLR Reset and Watchdog Timer Reset during normal operation. MCLR and WDT Reset does not affect the previous value data latch. The RAIF bit will be cleared upon Reset but will set again if the 2: mismatched exists.

# 3.2 Oscillator Control

The Oscillator Control (OSCCON) register (Figure 3-1) controls the system clock and frequency selection options. The OSCCON register contains the following bits:

- Frequency selection bits (IRCF)

- Frequency Status bits (HTS, LTS)

- System clock control bits (OSTS, SCS)

# REGISTER 3-1: OSCCON: OSCILLATOR CONTROL REGISTER

| U-0   | R/W-1 | R/W-1 | R/W-0 | R-1                 | R-0 | R-0        | R/W-0 |

|-------|-------|-------|-------|---------------------|-----|------------|-------|

| —     | IRCF2 | IRCF1 | IRCF0 | OSTS <sup>(1)</sup> | HTS | HTS LTS SO |       |

| bit 7 |       |       |       |                     |     |            | bit 0 |

|       |       |       |       |                     |     |            |       |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

| bit 7   | Unimplemented: Read as '0'                                                                                                                                                                                |

|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 6-4 | IRCF<2:0>: Internal Oscillator Frequency Select bits                                                                                                                                                      |

|         | 111 = 8 MHz                                                                                                                                                                                               |

|         | 110 = 4 MHz (default)                                                                                                                                                                                     |

|         | 101 = 2 MHz                                                                                                                                                                                               |

|         | 100 = 1  MHz                                                                                                                                                                                              |

|         | 011 = 500  kHz                                                                                                                                                                                            |

|         | 010 = 250  kHz                                                                                                                                                                                            |

|         | 001 = 125  kHz                                                                                                                                                                                            |

|         | 000 = 31  kHz (LFINTOSC)                                                                                                                                                                                  |

| bit 3   | <b>OSTS:</b> Oscillator Start-up Time-out Status bit <sup>(1)</sup>                                                                                                                                       |

|         | <ul> <li>1 = Device is running from the external clock defined by FOSC&lt;2:0&gt; of the Configuration Word</li> <li>0 = Device is running from the internal oscillator (HFINTOSC or LFINTOSC)</li> </ul> |

| bit 2   | HTS: HFINTOSC Status bit (High Frequency – 8 MHz to 125 kHz)                                                                                                                                              |

|         | 1 = HFINTOSC is stable                                                                                                                                                                                    |

|         | 0 = HFINTOSC is not stable                                                                                                                                                                                |

| bit 1   | LTS: LFINTOSC Stable bit (Low Frequency – 31 kHz)                                                                                                                                                         |

|         | 1 = LFINTOSC is stable                                                                                                                                                                                    |

|         | 0 = LFINTOSC is not stable                                                                                                                                                                                |

| bit 0   | SCS: System Clock Select bit                                                                                                                                                                              |

|         | 1 = Internal oscillator is used for system clock                                                                                                                                                          |

|         | 0 = Clock source defined by FOSC<2:0> of the Configuration Word                                                                                                                                           |

| Note 4. | Bit resets to '0' with Two-Speed Start-up and LP, XT or HS selected as the Oscillator mode or Eail-Safe                                                                                                   |

**Note 1:** Bit resets to '0' with Two-Speed Start-up and LP, XT or HS selected as the Oscillator mode or Fail-Safe mode is enabled.

# 3.6 Clock Switching

The system clock source can be switched between external and internal clock sources via software using the System Clock Select (SCS) bit of the OSCCON register.

# 3.6.1 SYSTEM CLOCK SELECT (SCS) BIT

The System Clock Select (SCS) bit of the OSCCON register selects the system clock source that is used for the CPU and peripherals.

- When the SCS bit of the OSCCON register = 0, the system clock source is determined by configuration of the FOSC<2:0> bits in the Configuration Word register (CONFIG).

- When the SCS bit of the OSCCON register = 1, the system clock source is chosen by the internal oscillator frequency selected by the IRCF<2:0> bits of the OSCCON register. After a Reset, the SCS bit of the OSCCON register is always cleared.

- Note: Any automatic clock switch, which may occur from Two-Speed Start-up or Fail-Safe Clock Monitor, does not update the SCS bit of the OSCCON register. The user can monitor the OSTS bit of the OSCCON register to determine the current system clock source.

# 3.6.2 OSCILLATOR START-UP TIME-OUT STATUS (OSTS) BIT

The Oscillator Start-up Time-out Status (OSTS) bit of the OSCCON register indicates whether the system clock is running from the external clock source, as defined by the FOSC<2:0> bits in the Configuration Word register (CONFIG), or from the internal clock source. In particular, OSTS indicates that the Oscillator Start-up Timer (OST) has timed out for LP, XT or HS modes.

# 3.7 Two-Speed Clock Start-up Mode

Two-Speed Start-up mode provides additional power savings by minimizing the latency between external oscillator start-up and code execution. In applications that make heavy use of the Sleep mode, Two-Speed Start-up will remove the external oscillator start-up time from the time spent awake and can reduce the overall power consumption of the device.

This mode allows the application to wake-up from Sleep, perform a few instructions using the INTOSC as the clock source and go back to Sleep without waiting for the primary oscillator to become stable.

| Note: | Executing a SLEEP instruction will abort    |

|-------|---------------------------------------------|

|       | the oscillator start-up time and will cause |

|       | the OSTS bit of the OSCCON register to      |

|       | remain clear.                               |

When the oscillator module is configured for LP, XT or HS modes, the Oscillator Start-up Timer (OST) is enabled (see **Section 3.4.1 "Oscillator Start-up Timer (OST)"**). The OST will suspend program execution until 1024 oscillations are counted. Two-Speed Start-up mode minimizes the delay in code execution by operating from the internal oscillator as the OST is counting. When the OST count reaches 1024 and the OSTS bit of the OSCCON register is set, program execution switches to the external oscillator.

# 3.7.1 TWO-SPEED START-UP MODE CONFIGURATION

Two-Speed Start-up mode is configured by the following settings:

- IESO (of the Configuration Word register) = 1; Internal/External Switchover bit (Two-Speed Startup mode enabled).

- SCS (of the OSCCON register) = 0.

- FOSC<2:0> bits in the Configuration Word register (CONFIG) configured for LP, XT or HS mode.

Two-Speed Start-up mode is entered after:

- Power-on Reset (POR) and, if enabled, after Power-up Timer (PWRT) has expired, or

- Wake-up from Sleep.

If the external clock oscillator is configured to be anything other than LP, XT or HS mode, then Two-Speed Start-up is disabled. This is because the external clock oscillator does not require any stabilization time after POR or an exit from Sleep.

# 3.7.2 TWO-SPEED START-UP SEQUENCE

- 1. Wake-up from Power-on Reset or Sleep.

- Instructions begin execution by the internal oscillator at the frequency set in the IRCF<2:0> bits of the OSCCON register.

- 3. OST enabled to count 1024 clock cycles.

- 4. OST timed out, wait for falling edge of the internal oscillator.

- 5. OSTS is set.

- 6. System clock held low until the next falling edge of new clock (LP, XT or HS mode).

- 7. System clock is switched to external clock source.

# 6.0 TIMER1 MODULE WITH GATE CONTROL

The Timer1 module is a 16-bit timer/counter with the following features:

- 16-bit timer/counter register pair (TMR1H:TMR1L)

- · Programmable internal or external clock source

- 3-bit prescaler

- Optional LP oscillator

- Synchronous or asynchronous operation

- Timer1 gate (count enable) via comparator or  $$\overline{\text{T1G}}$ pin$

- Interrupt on overflow

- Wake-up on overflow (external clock, Asynchronous mode only)

Figure 6-1 is a block diagram of the Timer1 module.

# 6.1 Timer1 Operation

The Timer1 module is a 16-bit incrementing counter which is accessed through the TMR1H:TMR1L register pair. Writes to TMR1H or TMR1L directly update the counter.

When used with an internal clock source, the module is a timer. When used with an external clock source, the module can be used as either a timer or counter.

# 6.2 Clock Source Selection

The TMR1CS bit of the T1CON register is used to select the clock source. When TMR1CS = 0, the clock source is FOSC/4. When TMR1CS = 1, the clock source is supplied externally.

| Clock Source | TMR1CS | Clock Source |

|--------------|--------|--------------|

| Fosc/4       | 0      | Fosc/4       |

| T1CKI pin    | 1      | T1CKI pin    |

#### TMR1GE T1GINV TMR1ON Set flag bit TMR1IF on To C2 Comparator Module Overflow Timer1 Clock TMR1(2) Synchronized 0 ΕN clock input TMR1H TMR1L Oscillator (1) T1SYNC OSC1/T1CKI 1 Synchronize<sup>(3)</sup> Prescaler Fosc/4 1.2.4.8 det 0 Internal Clock 1∕2 OSC2/T1G X T1CKPS<1:0> TMR1CS 1 INTOSC Without CLKOUT C2OUT 0 T1OSCEN T1GSS Note 1: ST Buffer is low power type when using LP oscillator, or high speed type when using T1CKI. Timer1 register increments on rising edge. 2: 3: Synchronize does not operate while in Sleep.

# FIGURE 6-1: TIMER1 BLOCK DIAGRAM

# 7.1.1 ANALOG INPUT CONNECTION CONSIDERATIONS

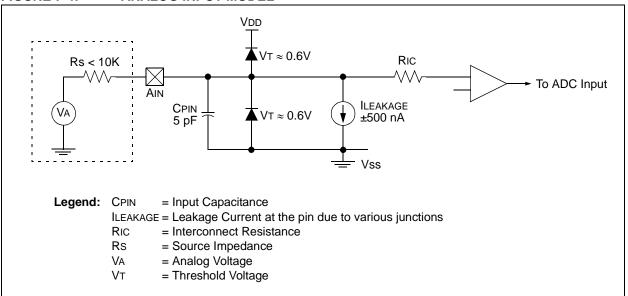

A simplified circuit for an analog input is shown in Figure 7-4. Since the analog input pins share their connection with a digital input, they have reverse biased ESD protection diodes to VDD and Vss. The analog input, therefore, must be between Vss and VDD. If the input voltage deviates from this range by more than 0.6V in either direction, one of the diodes is forward biased and a latch-up may occur.

A maximum source impedance of  $10 \text{ k}\Omega$  is recommended for the analog sources. Also, any external component connected to an analog input pin, such as a capacitor or a Zener diode, should have very little leakage current to minimize inaccuracies introduced.

- Note 1: When reading a PORT register, all pins configured as analog inputs will read as a '0'. Pins configured as digital inputs will convert as an analog input, according to the input specification.

- 2: Analog levels on any pin defined as a digital input, may cause the input buffer to consume more current than is specified.

### FIGURE 7-4: ANALOG INPUT MODEL

# PIC16F688

# EXAMPLE 8-1: A/D CONVERSION

```

;This code block configures the ADC

; for polling, Vdd reference, Frc clock

;and AN0 input.

;

;Conversion start & polling for completion

; are included.

;

BANKSEL ADCON1

;

MOVLW B'01110000' ;ADC Frc clock

MOVWF ADCON1

;

BANKSEL TRISA

;

BSF TRISA,0 ;Set RA0 to input

BANKSEL ANSEL ;

BSF ANSEL,0 ;Set RA0 to analog

BANKSEL ADCON0

;

MOVLW B'10000001' ;Right justify,

MOVWF ADCON0 ;Vdd Vref, ANO,

;Vdd Vref, AN0, On

CALL SampleTime ;Acquisiton delay

BSF ADCON0,GO ;Start conversion

BTFSC ADCON0,GO ;Is conversion done?

;No, test again

GOTO $-1

BANKSEL ADRESH

;

MOVF ADRESH,W ;Read upper 2 bits

MOVWF RESULTHI ;store in GPR space

BANKSEL ADRESL ;

MOVF ADRESL,W ;Read lower 8 bits

MOVWF RESULTLO ;Store in GPR space

```

# **PIC16F688**

#### **TABLE 9-1:** SUMMARY OF REGISTERS ASSOCIATED WITH DATA EEPROM

| Name   | Bit 7    | Bit 6        | Bit 5           | Bit 4         | Bit 3   | Bit 2   | Bit 1   | Bit 0   | Value on<br>POR, BOR | Value on<br>all other<br>Resets |

|--------|----------|--------------|-----------------|---------------|---------|---------|---------|---------|----------------------|---------------------------------|

| EECON1 | EEPGD    | —            |                 |               | WRERR   | WREN    | WR      | RD      | x x000               | 0 q000                          |

| EECON2 | EEPROM C | ontrol Regis | ster 2 (not a p | hysical regis | ter)    |         |         |         |                      |                                 |

| EEADR  | EEADR7   | EEADR6       | EEADR5          | EEADR4        | EEADR3  | EEADR2  | EEADR1  | EEADR0  | 0000 0000            | 0000 0000                       |

| EEADRH | _        | _            |                 |               | EEADRH3 | EEADRH2 | EEADRH1 | EEADRH0 | 0000                 | 0000                            |

| EEDAT  | EEDAT7   | EEDAT6       | EEDAT5          | EEDAT4        | EEDAT3  | EEDAT2  | EEDAT1  | EEDAT0  | 0000 0000            | 0000 0000                       |

| EEDATH | _        | _            | EEDATH5         | EEDATH4       | EEDATH3 | EEDATH2 | EEDATH1 | EEDATH0 | 00 0000              | 00 0000                         |

| INTCON | GIE      | PEIE         | TOIE            | INTE          | RABIE   | T0IF    | INTF    | RABIF   | 0000 000x            | 0000 000x                       |

| PIE1   | EEIE     | ADIE         | RCIE            | C2IE          | C1IE    | OSFIE   | TXIE    | TMR1IE  | 0000 0000            | 0000 0000                       |

| PIR1   | EEIF     | ADIF         | RCIF            | C2IF          | C1IF    | OSFIF   | TXIF    | TMR1IF  | 0000 0000            | 0000 0000                       |

Legend: x = unknown, u = unchanged, - = unimplemented read as '0', q = value depends upon condition. Shaded cells are not used by data EEPROM module.

|        |                |            |                             | SYNC = 0          | BRGH       | = 1, BRG16                  | = 1 or SY      | /NC = 1,   | BRG16 = 1                   |                |            |                             |

|--------|----------------|------------|-----------------------------|-------------------|------------|-----------------------------|----------------|------------|-----------------------------|----------------|------------|-----------------------------|

| BAUD   | Fosc           | = 20.00    | 0 MHz                       | Fosc = 18.432 MHz |            |                             | Fosc           | = 11.059   | 92 MHz                      | Fos            | c = 8.000  | ) MHz                       |

| RATE   | Actual<br>Rate | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate    | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate | %<br>Error | SPBRG<br>value<br>(decimal) |

| 300    | 300.0          | 0.00       | 16665                       | 300.0             | 0.00       | 15359                       | 300.0          | 0.00       | 9215                        | 300.0          | 0.00       | 6666                        |

| 1200   | 1200           | -0.01      | 4166                        | 1200              | 0.00       | 3839                        | 1200           | 0.00       | 2303                        | 1200           | -0.02      | 1666                        |

| 2400   | 2400           | 0.02       | 2082                        | 2400              | 0.00       | 1919                        | 2400           | 0.00       | 1151                        | 2401           | 0.04       | 832                         |

| 9600   | 9597           | -0.03      | 520                         | 9600              | 0.00       | 479                         | 9600           | 0.00       | 287                         | 9615           | 0.16       | 207                         |

| 10417  | 10417          | 0.00       | 479                         | 10425             | 0.08       | 441                         | 10433          | 0.16       | 264                         | 10417          | 0          | 191                         |

| 19.2k  | 19.23k         | 0.16       | 259                         | 19.20k            | 0.00       | 239                         | 19.20k         | 0.00       | 143                         | 19.23k         | 0.16       | 103                         |

| 57.6k  | 57.47k         | -0.22      | 86                          | 57.60k            | 0.00       | 79                          | 57.60k         | 0.00       | 47                          | 57.14k         | -0.79      | 34                          |

| 115.2k | 116.3k         | 0.94       | 42                          | 115.2k            | 0.00       | 39                          | 115.2k         | 0.00       | 23                          | 117.6k         | 2.12       | 16                          |

# TABLE 10-5: BAUD RATES FOR ASYNCHRONOUS MODES (CONTINUED)

|        |                |            |                             | SYNC = 0          | , BRGH     | = 1, BRG16                  | = 1 or SΥ      | ′NC = 1,   | BRG16 = 1                   |                |            |                             |

|--------|----------------|------------|-----------------------------|-------------------|------------|-----------------------------|----------------|------------|-----------------------------|----------------|------------|-----------------------------|

| BAUD   | Fos            | c = 4.000  | ) MHz                       | Fosc = 3.6864 MHz |            |                             | Fos            | c = 2.000  | ) MHz                       | Fos            | c = 1.000  | ) MHz                       |

| RATE   | Actual<br>Rate | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate    | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate | %<br>Error | SPBRG<br>value<br>(decimal) |

| 300    | 300.0          | 0.01       | 3332                        | 300.0             | 0.00       | 3071                        | 299.9          | -0.02      | 1666                        | 300.1          | 0.04       | 832                         |

| 1200   | 1200           | 0.04       | 832                         | 1200              | 0.00       | 767                         | 1199           | -0.08      | 416                         | 1202           | 0.16       | 207                         |

| 2400   | 2398           | 0.08       | 416                         | 2400              | 0.00       | 383                         | 2404           | 0.16       | 207                         | 2404           | 0.16       | 103                         |

| 9600   | 9615           | 0.16       | 103                         | 9600              | 0.00       | 95                          | 9615           | 0.16       | 51                          | 9615           | 0.16       | 25                          |

| 10417  | 10417          | 0.00       | 95                          | 10473             | 0.53       | 87                          | 10417          | 0.00       | 47                          | 10417          | 0.00       | 23                          |

| 19.2k  | 19.23k         | 0.16       | 51                          | 19.20k            | 0.00       | 47                          | 19.23k         | 0.16       | 25                          | 19.23k         | 0.16       | 12                          |

| 57.6k  | 58.82k         | 2.12       | 16                          | 57.60k            | 0.00       | 15                          | 55.56k         | -3.55      | 8                           | —              | —          | _                           |

| 115.2k | 111.1k         | -3.55      | 8                           | 115.2k            | 0.00       | 7                           | _              | _          | —                           | _              | _          | —                           |

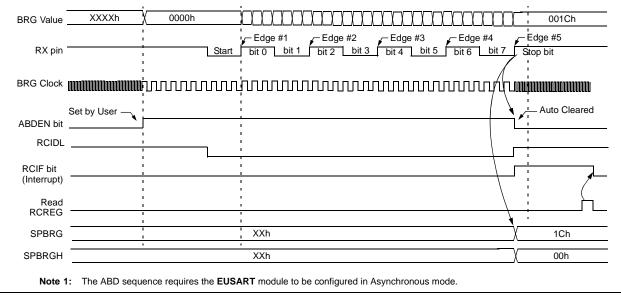

# 10.3.1 AUTO-BAUD DETECT

The EUSART module supports automatic detection and calibration of the baud rate.

In the Auto-Baud Detect (ABD) mode, the clock to the BRG is reversed. Rather than the BRG clocking the incoming RX signal, the RX signal is timing the BRG. The Baud Rate Generator is used to time the period of a received 55h (ASCII "U") which is the Sync character for the LIN bus. The unique feature of this character is that it has five rising edges including the Stop bit edge.

Setting the ABDEN bit of the BAUDCTL register starts the auto-boot sequence (Figure 10-6). While the ABD sequence takes place, the EUSART state machine is held in Idle. On the first rising edge of the receive line, after the Start bit, the SPBRG begins counting up using the BRG counter clock as shown in Table 10-6. The fifth rising edge will occur on the RX pin at the end of the eighth bit period. At that time, an accumulated value totaling the proper BRG period is left in SPBRGH, SPBRG register pair, the ABDEN bit is automatically cleared and the RCIF interrupt flag is set. The value in the RCREG needs to be read to clear the RCIF interrupt. RCREG content should be discarded. When calibrating for modes that do not use the SPBRGH register the user can verify that the SPBRG register did not overflow by checking for 00h in the SPBRGH register.

The BRG auto-baud clock is determined by the BRG16 and BRGH bits as shown in Table 10-6. During ABD, both the SPBRGH and SPBRG registers are used as a 16-bit counter, independent of the BRG16 bit setting. While calibrating the baud rate period, the SPBRGH and SPBRG registers are clocked at 1/8th the BRG base clock rate. The resulting byte measurement is the average bit time when clocked at full speed.

- Note 1: If the WUE bit is set with the ABDEN bit, auto-baud detection will occur on the byte following the Break character (see Section 10.3.3 "Auto-Wake-up on Break").

- 2: It is up to the user to determine that the incoming character baud rate is within the range of the selected BRG clock source. Some combinations of oscillator frequency and EUSART baud rates are not possible due to bit error rates. Overall system timing and communication baud rates must be taken into consideration when using the Auto-Baud Detect feature.

- 3: During the auto-baud process, the autobaud counter starts counting at 1. Upon completion of the auto-baud sequence, to achieve maximum accuracy, subtract 1 from the SPBRGH:SPBRG register pair.

| TABLE 10-6: BRG COUNTER CLOCK RATE |

|------------------------------------|

|------------------------------------|

| BRG16 | BRGH | BRG Base<br>Clock | BRG ABD<br>Clock |

|-------|------|-------------------|------------------|

| 0     | 0    | Fosc/64           | Fosc/512         |

| 0     | 1    | Fosc/16           | Fosc/128         |

| 1     | 0    | Fosc/16           | Fosc/128         |

| 1     | 1    | Fosc/4            | Fosc/32          |

**Note:** During the ABD sequence, SPBRG and SPBRGH registers are both used as a 16-bit counter, independent of BRG16 setting.

# FIGURE 10-6: AUTOMATIC BAUD RATE CALCULATION

# 11.0 SPECIAL FEATURES OF THE CPU

The PIC16F688 has a host of features intended to maximize system reliability, minimize cost through elimination of external components, provide power-saving features and offer code protection.

These features are:

- Reset

- Power-on Reset (POR)

- Power-up Timer (PWRT)

- Oscillator Start-up Timer (OST)

- Brown-out Reset (BOR)

- Interrupts

- Watchdog Timer (WDT)

- Oscillator Selection

- Sleep

- Code Protection

- ID Locations

- In-Circuit Serial Programming™

The PIC16F688 has two timers that offer necessary delays on power-up. One is the Oscillator Start-up Timer (OST), intended to keep the chip in Reset until the crystal oscillator is stable. The other is the Power-up Timer (PWRT), which provides a fixed delay of 64 ms (nominal) on power-up only, designed to keep the part in Reset while the power supply stabilizes. There is also circuitry to reset the device if a brown-out occurs, which can use the Power-up Timer to provide at least a 64 ms Reset. With these three functions-on-chip, most applications need no external Reset circuitry.

The Sleep mode is designed to offer a very low-current Power-Down mode. The user can wake-up from Sleep through:

- External Reset

- Watchdog Timer Wake-up

- An interrupt

Several oscillator options are also made available to allow the part to fit the application. The INTOSC option saves system cost while the LP crystal option saves power. A set of Configuration bits are used to select various options (see Register 11-1).

# 11.6 Power-Down Mode (Sleep)

The Power-down mode is entered by executing a SLEEP instruction.

If the Watchdog Timer is enabled:

- WDT will be cleared but keeps running.

- PD bit in the Status register is cleared.

- TO bit is set.

- Oscillator driver is turned off.

- I/O ports maintain the status they had before SLEEP was executed (driving high, low or high-impedance).

For lowest current consumption in this mode, all I/O pins should be either at VDD or VSS, with no external circuitry drawing current from the I/O pin, and the comparators and CVREF should be disabled. I/O pins that are high-impedance inputs should be pulled high or low externally to avoid switching currents caused by floating inputs. The TOCKI input should also be at VDD or VSs for lowest current consumption. The contribution from on-chip pull-ups on PORTA should be considered.

The  $\overline{\text{MCLR}}$  pin must be at a logic high level.

Note: It should be noted that a Reset generated by a WDT time-out does not drive MCLR pin low.

# 11.6.1 WAKE-UP FROM SLEEP

The device can wake-up from Sleep through one of the following events:

- 1. External Reset input on  $\overline{\text{MCLR}}$  pin.

- 2. Watchdog Timer wake-up (if WDT was enabled).

- 3. Interrupt from RA2/INT pin, PORTA change or a peripheral interrupt.

The first event will cause a device Reset. The two latter events are considered <u>a</u> continuation of program execution. The TO and PD bits in the Status register can <u>be</u> used to determine the cause of device Reset. The PD bit, which is set on power-up, is cleared when Sleep is invoked. TO bit is cleared if WDT wake-up occurred.

The following peripheral interrupts can wake the device from Sleep:

- 1. Timer1 interrupt. Timer1 must be operating as an asynchronous counter.

- 2. A/D conversion (when A/D clock source is FRC).

- 3. EEPROM write operation completion.

- 4. Comparator output changes state.

- 5. Interrupt-on-change.

- 6. External Interrupt from INT pin.

- 7. EUSART Receive Interrupt.

- 8. ULPWU Interrupt.

Other peripherals cannot generate interrupts since during Sleep, no on-chip clocks are present.

When the SLEEP instruction is being executed, the next instruction (PC + 1) is prefetched. For the device to wake-up through an interrupt event, the corresponding interrupt enable bit must be set (enabled). Wake-up is regardless of the state of the GIE bit. If the GIE bit is clear (disabled), the device continues execution at the instruction after the SLEEP instruction. If the GIE bit is set (enabled), the device executes the instruction after the SLEEP instruction, then branches to the interrupt address (0004h). In cases where the execution of the instruction following SLEEP is not desirable, the user should have a NOP after the SLEEP instruction.

**Note:** If the global interrupts are disabled (GIE is cleared), but any interrupt source has both its interrupt enable bit and the corresponding interrupt flag bits set, the device will immediately wake-up from Sleep. The SLEEP instruction is completely executed.

The WDT is cleared when the device wakes up from Sleep, regardless of the source of wake-up.

# 11.6.2 WAKE-UP USING INTERRUPTS

When global interrupts are disabled (GIE cleared) and any interrupt source has both its interrupt enable bit and interrupt flag bit set, one of the following will occur:

- If the interrupt occurs **before** the execution of a SLEEP instruction, the SLEEP instruction will complete as a NOP. Therefore, the WDT and WDT prescaler and postscaler (if enabled) will not be cleared, the TO bit will not be set and the PD bit will not be cleared.

- If the interrupt occurs **during or after** the execution of a SLEEP instruction, the device will immediately wake-up from Sleep. The SLEEP instruction will be completely executed before the wake-up. Therefore, the WDT and WDT prescaler and postscaler (if enabled) will be cleared, the TO bit will be set and the PD bit will be cleared.

Even if the flag bits were checked before executing a SLEEP instruction, it may be possible for flag bits to become set before the SLEEP instruction completes. To determine whether a SLEEP instruction executed, test the PD bit. If the PD bit is set, the SLEEP instruction was executed as a NOP.

To ensure that the WDT is cleared, a CLRWDT instruction should be executed before a SLEEP instruction.

## FIGURE 11-10: WAKE-UP FROM SLEEP THROUGH INTERRUPT

|                             | Q1 Q2 Q3 Q4                                 | Q1 Q2 Q3  Q4 | Q1             |                     | Q1 Q2 Q3 Q4        | Q1 Q2 Q3 Q4                           | Q1 Q2 Q3 Q4 | Q1 Q2 Q3 Q4                                |

|-----------------------------|---------------------------------------------|--------------|----------------|---------------------|--------------------|---------------------------------------|-------------|--------------------------------------------|

| OSC1                        |                                             |              |                |                     |                    |                                       |             |                                            |

| CLKOUT <sup>(4)</sup>       | <u>`</u>                                    |              |                | Tost <sup>(2)</sup> | ·                  | \/                                    | \           |                                            |

| INT pin                     | <u> </u>                                    |              |                | ı                   | 1                  | ı 1                                   | 1           |                                            |

| INTF flag<br>(INTCON<1>)    |                                             |              | <u> </u>       | ।<br>।<br>≉         | Interrupt Laten    | су <sup>(3)</sup>                     |             |                                            |

| GIE bit<br>(INTCON<7>)      |                                             |              | Processor i    | ሱ                   | 1                  |                                       |             |                                            |

|                             |                                             |              | Sleep          | ;                   |                    | ¦                                     | ¦           | ¦-                                         |

| Instruction Flow            | , , , , , , , , , , , , , , , , , , ,       |              |                |                     | \                  | , , , , , , , , , , , , , , , , , , , |             | ،<br>لــــــــــــــــــــــــــــــــــــ |

| PC )                        | ( <u>PC</u> X                               | PC + 1       | <u>х РС</u>    | + 2                 | X PC + 2           | X <u>PC+2</u> X                       | <u> </u>    | 0005h                                      |

| Instruction [<br>Fetched    | Inst(PC) = Sleep                            | Inst(PC + 1) | <br>           |                     | Inst(PC + 2)       | · · · · · · · · · · · · · · · · · · · | Inst(0004h) | Inst(0005h)                                |

| Instruction {<br>Executed { | Inst(PC - 1)                                | Sleep        |                |                     | Inst(PC + 1)       | Dummy Cycle                           | Dummy Cycle | Inst(0004h)                                |

|                             | (T, HS or LP Oscilla<br>fost = 1024 Tosc (d |              | ale). This del | ay does i           | not apply to EC an | d RC Oscillator mo                    | des.        |                                            |

3: GIE = 1 assumed. In this case after wake-up, the processor jumps to 0004h. If GIE = 0, execution will continue in-line.

4: CLKOUT is not available in XT, HS, LP or EC Oscillator modes, but shown here for timing reference.

# 11.7 Code Protection

If the code protection bit(s) have not been programmed, the on-chip program memory can be read out using ICSP for verification purposes.

| Note: | The entire data EEPROM and Flash       |

|-------|----------------------------------------|

|       | program memory will be erased when the |

|       | code protection is turned off. See the |

|       | "PIC12F6XX/16F6XX Memory Program-      |

|       | ming Specification" (DS41204) for more |

|       | information.                           |

# 11.8 ID Locations

Four memory locations (2000h-2003h) are designated as ID locations where the user can store checksum or other code identification numbers. These locations are not accessible during normal execution but are readable and writable during Program/Verify mode. Only the Least Significant 7 bits of the ID locations are used.

# **PIC16F688**

NOTES:

# TABLE 14-9: PIC16F688 A/D CONVERSION REQUIREMENTS

| Standard Operating Conditions (unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +125^{\circ}C$ |      |                                                                       |     |              |     |       |                                                                                                                                                  |  |

|----------------------------------------------------------------------------------------------------------------------|------|-----------------------------------------------------------------------|-----|--------------|-----|-------|--------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Param<br>No.                                                                                                         | Sym  | Characteristic                                                        | Min | Тур†         | Max | Units | Conditions                                                                                                                                       |  |

| AD130*                                                                                                               | TAD  | A/D Clock Period                                                      | 1.6 |              | 9.0 | μS    | Tosc-based, VREF $\geq$ 3.0V                                                                                                                     |  |

|                                                                                                                      |      |                                                                       | 3.0 | —            | 9.0 | μS    | Tosc-based, VREF full range                                                                                                                      |  |

|                                                                                                                      |      | A/D Internal RC<br>Oscillator Period                                  | 3.0 | 6.0          | 9.0 | μS    | ADCS<1:0> = 11 (ADRC mode)<br>At VDD = 2.5V                                                                                                      |  |

|                                                                                                                      |      |                                                                       | 1.6 | 4.0          | 6.0 | μS    | At VDD = 5.0V                                                                                                                                    |  |

| AD131                                                                                                                | TCNV | Conversion Time<br>(not including<br>Acquisition Time) <sup>(1)</sup> | _   | 11           |     | TAD   | Set GO/DONE bit to new data in A/D<br>Result register                                                                                            |  |

| AD132*                                                                                                               | TACQ | Acquisition Time                                                      |     | 11.5         |     | μs    |                                                                                                                                                  |  |

| AD133*                                                                                                               | TAMP | Amplifier Settling Time                                               | _   | —            | 5   | μS    |                                                                                                                                                  |  |

| AD134                                                                                                                | Tgo  | Q4 to A/D Clock Start                                                 | —   | Tosc/2       |     | —     |                                                                                                                                                  |  |

|                                                                                                                      |      |                                                                       | _   | Tosc/2 + Tcy |     |       | If the A/D clock source is selected as RC, a time of TCY is added before the A/D clock starts. This allows the SLEEP instruction to be executed. |  |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

**Note 1:** ADRESH and ADRESL registers may be read on the following TCY cycle.

2: See Section 8.3 "A/D Acquisition Requirements" for minimum conditions.

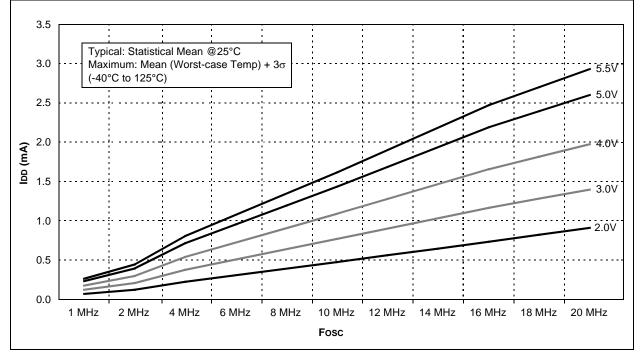

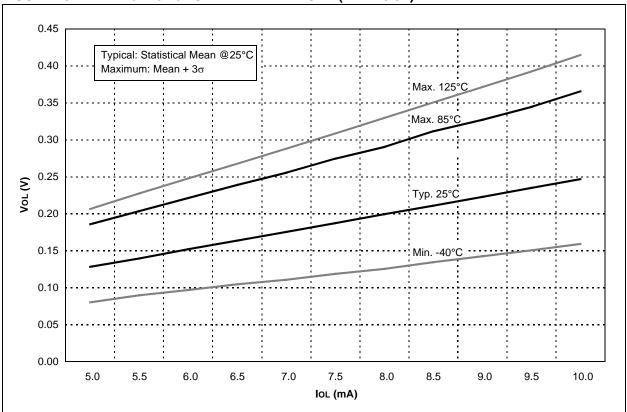

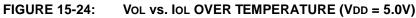

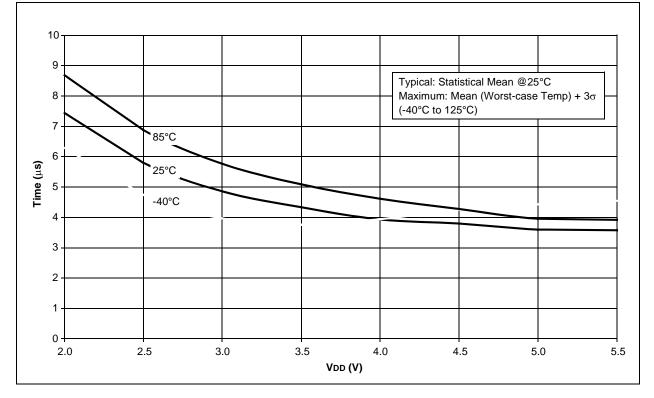

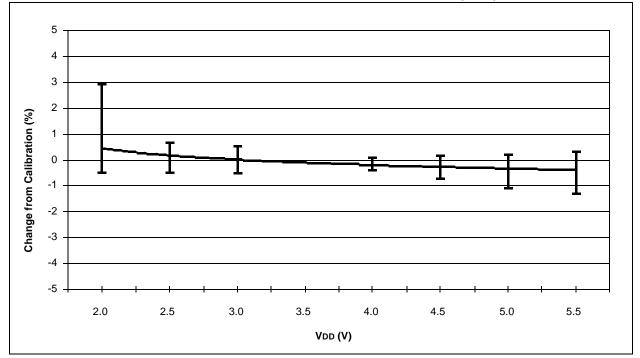

# 15.0 DC AND AC CHARACTERISTICS GRAPHS AND TABLES

The graphs and tables provided in this section are for **design guidance** and are **not tested**.

In some graphs or tables, the data presented are **outside specified operating range** (i.e., outside specified VDD range). This is for **information only** and devices are ensured to operate properly only within the specified range.

**Note:** The graphs and tables provided following this note are a statistical summary based on a limited number of samples and are provided for informational purposes only. The performance characteristics listed herein are not tested or guaranteed. In some graphs or tables, the data presented may be outside the specified operating range (e.g., outside specified power supply range) and therefore, outside the warranted range.

"Typical" represents the mean of the distribution at 25°C. "Maximum" or "minimum" represents (mean +  $3\sigma$ ) or (mean -  $3\sigma$ ) respectively, where  $\sigma$  is a standard deviation, over each temperature range.

© 2009 Microchip Technology Inc.

FIGURE 15-37: TYPICAL HFINTOSC FREQUENCY CHANGE vs. VDD (25°C)

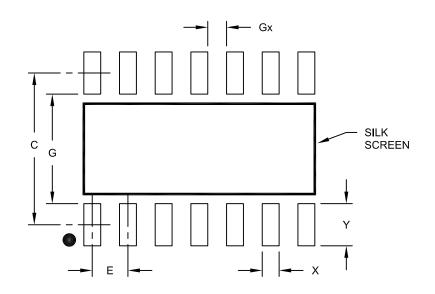

14-Lead Plastic Small Outline (SL) - Narrow, 3.90 mm Body [SOIC]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

# RECOMMENDED LAND PATTERN

|                       | Linita           | •           |      | <u> </u> |  |

|-----------------------|------------------|-------------|------|----------|--|

|                       | Units            | MILLIMETERS |      |          |  |

| Dimension             | Dimension Limits |             | NOM  | MAX      |  |

| Contact Pitch         | 1.27 BSC         |             |      |          |  |

| Contact Pad Spacing   | С                |             | 5.40 |          |  |

| Contact Pad Width     | X                |             |      | 0.60     |  |

| Contact Pad Length    | Y                |             |      | 1.50     |  |

| Distance Between Pads | Gx               | 0.67        |      |          |  |

| Distance Between Pads | G                | 3.90        |      |          |  |

Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2065A

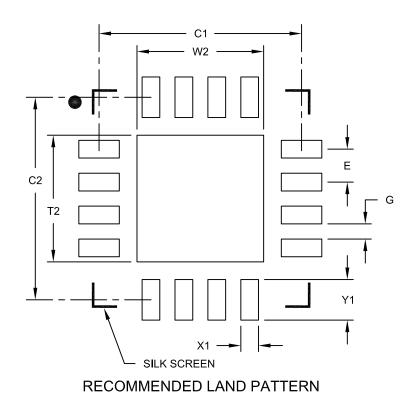

16-Lead Plastic Quad Flat, No Lead Package (ML) - 4x4x0.9mm Body [QFN]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                            | MILLIMETERS |          |      |      |  |  |

|----------------------------|-------------|----------|------|------|--|--|

| Dimensior                  | MIN         | NOM      | MAX  |      |  |  |

| Contact Pitch              | E           | 0.65 BSC |      |      |  |  |

| Optional Center Pad Width  | W2          |          |      | 2.50 |  |  |

| Optional Center Pad Length | T2          |          |      | 2.50 |  |  |

| Contact Pad Spacing        | C1          |          | 4.00 |      |  |  |

| Contact Pad Spacing        | C2          |          | 4.00 |      |  |  |

| Contact Pad Width (X28)    | X1          |          |      | 0.35 |  |  |

| Contact Pad Length (X28)   | Y1          |          |      | 0.80 |  |  |

| Distance Between Pads      | G           | 0.30     |      |      |  |  |

Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2127A