Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XF

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 20MHz                                                                     |

| Connectivity               | UART/USART                                                                |

| Peripherals                | Brown-out Detect/Reset, POR, WDT                                          |

| Number of I/O              | 12                                                                        |

| Program Memory Size        | 7KB (4K x 14)                                                             |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 256 x 8                                                                   |

| RAM Size                   | 256 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                 |

| Data Converters            | A/D 8x10b                                                                 |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 14-TSSOP (0.173", 4.40mm Width)                                           |

| Supplier Device Package    | 14-TSSOP                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f688t-e-st |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### FIGURE 2-2: PIC16F688 SPECIAL FUNCTION REGISTERS

|                     | Address |                       | Address |                    | Address |                    | Addres |

|---------------------|---------|-----------------------|---------|--------------------|---------|--------------------|--------|

| ndirect addr. (1)   | 00h     | Indirect addr. (1)    | 80h     | Indirect addr. (1) | 100h    | Indirect addr. (1) | 180h   |

| TMR0                | 01h     | OPTION_REG            | 81h     | TMR0               | 101h    | OPTION_REG         | 181h   |

| PCL                 | 02h     | PCL                   | 82h     | PCL                | 102h    | PCL                | 182h   |

| STATUS              | 03h     | STATUS                | 83h     | STATUS             | 103h    | STATUS             | 183h   |

| FSR                 | 04h     | FSR                   | 84h     | FSR                | 104h    | FSR                | 184h   |

| PORTA               | 05h     | TRISA                 | 85h     | PORTA              | 105h    | TRISA              | 185h   |

|                     | 06h     |                       | 86h     |                    | 106h    |                    | 186h   |

| PORTC               | 07h     | TRISC                 | 87h     | PORTC              | 107h    | TRISC              | 187h   |

|                     | 08h     |                       | 88h     |                    | 108h    |                    | 188h   |

|                     | 09h     |                       | 89h     |                    | 109h    |                    | 189h   |

| PCLATH              | 0Ah     | PCLATH                | 8Ah     | PCLATH             | 10Ah    | PCLATH             | 18Ah   |

| INTCON              | 0Bh     | INTCON                | 8Bh     | INTCON             | 10Bh    | INTCON             | 18Bh   |

| PIR1                | 0Ch     | PIE1                  | 8Ch     |                    | 10Ch    |                    | 18Ch   |

|                     | 0Dh     |                       | 8Dh     |                    | 10Dh    |                    | 18Dh   |

| TMR1L               | 0Eh     | PCON                  | 8Eh     |                    | 10Eh    |                    | 18Eh   |

| TMR1H               | 0Fh     | OSCCON                | 8Fh     |                    | 10Fh    |                    | 18Fh   |

| T1CON               | 10h     | OSCTUNE               | 90h     |                    | 110h    |                    | 190h   |

| BAUDCTL             | 11h     | ANSEL                 | 91h     |                    | 111h    |                    | 191h   |

| SPBRGH              | 12h     |                       | 92h     |                    | 112h    |                    | 192h   |

| SPBRG               | 13h     |                       | 93h     |                    | 113h    |                    | 193h   |

| RCREG               | 14h     |                       | 94h     |                    | 114h    |                    | 194h   |

| TXREG               | 15h     | WPUA                  | 95h     |                    | 115h    |                    | 195h   |

| TXSTA               | 16h     | IOCA                  | 96h     |                    | 116h    |                    | 196h   |

| RCSTA               | 17h     | EEDATH                | 97h     |                    | 117h    |                    | 197h   |

| WDTCON              | 18h     | EEADRH                | 98h     |                    | 118h    |                    | 198h   |

| CMCON0              | 19h     | VRCON                 | 99h     |                    | 119h    |                    | 199h   |

| CMCON1              | 1Ah     | EEDAT                 | 9Ah     |                    | 11Ah    |                    | 19Ah   |

|                     | 1Bh     | EEADR                 | 9Bh     |                    | 11Bh    |                    | 19Bh   |

|                     | 1Ch     | EECON1                | 9Ch     |                    | 11Ch    |                    | 19Ch   |

|                     | 1Dh     | EECON2 <sup>(1)</sup> | 9Dh     |                    | 11Dh    |                    | 19Dh   |

| ADRESH              | 1Eh     | ADRESL                | 9Eh     |                    | 11Eh    |                    | 19Eh   |

| ADCON0              | 1Fh     | ADCON1                | 9Fh     |                    | 11Fh    |                    | 19Fh   |

|                     | 20h     |                       | A0h     |                    | 120h    |                    | 1A0h   |

|                     |         | General               |         | General            |         |                    |        |

| General             |         | Purpose               |         | Purpose            |         |                    |        |

| Purpose<br>Register |         | Register              |         | Register           |         |                    |        |

| -                   |         | 80 Bytes              |         | 80 Bytes           |         |                    |        |

| 96 Bytes            |         |                       | EFh     |                    | 16Fh    |                    | 1EFh   |

|                     |         | accesses              | F0h     | accesses           | 170h    | accesses           | 1F0h   |

|                     | 7Fh     | Bank 0                | FFh     | Bank 0             | 17Fh    | Bank 0             | 1FFh   |

| Bank 0              | -       | Bank 1                |         | Bank 2             |         | Bank 3             | -      |

**Note 1:** Not a physical register.

#### 2.2.2.3 INTCON Register

The INTCON register is a readable and writable register, which contains the various enable and flag bits for TMR0 register overflow, PORTA change and external RA2/INT pin interrupts.

Note: Interrupt flag bits are set when an interrupt condition occurs, regardless of the state of its corresponding enable bit or the global enable bit, GIE of the INTCON register. User software should ensure the appropriate interrupt flag bits are clear prior to enabling an interrupt.

#### REGISTER 2-3: INTCON: INTERRUPT CONTROL REGISTER

| R/W-0 | R/W-x |

|-------|-------|-------|-------|-------|-------|-------|-------|

| GIE   | PEIE  | TOIE  | INTE  | RAIE  | TOIF  | INTF  | RAIF  |

| bit 7 |       |       |       |       |       |       | bit 0 |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | l as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

| bit 7 | <b>GIE:</b> Global Interrupt Enable bit<br>1 = Enables all unmasked interrupts<br>0 = Disables all interrupts                                                                                    |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 6 | <b>PEIE:</b> Peripheral Interrupt Enable bit<br>1 = Enables all unmasked peripheral interrupts<br>0 = Disables all peripheral interrupts                                                         |

| bit 5 | <b>TolE:</b> Timer0 Overflow Interrupt Enable bit<br>1 = Enables the Timer0 interrupt<br>0 = Disables the Timer0 interrupt                                                                       |

| bit 4 | INTE: RA2/INT External Interrupt Enable bit<br>1 = Enables the RA2/INT external interrupt<br>0 = Disables the RA2/INT external interrupt                                                         |

| bit 3 | <b>RAIE:</b> PORTA Change Interrupt Enable bit <sup>(1)</sup><br>1 = Enables the PORTA change interrupt<br>0 = Disables the PORTA change interrupt                                               |

| bit 2 | <b>TOIF:</b> Timer0 Overflow Interrupt Flag bit <sup>(2)</sup><br>1 = Timer0 register has overflowed (must be cleared in software)<br>0 = Timer0 register did not overflow                       |

| bit 1 | INTF: RA2/INT External Interrupt Flag bit<br>1 = The RA2/INT external interrupt occurred (must be cleared in software)<br>0 = The RA2/INT external interrupt did not occur                       |

| bit 0 | <b>RAIF:</b> PORTA Change Interrupt Flag bit<br>1 = When at least one of the PORTA <5:0> pins changed state (must be cleared in software)<br>0 = None of the PORTA <5:0> pins have changed state |

|       |                                                                                                                                                                                                  |

- Note 1: IOCA register must also be enabled.

- 2: T0IF bit is set when TMR0 rolls over. TMR0 is unchanged on Reset and should be initialized before clearing T0IF bit.

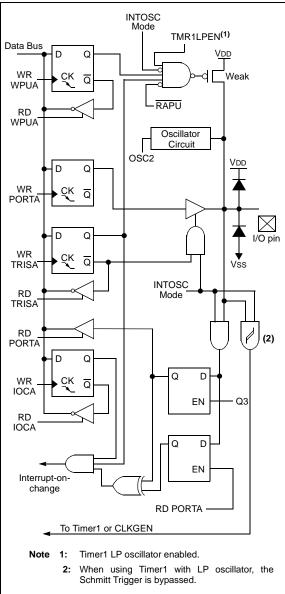

# 4.0 I/O PORTS

There are as many as twelve general purpose I/O pins available. Depending on which peripherals are enabled, some or all of the pins may not be available as general purpose I/O. In general, when a peripheral is enabled, the associated pin may not be used as a general purpose I/O pin.

### 4.1 PORTA and the TRISA Registers

PORTA is a 6-bit wide, bidirectional port. The corresponding data direction register is TRISA. Setting a TRISA bit (= 1) will make the corresponding PORTA pin an input (i.e., put the corresponding output driver in a High-Impedance mode). Clearing a TRISA bit (= 0) will make the corresponding PORTA pin an output (i.e., put the contents of the output latch on the selected pin). The exception is RA3, which is input only and its TRISA bit will always read as '1'. Example 4-1 shows how to initialize PORTA.

Reading the PORTA register reads the status of the pins, whereas writing to it will write to the PORT latch. All write operations are read-modify-write operations.

Therefore, a write to a port implies that the port pins are read, this value is modified and then written to the PORT data latch. RA3 reads '0' when MCLRE = 1.

The TRISA register controls the direction of the PORTA pins, even when they are being used as analog inputs. The user must ensure the bits in the TRISA register are maintained set when using them as analog inputs. I/O pins configured as analog input always read '0'.

| Note: | The ANSEL and CMCON0 registers must         |  |  |  |  |  |  |

|-------|---------------------------------------------|--|--|--|--|--|--|

|       | be initialized to configure an analog       |  |  |  |  |  |  |

|       | channel as a digital input. Pins configured |  |  |  |  |  |  |

|       | as analog inputs will read '0'.             |  |  |  |  |  |  |

| EXAMP   | 'LE 4-1: | INITIALIZING PORTA     |

|---------|----------|------------------------|

| BANKSEI | L PORTA  | ;                      |

| CLRF    | PORTA    | ;Init PORTA            |

| MOVLW   | 07h      | ;Set RA<2:0> to        |

| MOVWF   | CMCON0   | ;digital I/O           |

| BANKSEI | L ANSEL  | ;                      |

| CLRF    | ANSEL    | ;digital I/O           |

| MOVLW   | 0Ch      | ;Set RA<3:2> as inputs |

| MOVWF   | TRISA    | ;and set RA<5:4,1:0>   |

|         |          | ;as outputs            |

#### REGISTER 4-1: PORTA: PORTA REGISTER

| RA5                               | RA4                                                                                            | RA3                                                                | RA2                                                                | RA1                                                                | RA0<br>bit                                                         |  |  |

|-----------------------------------|------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|--------------------------------------------------------------------|--------------------------------------------------------------------|--------------------------------------------------------------------|--|--|

|                                   |                                                                                                |                                                                    |                                                                    |                                                                    | bit                                                                |  |  |

|                                   |                                                                                                |                                                                    |                                                                    |                                                                    |                                                                    |  |  |

|                                   |                                                                                                |                                                                    |                                                                    |                                                                    |                                                                    |  |  |

|                                   |                                                                                                |                                                                    |                                                                    |                                                                    |                                                                    |  |  |

| R = Readable bit W = Writable bit |                                                                                                |                                                                    | U = Unimplemented bit, read as '0'                                 |                                                                    |                                                                    |  |  |

| '1' = Bit is set                  |                                                                                                | '0' = Bit is cleared                                               |                                                                    | x = Bit is unknown                                                 | wn                                                                 |  |  |

|                                   |                                                                                                |                                                                    |                                                                    |                                                                    |                                                                    |  |  |

| nented: Read as '0'               |                                                                                                |                                                                    |                                                                    |                                                                    |                                                                    |  |  |

| PORTA I/O Pin bit                 |                                                                                                |                                                                    |                                                                    |                                                                    |                                                                    |  |  |

| in is > Viн                       |                                                                                                |                                                                    |                                                                    |                                                                    |                                                                    |  |  |

| in is < Vı∟                       |                                                                                                |                                                                    |                                                                    |                                                                    |                                                                    |  |  |

| :                                 | '1' = Bit is set<br>mented: Read as '0'<br>: PORTA I/O Pin bit<br>bin is > VIH<br>bin is < VIL | <b>mented</b> : Read as '0'<br>: PORTA I/O Pin bit<br>bin is > VIH | <b>mented</b> : Read as '0'<br>: PORTA I/O Pin bit<br>bin is > VIн | <b>nented</b> : Read as '0'<br>: PORTA I/O Pin bit<br>bin is > Vін | <b>nented</b> : Read as '0'<br>: PORTA I/O Pin bit<br>bin is > Vін |  |  |

| U-0   | U-0 | R/W-1  | R/W-1  | R-1    | R/W-1  | R/W-1  | R/W-1  |

|-------|-----|--------|--------|--------|--------|--------|--------|

| —     | —   | TRISA5 | TRISA4 | TRISA3 | TRISA2 | TRISA1 | TRISA0 |

| bit 7 |     |        |        |        |        |        | bit 0  |

| Legend:           |                  |                           |                    |

|-------------------|------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

bit 7-6 Unimplemented: Read as '0'

TRISA<5:0>: PORTA Tri-State Control bits

1 = PORTA pin configured as an input (tri-stated)

0 = PORTA pin configured as an output

**Note 1:** TRISA<3> always reads '1'.

2: TRISA<5:4> always reads '1' in XT, HS and LP Oscillator modes.

bit 5-0

### 4.2.5.6 RA5/T1CKI/OSC1/CLKIN

Figure 4-6 shows the diagram for this pin. The RA5 pin is configurable to function as one of the following:

- a general purpose I/O

- a Timer1 clock input

- a crystal/resonator connection

- a clock input

FIGURE 4-6: BLOCK DIAGRAM OF RA5

## 4.3 PORTC

PORTC is a general purpose I/O port consisting of 6 bidirectional pins. The pins can be configured for either digital I/O or analog input to A/D converter or comparator. For specific information about individual functions such as the EUSART or the A/D converter, refer to the appropriate section in this data sheet.

| Note: | The ANSEL and CMCON0 registers must         |  |  |  |  |  |  |

|-------|---------------------------------------------|--|--|--|--|--|--|

|       | be initialized to configure an analog       |  |  |  |  |  |  |

|       | channel as a digital input. Pins configured |  |  |  |  |  |  |

|       | as analog inputs will read '0'.             |  |  |  |  |  |  |

#### EXAMPLE 4-3: INITIALIZING PORTC

| BANKSEL | PORTC  | ;                      |

|---------|--------|------------------------|

| CLRF    | PORTC  | ;Init PORTC            |

| MOVLW   | 07h    | ;Set RC<4,1:0> to      |

| MOVWF   | CMCON0 | ;digital I/O           |

| BANKSEL | ANSEL  | ;                      |

| CLRF    | ANSEL  | ;digital I/O           |

| MOVLW   | 0Ch    | ;Set RC<3:2> as inputs |

| MOVWF   | TRISC  | ;and set RC<5:4,1:0>   |

|         |        | ;as outputs            |

|         |        |                        |

#### REGISTER 4-6: PORTC: PORTC REGISTER

| U-0     | U-0 R/W-x |         | R/W-x R/W-0 |     | R/W-0 | R/W-0 | R/W-0 |  |

|---------|-----------|---------|-------------|-----|-------|-------|-------|--|

| — — RC5 |           | RC4 RC3 |             | RC2 | RC1   | RC0   |       |  |

| bit 7   |           |         |             |     |       |       | bit 0 |  |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

|                   |                  |                        |                    |

| bit 7-6 | Unimplemented: Read as '0' |

|---------|----------------------------|

|---------|----------------------------|

bit 5-0 **RC<5:0>**: PORTC I/O Pin bit 1 = PORTC pin is > VIH

0 = PORTC pin is < VIL

#### **REGISTER 4-7:** TRISC: PORTC TRI-STATE REGISTER

| U-0   | U-0 R/ |        | R/W-1 R/W-1 |        | R/W-1 R/W-1 |        | R/W-1  |  |

|-------|--------|--------|-------------|--------|-------------|--------|--------|--|

|       |        | TRISC5 | TRISC4      | TRISC3 | TRISC2      | TRISC1 | TRISC0 |  |

| bit 7 |        |        |             |        |             |        | bit 0  |  |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | l as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

bit 7-6 Unimplemented: Read as '0'

TRISC<5:0>: PORTC Tri-State Control bits

1 = PORTC pin configured as an input (tri-stated)

0 = PORTC pin configured as an output

bit 5-0

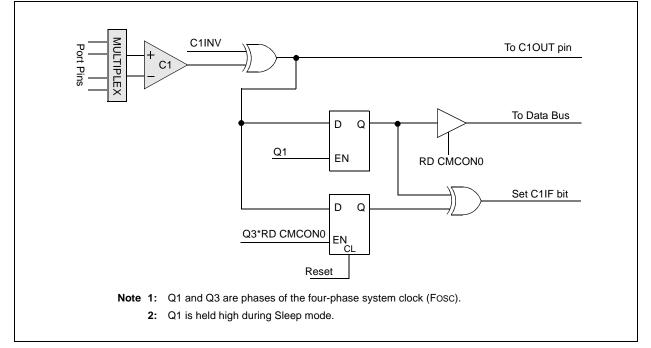

### FIGURE 7-2: COMPARATOR C1 OUTPUT BLOCK DIAGRAM

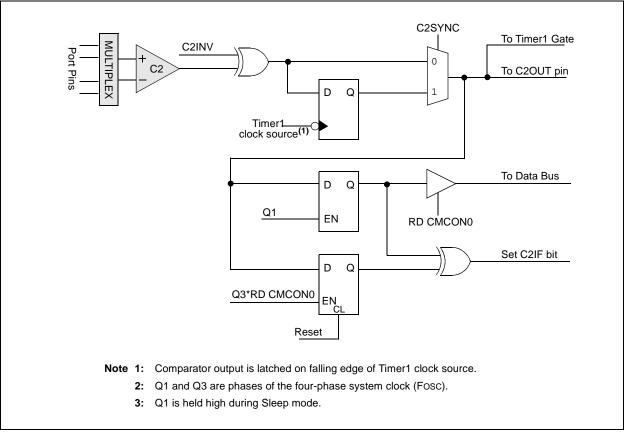

#### FIGURE 7-3: COMPARATOR C2 OUTPUT BLOCK DIAGRAM

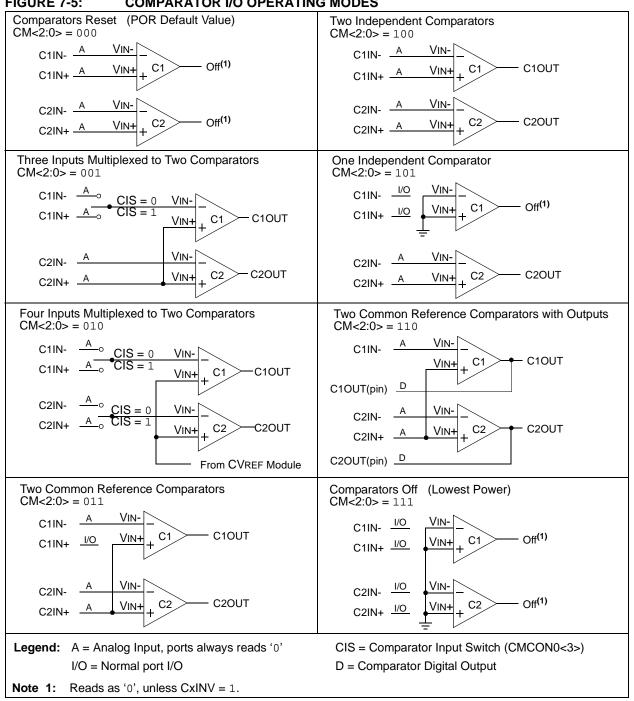

#### FIGURE 7-5: **COMPARATOR I/O OPERATING MODES**

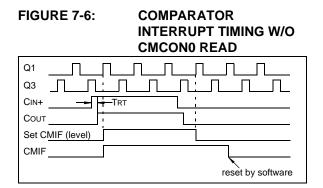

FIGURE 7-7: COMPARATOR INTERRUPT TIMING WITH CMCON0 READ

- Note 1: If a change in the CM1CON0 register (CxOUT) occurs when a read operation is being executed (start of the Q2 cycle), then the CxIF Interrupt Flag bit of the PIR1 register may not get set.

- 2: When either comparator is first enabled, bias circuitry in the comparator module may cause an invalid output from the comparator until the bias circuitry is stable. Allow about 1  $\mu$ s for bias settling then clear the mismatch condition and interrupt flags before enabling comparator interrupts.

## 7.6 Operation During Sleep

The comparator, if enabled before entering Sleep mode, remains active during Sleep. The additional current consumed by the comparator is shown separately in **Section 14.0** "**Electrical Specifications**". If the comparator is not used to wake the device, power consumption can be minimized while in Sleep mode by turning off the comparator. The comparator is turned off by selecting mode CM<2:0> = 000 or CM<2:0> = 111 of the CMCON0 register.

A change to the comparator output can wake-up the device from Sleep. To enable the comparator to wake the device from Sleep, the CxIE bit of the PIE1 register and the PEIE bit of the INTCON register must be set. The instruction following the Sleep instruction always executes following a wake from Sleep. If the GIE bit of the INTCON register is also set, the device will then execute the Interrupt Service Routine.

### 7.7 Effects of a Reset

A device Reset forces the CMCON0 and CMCON1 registers to their Reset states. This forces the comparator module to be in the Comparator Reset mode (CM<2:0> = 000). Thus, all comparator inputs are analog inputs with the comparator disabled to consume the smallest current possible.

#### 7.10 Comparator Voltage Reference

The Comparator Voltage Reference module provides an internally generated voltage reference for the comparators. The following features are available:

- Independent from Comparator operation

- Two 16-level voltage ranges

- Output clamped to Vss

- Ratiometric with VDD

The VRCON register (Figure 7-3) controls the Voltage Reference module shown in Figure 7-8.

#### 7.10.1 INDEPENDENT OPERATION

The comparator voltage reference is independent of the comparator configuration. Setting the VREN bit of the VRCON register will enable the voltage reference.

#### 7.10.2 OUTPUT VOLTAGE SELECTION

The CVREF voltage reference has 2 ranges with 16 voltage levels in each range. Range selection is controlled by the VRR bit of the VRCON register. The 16 levels are set with the VR<3:0> bits of the VRCON register.

The CVREF output voltage is determined by the following equations:

#### EQUATION 7-1: CVREF OUTPUT VOLTAGE

```

V_{RR} = 1 (low range):

CV_{REF} = (VR < 3:0 > /24) \times VDD

V_{RR} = 0 (high range):

CV_{REF} = (VDD/4) + (VR < 3:0 > \times VDD/32)

```

The full range of VSS to VDD cannot be realized due to the construction of the module. See Figure 7-8.

#### 7.10.3 OUTPUT CLAMPED TO Vss

The CVREF output voltage can be set to Vss with no power consumption by configuring VRCON as follows:

- VREN = 0

- VRR = 1

- VR<3:0> = 0000

This allows the comparator to detect a zero-crossing while not consuming additional CVREF module current.

#### 7.10.4 OUTPUT RATIOMETRIC TO VDD

The comparator voltage reference is VDD derived and therefore, the CVREF output changes with fluctuations in VDD. The tested absolute accuracy of the Comparator Voltage Reference can be found in **Section 14.0 "Electrical Specifications"**.

#### REGISTER 7-3: VRCON: VOLTAGE REFERENCE CONTROL REGISTER

| R/W-0 | U-0        | R/W-0 | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|-------|------------|-------|-----|-------|-------|-------|-------|

| VREN  | VREN — VRR |       | —   | VR3   | VR2   | VR1   | VR0   |

| bit 7 |            |       |     |       |       |       | bit 0 |

|       |            |       |     |       |       |       |       |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

| bit 7   | VREN: CVREF Enable bit                                                                                                                                                                   |

|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | 1 = CVREF circuit powered on<br>0 = CVREF circuit powered down, no IDD drain and CVREF = VSS.                                                                                            |

| bit 6   | Unimplemented: Read as '0'                                                                                                                                                               |

| bit 5   | VRR: CVREF Range Selection bit                                                                                                                                                           |

|         | 1 = Low range<br>0 = High range                                                                                                                                                          |

| bit 4   | Unimplemented: Read as '0'                                                                                                                                                               |

| bit 3-0 | <b>VR&lt;3:0&gt;:</b> CVREF Value Selection bits $(0 \le VR<3:0>\le 15)$<br><u>When VRR = 1</u> : CVREF = (VR<3:0>/24) * VDD<br><u>When VRR = 0</u> : CVREF = VDD/4 + (VR<3:0>/32) * VDD |

|         |                                                                                                                                                                                          |

| Name   | Bit 7                         | Bit 6        | Bit 5   | Bit 4  | Bit 3  | Bit 2  | Bit 1   | Bit 0  | Value on<br>POR, BOR | Value on<br>all other<br>Resets |

|--------|-------------------------------|--------------|---------|--------|--------|--------|---------|--------|----------------------|---------------------------------|

| ADCON0 | ADFM                          | VCFG         | —       | CHS2   | CHS1   | CHS0   | GO/DONE | ADON   | 00-0 0000            | 00-0 0000                       |

| ADCON1 | _                             | ADCS2        | ADCS1   | ADCS0  | —      | _      | _       |        | -000                 | -000                            |

| ANSEL  | ANS7                          | ANS6         | ANS5    | ANS4   | ANS3   | ANS2   | ANS1    | ANS0   | 1111 1111            | 1111 1111                       |

| ADRESH | A/D Result Register High Byte |              |         |        |        |        |         |        | xxxx xxxx            | uuuu uuuu                       |

| ADRESL | A/D Resul                     | t Register L | ow Byte |        |        |        |         |        | xxxx xxxx            | uuuu uuuu                       |

| INTCON | GIE                           | PEIE         | TOIE    | INTE   | RAIE   | T0IF   | INTF    | RAIF   | 0000 000x            | 0000 000x                       |

| PIE1   | EEIE                          | ADIE         | RCIE    | C2IE   | C1IE   | OSFIE  | TXIE    | TMR1IE | 0000 0000            | 0000 0000                       |

| PIR1   | EEIF                          | ADIF         | RCIF    | C2IF   | C1IF   | OSFIF  | TXIF    | TMR1IF | 0000 0000            | 0000 0000                       |

| PORTA  | _                             | —            | RA5     | RA4    | RA3    | RA2    | RA1     | RA0    | x0 x000              | x0 x000                         |

| PORTC  | _                             | _            | RC5     | RC4    | RC3    | RC2    | RC1     | RC0    | xx 0000              | xx 0000                         |

| TRISA  | _                             | _            | TRISA5  | TRISA4 | TRISA3 | TRISA2 | TRISA1  | TRISA0 | 11 1111              | 11 1111                         |

| TRISC  | —                             | —            | TRISC5  | TRISC4 | TRISC3 | TRISC2 | TRISC1  | TRISC0 | 11 1111              | 11 1111                         |

TABLE 8-2: SUMMARY OF ASSOCIATED ADC REGISTERS

**Legend:** x = unknown, u = unchanged, - = unimplemented read as '0'. Shaded cells are not used for ADC module.

| R/W-x           | U-0                                                                                  | U-0                            | U-0          | R/W-x            | R/W-0            | R/S-0           | R/S-0          |  |  |  |  |

|-----------------|--------------------------------------------------------------------------------------|--------------------------------|--------------|------------------|------------------|-----------------|----------------|--|--|--|--|

| EEPGD           |                                                                                      | _                              | _            | WRERR            | WREN             | WR              | RD             |  |  |  |  |

| bit 7           |                                                                                      |                                |              |                  |                  |                 | bit (          |  |  |  |  |

|                 |                                                                                      |                                |              |                  |                  |                 |                |  |  |  |  |

| Legend:         |                                                                                      |                                |              |                  |                  |                 |                |  |  |  |  |

| S = Bit can or  | nly be set                                                                           |                                |              |                  |                  |                 |                |  |  |  |  |

| R = Readable    | e bit                                                                                | W = Writable                   | bit          | U = Unimplen     | nented bit, read | l as '0'        |                |  |  |  |  |

| -n = Value at I | POR                                                                                  | '1' = Bit is set               |              | '0' = Bit is cle | ared             | x = Bit is unkr | nown           |  |  |  |  |

|                 |                                                                                      |                                |              |                  |                  |                 |                |  |  |  |  |

| bit 7           |                                                                                      | gram/Data EEF                  |              | bit              |                  |                 |                |  |  |  |  |

|                 |                                                                                      | s program mer<br>s data memory |              |                  |                  |                 |                |  |  |  |  |

| bit 6-4         |                                                                                      | ited: Read as '                |              |                  |                  |                 |                |  |  |  |  |

| bit 3           | -                                                                                    | PROM Error FI                  |              |                  |                  |                 |                |  |  |  |  |

|                 |                                                                                      |                                | •            | ninated (any MC  | LR Reset, any    | WDT Reset du    | ıring          |  |  |  |  |

|                 | normal operation or BOR Reset)<br>0 = The write operation completed                  |                                |              |                  |                  |                 |                |  |  |  |  |

|                 |                                                                                      |                                | -            |                  |                  |                 |                |  |  |  |  |

| bit 2           | WREN: EEPROM Write Enable bit                                                        |                                |              |                  |                  |                 |                |  |  |  |  |

|                 | 1 = Allows write cycles<br>0 = Inhibits write to the data EEPROM                     |                                |              |                  |                  |                 |                |  |  |  |  |

| bit 1           | WR: Write Co                                                                         |                                |              |                  |                  |                 |                |  |  |  |  |

|                 | EEPGD = 1:                                                                           |                                |              |                  |                  |                 |                |  |  |  |  |

|                 | This bit is ign                                                                      | ored                           |              |                  |                  |                 |                |  |  |  |  |

|                 | $\underline{EEPGD} = 0$                                                              |                                |              |                  |                  |                 | (D. L.).       |  |  |  |  |

|                 |                                                                                      |                                |              | red by hardware  | once write is c  | omplete. The W  | VR bit can onl |  |  |  |  |

|                 | be set, not cleared, in software.)<br>0 = Write cycle to the data EEPROM is complete |                                |              |                  |                  |                 |                |  |  |  |  |

| bit 0           | <b>RD:</b> Read Control bit                                                          |                                |              |                  |                  |                 |                |  |  |  |  |

|                 |                                                                                      | •                              | d (the RD is | cleared in hard  | dware and can    | only be set, r  | not cleared, i |  |  |  |  |

|                 | software                                                                             | .)<br>t initiate a merr        |              |                  |                  |                 |                |  |  |  |  |

|                 | $() - 1) \cos n \alpha$                                                              | t initiata a mam               | ory road     |                  |                  |                 |                |  |  |  |  |

## REGISTER 9-5: EECON1: EEPROM CONTROL REGISTER

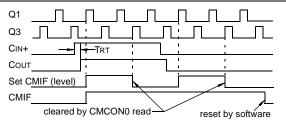

#### FIGURE 10-2: EUSART RECEIVE BLOCK DIAGRAM

The operation of the EUSART module is controlled through three registers:

- Transmit Status and Control (TXSTA)

- Receive Status and Control (RCSTA)

- Baud Rate Control (BAUDCTL)

These registers are detailed in Register 10-1, Register 10-2 and Register 10-3, respectively.

|        |                   | SYNC = 0, BRGH = 1, BRG16 = 1 or SYNC = 1, BRG16 = 1 |                             |                   |            |                             |                    |            |                             |                |                  |                             |  |  |  |

|--------|-------------------|------------------------------------------------------|-----------------------------|-------------------|------------|-----------------------------|--------------------|------------|-----------------------------|----------------|------------------|-----------------------------|--|--|--|

| BAUD   | Fosc = 20.000 MHz |                                                      |                             | Fosc = 18.432 MHz |            |                             | Fosc = 11.0592 MHz |            |                             | Fos            | Fosc = 8.000 MHz |                             |  |  |  |

| RATE   | Actual<br>Rate    | %<br>Error                                           | SPBRG<br>value<br>(decimal) | Actual<br>Rate    | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate     | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate | %<br>Error       | SPBRG<br>value<br>(decimal) |  |  |  |

| 300    | 300.0             | 0.00                                                 | 16665                       | 300.0             | 0.00       | 15359                       | 300.0              | 0.00       | 9215                        | 300.0          | 0.00             | 6666                        |  |  |  |

| 1200   | 1200              | -0.01                                                | 4166                        | 1200              | 0.00       | 3839                        | 1200               | 0.00       | 2303                        | 1200           | -0.02            | 1666                        |  |  |  |

| 2400   | 2400              | 0.02                                                 | 2082                        | 2400              | 0.00       | 1919                        | 2400               | 0.00       | 1151                        | 2401           | 0.04             | 832                         |  |  |  |

| 9600   | 9597              | -0.03                                                | 520                         | 9600              | 0.00       | 479                         | 9600               | 0.00       | 287                         | 9615           | 0.16             | 207                         |  |  |  |

| 10417  | 10417             | 0.00                                                 | 479                         | 10425             | 0.08       | 441                         | 10433              | 0.16       | 264                         | 10417          | 0                | 191                         |  |  |  |

| 19.2k  | 19.23k            | 0.16                                                 | 259                         | 19.20k            | 0.00       | 239                         | 19.20k             | 0.00       | 143                         | 19.23k         | 0.16             | 103                         |  |  |  |

| 57.6k  | 57.47k            | -0.22                                                | 86                          | 57.60k            | 0.00       | 79                          | 57.60k             | 0.00       | 47                          | 57.14k         | -0.79            | 34                          |  |  |  |

| 115.2k | 116.3k            | 0.94                                                 | 42                          | 115.2k            | 0.00       | 39                          | 115.2k             | 0.00       | 23                          | 117.6k         | 2.12             | 16                          |  |  |  |

# TABLE 10-5: BAUD RATES FOR ASYNCHRONOUS MODES (CONTINUED)

|        |                  | SYNC = 0, BRGH = 1, BRG16 = 1 or SYNC = 1, BRG16 = 1 |                             |                   |            |                             |                  |            |                             |                  |            |                             |  |  |  |

|--------|------------------|------------------------------------------------------|-----------------------------|-------------------|------------|-----------------------------|------------------|------------|-----------------------------|------------------|------------|-----------------------------|--|--|--|

| BAUD   | Fosc = 4.000 MHz |                                                      |                             | Fosc = 3.6864 MHz |            |                             | Fosc = 2.000 MHz |            |                             | Fosc = 1.000 MHz |            |                             |  |  |  |

| RATE   | Actual<br>Rate   | %<br>Error                                           | SPBRG<br>value<br>(decimal) | Actual<br>Rate    | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate   | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate   | %<br>Error | SPBRG<br>value<br>(decimal) |  |  |  |

| 300    | 300.0            | 0.01                                                 | 3332                        | 300.0             | 0.00       | 3071                        | 299.9            | -0.02      | 1666                        | 300.1            | 0.04       | 832                         |  |  |  |

| 1200   | 1200             | 0.04                                                 | 832                         | 1200              | 0.00       | 767                         | 1199             | -0.08      | 416                         | 1202             | 0.16       | 207                         |  |  |  |

| 2400   | 2398             | 0.08                                                 | 416                         | 2400              | 0.00       | 383                         | 2404             | 0.16       | 207                         | 2404             | 0.16       | 103                         |  |  |  |

| 9600   | 9615             | 0.16                                                 | 103                         | 9600              | 0.00       | 95                          | 9615             | 0.16       | 51                          | 9615             | 0.16       | 25                          |  |  |  |

| 10417  | 10417            | 0.00                                                 | 95                          | 10473             | 0.53       | 87                          | 10417            | 0.00       | 47                          | 10417            | 0.00       | 23                          |  |  |  |

| 19.2k  | 19.23k           | 0.16                                                 | 51                          | 19.20k            | 0.00       | 47                          | 19.23k           | 0.16       | 25                          | 19.23k           | 0.16       | 12                          |  |  |  |

| 57.6k  | 58.82k           | 2.12                                                 | 16                          | 57.60k            | 0.00       | 15                          | 55.56k           | -3.55      | 8                           | —                | _          | _                           |  |  |  |

| 115.2k | 111.1k           | -3.55                                                | 8                           | 115.2k            | 0.00       | 7                           | _                |            | —                           | —                |            | —                           |  |  |  |

#### FIGURE 10-8: AUTO-WAKE-UP BIT (WUE) TIMINGS DURING SLEEP

#### 10.3.4 BREAK CHARACTER SEQUENCE

The EUSART module has the capability of sending the special Break character sequences that are required by the LIN bus standard. A Break character consists of a Start bit, followed by 12 '0' bits and a Stop bit.

To send a Break character, set the SENDB and TXEN bits of the TXSTA register. The Break character transmission is then initiated by a write to the TXREG. The value of data written to TXREG will be ignored and all '0's will be transmitted.

The SENDB bit is automatically reset by hardware after the corresponding Stop bit is sent. This allows the user to preload the transmit FIFO with the next transmit byte following the Break character (typically, the Sync character in the LIN specification).

The TRMT bit of the TXSTA register indicates when the transmit operation is active or Idle, just as it does during normal transmission. See Figure 10-9 for the timing of the Break character sequence.

#### 10.3.4.1 Break and Sync Transmit Sequence

The following sequence will start a message frame header made up of a Break, followed by an auto-baud Sync byte. This sequence is typical of a LIN bus master.

- 1. Configure the EUSART for the desired mode.

- 2. Set the TXEN and SENDB bits to enable the Break sequence.

- 3. Load the TXREG with a dummy character to initiate transmission (the value is ignored).

- 4. Write '55h' to TXREG to load the Sync character into the transmit FIFO buffer.

- 5. After the Break has been sent, the SENDB bit is reset by hardware and the Sync character is then transmitted.

When the TXREG becomes empty, as indicated by the TXIF, the next data byte can be written to TXREG.

#### 10.3.5 RECEIVING A BREAK CHARACTER

The Enhanced EUSART module can receive a Break character in two ways.

The first method to detect a Break character uses the FERR bit of the RCSTA register and the Received data as indicated by RCREG. The Baud Rate Generator is assumed to have been initialized to the expected baud rate.

A Break character has been received when;

- · RCIF bit is set

- FERR bit is set

- RCREG = 00h

The second method uses the Auto-Wake-up feature described in **Section 10.3.3** "**Auto-Wake-up on Break**". By enabling this feature, the EUSART will sample the next two transitions on RX/DT, cause an RCIF interrupt, and receive the next data byte followed by another interrupt.

Note that following a Break character, the user will typically want to enable the Auto-Baud Detect feature. For both methods, the user can set the ABDEN bit of the BAUDCTL register before placing the EUSART in Sleep mode.

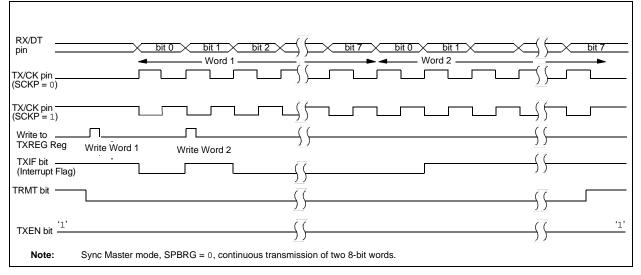

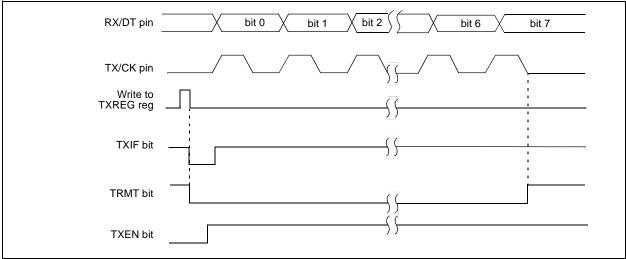

#### FIGURE 10-11: SYNCHRONOUS TRANSMISSION (THROUGH TXEN)

#### TABLE 10-7: REGISTERS ASSOCIATED WITH SYNCHRONOUS MASTER TRANSMISSION

| Name                                                                                                            | Bit 7                         | Bit 6 | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Value on<br>POR, BOR | Value on<br>all other<br>Resets |  |

|-----------------------------------------------------------------------------------------------------------------|-------------------------------|-------|--------|--------|--------|--------|--------|--------|----------------------|---------------------------------|--|

| BAUDCTL                                                                                                         | ABDOVF                        | RCIDL | —      | SCKP   | BRG16  | —      | WUE    | ABDEN  | 01-0 0-00            | 01-0 0-00                       |  |

| INTCON                                                                                                          | GIE                           | PEIE  | TOIE   | INTE   | RAIE   | T0IF   | INTF   | RAIF   | x000 000x            | x000 000x                       |  |

| PIE1                                                                                                            | EEIE                          | ADIE  | RCIE   | C2IE   | C1IE   | OSFIE  | TXIE   | TMR1IE | 0000 0000            | 0000 0000                       |  |

| PIR1                                                                                                            | EEIF                          | ADIF  | RCIF   | C2IF   | C1IF   | OSFIF  | TXIF   | TMR1IF | 0000 0000            | 0000 0000                       |  |

| RCREG                                                                                                           | EUSART Receive Data Register  |       |        |        |        |        |        |        | 0000 0000            | 0000 0000                       |  |

| RCSTA                                                                                                           | SPEN                          | RX9   | SREN   | CREN   | ADDEN  | FERR   | OERR   | RX9D   | 0000 000x            | 0000 000x                       |  |

| SPBRG                                                                                                           | BRG7                          | BRG6  | BRG5   | BRG4   | BRG3   | BRG2   | BRG1   | BRG0   | 0000 0000            | 0000 0000                       |  |

| SPBRGH                                                                                                          | BRG15                         | BRG14 | BRG13  | BRG12  | BRG11  | BRG10  | BRG9   | BRG8   | 0000 0000            | 0000 0000                       |  |

| TRISC                                                                                                           | _                             | _     | TRISC5 | TRISC4 | TRISC3 | TRISC2 | TRISC1 | TRISC0 | 11 1111              | 11 1111                         |  |

| TXREG                                                                                                           | EUSART Transmit Data Register |       |        |        |        |        |        |        | 0000 0000            | 0000 0000                       |  |

| TXSTA                                                                                                           | CSRC                          | TX9   | TXEN   | SYNC   | SENDB  | BRGH   | TRMT   | TX9D   | 0000 0010            | 0000 0010                       |  |

| Legend: $x = unknown = unimplemented read as (0) Shaded calls are not used for Synchronous Master Transmission$ |                               |       |        |        |        |        |        |        |                      |                                 |  |

Legend: x = unknown, - = unimplemented read as '0'. Shaded cells are not used for Synchronous Master Transmission.

### 11.3 Interrupts

The PIC16F688 has multiple sources of interrupt:

- External Interrupt RA2/INT

- TMR0 Overflow Interrupt

- PORTA Change Interrupts

- 2 Comparator Interrupts

- A/D Interrupt

- Timer1 Overflow Interrupt

- EEPROM Data Write Interrupt

- Fail-Safe Clock Monitor Interrupt

- · EUSART Receive and Transmit interrupts

The Interrupt Control (INTCON) register and Peripheral Interrupt Request 1 (PIR1) register record individual interrupt requests in flag bits. The INTCON register also has individual and global interrupt enable bits.

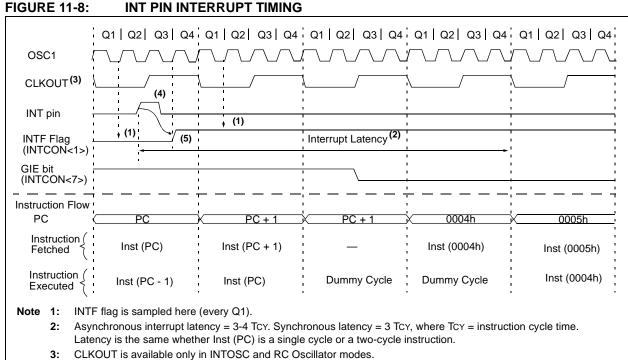

A Global Interrupt Enable bit, GIE bit of the INTCON register, enables (if set) all unmasked interrupts, or disables (if cleared) all interrupts. Individual interrupts can be disabled through their corresponding enable bits in the INTCON register and PIE1 register. GIE is cleared on Reset.

The Return from Interrupt instruction, RETFIE, exits the interrupt routine, as well as sets the GIE bit, which re-enables unmasked interrupts.

The following interrupt flags are contained in the INTCON register:

- INT Pin Interrupt

- PORTA Change Interrupt

- TMR0 Overflow Interrupt

The peripheral interrupt flags are contained in the special register, PIR1. The corresponding interrupt enable bit is contained in special register, PIE1.

The following interrupt flags are contained in the PIR1 register:

- EEPROM Data Write Interrupt

- A/D Interrupt

- EUSART Receive and Transmit Interrupts

- 2 Comparator Interrupts

- Timer1 Overflow Interrupt

- Fail-Safe Clock Monitor Interrupt

When an interrupt is serviced:

- The GIE is cleared to disable any further interrupt.

- The return address is pushed onto the stack.

- The PC is loaded with 0004h.

For external interrupt events, such as the INT pin or PORTA change interrupt, the interrupt latency will be three or four instruction cycles. The exact latency depends upon when the interrupt event occurs (see Figure 11-8). The latency is the same for one or two-cycle instructions. Once in the Interrupt Service Routine, the source(s) of the interrupt can be determined by polling the interrupt flag bits. The interrupt flag bit(s) must be cleared in software before re-enabling interrupts to avoid multiple interrupt requests.

- Note 1: Individual interrupt flag bits are set, regardless of the status of their corresponding mask bit or the GIE bit.

- 2: When an instruction that clears the GIE bit is executed, any interrupts that were pending for execution in the next cycle are ignored. The interrupts, which were ignored, are still pending to be serviced when the GIE bit is set again.

For additional information on Timer1, A/D or data EEPROM modules, refer to the respective peripheral section.

- 4: For minimum width of INT pulse, refer to AC specifications in Section 14.0 "Electrical Specifications".

- 5: INTF is enabled to be set any time during the Q4-Q1 cycles.

#### TABLE 11-6: SUMMARY OF REGISTERS ASSOCIATED WITH INTERRUPTS

| Name   | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0  | Value on<br>POR, BOR | Value on<br>all other<br>Resets |  |

|--------|-------|-------|-------|-------|-------|-------|-------|--------|----------------------|---------------------------------|--|

| INTCON | GIE   | PEIE  | TOIE  | INTE  | RAIE  | T0IF  | INTF  | RAIF   | x000 000x            | 0000 000x                       |  |

| PIE1   | EEIE  | ADIE  | RCIE  | C2IE  | C1IE  | OSFIE | TXIE  | TMR1IE | 0000 0000            | 0000 0000                       |  |

| PIR1   | EEIF  | ADIF  | RCIF  | C2IF  | C1IF  | OSFIF | TXIF  | TMR1IF | 0000 0000            | 0000 0000                       |  |

**Legend:** x = unknown, u = unchanged, - = unimplemented read as '0', q = value depends upon condition. Shaded cells are not used by the Interrupt module.

### 13.2 MPASM Assembler

The MPASM Assembler is a full-featured, universal macro assembler for all PIC MCUs.

The MPASM Assembler generates relocatable object files for the MPLINK Object Linker, Intel<sup>®</sup> standard HEX files, MAP files to detail memory usage and symbol reference, absolute LST files that contain source lines and generated machine code and COFF files for debugging.

The MPASM Assembler features include:

- Integration into MPLAB IDE projects

- User-defined macros to streamline

assembly code

- Conditional assembly for multi-purpose source files

- Directives that allow complete control over the assembly process

### 13.3 MPLAB C18 and MPLAB C30 C Compilers

The MPLAB C18 and MPLAB C30 Code Development Systems are complete ANSI C compilers for Microchip's PIC18 and PIC24 families of microcontrollers and the dsPIC30 and dsPIC33 family of digital signal controllers. These compilers provide powerful integration capabilities, superior code optimization and ease of use not found with other compilers.

For easy source level debugging, the compilers provide symbol information that is optimized to the MPLAB IDE debugger.

### 13.4 MPLINK Object Linker/ MPLIB Object Librarian

The MPLINK Object Linker combines relocatable objects created by the MPASM Assembler and the MPLAB C18 C Compiler. It can link relocatable objects from precompiled libraries, using directives from a linker script.

The MPLIB Object Librarian manages the creation and modification of library files of precompiled code. When a routine from a library is called from a source file, only the modules that contain that routine will be linked in with the application. This allows large libraries to be used efficiently in many different applications.

The object linker/library features include:

- Efficient linking of single libraries instead of many smaller files

- Enhanced code maintainability by grouping related modules together

- Flexible creation of libraries with easy module listing, replacement, deletion and extraction

# 13.5 MPLAB ASM30 Assembler, Linker and Librarian

MPLAB ASM30 Assembler produces relocatable machine code from symbolic assembly language for dsPIC30F devices. MPLAB C30 C Compiler uses the assembler to produce its object file. The assembler generates relocatable object files that can then be archived or linked with other relocatable object files and archives to create an executable file. Notable features of the assembler include:

- Support for the entire dsPIC30F instruction set

- · Support for fixed-point and floating-point data

- · Command line interface

- Rich directive set

- Flexible macro language

- MPLAB IDE compatibility

### 13.6 MPLAB SIM Software Simulator

The MPLAB SIM Software Simulator allows code development in a PC-hosted environment by simulating the PIC MCUs and dsPIC<sup>®</sup> DSCs on an instruction level. On any given instruction, the data areas can be examined or modified and stimuli can be applied from a comprehensive stimulus controller. Registers can be logged to files for further run-time analysis. The trace buffer and logic analyzer display extend the power of the simulator to record and track program execution, actions on I/O, most peripherals and internal registers.

The MPLAB SIM Software Simulator fully supports symbolic debugging using the MPLAB C18 and MPLAB C30 C Compilers, and the MPASM and MPLAB ASM30 Assemblers. The software simulator offers the flexibility to develop and debug code outside of the hardware laboratory environment, making it an excellent, economical software development tool.

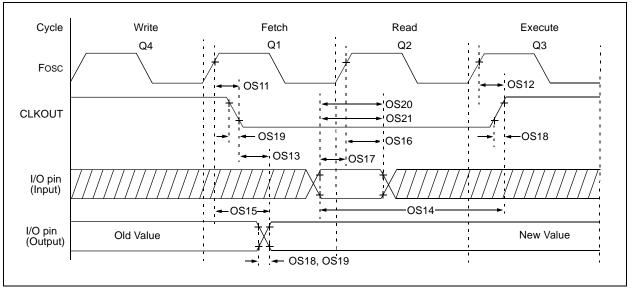

#### TABLE 14-3: CLKOUT AND I/O TIMING PARAMETERS

| Standard Operating Conditions (unless otherwise stated)<br>Operating Temperature -40°C $\leq$ TA $\leq$ +125°C |          |                                                             |               |          |          |       |                          |

|----------------------------------------------------------------------------------------------------------------|----------|-------------------------------------------------------------|---------------|----------|----------|-------|--------------------------|

| Param<br>No.                                                                                                   | Sym      | Characteristic                                              | Min           | Тур†     | Max      | Units | Conditions               |

| OS11                                                                                                           | TosH2cкL | Fosc↑ to CLKOUT↓ <sup>(1)</sup>                             | —             | _        | 70       | ns    | VDD = 5.0V               |

| OS12                                                                                                           | TosH2cкH | Fosc↑ to CLKOUT↑ <sup>(1)</sup>                             | —             | —        | 72       | ns    | VDD = 5.0V               |

| OS13                                                                                                           | TCKL2IOV | CLKOUT↓ to Port out valid <sup>(1)</sup>                    | —             | —        | 20       | ns    |                          |

| OS14                                                                                                           | ТюV2скН  | Port input valid before CLKOUT <sup>(1)</sup>               | Tosc + 200 ns | —        | _        | ns    |                          |

| OS15*                                                                                                          | TosH2IoV | Fosc↑ (Q1 cycle) to Port out valid                          | —             | 50       | 70       | ns    | VDD = 5.0V               |

| OS16                                                                                                           | TosH2IOI | Fosc↑ (Q2 cycle) to Port input invalid (I/O in hold time)   | 50            |          | _        | ns    | VDD = 5.0V               |

| OS17                                                                                                           | TioV2osH | Port input valid to Fosc1 (Q2 cycle)<br>(I/O in setup time) | 20            |          |          | ns    |                          |

| OS18                                                                                                           | TIOR     | Port output rise time <sup>(2)</sup>                        |               | 15<br>10 | 72<br>32 | ns    | VDD = 2.0V<br>VDD = 5.0V |

| OS19                                                                                                           | TIOF     | Port output fall time <sup>(2)</sup>                        |               | 28<br>15 | 55<br>30 | ns    | VDD = 2.0V<br>VDD = 5.0V |

| OS20*                                                                                                          | Tinp     | INT pin input high or low time                              | 25            | —        | _        | ns    |                          |

| OS21*                                                                                                          | Trap     | PORTA interrupt-on-change new input level time              | Тсү           | —        | _        | ns    |                          |

\* These parameters are characterized but not tested.

$\dagger~$  Data in "Typ" column is at 5.0V, 25°C unless otherwise stated.

Note 1: Measurements are taken in RC mode where CLKOUT output is 4 x Tosc.

2: Includes OSC2 in CLKOUT mode.

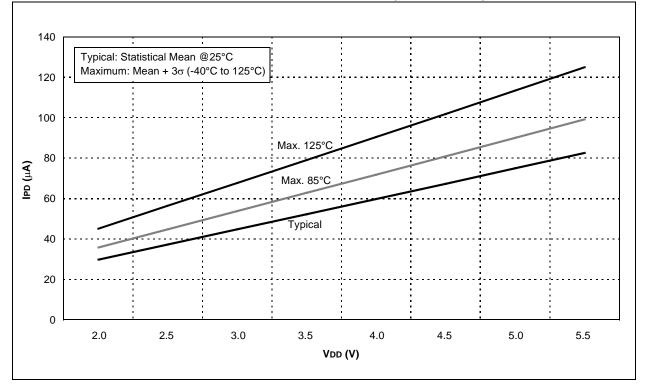

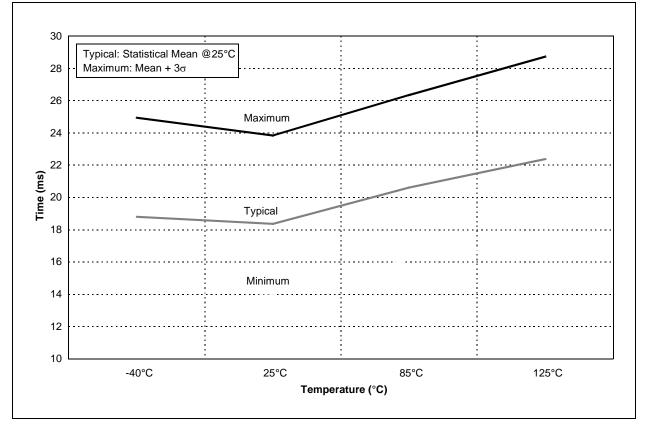

FIGURE 15-21: CVREF IPD vs. VDD OVER TEMPERATURE (HIGH RANGE)