Welcome to E-XFL.COM

#### Understanding <u>Embedded - DSP (Digital</u> <u>Signal Processors)</u>

#### Embedded - DSP (Digital Signal Processors) are specialized microprocessors designed to perform complex mathematical computations on digital signals in real-time. Unlike general-purpose processors, DSPs are optimized for high-speed numeric processing tasks, making them ideal for applications that require efficient and precise manipulation of digital data. These processors are fundamental in converting and processing signals in various forms, including audio, video, and communication signals, ensuring that data is accurately interpreted and utilized in embedded systems.

#### Applications of <u>Embedded - DSP (Digital</u> <u>Signal Processors)</u>

#### Details

E·XFl

| Product Status          | Active                                                               |

|-------------------------|----------------------------------------------------------------------|

| Туре                    | Fixed Point                                                          |

| Interface               | CAN, SPI, SSP, TWI, UART                                             |

| Clock Rate              | 400MHz                                                               |

| Non-Volatile Memory     | External                                                             |

| On-Chip RAM             | 132kB                                                                |

| Voltage - I/O           | 2.50V, 3.30V                                                         |

| Voltage - Core          | 1.20V                                                                |

| Operating Temperature   | -40°C ~ 85°C (TA)                                                    |

| Mounting Type           | Surface Mount                                                        |

| Package / Case          | 182-LFBGA, CSPBGA                                                    |

| Supplier Device Package | 182-CSPBGA (12x12)                                                   |

| Purchase URL            | https://www.e-xfl.com/product-detail/analog-devices/adbf534wbbcz4a03 |

|                         |                                                                      |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### TABLE OF CONTENTS

| F | eatures                                | . 1 |

|---|----------------------------------------|-----|

| N | 1emory                                 | . 1 |

| P | eripherals                             | . 1 |

| G | General Description                    | . 3 |

|   | Portable Low Power Architecture        | . 3 |

|   | System Integration                     | . 3 |

|   | Blackfin Processor Peripherals         | . 3 |

|   | Blackfin Processor Core                | . 4 |

|   | Memory Architecture                    | . 5 |

|   | DMA Controllers                        | . 8 |

|   | Real-Time Clock                        | . 9 |

|   | Watchdog Timer                         | . 9 |

|   | Timers                                 | . 9 |

|   | Serial Ports (SPORTs)                  | 10  |

|   | Serial Peripheral Interface (SPI) Port |     |

|   | UART Ports                             | 10  |

|   | Controller Area Network (CAN)          | 11  |

|   | TWI Controller Interface               | 11  |

|   | 10/100 Ethernet MAC                    | 11  |

|   | Ports                                  | 12  |

|   | Parallel Peripheral Interface (PPI)    | 12  |

|   | Dynamic Power Management               | 13  |

|   | Voltage Regulation                     | 14  |

|   | Clock Signals                          | 15  |

|   |                                        |     |

### Booting Modes ..... 16 Instruction Set Description ...... 17 Development Tools ..... 17 Additional Information ...... 18 Related Signal Chains ..... 18 Operating Conditions ..... 23 Absolute Maximum Ratings ...... 29 Timing Specifications ...... 30 Output Drive Currents ...... 50 Thermal Characteristics ...... 56 182-Ball CSP\_BGA Ball Assignment ..... 57 208-Ball CSP\_BGA Ball Assignment ...... 60

### **REVISION HISTORY**

| 2/14—Rev. I to Rev. J                                                           |    |

|---------------------------------------------------------------------------------|----|

| Corrected typographical error from Three 16-bit MACs to 16-bit MACs in Features |    |

| Updated Development Tools                                                       | 17 |

| Added t <sub>HDRE</sub> parameter to Serial Port Timing                         | 38 |

| Added footnotes in Serial Port Timing                                           | 38 |

#### Core Event Controller (CEC)

The CEC supports nine general-purpose interrupts (IVG15–7), in addition to the dedicated interrupt and exception events. Of these general-purpose interrupts, the two lowest priority interrupts (IVG15–14) are recommended to be reserved for software interrupt handlers, leaving seven prioritized interrupt inputs to support the peripherals of the Blackfin processor. Table 2 describes the inputs to the CEC, identifies their names in the event vector table (EVT), and lists their priorities.

#### Table 2. Core Event Controller (CEC)

| Priority       |                              |           |

|----------------|------------------------------|-----------|

| (0 Is Highest) | Event Class                  | EVT Entry |

| 0              | Emulation/Test Control       | EMU       |

| 1              | Reset                        | RST       |

| 2              | Nonmaskable Interrupt        | NMI       |

| 3              | Exception                    | EVX       |

| 4              | Reserved                     | —         |

| 5              | Hardware Error               | IVHW      |

| 6              | Core Timer                   | IVTMR     |

| 7              | General-Purpose Interrupt 7  | IVG7      |

| 8              | General-Purpose Interrupt 8  | IVG8      |

| 9              | General-Purpose Interrupt 9  | IVG9      |

| 10             | General-Purpose Interrupt 10 | IVG10     |

| 11             | General-Purpose Interrupt 11 | IVG11     |

| 12             | General-Purpose Interrupt 12 | IVG12     |

| 13             | General-Purpose Interrupt 13 | IVG13     |

| 14             | General-Purpose Interrupt 14 | IVG14     |

| 15             | General-Purpose Interrupt 15 | IVG15     |

#### System Interrupt Controller (SIC)

The system interrupt controller provides the mapping and routing of events from the many peripheral interrupt sources to the prioritized general-purpose interrupt inputs of the CEC. Although the processor provides a default mapping, the user can alter the mappings and priorities of interrupt events by writing the appropriate values into the interrupt assignment registers (IAR). Table 3 describes the inputs into the SIC and the default mappings into the CEC. Table 3. System Interrupt Controller (SIC)

| Peripheral Interrupt Event                                     | Default<br>Mapping | Peripheral<br>Interrupt ID |

|----------------------------------------------------------------|--------------------|----------------------------|

| PLL Wakeup                                                     | IVG7               | 0                          |

| DMA Error (Generic)                                            | IVG7               | 1                          |

| DMAR0 Block Interrupt                                          | IVG7               | 1                          |

| DMAR1 Block Interrupt                                          | IVG7               | 1                          |

| DMAR0 Overflow Error                                           | IVG7               | 1                          |

| DMAR1 Overflow Error                                           | IVG7               | 1                          |

| CAN Error                                                      | IVG7               | 2                          |

| Ethernet Error (ADSP-BF536 and ADSP-BF537 only)                | IVG7               | 2                          |

| SPORT 0 Error                                                  | IVG7               | 2                          |

| SPORT 1 Error                                                  | IVG7               | 2                          |

| PPI Error                                                      | IVG7               | 2                          |

| SPI Error                                                      | IVG7               | 2                          |

| UART0 Error                                                    | IVG7               | 2                          |

| UART1 Error                                                    | IVG7               | 2                          |

| Real-Time Clock                                                | IVG8               | 3                          |

| DMA Channel 0 (PPI)                                            | IVG8               | 4                          |

| DMA Channel 3 (SPORT 0 Rx)                                     | IVG9               | 5                          |

| DMA Channel 4 (SPORT 0 Tx)                                     | IVG9               | 6                          |

| DMA Channel 5 (SPORT 1 Rx)                                     | IVG9               | 7                          |

| DMA Channel 6 (SPORT 1 Tx)                                     | IVG9               | 8                          |

| TWI                                                            | IVG10              | 9                          |

| DMA Channel 7 (SPI)                                            | IVG10              | 10                         |

| DMA Channel 8 (UARTO Rx)                                       | IVG10              | 11                         |

| DMA Channel 9 (UART0 Tx)                                       | IVG10              | 12                         |

| DMA Channel 10 (UART1 Rx)                                      | IVG10              | 13                         |

| DMA Channel 11 (UART1 Tx)                                      | IVG10              | 14                         |

| CAN Rx                                                         | IVG10              | 15                         |

| CAN Tx                                                         | IVG11              | 16                         |

| DMA Channel 1 (Ethernet Rx,<br>ADSP-BF536 and ADSP-BF537 only) | IVG11              | 17                         |

| Port H Interrupt A                                             | IVG11              | 17                         |

| DMA Channel 2 (Ethernet Tx,<br>ADSP-BF536 and ADSP-BF537 only) | IVG11              | 18                         |

| Port H Interrupt B                                             | IVG11              | 18                         |

| Timer 0                                                        | IVG12              | 19                         |

| Timer 1                                                        | IVG12              | 20                         |

| Timer 2                                                        | IVG12              | 21                         |

| Timer 3                                                        | IVG12              | 22                         |

| Timer 4                                                        | IVG12              | 23                         |

| Timer 5                                                        | IVG12              | 24                         |

| Timer 6                                                        | IVG12              | 25                         |

| Timer 7                                                        | IVG12              | 26                         |

| Port F, G Interrupt A                                          | IVG12              | 27                         |

| Port G Interrupt B                                             | IVG12              | 28                         |

In addition to the dedicated peripheral DMA channels, there are two memory DMA channels provided for transfers between the various memories of the processor system. This enables transfers of blocks of data between any of the memories—including external SDRAM, ROM, SRAM, and flash memory—with minimal processor intervention. Memory DMA transfers can be controlled by a very flexible descriptor-based methodology or by a standard register-based autobuffer mechanism.

The ADSP-BF534/ADSP-BF536/ADSP-BF537 processors also have an external DMA controller capability via dual external DMA request pins when used in conjunction with the external bus interface unit (EBIU). This functionality can be used when a high speed interface is required for external FIFOs and high bandwidth communications peripherals such as USB 2.0. It allows control of the number of data transfers for memDMA. The number of transfers per edge is programmable. This feature can be programmed to allow memDMA to have an increased priority on the external bus relative to the core.

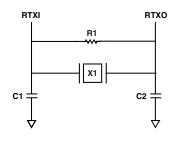

### **REAL-TIME CLOCK**

The real-time clock (RTC) provides a robust set of digital watch features, including current time, stopwatch, and alarm. The RTC is clocked by a 32.768 kHz crystal external to the processor. The RTC peripheral has dedicated power supply pins so that it can remain powered up and clocked even when the rest of the processor is in a low power state. The RTC provides several programmable interrupt options, including interrupt per second, minute, hour, or day clock ticks, interrupt on programmable stopwatch countdown, or interrupt at a programmed alarm time.

The 32.768 kHz input clock frequency is divided down to a 1 Hz signal by a prescaler. The counter function of the timer consists of four counters: a 60-second counter, a 60-minute counter, a 24-hour counter, and an 32,768-day counter.

When enabled, the alarm function generates an interrupt when the output of the timer matches the programmed value in the alarm control register. There are two alarms: The first alarm is for a time of day, while the second alarm is for a day and time of that day.

The stopwatch function counts down from a programmed value, with one-second resolution. When the stopwatch is enabled and the counter underflows, an interrupt is generated.

Like the other peripherals, the RTC can wake up the processor from sleep mode upon generation of any RTC wake-up event. Additionally, an RTC wake-up event can wake up the processor from deep sleep mode, and wake up the on-chip internal voltage regulator from the hibernate operating mode.

Connect RTC pins RTXI and RTXO with external components as shown in Figure 4.

### WATCHDOG TIMER

The ADSP-BF534/ADSP-BF536/ADSP-BF537 processors include a 32-bit timer that can be used to implement a software watchdog function. A software watchdog can improve system availability by forcing the processor to a known state through generation of a system reset, nonmaskable interrupt (NMI), or

SUGGESTED COMPONENTS: X1 = ECLIPTEK EC38J (THROUGH-HOLE PACKAGE) OR EPSON MC405 12 pF LOAD (SURFACE-MOUNT PACKAGE) C1 = 22 pF C2 = 22 pF R1 = 10 MΩ NOTE: C1 AND C2 ARE SPECIFIC TO CRYSTAL SPECIFIED FOR X1. CONTACT CRYSTAL MANUFACTURER FOR DETAILS. C1 AND C2 SPECIFICATIONS ASSUME BOARD TRACE CAPACITANCE OF 3 pF.

general-purpose interrupt, if the timer expires before being reset by software. The programmer initializes the count value of the timer, enables the appropriate interrupt, then enables the timer. Thereafter, the software must reload the counter before it counts to zero from the programmed value. This protects the system from remaining in an unknown state where software, which would normally reset the timer, has stopped running due to an external noise condition or software error.

If configured to generate a hardware reset, the watchdog timer resets both the core and the processor peripherals. After a reset, software can determine if the watchdog was the source of the hardware reset by interrogating a status bit in the watchdog timer control register.

The timer is clocked by the system clock (SCLK), at a maximum frequency of  $f_{SCLK}$ .

#### TIMERS

There are nine general-purpose programmable timer units in the processor. Eight timers have an external pin that can be configured either as a pulse-width modulator (PWM) or timer output, as an input to clock the timer, or as a mechanism for measuring pulse widths and periods of external events. These timers can be synchronized to an external clock input to the several other associated PF pins, to an external clock input to the PPI\_CLK input pin, or to the internal SCLK.

The timer units can be used in conjunction with the two UARTs and the CAN controller to measure the width of the pulses in the data stream to provide a software auto-baud detect function for the respective serial channels.

The timers can generate interrupts to the processor core providing periodic events for synchronization, either to the system clock or to a count of external signals.

In addition to the eight general-purpose programmable timers, a ninth timer is also provided. This extra timer is clocked by the internal processor clock and is typically used as a system tick clock for generating periodic interrupts in an operating system.

In conjunction with the general-purpose timer functions, autobaud detection is supported.

The capabilities of the UARTs are further extended with support for the infrared data association (IrDA<sup>®</sup>) serial infrared physical layer link specification (SIR) protocol.

### **CONTROLLER AREA NETWORK (CAN)**

The ADSP-BF534/ADSP-BF536/ADSP-BF537 processors offer a CAN controller that is a communication controller implementing the CAN 2.0B (active) protocol. This protocol is an asynchronous communications protocol used in both industrial and automotive control systems. The CAN protocol is wellsuited for control applications due to its capability to communicate reliably over a network, since the protocol incorporates CRC checking message error tracking, and fault node confinement.

The CAN controller offers the following features:

- 32 mailboxes (eight receive only, eight transmit only, 16 configurable for receive or transmit).

- Dedicated acceptance masks for each mailbox.

- Additional data filtering on first two bytes.

- Support for both the standard (11-bit) and extended (29-bit) identifier (ID) message formats.

- Support for remote frames.

- Active or passive network support.

- CAN wake-up from hibernation mode (lowest static power consumption mode).

- Interrupts, including: Tx complete, Rx complete, error, global.

The electrical characteristics of each network connection are very demanding so the CAN interface is typically divided into two parts: a controller and a transceiver. This allows a single controller to support different drivers and CAN networks. The CAN module represents only the controller part of the interface. The controller interface supports connection to 3.3 V highspeed, fault-tolerant, single-wire transceivers.

#### **TWI CONTROLLER INTERFACE**

The ADSP-BF534/ADSP-BF536/ADSP-BF537 processors include a 2-wire interface (TWI) module for providing a simple exchange method of control data between multiple devices. The TWI is compatible with the widely used  $I^2C^{\otimes}$  bus standard. The TWI module offers the capabilities of simultaneous master and slave operation, support for both 7-bit addressing and multimedia data arbitration. The TWI interface utilizes two pins for transferring clock (SCL) and data (SDA) and supports the protocol at speeds up to 400 kbps. The TWI interface pins are compatible with 5 V logic levels.

Additionally, the processor's TWI module is fully compatible with serial camera control bus (SCCB) functionality for easier control of various CMOS camera sensor devices.

#### 10/100 ETHERNET MAC

The ADSP-BF536 and ADSP-BF537 processors offer the capability to directly connect to a network by way of an embedded fast Ethernet Media Access Controller (MAC) that supports both 10-BaseT (10 Mbps) and 100-BaseT (100 Mbps) operation. The 10/100 Ethernet MAC peripheral is fully compliant to the IEEE 802.3-2002 standard, and it provides programmable features designed to minimize supervision, bus use, or message processing by the rest of the processor system.

Some standard features are

- Support of MII and RMII protocols for external PHYs.

- Full duplex and half duplex modes.

- Data framing and encapsulation: generation and detection of preamble, length padding, and FCS.

- Media access management (in half-duplex operation): collision and contention handling, including control of retransmission of collision frames and of back-off timing.

- Flow control (in full-duplex operation): generation and detection of PAUSE frames.

- Station management: generation of MDC/MDIO frames for read-write access to PHY registers.

- SCLK operating range down to 25 MHz (active and sleep operating modes).

- Internal loopback from Tx to Rx.

Some advanced features are

- Buffered crystal output to external PHY for support of a single crystal system.

- Automatic checksum computation of IP header and IP payload fields of Rx frames.

- Independent 32-bit descriptor-driven Rx and Tx DMA channels.

- Frame status delivery to memory via DMA, including frame completion semaphores, for efficient buffer queue management in software.

- Tx DMA support for separate descriptors for MAC header and payload to eliminate buffer copy operations.

- Convenient frame alignment modes support even 32-bit alignment of encapsulated Rx or Tx IP packet data in memory after the 14-byte MAC header.

- Programmable Ethernet event interrupt supports any combination of

- Any selected Rx or Tx frame status conditions.

- PHY interrupt condition.

- Wake-up frame detected.

- Any selected MAC management counter(s) at half-full.

- DMA descriptor error.

- 47 MAC management statistics counters with selectable clear-on-read behavior and programmable interrupts on half maximum value.

- Programmable Rx address filters, including a 64-bit address hash table for multicast and/or unicast frames, and programmable filter modes for broadcast, multicast, unicast, control, and damaged frames.

- Advanced power management supporting unattended transfer of Rx and Tx frames and status to/from external memory via DMA during low power sleep mode.

- System wake-up from sleep operating mode upon magic packet or any of four user-definable wake-up frame filters.

- Support for 802.3Q tagged VLAN frames.

- Programmable MDC clock rate and preamble suppression.

- In RMII operation, 7 unused pins can be configured as GPIO pins for other purposes.

### PORTS

The ADSP-BF534/ADSP-BF536/ADSP-BF537 processors group the many peripheral signals to four ports—Port F, Port G, Port H, and Port J. Most of the associated pins are shared by multiple signals. The ports function as multiplexer controls. Eight of the pins (Port F7–0) offer high source/high sink current capabilities.

### General-Purpose I/O (GPIO)

The processors have 48 bidirectional, general-purpose I/O (GPIO) pins allocated across three separate GPIO modules— PORTFIO, PORTGIO, and PORTHIO, associated with Port F, Port G, and Port H, respectively. Port J does not provide GPIO functionality. Each GPIO-capable pin shares functionality with other processor peripherals via a multiplexing scheme; however, the GPIO functionality is the default state of the device upon power-up. Neither GPIO output or input drivers are active by default. Each general-purpose port pin can be individually controlled by manipulation of the port control, status, and interrupt registers:

- GPIO direction control register Specifies the direction of each individual GPIO pin as input or output.

- GPIO control and status registers The processors employ a "write one to modify" mechanism that allows any combination of individual GPIO pins to be modified in a single instruction, without affecting the level of any other GPIO pins. Four control registers are provided. One register is written in order to set pin values, one register is written in order to clear pin values, one register is written in order to toggle pin values, and one register is written in order to specify a pin value. Reading the GPIO status register allows software to interrogate the sense of the pins.

- GPIO interrupt mask registers The two GPIO interrupt mask registers allow each individual GPIO pin to function as an interrupt to the processor. Similar to the two GPIO control registers that are used to set and clear individual pin values, one GPIO interrupt mask register sets bits to enable interrupt function, and the other GPIO interrupt mask register clears bits to disable interrupt function.

GPIO pins defined as inputs can be configured to generate hardware interrupts, while output pins can be triggered by software interrupts.

• GPIO interrupt sensitivity registers – The two GPIO interrupt sensitivity registers specify whether individual pins are level- or edge-sensitive and specify—if edge-sensitive whether just the rising edge or both the rising and falling edges of the signal are significant. One register selects the type of sensitivity, and one register selects which edges are significant for edge-sensitivity.

### PARALLEL PERIPHERAL INTERFACE (PPI)

The processor provides a parallel peripheral interface (PPI) that can connect directly to parallel ADC and DAC converters, video encoders and decoders, and other general-purpose peripherals. The PPI consists of a dedicated input clock pin, up to three frame synchronization pins, and up to 16 data pins. The input clock supports parallel data rates up to half the system clock rate and the synchronization signals can be configured as either inputs or outputs.

The PPI supports a variety of general-purpose and ITU-R 656 modes of operation. In general-purpose mode, the PPI provides half-duplex, bidirectional data transfer with up to 16 bits of data. Up to three frame synchronization signals are also provided. In ITU-R 656 mode, the PPI provides half-duplex bidirectional transfer of 8- or 10-bit video data. Additionally, on-chip decode of embedded start-of-line (SOL) and start-of-field (SOF) preamble packets is supported.

### **General-Purpose Mode Descriptions**

The general-purpose modes of the PPI are intended to suit a wide variety of data capture and transmission applications. Three distinct submodes are supported:

- 1. Input mode Frame syncs and data are inputs into the PPI.

- 2. Frame capture mode Frame syncs are outputs from the PPI, but data are inputs.

- 3. Output mode Frame syncs and data are outputs from the PPI.

### Input Mode

Input mode is intended for ADC applications, as well as video communication with hardware signaling. In its simplest form, PPI\_FS1 is an external frame sync input that controls when to read data. The PPI\_DELAY MMR allows for a delay (in PPI\_ CLK cycles) between reception of this frame sync and the initiation of data reads. The number of input data samples is user programmable and defined by the contents of the PPI\_COUNT register. The PPI supports 8-bit and 10-bit through 16-bit data, programmable in the PPI\_CONTROL register.

#### Frame Capture Mode

Frame capture mode allows the video source(s) to act as a slave (for frame capture for example). The ADSP-BF534/ ADSP-BF536/ADSP-BF537 processors control when to read from the video source(s). PPI\_FS1 is an HSYNC output and PPI\_FS2 is a VSYNC output.

suite to emulate the on-board processor in-circuit. This permits the customer to download, execute, and debug programs for the EZ-KIT Lite system. It also supports in-circuit programming of the on-board Flash device to store user-specific boot code, enabling standalone operation. With the full version of Cross-Core Embedded Studio or VisualDSP++ installed (sold separately), engineers can develop software for supported EZ-KITs or any custom system utilizing supported Analog Devices processors.

#### Software Add-Ins for CrossCore Embedded Studio

Analog Devices offers software add-ins which seamlessly integrate with CrossCore Embedded Studio to extend its capabilities and reduce development time. Add-ins include board support packages for evaluation hardware, various middleware packages, and algorithmic modules. Documentation, help, configuration dialogs, and coding examples present in these add-ins are viewable through the CrossCore Embedded Studio IDE once the add-in is installed.

#### **Board Support Packages for Evaluation Hardware**

Software support for the EZ-KIT Lite evaluation boards and EZ-Extender daughter cards is provided by software add-ins called Board Support Packages (BSPs). The BSPs contain the required drivers, pertinent release notes, and select example code for the given evaluation hardware. A download link for a specific BSP is located on the web page for the associated EZ-KIT or EZ-Extender product. The link is found in the *Product Download* area of the product web page.

#### **Middleware Packages**

Analog Devices separately offers middleware add-ins such as real time operating systems, file systems, USB stacks, and TCP/IP stacks. For more information see the following web pages:

- www.analog.com/ucos3

- www.analog.com/ucfs

- www.analog.com/ucusbd

- www.analog.com/lwip

#### **Algorithmic Modules**

To speed development, Analog Devices offers add-ins that perform popular audio and video processing algorithms. These are available for use with both CrossCore Embedded Studio and VisualDSP++. For more information visit www.analog.com and search on "Blackfin software modules" or "SHARC software modules".

#### Designing an Emulator-Compatible DSP Board (Target)

For embedded system test and debug, Analog Devices provides a family of emulators. On each JTAG DSP, Analog Devices supplies an IEEE 1149.1 JTAG Test Access Port (TAP). In-circuit emulation is facilitated by use of this JTAG interface. The emulator accesses the processor's internal features via the processor's TAP, allowing the developer to load code, set breakpoints, and view variables, memory, and registers. The processor must be halted to send data and commands, but once an operation is completed by the emulator, the DSP system is set to run at full speed with no impact on system timing. The emulators require the target board to include a header that supports connection of the DSP's JTAG port to the emulator.

For details on target board design issues including mechanical layout, single processor connections, signal buffering, signal termination, and emulator pod logic, see the Engineer-to-Engineer Note *"Analog Devices JTAG Emulation Technical Reference"* (EE-68) on the Analog Devices website (www.analog.com)—use site search on "EE-68." This document is updated regularly to keep pace with improvements to emulator support.

#### **ADDITIONAL INFORMATION**

The following publications that describe the ADSP-BF534/ ADSP-BF536/ADSP-BF537 processors (and related processors) can be ordered from any Analog Devices sales office or accessed electronically on our website:

- Getting Started with Blackfin Processors

- ADSP-BF537 Blackfin Processor Hardware Reference

- ADSP-BF53x/ADSP-BF56x Blackfin Processor Programming Reference

- ADSP-BF534/ADSP-BF536/ADSP-BF537 Blackfin Processor Anomaly List

#### **RELATED SIGNAL CHAINS**

A *signal chain* is a series of signal-conditioning electronic components that receive input (data acquired from sampling either real-time phenomena or from stored data) in tandem, with the output of one portion of the chain supplying input to the next. Signal chains are often used in signal processing applications to gather and process data or to apply system controls based on analysis of real-time phenomena. For more information about this term and related topics, see the "signal chain" entry in Wikipedia or the Glossary of EE Terms on the Analog Devices website.

Analog Devices eases signal processing system development by providing signal processing components that are designed to work together well. A tool for viewing relationships between specific applications and related components is available on the www.analog.com website.

The Application Signal Chains page in the Circuits from the Lab<sup>™</sup> site (http://www.analog.com/signalchains) provides:

- Graphical circuit block diagram presentation of signal chains for a variety of circuit types and applications

- Drill down links for components in each chain to selection guides and application information

- Reference designs applying best practice design techniques

|                                            |                                                     |                                                                                                                                |     | 300 MHz | /400 MHz <sup>1</sup>                                       | 500 l | MHz/533 | MHz/600 MHz <sup>2</sup>                                    |      |

|--------------------------------------------|-----------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|-----|---------|-------------------------------------------------------------|-------|---------|-------------------------------------------------------------|------|

| Parameter                                  |                                                     | Test Conditions                                                                                                                | Min | Тур     | Мах                                                         | Min   | Тур     | Max                                                         | Unit |

| C <sub>IN</sub>                            | Input<br>Capacitance <sup>13, 14</sup>              | $f_{IN} = 1 \text{ MHz},$<br>$T_{AMBIENT} = 25^{\circ}\text{C},$<br>$V_{IN} = 2.5 \text{ V}$                                   |     |         | 8                                                           |       |         | 8                                                           | pF   |

| I <sub>DD-IDLE</sub>                       | V <sub>DDINT</sub> Current in<br>Idle               | $V_{DDINT} = 1.0 V,$<br>$f_{CCLK} = 50 MHz,$<br>$T_{J} = 25^{\circ}C, ASF = 0.43$                                              |     | 14      |                                                             |       | 24      |                                                             | mA   |

| I <sub>DD-TYP</sub>                        | V <sub>DDINT</sub> Current                          | $V_{DDINT} = 1.14 V,$<br>$f_{CCLK} = 300 MHz,$<br>$T_J = 25^{\circ}C, ASF = 1.00$                                              |     | 100     |                                                             |       | 113     |                                                             | mA   |

| I <sub>DD-TYP</sub>                        | V <sub>DDINT</sub> Current                          | $V_{DDINT} = 1.14 V,$<br>$f_{CCLK} = 400 MHz,$<br>$T_J = 25^{\circ}C, ASF = 1.00$                                              |     | 125     |                                                             |       | 138     |                                                             | mA   |

| I <sub>DDDEEPSLEEP</sub> <sup>15</sup>     | V <sub>DDINT</sub> Current in<br>Deep Sleep<br>Mode | $V_{DDINT} = 1.0 V,$<br>$f_{CCLK} = 0 MHz,$<br>$T_J = 25^{\circ}C, ASF = 0.00$                                                 |     | 6       |                                                             |       | 16      |                                                             | mA   |

| I <sub>DDSLEEP</sub>                       | V <sub>DDINT</sub> Current in Sleep Mode            | $\begin{split} V_{DDINT} &= 1.0 \text{ V}, \\ f_{SCLK} &= 25 \text{ MHz}, \\ T_J &= 25^{\circ}\text{C} \end{split}$            |     | 9.5     |                                                             |       | 19.5    |                                                             | mA   |

| I <sub>DD-TYP</sub>                        | V <sub>DDINT</sub> Current                          | $V_{DDINT} = 1.20 V,$<br>$f_{CCLK} = 533 MHz,$<br>$T_J = 25^{\circ}C, ASF = 1.00$                                              |     |         |                                                             |       | 185     |                                                             | mA   |

| I <sub>DD-TYP</sub>                        | V <sub>DDINT</sub> Current                          | $V_{DDINT} = 1.30 V,$<br>$f_{CCLK} = 600 MHz,$<br>$T_J = 25^{\circ}C, ASF = 1.00$                                              |     |         |                                                             |       | 227     |                                                             | mA   |

| I <sub>DDHIBERNATE</sub> <sup>15, 16</sup> | V <sub>DDEXT</sub> Current in<br>Hibernate State    | $V_{DDEXT} = 3.60 V,$<br>CLKIN=0 MHz,<br>T <sub>J</sub> = maximum, with<br>voltage regulator off<br>(V <sub>DDINT</sub> = 0 V) |     | 50      | 100                                                         |       | 50      | 100                                                         | μA   |

| I <sub>DDRTC</sub>                         | V <sub>DDRTC</sub> Current                          | $V_{DDRTC} = 3.3 V, T_J = 25^{\circ}C$                                                                                         |     | 20      |                                                             |       | 20      |                                                             | μA   |

| I <sub>DDDEEPSLEEP</sub> <sup>15</sup>     | V <sub>DDINT</sub> Current in<br>Deep Sleep<br>Mode | $f_{CCLK} = 0 \text{ MHz},$<br>$f_{SCLK} = 0 \text{ MHz}$                                                                      |     |         | Table 16                                                    |       |         | Table 15                                                    | mA   |

| I <sub>DDSLEEP</sub> 15, 17                | V <sub>DDINT</sub> Current in Sleep Mode            | $\label{eq:f_cclk} \begin{split} f_{\text{CCLK}} &= 0 \text{ MHz}, \\ f_{\text{SCLK}} &> 0 \text{ MHz} \end{split}$            |     |         | $I_{DDDEEPSLEEP} + (0.14 \times V_{DDINT} \times f_{SCLK})$ |       |         | $I_{DDDEEPSLEEP} + (0.14 \times V_{DDINT} \times f_{SCLK})$ | mA   |

| I <sub>DDINT</sub> <sup>18</sup>           | V <sub>DDINT</sub> Current                          | $\label{eq:f_cclk} \begin{split} f_{CCLK} &> 0 \text{ MHz}, \\ f_{SCLK} &> 0 \text{ MHz} \end{split}$                          |     |         | I <sub>DDSLEEP</sub> +<br>(Table 18 × ASF)                  |       |         | $I_{DDSLEEP}$ + (Table 18 × ASF)                            | mA   |

<sup>1</sup> Applies to all 300 MHz and 400 MHz speed grade models. See Ordering Guide on Page 67.

<sup>2</sup> Applies to all 500 MHz, 533 MHz, and 600 MHz speed grade models. See Ordering Guide on Page 67.

<sup>3</sup> Applies to all output and bidirectional pins except port F pins, port G pins, and port H pins.

<sup>4</sup> Applies to port F pins PF7–0.

<sup>5</sup> Applies to port F pins PF15–8, all port G pins, and all port H pins.

<sup>6</sup>Maximum combined current for Port F7-0.

<sup>7</sup> Maximum total current for all port F, port G, and port H pins.

<sup>8</sup> Applies to all input pins except PJ4.

<sup>9</sup> Applies to input pin PJ4 only.

<sup>10</sup>Applies to JTAG input pins (TCK, TDI, TMS, TRST).

<sup>11</sup>Applies to three-statable pins.

<sup>12</sup>Applies to bidirectional pins PJ2 and PJ3.

<sup>13</sup>Applies to all signal pins.

<sup>14</sup>Guaranteed, but not tested.

<sup>15</sup>See the ADSP-BF537 Blackfin Processor Hardware Reference Manual for definition of sleep, deep sleep, and hibernate operating modes.

$^{16}\mathrm{CLKIN}$  must be tied to  $\mathrm{V}_{\mathrm{DDEXT}}$  or GND during hibernate.

$^{17}\mbox{In}$  the equations, the  $f_{\mbox{SCLK}}$  parameter is the system clock in MHz.

$^{18}\text{See Table 17}$  for the list of  $I_{\text{DDINT}}$  power vectors covered.

#### Table 17. Activity Scaling Factors

| I <sub>DDINT</sub> Power Vector <sup>1</sup> | Activity Scaling Factor (ASF) <sup>2</sup> |

|----------------------------------------------|--------------------------------------------|

| I <sub>DD-PEAK</sub>                         | 1.33                                       |

| I <sub>DD-HIGH</sub>                         | 1.29                                       |

| I <sub>DD-TYP</sub>                          | 1.00                                       |

| I <sub>DD-APP</sub>                          | 0.88                                       |

| I <sub>DD-NOP</sub>                          | 0.72                                       |

| I <sub>DD-IDLE</sub>                         | 0.43                                       |

<sup>1</sup> See EE-297 for power vector definitions.

<sup>2</sup> All ASF values determined using a 10:1 CCLK:SCLK ratio.

#### Table 18. Dynamic Current (mA, with ASF = 1.0)<sup>1</sup>

|                    |        | Voltage (V <sub>DDINT</sub> ) |        |        |        |        |        |        |        |        |        |        |         |        |

|--------------------|--------|-------------------------------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|---------|--------|

| Frequency<br>(MHz) | 0.80 V | 0.85 V                        | 0.90 V | 0.95 V | 1.00 V | 1.05 V | 1.10 V | 1.15 V | 1.20 V | 1.25 V | 1.30 V | 1.32 V | 1.375 V | 1.43 V |

| 50                 | 11.0   | 13.7                          | 19.13  | 18.2   | 18.67  | 19.13  | 19.6   | 21.2   | 24.1   | 25.5   | 28.5   | 28.6   | 28.85   | 29.2   |

| 100                | 27.9   | 22.7                          | 30.8   | 28.4   | 29.3   | 30.8   | 32.9   | 35.3   | 37.8   | 40.6   | 43.5   | 43.7   | 44.1    | 45.8   |

| 200                | 36.9   | 42.6                          | 55.0   | 49.2   | 51.5   | 55.0   | 58.3   | 62.9   | 67.0   | 69.7   | 73.0   | 74.0   | 75.7    | 80.7   |

| 300                | N/A    | 61.5                          | 79.2   | 70.4   | 74.6   | 79.2   | 84.4   | 90.7   | 94.3   | 99.1   | 103.9  | 105.5  | 108.0   | 113.4  |

| 400                | N/A    | N/A                           | N/A    | 92.4   | 97.2   | 104.3  | 109.8  | 116.5  | 121.9  | 128.0  | 134.6  | 136.6  | 139.8   | 145.1  |

| 500                | N/A    | N/A                           | N/A    | N/A    | N/A    | N/A    | N/A    | 142.3  | 149.3  | 157.5  | 164.7  | 166.7  | 169.8   | 176.9  |

| 533                | N/A    | N/A                           | N/A    | N/A    | N/A    | N/A    | N/A    | N/A    | 158.6  | 167.0  | 174.3  | 176.6  | 180.1   | 187.9  |

| 600                | N/A    | N/A                           | N/A    | N/A    | N/A    | N/A    | N/A    | N/A    | N/A    | N/A    | 193.7  | 196.5  | 200.7   | 210.0  |

<sup>1</sup> The values are not guaranteed as stand-alone maximum specifications, they must be combined with static current per the equations of Electrical Characteristics on Page 25.

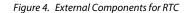

#### Asynchronous Memory Read Cycle Timing

#### Table 24. Asynchronous Memory Read Cycle Timing

| Parameter          |                                        | Min | Max | Unit |

|--------------------|----------------------------------------|-----|-----|------|

| Timing Requ        | uirements                              |     |     |      |

| t <sub>SDAT</sub>  | DATA15-0 Setup Before CLKOUT           | 2.1 |     | ns   |

| t <sub>HDAT</sub>  | DATA15–0 Hold After CLKOUT             | 0.8 |     | ns   |

| t <sub>SARDY</sub> | ARDY Setup Before CLKOUT               | 4.0 |     | ns   |

| t <sub>HARDY</sub> | ARDY Hold After CLKOUT                 | 0.0 |     | ns   |

| Switching C        | haracteristics                         |     |     |      |

| t <sub>DO</sub>    | Output Delay After CLKOUT <sup>1</sup> |     | 6.0 | ns   |

| t <sub>HO</sub>    | Output Hold After CLKOUT <sup>1</sup>  | 0.8 |     | ns   |

<sup>1</sup>Output pins include  $\overline{\text{AMS3-0}}$ ,  $\overline{\text{ABE1-0}}$ , ADDR19-1,  $\overline{\text{AOE}}$ ,  $\overline{\text{ARE}}$ .

Figure 11. Asynchronous Memory Read Cycle Timing

#### **External Port Bus Request and Grant Cycle Timing**

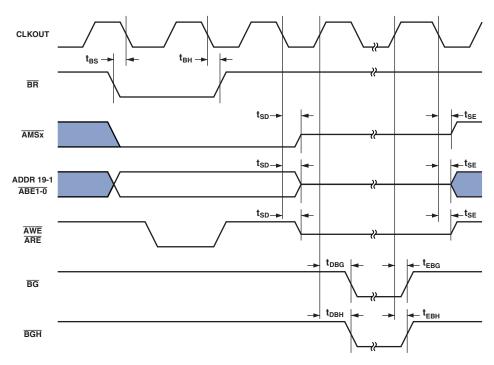

Table 26 and Figure 13 describe external port bus request and bus grant operations.

#### Table 26. External Port Bus Request and Grant Cycle Timing

| Paramete         | r1,2                                             | Min | Мах | Unit |

|------------------|--------------------------------------------------|-----|-----|------|

| Timing Req       | uirements                                        |     |     |      |

| t <sub>BS</sub>  | BR Asserted to CLKOUT Low Setup                  | 4.6 |     | ns   |

| t <sub>BH</sub>  | CLKOUT Low to BR Deasserted Hold Time            | 0.0 |     | ns   |

| Switching        | Characteristics                                  |     |     |      |

| t <sub>SD</sub>  | CLKOUT Low to AMSx, Address, and ARE/AWE Disable |     | 4.5 | ns   |

| t <sub>se</sub>  | CLKOUT Low to AMSx, Address, and ARE/AWE Enable  |     | 4.5 | ns   |

| t <sub>DBG</sub> | CLKOUT High to BG Asserted Setup                 |     | 3.6 | ns   |

| t <sub>EBG</sub> | CLKOUT High to BG Deasserted Hold Time           |     | 3.6 | ns   |

| t <sub>DBH</sub> | CLKOUT High to BGH Asserted Setup                |     | 3.6 | ns   |

| t <sub>EBH</sub> | CLKOUT High to BGH Deasserted Hold Time          |     | 3.6 | ns   |

<sup>1</sup> These timing parameters are based on worst-case operating conditions.

<sup>2</sup> The pad loads for these timing parameters are 20 pF.

Figure 13. External Port Bus Request and Grant Cycle Timing

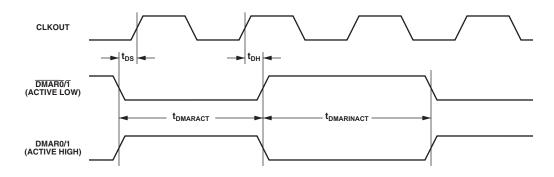

#### **External DMA Request Timing**

Table 28 and Figure 15 describe the external DMA requestoperations.

#### Table 28. External DMA Request Timing

| Parameter              |                                           | Min                    | Max | Unit |

|------------------------|-------------------------------------------|------------------------|-----|------|

| Timing Requir          | rements                                   |                        |     |      |

| t <sub>DS</sub>        | DMARx Asserted to CLKOUT High Setup       | 6.0                    |     | ns   |

| t <sub>DH</sub>        | CLKOUT High to DMARx Deasserted Hold Time | 0.0                    |     | ns   |

| t <sub>DMARACT</sub>   | DMARx Active Pulse Width                  | $1.0 \times t_{SCLK}$  |     | ns   |

| t <sub>DMARINACT</sub> | DMARx Inactive Pulse Width                | $1.75 \times t_{SCLK}$ |     | ns   |

Figure 15. External DMA Request Timing

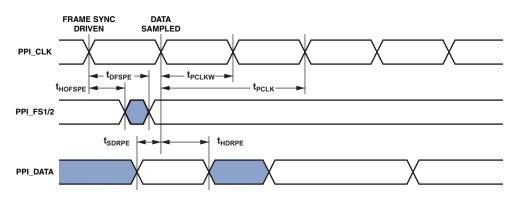

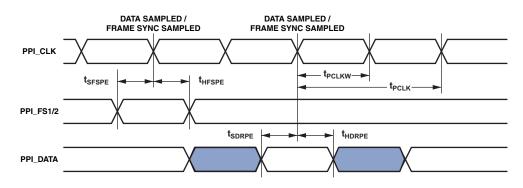

#### Parallel Peripheral Interface Timing

Table 29 and Figure 16 on Page 36, Figure 20 on Page 39, and Figure 23 on Page 41 describe parallel peripheral interface operations.

#### Table 29. Parallel Peripheral Interface Timing

| Parameter           |                                                  | Min  | Max | Unit |

|---------------------|--------------------------------------------------|------|-----|------|

| Timing Requ         | irements                                         |      |     |      |

| t <sub>PCLKW</sub>  | PPI_CLK Width <sup>1</sup>                       | 6.0  |     | ns   |

| t <sub>PCLK</sub>   | PPI_CLK Period <sup>1</sup>                      | 15.0 |     | ns   |

| Timing Requ         | irements—GP Input and Frame Capture Modes        |      |     |      |

| t <sub>SFSPE</sub>  | External Frame Sync Setup Before PPI_CLK         | 6.7  |     | ns   |

| t <sub>HFSPE</sub>  | External Frame Sync Hold After PPI_CLK           | 1.0  |     | ns   |

| t <sub>SDRPE</sub>  | Receive Data Setup Before PPI_CLK                | 3.5  |     | ns   |

| t <sub>HDRPE</sub>  | Receive Data Hold After PPI_CLK                  | 1.5  |     | ns   |

| Switching Cl        | haracteristics—GP Output and Frame Capture Modes |      |     |      |

| t <sub>DFSPE</sub>  | Internal Frame Sync Delay After PPI_CLK          |      | 8.0 | ns   |

| t <sub>HOFSPE</sub> | Internal Frame Sync Hold After PPI_CLK           | 1.7  |     | ns   |

| t <sub>DDTPE</sub>  | Transmit Data Delay After PPI_CLK                |      | 8.0 | ns   |

| t <sub>HDTPE</sub>  | Transmit Data Hold After PPI_CLK                 | 1.8  |     | ns   |

$^{1}$  PPI\_CLK frequency cannot exceed f<sub>SCLK</sub>/2.

Figure 16. PPI GP Rx Mode with Internal Frame Sync Timing

Figure 17. PPI GP Rx Mode with External Frame Sync Timing

#### Serial Port Timing

Table 30 through Table 33 on Page 41 and Figure 20 on Page 39 through Figure 23 on Page 41 describe serial port operations.

#### Table 30. Serial Ports-External Clock

| Parameter           |                                                                                  | Min                    | Max  | Unit |

|---------------------|----------------------------------------------------------------------------------|------------------------|------|------|

| Timing Requ         | irements                                                                         |                        |      |      |

| t <sub>SFSE</sub>   | TFSx/RFSx Setup Before TSCLKx/RSCLKx <sup>1</sup>                                | 3.0                    |      | ns   |

| t <sub>HFSE</sub>   | TFSx/RFSx Hold After TSCLKx/RSCLKx <sup>1</sup>                                  | 3.0                    |      | ns   |

| t <sub>SDRE</sub>   | Receive Data Setup Before RSCLKx <sup>1</sup>                                    | 3.0                    |      | ns   |

| t <sub>HDRE</sub>   | Receive Data Hold After RSCLKx <sup>1</sup>                                      | 3.0                    |      | ns   |

| t <sub>SCLKEW</sub> | TSCLKx/RSCLKx Width                                                              | 4.5                    |      | ns   |

| t <sub>SCLKE</sub>  | TSCLKx/RSCLKx Period                                                             | 15.0                   |      | ns   |

| t <sub>SUDTE</sub>  | Start-Up Delay From SPORT Enable To First External TFSx <sup>2</sup>             | $4.0 \times t_{SCLKE}$ |      | ns   |

| t <sub>SUDRE</sub>  | Start-Up Delay From SPORT Enable To First External RFSx <sup>2</sup>             | $4.0 \times t_{SCLKE}$ |      | ns   |

| Switching Ch        | paracteristics                                                                   |                        |      |      |

| t <sub>DFSE</sub>   | TFSx/RFSx Delay After TSCLKx/RSCLK (Internally Generated TFSx/RFSx) <sup>3</sup> |                        | 10.0 | ns   |

| t <sub>HOFSE</sub>  | TFSx/RFSx Hold After TSCLKx/RSCLK (Internally Generated TFSx/RFSx) <sup>2</sup>  | 0                      |      | ns   |

| t <sub>DDTE</sub>   | Transmit Data Delay After TSCLKx <sup>2</sup>                                    |                        | 10.0 | ns   |

| t <sub>HDTE</sub>   | Transmit Data Hold After TSCLKx <sup>2</sup>                                     | 0                      |      | ns   |

<sup>1</sup>Referenced to sample edge.

<sup>2</sup> Verified in design but untested. After being enabled, the serial port requires external clock pulses—before the first external frame sync edge—to initialize the serial port. <sup>3</sup> Referenced to drive edge.

#### Table 31. Serial Ports—Internal Clock

|                     |                                                                                   | 2.25 V | ≤ V <sub>DDEXT</sub> < 2.70 V<br>or             |        | $V \le V_{DDEXT} \le 3.60 V$ and    |      |

|---------------------|-----------------------------------------------------------------------------------|--------|-------------------------------------------------|--------|-------------------------------------|------|

|                     |                                                                                   | 0.80 V | $\leq$ V <sub>DDINT</sub> < 0.95 V <sup>1</sup> | 0.95 V | $\leq V_{DDINT} \leq 1.43 V^{2, 3}$ |      |

| Parameter           |                                                                                   | Min    | Мах                                             | Min    | Max                                 | Unit |

| Timing Re           | equirements                                                                       |        |                                                 |        |                                     |      |

| t <sub>SFSI</sub>   | TFSx/RFSx Setup Before TSCLKx/RSCLKx <sup>4</sup>                                 | 8.5    |                                                 | 8.0    |                                     | ns   |

| t <sub>HFSI</sub>   | TFSx/RFSx Hold After TSCLKx/RSCLKx <sup>4</sup>                                   | -1.5   |                                                 | -1.5   |                                     | ns   |

| t <sub>SDRI</sub>   | Receive Data Setup Before RSCLKx <sup>4</sup>                                     | 8.5    |                                                 | 8.0    |                                     | ns   |

| t <sub>HDRI</sub>   | Receive Data Hold After RSCLKx <sup>4</sup>                                       | -1.5   |                                                 | -1.5   |                                     | ns   |

| Switching           | Characteristics                                                                   |        |                                                 |        |                                     |      |

| t <sub>DFSI</sub>   | TFSx/RFSx Delay After TSCLKx/RSCLKx (Internally Generated TFSx/RFSx) <sup>5</sup> |        | 3.0                                             |        | 3.0                                 | ns   |

| t <sub>HOFSI</sub>  | TFSx/RFSx Hold After TSCLKx/RSCLKx (Internally Generated TFSx/RFSx) <sup>5</sup>  | -1.0   |                                                 | -1.0   |                                     | ns   |

| t <sub>DDTI</sub>   | Transmit Data Delay After TSCLKx⁵                                                 |        | 3.0                                             |        | 3.0                                 | ns   |

| t <sub>HDTI</sub>   | Transmit Data Hold After TSCLKx <sup>5</sup>                                      | -1.0   |                                                 | -1.0   |                                     | ns   |

| t <sub>SCLKIW</sub> | TSCLKx/RSCLKx Width                                                               | 4.5    |                                                 | 4.5    |                                     | ns   |

<sup>1</sup>Applies to all nonautomotive-grade devices when operated within either of these voltage ranges.

<sup>2</sup> Applies to all nonautomotive-grade devices when operated within these voltage ranges.

<sup>3</sup> All automotive-grade devices are within these specifications.

<sup>4</sup>Referenced to sample edge.

<sup>5</sup> Referenced to drive edge.

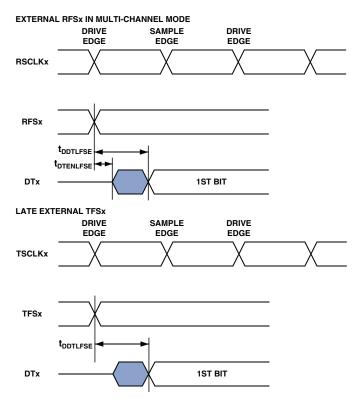

#### Table 33. External Late Frame Sync

| Parameter            |                                                                                     | Min | Мах  | Unit |

|----------------------|-------------------------------------------------------------------------------------|-----|------|------|

| Switching Ch         | aracteristics                                                                       |     |      |      |

| t <sub>DDTLFSE</sub> | Data Delay from Late External TFSx or External RFSx with MCMEN = 1, MFD = $0^{1,2}$ |     | 10.0 | ns   |

| t <sub>DTENLFS</sub> | Data Enable from Late FS or MCMEN = 1, MFD = $0^{1, 2}$                             | 0   |      | ns   |

$^{1}$  MCMEN = 1, TFSx enable and TFSx valid follow t<sub>DDTENFS</sub> and t<sub>DDTLFS</sub>.

$^{2}$  If external RFSx/TFSx setup to RSCLKx/TSCLKx > t<sub>SCLKE</sub>/2, then t<sub>DDTE/1</sub> and t<sub>DTENE/1</sub> apply, otherwise t<sub>DDTLFSE</sub> and t<sub>DTENLFS</sub> apply.

Figure 23. External Late Frame Sync

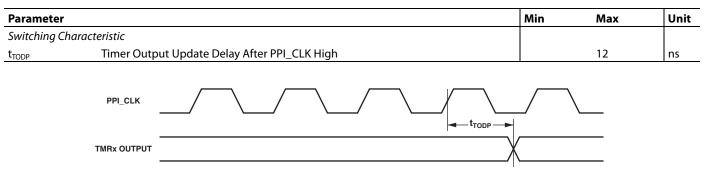

#### **Timer Clock Timing**

Table 37 and Figure 27 describe timer clock timing.

#### Table 37. Timer Clock Timing

Figure 27. Timer Clock Timing

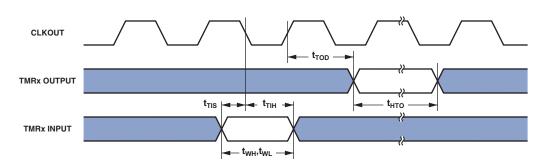

#### **Timer Cycle Timing**

Table 38 and Figure 28 describe timer expired operations. The input signal is asynchronous in "width capture mode" and "external clock mode" and has an absolute maximum input frequency of ( $f_{SCLK}/2$ ) MHz.

#### Table 38. Timer Cycle Timing

|                  |                                                                     | $\begin{array}{c} \textbf{2.25 V} \leq V_{\text{DDEXT}} < \textbf{2.70 V} \\ \textbf{or} \\ \textbf{0.80 V} \leq V_{\text{DDINT}} < \textbf{0.95 V}^1 \end{array}$ |                              | $\begin{array}{c} \textbf{2.70 V} \leq V_{\text{DDEXT}} \leq \textbf{3.60 V} \\ \textbf{and} \\ \textbf{0.95 V} \leq V_{\text{DDINT}} \leq \textbf{1.43 V}^{2, 3} \end{array}$ |                              |      |  |

|------------------|---------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|------|--|

| Parame           | ter                                                                 | Min                                                                                                                                                                | Max                          | Min                                                                                                                                                                            | Max                          | Unit |  |

| Timing C         | Characteristics                                                     |                                                                                                                                                                    |                              |                                                                                                                                                                                |                              |      |  |

| t <sub>WL</sub>  | Timer Pulse Width Input Low (Measured In SCLK Cycles) <sup>4</sup>  | $1 \times t_{SCLK}$                                                                                                                                                |                              | $1 \times t_{SCLK}$                                                                                                                                                            |                              | ns   |  |

| t <sub>WH</sub>  | Timer Pulse Width Input High (Measured In SCLK Cycles) <sup>4</sup> | $1 \times t_{SCLK}$                                                                                                                                                |                              | $1 \times t_{SCLK}$                                                                                                                                                            |                              | ns   |  |

| t <sub>TIS</sub> | Timer Input Setup Time Before CLKOUT Low <sup>5</sup>               | 5.5                                                                                                                                                                |                              | 5.0                                                                                                                                                                            |                              | ns   |  |

| t <sub>TIH</sub> | Timer Input Hold Time After CLKOUT Low <sup>5</sup>                 | 1.5                                                                                                                                                                |                              | 1.5                                                                                                                                                                            |                              | ns   |  |

| Switchin         | ng Characteristics                                                  |                                                                                                                                                                    |                              |                                                                                                                                                                                |                              |      |  |

| t <sub>HTO</sub> | Timer Pulse Width Output (Measured In SCLK Cycles)                  | $1 \times t_{SCLK}$                                                                                                                                                | $(2^{32}-1) \times t_{SCLK}$ | $1 \times t_{SCLK}$                                                                                                                                                            | $(2^{32}-1) \times t_{SCLK}$ | ns   |  |

| t <sub>TOD</sub> | Timer Output Update Delay After CLKOUT High                         |                                                                                                                                                                    | 6.5                          |                                                                                                                                                                                | 6.0                          | ns   |  |

<sup>1</sup> Applies to all nonautomotive-grade devices when operated within either of these voltage ranges.

<sup>2</sup> Applies to all nonautomotive-grade devices when operated within these voltage ranges.

<sup>3</sup> All automotive-grade devices are within these specifications.

<sup>4</sup> The minimum pulse widths apply for TMRx signals in width capture and external clock modes. They also apply to the PF15 or PPI\_CLK signals in PWM output mode. <sup>5</sup> Either a valid setup and hold time or a valid pulse width is sufficient. There is no need to resynchronize programmable flag inputs.

Figure 28. Timer Cycle Timing

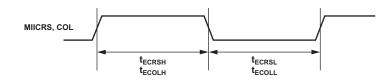

#### Table 44. 10/100 Ethernet MAC Controller Timing: MII/RMII Asynchronous Signal

| Parameter <sup>1,</sup> | ,2                   | Min Max                                                                                     | Unit |

|-------------------------|----------------------|---------------------------------------------------------------------------------------------|------|

| t <sub>ecolh</sub>      | COL Pulse Width High | t <sub>ETxCLK</sub> × 1.5                                                                   | ns   |

|                         |                      | $\begin{array}{l} t_{\text{ETxCLK}} \times 1.5 \\ t_{\text{ERxCLK}} \times 1.5 \end{array}$ | ns   |

| t <sub>ECOLL</sub>      | COL Pulse Width Low  | $t_{ETxCLK} \times 1.5$                                                                     | ns   |

|                         |                      | $\begin{array}{l} t_{\text{ETXCLK}} \times 1.5 \\ t_{\text{ERXCLK}} \times 1.5 \end{array}$ | ns   |

| t <sub>ECRSH</sub>      | CRS Pulse Width High | $t_{ETxCLK} \times 1.5$                                                                     | ns   |

| t <sub>ECRSL</sub>      | CRS Pulse Width Low  | $t_{ETxCLK} \times 1.5$                                                                     | ns   |

<sup>1</sup>MII/RMII asynchronous signals are COL, CRS. These signals are applicable in both MII and RMII modes. The asynchronous COL input is synchronized separately to both the ETxCLK and the ERxCLK, and must have a minimum pulse width high or low at least 1.5 times the period of the slower of the two clocks.

<sup>2</sup> The asynchronous CRS input is synchronized to the ETxCLK, and must have a minimum pulse width high or low at least 1.5 times the period of ETxCLK.

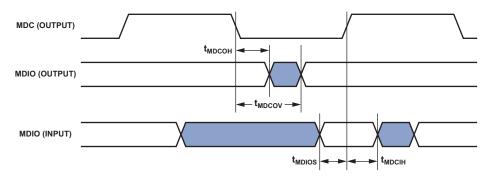

| Table 45. | 10/100 Ethernet MAC Control | ler Timing: MII Stat | ion Management |

|-----------|-----------------------------|----------------------|----------------|

|           |                             |                      |                |

| Parameter <sup>1</sup> |                                                | Min | Мах | Unit |

|------------------------|------------------------------------------------|-----|-----|------|

| t <sub>MDIOS</sub>     | MDIO Input Valid to MDC Rising Edge (Setup)    | 10  |     | ns   |

| t <sub>MDCIH</sub>     | MDC Rising Edge to MDIO Input Invalid (Hold)   | 10  |     | ns   |

| t <sub>MDCOV</sub>     | MDC Falling Edge to MDIO Output Valid          | 25  |     | ns   |

| t <sub>MDCOH</sub>     | MDC Falling Edge to MDIO Output Invalid (Hold) | -1  |     | ns   |

<sup>1</sup> MDC/MDIO is a 2-wire serial bidirectional port for controlling one or more external PHYs. MDC is an output clock whose minimum period is programmable as a multiple of the system clock SCLK. MDIO is a bidirectional data line.

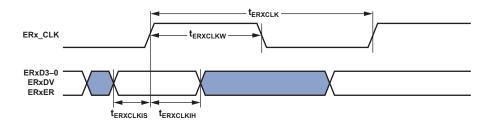

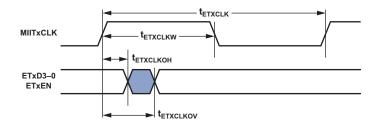

*Figure 30.* 10/100 *Ethernet MAC Controller Timing: MII Receive Signal*

Figure 31. 10/100 Ethernet MAC Controller Timing: Mll Transmit Signal

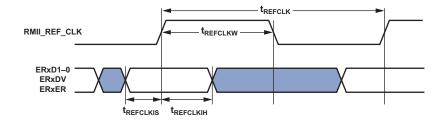

Figure 32. 10/100 Ethernet MAC Controller Timing: RMII Receive Signal

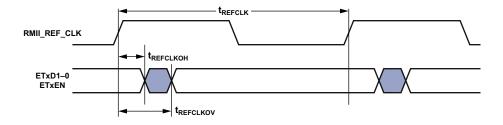

Figure 33. 10/100 Ethernet MAC Controller Timing: RMII Transmit Signal

Figure 34. 10/100 Ethernet MAC Controller Timing: Asynchronous Signal

Figure 35. 10/100 Ethernet MAC Controller Timing: MII Station Management

### **TEST CONDITIONS**

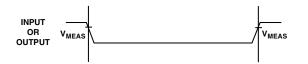

All timing parameters appearing in this data sheet were measured under the conditions described in this section. Figure 48 shows the measurement point for ac measurements (other than output enable/disable). The measurement point is  $V_{MEAS} = V_{DDEXT}/2$ .

Figure 48. Voltage Reference Levels for AC Measurements (Except Output Enable/Disable)

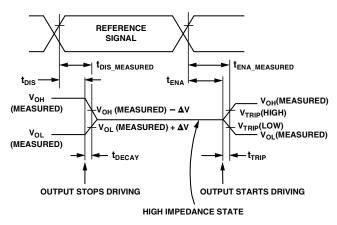

### **Output Enable Time**

Output pins are considered to be enabled when they have made a transition from a high impedance state to the point when they start driving. The output enable time  $t_{ENA}$  is the interval from the point when a reference signal reaches a high or low voltage level to the point when the output starts driving as shown in the Output Enable/Disable diagram (Figure 49). The time  $t_{ENA\_MEA}$ . SURED is the interval from when the reference signal switches to when the output voltage reaches 2.0 V (output high) or 1.0 V (output low). Time  $t_{TRIP}$  is the interval from when the output starts driving to when the output reaches the 1.0 V or 2.0 V trip voltage. Time  $t_{ENA}$  is calculated as shown in the equation:

$$t_{ENA} = t_{ENA\_MEASURED} - t_{TRIP}$$

If multiple pins (such as the data bus) are enabled, the measurement value is that of the first pin to start driving.

### **Output Disable Time**

Output pins are considered to be disabled when they stop driving, go into a high impedance state, and start to decay from their output high or low voltage. The time for the voltage on the bus to decay by  $\Delta V$  is dependent on the capacitive load, C<sub>L</sub>, and the load current, I<sub>L</sub>. This decay time can be approximated by the equation:

$$t_{DECAY} = (C_L \Delta V) / I_L$$

The output disable time  $t_{DIS}$  is the difference between  $t_{DIS\_MEA-SURED}$  and  $t_{DECAY}$  as shown in Figure 49. The time  $t_{DIS\_MEASURED}$  is the interval from when the reference signal switches to when the output voltage decays  $\Delta V$  from the measured output-high or output-low voltage. The time  $t_{DECAY}$  is calculated with the test loads  $C_L$  and  $I_L$ , and with  $\Delta V$  equal to 0.5 V.

Figure 49. Output Enable/Disable

#### **Example System Hold Time Calculation**

To determine the data output hold time in a particular system, first calculate  $t_{DECAY}$  using the equation given above. Choose  $\Delta V$  to be the difference between the processor's output voltage and the input threshold for the device requiring the hold time. A typical  $\Delta V$  is 0.4 V.  $C_L$  is the total bus capacitance (per data line), and  $I_L$  is the total leakage or three-state current (per data line). The hold time is  $t_{DECAY}$  plus the minimum disable time (for example,  $t_{DSDAT}$  for an SDRAM write cycle).

#### **Capacitive Loading**

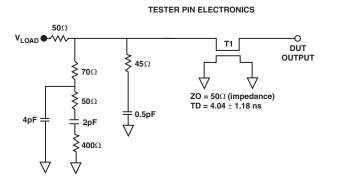

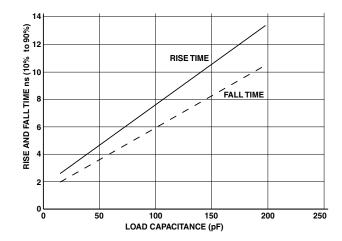

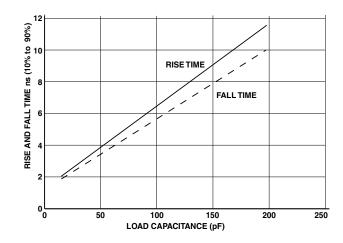

Output delays and holds are based on standard capacitive loads: 30 pF on all pins (see Figure 50). Figure 51 through Figure 60 on Page 55 show how output rise time varies with capacitance. The delay and hold specifications given should be derated by a factor derived from these figures. The graphs in these figures may not be linear outside the ranges shown.

#### NOTES:

THE WORST CASE TRANSMISSION LINE DELAY IS SHOWN AND CAN BE USED FOR THE OUTPUT TIMING ANALYSIS TO REFELECT THE TRANSMISSION LINE EFFECT AND MUST BE CONSIDERED. THE TRANSMISSION LINE (TD) IS FOR LOAD ONLY AND DOES NOT AFFECT THE DATA SHEET TIMING SPECIFICATIONS.

ANALOG DEVICES RECOMMENDS USING THE IBIS MODEL TIMING FOR A GIVEN SYSTEM REQUIREMENT. IF NECESSARY, A SYSTEM MAY INCORPORATE EXTERNAL DRIVERS TO COMPENSATE FOR ANY TIMING DIFFERENCES.

Figure 50. Equivalent Device Loading for AC Measurements (Includes All Fixtures)

Figure 51. Typical Output Delay or Hold for Driver A at V<sub>DDEXT</sub> Min

Figure 52. Typical Output Delay or Hold for Driver A at V<sub>DDEXT</sub> Max

### **ORDERING GUIDE**

In the following table CSP\_BGA = Chip Scale Package Ball Grid Array.

| Model <sup>1</sup> | Temperature Range <sup>2</sup> | Speed Grade (Max) | Package Description                 | Package<br>Option |

|--------------------|--------------------------------|-------------------|-------------------------------------|-------------------|

| ADSP-BF534BBC-4A   | -40°C to +85°C                 | 400 MHz           | 182-Ball CSP_BGA                    | BC-182            |

| ADSP-BF534BBCZ-4A  | -40°C to +85°C                 | 400 MHz           | 182-Ball CSP_BGA                    | BC-182            |

| ADSP-BF534BBC-5A   | -40°C to +85°C                 | 500 MHz           | 182-Ball CSP_BGA                    | BC-182            |

| ADSP-BF534BBCZ-5A  | -40°C to +85°C                 | 500 MHz           | 182-Ball CSP_BGA                    | BC-182            |

| ADSP-BF534BBCZ-4B  | -40°C to +85°C                 | 400 MHz           | 208-Ball CSP_BGA                    | BC-208-2          |

| ADSP-BF534YBCZ-4B  | -40°C to +105°C                | 400 MHz           | 208-Ball CSP_BGA                    | BC-208-2          |

| ADSP-BF534BBCZ-5B  | -40°C to +85°C                 | 500 MHz           | 208-Ball CSP_BGA                    | BC-208-2          |

| ADSP-BF536BBC-3A   | -40°C to +85°C                 | 300 MHz           | 182-Ball CSP_BGA                    | BC-182            |

| ADSP-BF536BBCZ-3A  | -40°C to +85°C                 | 300 MHz           | 182-Ball CSP_BGA                    | BC-182            |

| ADSP-BF536BBC-4A   | -40°C to +85°C                 | 400 MHz           | 182-Ball CSP_BGA                    | BC-182            |

| ADSP-BF536BBCZ-4A  | -40°C to +85°C                 | 400 MHz           | 182-Ball CSP_BGA                    | BC-182            |

| ADSP-BF536BBCZ-3B  | -40°C to +85°C                 | 300 MHz           | 208-Ball CSP_BGA                    | BC-208-2          |

| ADSP-BF536BBCZ3BRL | -40°C to +85°C                 | 300 MHz           | 208-Ball CSP_BGA, 13" Tape and Reel | BC-208-2          |

| ADSP-BF536BBCZ-4B  | -40°C to +85°C                 | 400 MHz           | 208-Ball CSP_BGA                    | BC-208-2          |

| ADSP-BF537BBC-5A   | -40°C to +85°C                 | 500 MHz           | 182-Ball CSP_BGA                    | BC-182            |

| ADSP-BF537BBCZ-5A  | -40°C to +85°C                 | 500 MHz           | 182-Ball CSP_BGA                    | BC-182            |

| ADSP-BF537BBCZ-5B  | -40°C to +85°C                 | 500 MHz           | 208-Ball CSP_BGA                    | BC-208-2          |

| ADSP-BF537BBCZ-5AV | -40°C to +85°C                 | 533 MHz           | 182-Ball CSP_BGA                    | BC-182            |

| ADSP-BF537BBCZ-5BV | -40°C to +85°C                 | 533 MHz           | 208-Ball CSP_BGA                    | BC-208-2          |

| ADSP-BF537KBCZ-6AV | 0°C to +70°C                   | 600 MHz           | 182-Ball CSP_BGA                    | BC-182            |

| ADSP-BF537KBCZ-6BV | 0°C to +70°C                   | 600 MHz           | 208-Ball CSP_BGA                    | BC-208-2          |

$^{1}$ Z = RoHS compliant part.

<sup>2</sup> Referenced temperature is ambient temperature. The ambient temperature is not a specification. Please see Operating Conditions on Page 23 for junction temperature (T<sub>j</sub>) specification which is the only temperature specification.