Welcome to E-XFL.COM

#### Understanding <u>Embedded - DSP (Digital</u> <u>Signal Processors)</u>

#### Embedded - DSP (Digital Signal Processors) are specialized microprocessors designed to perform complex mathematical computations on digital signals in real-time. Unlike general-purpose processors, DSPs are optimized for high-speed numeric processing tasks, making them ideal for applications that require efficient and precise manipulation of digital data. These processors are fundamental in converting and processing signals in various forms, including audio, video, and communication signals, ensuring that data is accurately interpreted and utilized in embedded systems.

#### Applications of <u>Embedded - DSP (Digital</u> <u>Signal Processors)</u>

#### Details

E·XFl

| Details                 |                                                                      |

|-------------------------|----------------------------------------------------------------------|

| Product Status          | Obsolete                                                             |

| Туре                    | Fixed Point                                                          |

| Interface               | CAN, SPI, SSP, TWI, UART                                             |

| Clock Rate              | 500MHz                                                               |

| Non-Volatile Memory     | External                                                             |

| On-Chip RAM             | 132kB                                                                |

| Voltage - I/O           | 2.50V, 3.30V                                                         |

| Voltage - Core          | 1.26V                                                                |

| Operating Temperature   | -40°C ~ 85°C (TA)                                                    |

| Mounting Type           | Surface Mount                                                        |

| Package / Case          | 182-LFBGA, CSPBGA                                                    |

| Supplier Device Package | 182-CSPBGA (12x12)                                                   |

| Purchase URL            | https://www.e-xfl.com/product-detail/analog-devices/adsp-bf537bbc-5a |

|                         |                                                                      |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **GENERAL DESCRIPTION**

Table 1. Processor Comparison

The ADSP-BF534/ADSP-BF536/ADSP-BF537 processors are members of the Blackfin<sup>®</sup> family of products, incorporating the Analog Devices, Inc./Intel Micro Signal Architecture (MSA). Blackfin processors combine a dual-MAC, state-of-the-art signal processing engine, the advantages of a clean, orthogonal RISC-like microprocessor instruction set, and single-instruction, multiple-data (SIMD) multimedia capabilities into a single instruction-set architecture.

The ADSP-BF534/ADSP-BF536/ADSP-BF537 processors are completely code and pin compatible. They differ only with respect to their performance, on-chip memory, and presence of the Ethernet MAC module. Specific performance, memory, and feature configurations are shown in Table 1.

| -                                      |                              |                      |                      |                      |  |  |  |

|----------------------------------------|------------------------------|----------------------|----------------------|----------------------|--|--|--|

| Features                               |                              | ADSP-BF534           | ADSP-BF536           | ADSP-BF537           |  |  |  |

| Ethernet MAC                           |                              | _                    | 1                    | 1                    |  |  |  |

| CAN                                    |                              | 1                    | 1                    | 1                    |  |  |  |

| TWI                                    |                              | 1                    | 1                    | 1                    |  |  |  |

| SPORTs                                 |                              | 2                    | 2                    | 2                    |  |  |  |

| UARTs                                  |                              | 2                    | 2                    | 2                    |  |  |  |

| SPI                                    |                              | 1                    | 1                    | 1                    |  |  |  |

| GP Timers                              |                              | 8                    | 8                    | 8                    |  |  |  |

| Watchdog Time                          | ers                          | 1                    | 1                    | 1                    |  |  |  |

| RTC                                    |                              | 1                    | 1                    | 1                    |  |  |  |

| Parallel Periphe                       | eral Interface               | 1                    | 1                    | 1                    |  |  |  |

| GPIOs                                  |                              | 48                   | 48                   | 48                   |  |  |  |

|                                        | L1 Instruction<br>SRAM/Cache | 16K bytes            | 16K bytes            | 16K bytes            |  |  |  |

|                                        | L1 Instruction<br>SRAM       | 48K bytes            | 48K bytes            | 48K bytes            |  |  |  |

| Memory<br>Configuration                | L1 Data<br>SRAM/Cache        | 32K bytes            | 32K bytes            | 32K bytes            |  |  |  |

|                                        | L1 Data SRAM                 | 32K bytes            | _                    | 32K bytes            |  |  |  |

| L1 Scratchpad<br>L3 Boot ROM           |                              | 4K bytes             | 4K bytes             | 4K bytes             |  |  |  |

|                                        |                              | 2K bytes             | 2K bytes             | 2K bytes             |  |  |  |

| Maximum Spee                           | ed Grade                     | 500 MHz              | 400 MHz              | 600 MHz              |  |  |  |

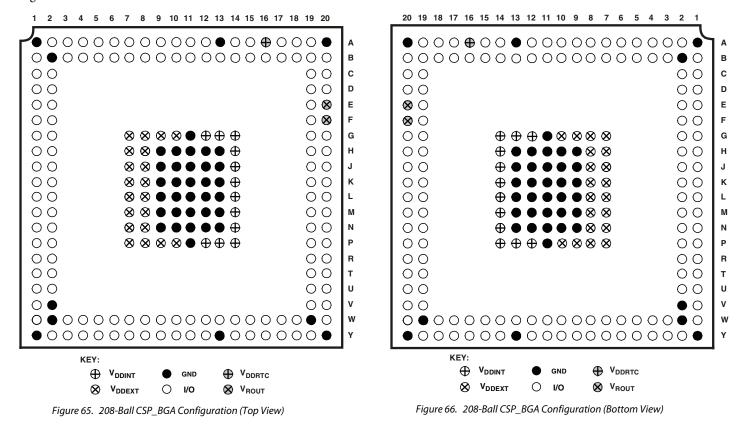

| Package Options:<br>CSP_BGA<br>CSP_BGA |                              | 208-Ball<br>182-Ball | 208-Ball<br>182-Ball | 208-Ball<br>182-Ball |  |  |  |

By integrating a rich set of industry-leading system peripherals and memory, the Blackfin processors are the platform of choice for next-generation applications that require RISC-like programmability, multimedia support, and leading-edge signal processing in one integrated package.

### PORTABLE LOW POWER ARCHITECTURE

Blackfin processors provide world-class power management and performance. They are produced with a low power and low voltage design methodology and feature on-chip dynamic power management, which is the ability to vary both the voltage and frequency of operation to significantly lower overall power consumption. This capability can result in a substantial reduction in power consumption, compared with just varying the frequency of operation. This allows longer battery life for portable appliances.

### SYSTEM INTEGRATION

The Blackfin processor is a highly integrated system-on-a-chip solution for the next generation of embedded network-connected applications. By combining industry-standard interfaces with a high performance signal processing core, cost-effective applications can be developed quickly, without the need for costly external components. The system peripherals include an IEEE-compliant 802.3 10/100 Ethernet MAC (ADSP-BF536 and ADSP-BF537 only), a CAN 2.0B controller, a TWI controller, two UART ports, an SPI port, two serial ports (SPORTs), nine general-purpose 32-bit timers (eight with PWM capability), a real-time clock, a watchdog timer, and a parallel peripheral interface (PPI).

### **BLACKFIN PROCESSOR PERIPHERALS**

The ADSP-BF534/ADSP-BF536/ADSP-BF537 processors contain a rich set of peripherals connected to the core via several high bandwidth buses, providing flexibility in system configuration as well as excellent overall system performance (see Figure 1). The processors contain dedicated network communication modules and high speed serial and parallel ports, an interrupt controller for flexible management of interrupts from the on-chip peripherals or external sources, and power management control functions to tailor the performance and power characteristics of the processor and system to many application scenarios.

All of the peripherals, except for the general-purpose I/O, CAN, TWI, real-time clock, and timers, are supported by a flexible DMA structure. There are also separate memory DMA channels dedicated to data transfers between the processor's various memory spaces, including external SDRAM and asynchronous memory. Multiple on-chip buses running at up to 133 MHz provide enough bandwidth to keep the processor core running along with activity on all of the on-chip and external peripherals.

The Blackfin processors include an on-chip voltage regulator in support of the processors' dynamic power management capability. The voltage regulator provides a range of core voltage levels when supplied from  $V_{DDEXT}$ . The voltage regulator can be bypassed at the user's discretion.

#### Core Event Controller (CEC)

The CEC supports nine general-purpose interrupts (IVG15–7), in addition to the dedicated interrupt and exception events. Of these general-purpose interrupts, the two lowest priority interrupts (IVG15–14) are recommended to be reserved for software interrupt handlers, leaving seven prioritized interrupt inputs to support the peripherals of the Blackfin processor. Table 2 describes the inputs to the CEC, identifies their names in the event vector table (EVT), and lists their priorities.

#### Table 2. Core Event Controller (CEC)

| Priority       |                              |           |

|----------------|------------------------------|-----------|

| (0 Is Highest) | Event Class                  | EVT Entry |

| 0              | Emulation/Test Control       | EMU       |

| 1              | Reset                        | RST       |

| 2              | Nonmaskable Interrupt        | NMI       |

| 3              | Exception                    | EVX       |

| 4              | Reserved                     | —         |

| 5              | Hardware Error               | IVHW      |

| 6              | Core Timer                   | IVTMR     |

| 7              | General-Purpose Interrupt 7  | IVG7      |

| 8              | General-Purpose Interrupt 8  | IVG8      |

| 9              | General-Purpose Interrupt 9  | IVG9      |

| 10             | General-Purpose Interrupt 10 | IVG10     |

| 11             | General-Purpose Interrupt 11 | IVG11     |

| 12             | General-Purpose Interrupt 12 | IVG12     |

| 13             | General-Purpose Interrupt 13 | IVG13     |

| 14             | General-Purpose Interrupt 14 | IVG14     |

| 15             | General-Purpose Interrupt 15 | IVG15     |

#### System Interrupt Controller (SIC)

The system interrupt controller provides the mapping and routing of events from the many peripheral interrupt sources to the prioritized general-purpose interrupt inputs of the CEC. Although the processor provides a default mapping, the user can alter the mappings and priorities of interrupt events by writing the appropriate values into the interrupt assignment registers (IAR). Table 3 describes the inputs into the SIC and the default mappings into the CEC. Table 3. System Interrupt Controller (SIC)

| Peripheral Interrupt Event                                     | Default<br>Mapping | Peripheral<br>Interrupt ID |

|----------------------------------------------------------------|--------------------|----------------------------|

| PLL Wakeup                                                     | IVG7               | 0                          |

| DMA Error (Generic)                                            | IVG7               | 1                          |

| DMAR0 Block Interrupt                                          | IVG7               | 1                          |

| DMAR1 Block Interrupt                                          | IVG7               | 1                          |

| DMAR0 Overflow Error                                           | IVG7               | 1                          |

| DMAR1 Overflow Error                                           | IVG7               | 1                          |

| CAN Error                                                      | IVG7               | 2                          |

| Ethernet Error (ADSP-BF536 and ADSP-BF537 only)                | IVG7               | 2                          |

| SPORT 0 Error                                                  | IVG7               | 2                          |

| SPORT 1 Error                                                  | IVG7               | 2                          |

| PPI Error                                                      | IVG7               | 2                          |

| SPI Error                                                      | IVG7               | 2                          |

| UART0 Error                                                    | IVG7               | 2                          |

| UART1 Error                                                    | IVG7               | 2                          |

| Real-Time Clock                                                | IVG8               | 3                          |

| DMA Channel 0 (PPI)                                            | IVG8               | 4                          |

| DMA Channel 3 (SPORT 0 Rx)                                     | IVG9               | 5                          |

| DMA Channel 4 (SPORT 0 Tx)                                     | IVG9               | 6                          |

| DMA Channel 5 (SPORT 1 Rx)                                     | IVG9               | 7                          |

| DMA Channel 6 (SPORT 1 Tx)                                     | IVG9               | 8                          |

| TWI                                                            | IVG10              | 9                          |

| DMA Channel 7 (SPI)                                            | IVG10              | 10                         |

| DMA Channel 8 (UARTO Rx)                                       | IVG10              | 11                         |

| DMA Channel 9 (UARTO Tx)                                       | IVG10              | 12                         |

| DMA Channel 10 (UART1 Rx)                                      | IVG10              | 13                         |

| DMA Channel 11 (UART1 Tx)                                      | IVG10              | 14                         |

| CAN Rx                                                         | IVG10              | 15                         |

| CAN Tx                                                         | IVG11              | 16                         |

| DMA Channel 1 (Ethernet Rx,<br>ADSP-BF536 and ADSP-BF537 only) | IVG11              | 17                         |

| Port H Interrupt A                                             | IVG11              | 17                         |

| DMA Channel 2 (Ethernet Tx,<br>ADSP-BF536 and ADSP-BF537 only) | IVG11              | 18                         |

| Port H Interrupt B                                             | IVG11              | 18                         |

| Timer 0                                                        | IVG12              | 19                         |

| Timer 1                                                        | IVG12              | 20                         |

| Timer 2                                                        | IVG12              | 21                         |

| Timer 3                                                        | IVG12              | 22                         |

| Timer 4                                                        | IVG12              | 23                         |

| Timer 5                                                        | IVG12              | 24                         |

| Timer 6                                                        | IVG12              | 25                         |

| Timer 7                                                        | IVG12              | 26                         |

| Port F, G Interrupt A                                          | IVG12              | 27                         |

| Port G Interrupt B                                             | IVG12              | 28                         |

### SERIAL PORTS (SPORTs)

The ADSP-BF534/ADSP-BF536/ADSP-BF537 processors incorporate two dual-channel synchronous serial ports (SPORT0 and SPORT1) for serial and multiprocessor communications. The SPORTs support the following features:

- I<sup>2</sup>S capable operation.

- Bidirectional operation Each SPORT has two sets of independent transmit and receive pins, enabling eight channels of I<sup>2</sup>S stereo audio.

- Buffered (8-deep) transmit and receive ports Each port has a data register for transferring data words to and from other processor components and shift registers for shifting data in and out of the data registers.

- Clocking Each transmit and receive port can either use an external serial clock or generate its own, in frequencies ranging from ( $f_{SCLK}/131,070$ ) Hz to ( $f_{SCLK}/2$ ) Hz.

- Word length Each SPORT supports serial data words from 3 bits to 32 bits in length, transferred most significant bit first or least significant bit first.

- Framing Each transmit and receive port can run with or without frame sync signals for each data word. Frame sync signals can be generated internally or externally, active high or low, and with either of two pulse widths and early or late frame sync.

- Companding in hardware Each SPORT can perform A-law or μ-law companding according to ITU recommendation G.711. Companding can be selected on the transmit and/or receive channel of the SPORT without additional latencies.

- DMA operations with single-cycle overhead Each SPORT can automatically receive and transmit multiple buffers of memory data. The processor can link or chain sequences of DMA transfers between a SPORT and memory.

- Interrupts Each transmit and receive port generates an interrupt upon completing the transfer of a data word or after transferring an entire data buffer, or buffers, through DMA.

- Multichannel capability Each SPORT supports 128 channels out of a 1024-channel window and is compatible with the H.100, H.110, MVIP-90, and HMVIP standards.

### **SERIAL PERIPHERAL INTERFACE (SPI) PORT**

The ADSP-BF534/ADSP-BF536/ADSP-BF537 processors have an SPI-compatible port that enables the processor to communicate with multiple SPI-compatible devices.

The SPI interface uses three pins for transferring data: two data pins (Master Output-Slave Input, MOSI, and Master Input-Slave Output, MISO) and a clock pin (serial clock, SCK). An SPI chip select input pin (SPISS) lets other SPI devices select the processor, and seven SPI chip select output pins (SPISEL7–1) let the processor select other SPI devices. The SPI select pins are reconfigured programmable flag pins. Using these pins, the SPI port provides a full-duplex, synchronous serial interface, which supports both master/slave modes and multimaster environments.

The SPI port's baud rate and clock phase/polarities are programmable, and it has an integrated DMA controller, configurable to support transmit or receive data streams. The SPI's DMA controller can only service unidirectional accesses at any given time.

The SPI port's clock rate is calculated as:

$$SPI Clock Rate = \frac{f_{SCLK}}{2 \times SPI\_BAUD}$$

where the 16-bit SPI\_BAUD register contains a value of 2 to 65,535.

During transfers, the SPI port simultaneously transmits and receives by serially shifting data in and out on its two serial data lines. The serial clock line synchronizes the shifting and sampling of data on the two serial data lines.

### **UART PORTS**

The ADSP-BF534/ADSP-BF536/ADSP-BF537 processors provide two full-duplex universal asynchronous receiver and transmitter (UART) ports, which are fully compatible with PCstandard UARTs. Each UART port provides a simplified UART interface to other peripherals or hosts, supporting full-duplex, DMA-supported, asynchronous transfers of serial data. A UART port includes support for five to eight data bits, one or two stop bits, and none, even, or odd parity. Each UART port supports two modes of operation:

- PIO (programmed I/O) The processor sends or receives data by writing or reading I/O mapped UART registers. The data is double-buffered on both transmit and receive.

- DMA (direct memory access) The DMA controller transfers both transmit and receive data. This reduces the number and frequency of interrupts required to transfer data to and from memory. The UART has two dedicated DMA channels, one for transmit and one for receive. These DMA channels have lower default priority than most DMA channels because of their relatively low service rates.

Each UART port's baud rate, serial data format, error code generation and status, and interrupts are programmable:

- Supporting bit rates ranging from (f<sub>SCLK</sub>/1,048,576) to (f<sub>SCLK</sub>/16) bits per second.

- Supporting data formats from 7 bits to 12 bits per frame.

- Both transmit and receive operations can be configured to generate maskable interrupts to the processor.

The UART port's clock rate is calculated as:

$$UART Clock Rate = \frac{f_{SCLK}}{16 \times UARTx\_Divisor}$$

where the 16-bit *UARTx\_Divisor* comes from the UARTx\_DLH register (most significant 8 bits) and UARTx\_DLL register (least significant 8 bits).

- Programmable Rx address filters, including a 64-bit address hash table for multicast and/or unicast frames, and programmable filter modes for broadcast, multicast, unicast, control, and damaged frames.

- Advanced power management supporting unattended transfer of Rx and Tx frames and status to/from external memory via DMA during low power sleep mode.

- System wake-up from sleep operating mode upon magic packet or any of four user-definable wake-up frame filters.

- Support for 802.3Q tagged VLAN frames.

- Programmable MDC clock rate and preamble suppression.

- In RMII operation, 7 unused pins can be configured as GPIO pins for other purposes.

## PORTS

The ADSP-BF534/ADSP-BF536/ADSP-BF537 processors group the many peripheral signals to four ports—Port F, Port G, Port H, and Port J. Most of the associated pins are shared by multiple signals. The ports function as multiplexer controls. Eight of the pins (Port F7–0) offer high source/high sink current capabilities.

### General-Purpose I/O (GPIO)

The processors have 48 bidirectional, general-purpose I/O (GPIO) pins allocated across three separate GPIO modules— PORTFIO, PORTGIO, and PORTHIO, associated with Port F, Port G, and Port H, respectively. Port J does not provide GPIO functionality. Each GPIO-capable pin shares functionality with other processor peripherals via a multiplexing scheme; however, the GPIO functionality is the default state of the device upon power-up. Neither GPIO output or input drivers are active by default. Each general-purpose port pin can be individually controlled by manipulation of the port control, status, and interrupt registers:

- GPIO direction control register Specifies the direction of each individual GPIO pin as input or output.

- GPIO control and status registers The processors employ a "write one to modify" mechanism that allows any combination of individual GPIO pins to be modified in a single instruction, without affecting the level of any other GPIO pins. Four control registers are provided. One register is written in order to set pin values, one register is written in order to clear pin values, one register is written in order to toggle pin values, and one register is written in order to specify a pin value. Reading the GPIO status register allows software to interrogate the sense of the pins.

- GPIO interrupt mask registers The two GPIO interrupt mask registers allow each individual GPIO pin to function as an interrupt to the processor. Similar to the two GPIO control registers that are used to set and clear individual pin values, one GPIO interrupt mask register sets bits to enable interrupt function, and the other GPIO interrupt mask register clears bits to disable interrupt function.

GPIO pins defined as inputs can be configured to generate hardware interrupts, while output pins can be triggered by software interrupts.

• GPIO interrupt sensitivity registers – The two GPIO interrupt sensitivity registers specify whether individual pins are level- or edge-sensitive and specify—if edge-sensitive whether just the rising edge or both the rising and falling edges of the signal are significant. One register selects the type of sensitivity, and one register selects which edges are significant for edge-sensitivity.

## PARALLEL PERIPHERAL INTERFACE (PPI)

The processor provides a parallel peripheral interface (PPI) that can connect directly to parallel ADC and DAC converters, video encoders and decoders, and other general-purpose peripherals. The PPI consists of a dedicated input clock pin, up to three frame synchronization pins, and up to 16 data pins. The input clock supports parallel data rates up to half the system clock rate and the synchronization signals can be configured as either inputs or outputs.

The PPI supports a variety of general-purpose and ITU-R 656 modes of operation. In general-purpose mode, the PPI provides half-duplex, bidirectional data transfer with up to 16 bits of data. Up to three frame synchronization signals are also provided. In ITU-R 656 mode, the PPI provides half-duplex bidirectional transfer of 8- or 10-bit video data. Additionally, on-chip decode of embedded start-of-line (SOL) and start-of-field (SOF) preamble packets is supported.

### **General-Purpose Mode Descriptions**

The general-purpose modes of the PPI are intended to suit a wide variety of data capture and transmission applications. Three distinct submodes are supported:

- 1. Input mode Frame syncs and data are inputs into the PPI.

- 2. Frame capture mode Frame syncs are outputs from the PPI, but data are inputs.

- 3. Output mode Frame syncs and data are outputs from the PPI.

### Input Mode

Input mode is intended for ADC applications, as well as video communication with hardware signaling. In its simplest form, PPI\_FS1 is an external frame sync input that controls when to read data. The PPI\_DELAY MMR allows for a delay (in PPI\_ CLK cycles) between reception of this frame sync and the initiation of data reads. The number of input data samples is user programmable and defined by the contents of the PPI\_COUNT register. The PPI supports 8-bit and 10-bit through 16-bit data, programmable in the PPI\_CONTROL register.

### Frame Capture Mode

Frame capture mode allows the video source(s) to act as a slave (for frame capture for example). The ADSP-BF534/ ADSP-BF536/ADSP-BF537 processors control when to read from the video source(s). PPI\_FS1 is an HSYNC output and PPI\_FS2 is a VSYNC output.

(VCO) and the system clock. SCLK divider values are 1 through 15. Table 6 illustrates typical system clock ratios.

| Signal Name | Divider Ratio | Example Frequency Ratios<br>(MHz) |      |  |

|-------------|---------------|-----------------------------------|------|--|

| SSEL3-0     |               | VCO                               | SCLK |  |

| 0001        | 1:1           | 100                               | 100  |  |

| 0110        | 6:1           | 300                               | 50   |  |

| 1010        | 10:1          | 500                               | 50   |  |

#### Table 6. Example System Clock Ratios

Note that the divisor ratio must be chosen to limit the system clock frequency to its maximum of  $f_{SCLK}$ . The SSEL value can be changed dynamically without any PLL lock latencies by writing the appropriate values to the PLL divisor register (PLL\_DIV).

The core clock (CCLK) frequency can also be dynamically changed by means of the CSEL1–0 bits of the PLL\_DIV register. Supported CCLK divider ratios are 1, 2, 4, and 8, as shown in Table 7. This programmable core clock capability is useful for fast core frequency modifications.

### Table 7. Core Clock Ratios

| Signal Name | Divider Ratio | Example Frequency Ratio<br>(MHz) |      |  |

|-------------|---------------|----------------------------------|------|--|

| CSEL1-0     | VCO:CCLK      | VCO                              | CCLK |  |

| 00          | 1:1           | 300                              | 300  |  |

| 01          | 2:1           | 300                              | 150  |  |

| 10          | 4:1           | 500                              | 125  |  |

| 11          | 8:1           | 200                              | 25   |  |

The maximum CCLK frequency not only depends on the part's speed grade (see Ordering Guide on Page 67), it also depends on the applied  $V_{DDINT}$  voltage (see Table 10, Table 11, and Table 12 on Page 24 for details). The maximal system clock rate (SCLK) depends on the chip package and the applied  $V_{DDEXT}$  voltage (see Table 14 on Page 24).

### **BOOTING MODES**

The ADSP-BF534/ADSP-BF536/ADSP-BF537 processor has six mechanisms (listed in Table 8) for automatically loading internal and external memory after a reset. A seventh mode is provided to execute from external memory, bypassing the boot sequence.

#### Table 8. Booting Modes

| BMODE2-0 | Description                                           |

|----------|-------------------------------------------------------|

| 000      | Execute from 16-bit external memory (bypass boot ROM) |

| 001      | Boot from 8-bit or 16-bit memory<br>(EPROM/flash)     |

| 010      | Reserved                                              |

| 011      | Boot from serial SPI memory (EEPROM/flash)            |

| 100      | Boot from SPI host (slave mode)                       |

#### Table 8. Booting Modes (Continued)

| BMODE2-0 | Description                                |

|----------|--------------------------------------------|

| 101      | Boot from serial TWI memory (EEPROM/flash) |

| 110      | Boot from TWI host (slave mode)            |

| 111      | Boot from UART host (slave mode)           |

The BMODE pins of the reset configuration register, sampled during power-on resets and software-initiated resets, implement the following modes:

- Execute from 16-bit external memory Execution starts from address 0x2000 0000 with 16-bit packing. The boot ROM is bypassed in this mode. All configuration settings are set for the slowest device possible (3-cycle hold time; 15-cycle R/W access times; 4-cycle setup).

- Boot from 8-bit and 16-bit external flash memory The 8-bit or 16-bit flash boot routine located in Boot ROM memory space is set up using asynchronous memory bank 0. All configuration settings are set for the slowest device possible (3-cycle hold time; 15-cycle R/W access times; 4-cycle setup). The Boot ROM evaluates the first byte of the boot stream at address 0x2000 0000. If it is 0x40, 8-bit boot is performed. A 0x60 byte assumes a 16-bit memory device and performs 8-bit DMA. A 0x20 byte also assumes 16-bit memory but performs 16-bit DMA.

- Boot from serial SPI memory (EEPROM or flash) 8-, 16-, or 24-bit addressable devices are supported as well as AT45DB041, AT45DB081, AT45DB161, AT45DB321, AT45DB642, and AT45DB1282 DataFlash<sup>®</sup> devices from Atmel. The SPI uses the PF10/SPI SSEL1 output pin to select a single SPI EEPROM/flash device, submits a read command and successive address bytes (0x00) until a valid 8-, 16-, or 24-bit, or Atmel addressable device is detected, and begins clocking data into the processor.

- Boot from SPI host device The Blackfin processor operates in SPI slave mode and is configured to receive the bytes of the .LDR file from an SPI host (master) agent. To hold off the host device from transmitting while the boot ROM is busy, the Blackfin processor asserts a GPIO pin, called host wait (HWAIT), to signal the host device not to send any more bytes until the flag is deasserted. The flag is chosen by the user and this information is transferred to the Blackfin processor via bits 10:5 of the FLAG header.

- Boot from UART Using an autobaud handshake sequence, a boot-stream-formatted program is downloaded by the host. The host agent selects a baud rate within the UART's clocking capabilities. When performing the autobaud, the UART expects an "@" (boot stream) character (8 bits data, 1 start bit, 1 stop bit, no parity bit) on the RXD pin to determine the bit rate. It then replies with an acknowledgement that is composed of 4 bytes: 0xBF, the value of UART\_DLL, the value of UART\_DLH, and 0x00. The host can then download the boot stream. When the processor needs to hold off the host, it deasserts CTS. Therefore, the host must monitor this signal.

### Table 9. Pin Descriptions (Continued)

| Pin Name                                                                          | Туре | Function                                                                                                                          | Driver<br>Type <sup>1</sup> |

|-----------------------------------------------------------------------------------|------|-----------------------------------------------------------------------------------------------------------------------------------|-----------------------------|

| <i>Port H: GPIO/10/100 Ethernet MAC</i> (On ADSP-BF534, these pins are GPIO only) |      |                                                                                                                                   |                             |

| PH0 – GPIO/ <i>ETxD0</i>                                                          | I/O  | GPIO/Ethernet MII or RMII Transmit D0                                                                                             | E                           |

| PH1 – GPIO/ <i>ETxD1</i>                                                          | I/O  | GPIO/Ethernet MII or RMII Transmit D1                                                                                             | E                           |

| PH2 – GPIO/ <i>ETxD2</i>                                                          | I/O  | GPIO/Ethernet MII Transmit D2                                                                                                     | E                           |

| PH3 – GPIO/ <i>ETxD3</i>                                                          | I/O  | GPIO/Ethernet MII Transmit D3                                                                                                     | E                           |

| PH4 – GPIO/ <i>ETxEN</i>                                                          | I/O  | GPIO/Ethernet MII or RMII Transmit Enable                                                                                         | E                           |

| PH5 – GPIO/ <i>MII TxCLK/RMII REF_CLK</i>                                         | I/O  | GPIO/Ethernet MII Transmit Clock/RMII Reference Clock                                                                             | E                           |

| PH6 – GPIO/ <i>MII <mark>PHYINT</mark>/RMII <mark>MDINT</mark></i>                | I/O  | GPIO/Ethernet MII PHY Interrupt/RMII Management Data Interrupt (This pin should be pulled high when used as a hibernate wake-up.) | E                           |

| PH7 – GPIO/ <i>COL</i>                                                            | I/O  | GPIO/Ethernet Collision                                                                                                           | E                           |

| PH8 – GPIO/ <i>ERxD0</i>                                                          | I/O  | GPIO/Ethernet MII or RMII Receive D0                                                                                              | E                           |

| PH9 – GPIO/ERxD1                                                                  | I/O  | GPIO/Ethernet MII or RMII Receive D1                                                                                              | E                           |

| PH10 – GPIO/ <i>ERxD2</i>                                                         | I/O  | GPIO/Ethernet MII Receive D2                                                                                                      | E                           |

| PH11 – GPIO/ <i>ERxD3</i>                                                         | I/O  | GPIO/Ethernet MII Receive D3                                                                                                      | E                           |

| PH12 – GPIO/ERxDV/TACLK5                                                          | I/O  | GPIO/Ethernet MII Receive Data Valid/Alternate Timer5 Input Clock                                                                 | E                           |

| PH13 – GPIO/ <i>ERxCLK/TACLK6</i>                                                 | I/O  | GPIO/Ethernet MII Receive Clock/Alternate Timer6 Input Clock                                                                      | E                           |

| PH14 – GPIO/ERxER/TACLK7                                                          | I/O  | GPIO/Ethernet MII or RMII Receive Error/Alternate Timer7 Input Clock                                                              | E                           |

| PH15 – GPIO/ <i>MII CRS/RMII CRS_DV</i>                                           | I/O  | GPIO/Ethernet MII Carrier Sense/Ethernet RMII Carrier Sense and Receive Data<br>Valid                                             | E                           |

| Port J: SPORT0/TWI/SPI Select/CAN                                                 |      |                                                                                                                                   |                             |

| PJO – MDC                                                                         | 0    | Ethernet Management Channel Clock (On ADSP-BF534 processors, do not connect this pin.)                                            | E                           |

| PJ1 – MDIO                                                                        | I/O  | Ethernet Management Channel Serial Data (On ADSP-BF534 processors, tie this pin to ground.)                                       | E                           |

| PJ2 – SCL                                                                         | I/O  | TWI Serial Clock (This pin is an open-drain output and requires a pull-up resistor.)                                              | F                           |

| PJ3 – SDA                                                                         | I/O  | TWI Serial Data (This pin is an open-drain output and requires a pull-up resistor.)                                               | F                           |

| PJ4 – DROSEC/CANRX/TACIO                                                          | I    | SPORT0 Receive Data Secondary/CAN Receive/Timer0 Alternate Input Capture                                                          |                             |

| PJ5 – DTOSEC/CANTX/SPI SSEL7                                                      | 0    | SPORT0 Transmit Data Secondary/CAN Transmit/SPI Slave Select Enable 7                                                             | С                           |

| PJ6 – RSCLK0/TACLK2                                                               | I/O  | SPORT0 Receive Serial Clock/Alternate Timer2 Clock Input                                                                          | D                           |

| PJ7 – RFSO/TACLK3                                                                 | I/O  | SPORT0 Receive Frame Sync/Alternate Timer3 Clock Input                                                                            | С                           |

| PJ8 – DROPRI/TACLK4                                                               | I    | SPORT0 Receive Data Primary/Alternate Timer4 Clock Input                                                                          |                             |

| PJ9 – TSCLK0/TACLK1                                                               | I/O  | SPORT0 Transmit Serial Clock/Alternate Timer1 Clock Input                                                                         | D                           |

| PJ10 – TFSO/SPI SSEL3                                                             | I/O  | SPORT0 Transmit Frame Sync/SPI Slave Select Enable 3                                                                              | С                           |

| PJ11 – DTOPRI/SPI SSEL2                                                           | 0    | SPORT0 Transmit Data Primary/SPI Slave Select Enable 2                                                                            | С                           |

| Real-Time Clock                                                                   |      |                                                                                                                                   |                             |

| RTXI                                                                              | I    | RTC Crystal Input (This pin should be pulled low when not used.)                                                                  |                             |

| RTXO                                                                              | 0    | RTC Crystal Output (Does not three-state in hibernate.)                                                                           |                             |

| JTAG Port                                                                         |      |                                                                                                                                   |                             |

| ТСК                                                                               | I    | JTAG Clock                                                                                                                        |                             |

| TDO                                                                               | 0    | JTAG Serial Data Out                                                                                                              | С                           |

| TDI                                                                               | 1    | JTAG Serial Data In                                                                                                               |                             |

| TMS                                                                               | 1    | JTAG Mode Select                                                                                                                  |                             |

| TRST                                                                              | I    | JTAG Reset (This pin should be pulled low if the JTAG port is not used.)                                                          |                             |

| EMU                                                                               | 0    | Emulation Output                                                                                                                  | С                           |

## **SPECIFICATIONS**

Note that component specifications are subject to change without notice.

## **OPERATING CONDITIONS**

| Param              | eter                                                          | Conditions                                                                                        | Min                    | Nominal    | Max                    | Unit |

|--------------------|---------------------------------------------------------------|---------------------------------------------------------------------------------------------------|------------------------|------------|------------------------|------|

| V <sub>DDINT</sub> | Internal Supply Voltage <sup>1</sup>                          | Nonautomotive 300 MHz, 400 MHz, and 500 MHz speed grade models <sup>2</sup>                       | 0.8                    | 1.2        | 1.32                   | V    |

| V <sub>DDINT</sub> | Internal Supply Voltage <sup>1</sup>                          | Nonautomotive 533 MHz speed grade models <sup>2</sup>                                             | 0.8                    | 1.25       | 1.375                  | v    |

| V <sub>DDINT</sub> | Internal Supply Voltage <sup>1</sup>                          | Nonautomotive 600 MHz speed grade models <sup>2</sup>                                             | 0.8                    | 1.3        | 1.43                   | v    |

| V <sub>DDINT</sub> | Internal Supply Voltage <sup>1</sup>                          | Automotive grade models and +105°C nonautomotive grade models <sup>2</sup>                        | 0.95                   | 1.2        | 1.32                   | V    |

| V <sub>DDEXT</sub> | External Supply Voltage                                       | Nonautomotive grade models <sup>2</sup>                                                           | 2.25                   | 2.5 or 3.3 | 3.6                    | V    |

| V <sub>DDEXT</sub> | External Supply Voltage                                       | Automotive grade models and +105°C nonautomotive grade models <sup>2</sup>                        | 2.7                    | 3.0 or 3.3 | 3.6                    | V    |

| V <sub>DDRTC</sub> | Real-Time Clock Power<br>Supply Voltage                       |                                                                                                   | 2.25                   |            | 3.6                    | V    |

| V <sub>IH</sub>    | High Level Input Voltage <sup>3, 4</sup>                      | V <sub>DDEXT</sub> = Maximum                                                                      | 2.0                    |            |                        | V    |

| VIHCLKIN           | High Level Input Voltage⁵                                     | V <sub>DDEXT</sub> = Maximum                                                                      | 2.2                    |            |                        | V    |

| V <sub>IH5V</sub>  | 5.0 V Tolerant Pins, High<br>Level Input Voltage <sup>6</sup> |                                                                                                   | $0.7 \times V_{DDEXT}$ |            |                        | V    |

| V <sub>IH5V</sub>  | 5.0 V Tolerant Pins, High<br>Level Input Voltage <sup>7</sup> | V <sub>DDEXT</sub> = Maximum                                                                      | 2.0                    |            |                        | V    |

| V <sub>IL</sub>    | Low Level Input Voltage <sup>3, 8</sup>                       | V <sub>DDEXT</sub> = Minimum                                                                      |                        |            | +0.6                   | V    |

| V <sub>IL5V</sub>  | 5.0 V Tolerant Pins, Low<br>Level Input Voltage <sup>6</sup>  |                                                                                                   |                        |            | $0.3 \times V_{DDEXT}$ | V    |

| V <sub>IL5V</sub>  | 5.0 V Tolerant Pins, Low<br>Level Input Voltage <sup>7</sup>  | V <sub>DDEXT</sub> = Minimum                                                                      |                        |            | +0.8                   | V    |

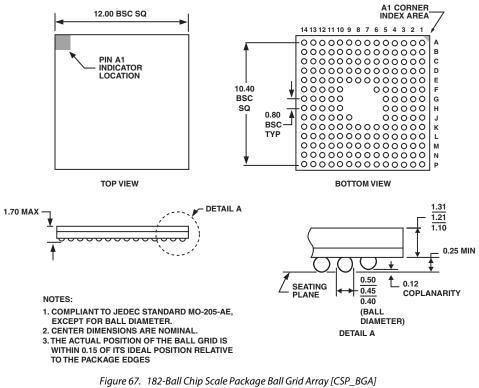

| Tj                 | Junction Temperature                                          | 208-Ball Chip Scale Package Ball Grid Array (CSP_BGA) @<br>$T_{AMBIENT} = -40^{\circ}C$ to +105°C | -40                    |            | +120                   | °C   |

| TJ                 | Junction Temperature                                          | 208-Ball Chip Scale Package Ball Grid Array (CSP_BGA) @<br>$T_{AMBIENT} = -40^{\circ}C$ to +85°C  | -40                    |            | +105                   | °C   |

| TJ                 | Junction Temperature                                          | 208-Ball Chip Scale Package Ball Grid Array (CSP_BGA) @<br>$T_{AMBIENT} = 0^{\circ}C$ to +70°C    | 0                      |            | +95                    | °C   |

| TJ                 | Junction Temperature                                          | 182-Ball Chip Scale Package Ball Grid Array (CSP_BGA) @<br>$T_{AMBIENT} = -40^{\circ}C$ to +85°C  | -40                    |            | +105                   | °C   |

| TJ                 | Junction Temperature                                          | 182-Ball Chip Scale Package Ball Grid Array (CSP_BGA) @<br>$T_{AMBIENT} = 0^{\circ}C$ to +70°C    | 0                      |            | +100                   | °C   |

<sup>1</sup>The regulator can generate V<sub>DDINT</sub> at levels of 0.85 V to 1.2 V with -5% to +10% tolerance, 1.25 V with -4% to +10% tolerance, and 1.3 V with -0% to +10% tolerance. The required V<sub>DDINT</sub> is a function of speed grade and operating frequency. See Table 10, Table 11, and Table 12 for details.

<sup>2</sup> See Ordering Guide on Page 67.

<sup>3</sup> Bidirectional pins (DATA15-0, PF15-0, PG15-0, PH15-0, TFS0, TSCLK0, RSCLK0, RFS0, MDIO) and input pins (BR, ARDY, DR0PRI, DR0SEC, RTXI, TCK, TDI, TMS, TRST, CLKIN, RESET, NMI, and BMODE2-0) of the ADSP-BF534/ADSP-BF536/ADSP-BF537 are 3.3 V-tolerant (always accept up to 3.6 V maximum V<sub>IH</sub>). Voltage compliance (on outputs, V<sub>OH</sub>) is limited by the V<sub>DDEXT</sub> supply voltage.

<sup>4</sup> Parameter value applies to all input and bidirectional pins except CLKIN, SDA, and SCL.

<sup>5</sup> Parameter value applies to CLKIN pin only.

<sup>6</sup> Applies to pins PJ2/SCL and PJ3/SDA which are 5.0 V tolerant (always accept up to 5.5 V maximum V<sub>IH</sub>). Voltage compliance (on outputs, V<sub>OH</sub>) is limited by the V<sub>DDEXT</sub> supply voltage.

<sup>7</sup> Applies to pin PJ4/DR0SEC/CANRX/TACI0 which is 5.0 V tolerant (always accepts up to 5.5 V maximum V<sub>IH</sub>). Voltage compliance (on outputs, V<sub>OH</sub>) is limited by the V<sub>DDEXT</sub> supply voltage.

<sup>8</sup> Parameter value applies to all input and bidirectional pins except SDA and SCL.

## **ELECTRICAL CHARACTERISTICS**

|                              |                                                 |                                                                                         | 30                       | 0 MHz/ | 400 MHz <sup>1</sup> | 500 N                  | /Hz/533 | MHz/600 MHz <sup>2</sup> |      |

|------------------------------|-------------------------------------------------|-----------------------------------------------------------------------------------------|--------------------------|--------|----------------------|------------------------|---------|--------------------------|------|

| Parameter                    |                                                 | Test Conditions                                                                         | Min                      | Тур    | Max                  | Min                    | Тур     | Max                      | Unit |

| V <sub>OH</sub> <sup>3</sup> | High Level<br>Output Voltage                    | $V_{DDEXT} = 2.5 \text{ V}/3.0 \text{ V}/$<br>3.3 V ± 10%,<br>I <sub>OH</sub> = -0.5 mA | V <sub>DDEXT</sub> – 0.5 |        |                      | V <sub>DDEXT</sub> – 0 | .5      |                          | V    |

| V <sub>OH</sub> <sup>4</sup> |                                                 | $V_{\text{DDEXT}} = 3.3 \text{ V} \pm 10\%,$<br>$I_{\text{OH}} = -8 \text{ mA}$         | V <sub>DDEXT</sub> – 0.5 |        |                      | V <sub>DDEXT</sub> – 0 | .5      |                          | v    |

|                              |                                                 | $V_{DDEXT} = 2.5 \text{ V}/3.0 \text{ V} \pm 10\%, I_{OH} = -6 \text{ mA}$              | V <sub>DDEXT</sub> – 0.5 |        |                      | V <sub>DDEXT</sub> – 0 | .5      |                          | V    |

| V <sub>OH</sub> <sup>5</sup> |                                                 | $V_{DDEXT} = 2.5 \text{ V}/3.0 \text{ V}/$<br>3.3 V ± 10%,<br>I <sub>OH</sub> = -2.0 mA | V <sub>DDEXT</sub> – 0.5 |        |                      | V <sub>DDEXT</sub> – 0 | .5      |                          | V    |

| I <sub>OH</sub> <sup>6</sup> | High Level<br>Output Current                    | $V_{OH} = V_{DDEXT} - 0.5 V Min$                                                        |                          |        | -64                  |                        |         | -64                      | mA   |

| I <sub>OH</sub> <sup>7</sup> |                                                 | $V_{OH} = V_{DDEXT} - 0.5 V Min$                                                        |                          |        | -144                 |                        |         | -144                     | mA   |

| V <sub>OL</sub> <sup>3</sup> | Low Level<br>Output Voltage                     | V <sub>DDEXT</sub> = 2.5 V/3.0 V/<br>3.3 V ± 10%,<br>I <sub>OL</sub> = 2.0 mA           |                          |        | 0.4                  |                        |         | 0.4                      | V    |

| V <sub>OL</sub> <sup>4</sup> |                                                 | $V_{\text{DDEXT}} = 3.3 \text{ V} \pm 10\%,$ $I_{\text{OL}} = 8 \text{ mA}$             |                          |        | 0.5                  |                        |         | 0.5                      | V    |

|                              |                                                 | $V_{DDEXT} = 2.5 \text{ V}/3.0 \text{ V} \pm 10\%, I_{OL} = 6 \text{ mA}$               |                          |        | 0.5                  |                        |         | 0.5                      | V    |

| V <sub>OL</sub> <sup>5</sup> |                                                 | $V_{DDEXT} = 2.5 \text{ V}/3.0 \text{ V}/$<br>3.3 V ± 10%,<br>$I_{OL} = 2.0 \text{ mA}$ |                          |        | 0.5                  |                        |         | 0.5                      | V    |

| I <sub>OL</sub> <sup>6</sup> | Low Level<br>Output Current                     | $V_{OL} = 0.5 V Max$                                                                    |                          |        | 64                   |                        |         | 64                       | mA   |

| l <sub>OL</sub> <sup>7</sup> |                                                 | V <sub>OL</sub> = 0.5 V Max                                                             |                          |        | 144                  |                        |         | 144                      | mA   |

| I <sub>IH</sub>              | High Level Input<br>Current <sup>8</sup>        | $V_{DDEXT} = 3.6 V, V_{IN} = 3.6 V$                                                     |                          |        | 10                   |                        |         | 10                       | μΑ   |

| I <sub>IH5V</sub>            | High Level Input<br>Current <sup>9</sup>        | $V_{DDEXT} = 3.6 V, V_{IN} = 5.5 V$                                                     |                          |        | 10                   |                        |         | 10                       | μΑ   |

| I <sub>IL</sub>              | Low Level Input<br>Current <sup>2</sup>         | $V_{DDEXT} = 3.6 V, V_{IN} = 0 V$                                                       |                          |        | 10                   |                        |         | 10                       | μΑ   |

| I <sub>IHP</sub>             | High Level Input<br>Current JTAG <sup>10</sup>  | $V_{DDEXT} = 3.6 V, V_{IN} = 3.6 V$                                                     |                          |        | 50                   |                        |         | 50                       | μΑ   |

| I <sub>оzн</sub>             | Three-State<br>Leakage<br>Current <sup>11</sup> | $V_{DDEXT} = 3.6 V, V_{IN} = 3.6 V$                                                     |                          |        | 10                   |                        |         | 10                       | μΑ   |

| I <sub>ozh5v</sub>           | Three-State<br>Leakage<br>Current <sup>12</sup> | $V_{DDEXT} = 3.6 V, V_{IN} = 5.5 V$                                                     |                          |        | 10                   |                        |         | 10                       | μΑ   |

| I <sub>OZL</sub>             | Three-State<br>Leakage<br>Current⁵              | $V_{DDEXT} = 3.6 \text{ V}, V_{IN} = 0 \text{ V}$                                       |                          |        | 10                   |                        |         | 10                       | μA   |

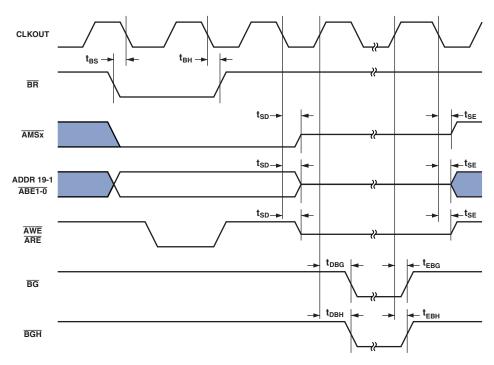

#### **External Port Bus Request and Grant Cycle Timing**

Table 26 and Figure 13 describe external port bus request and bus grant operations.

#### Table 26. External Port Bus Request and Grant Cycle Timing

| Paramete         | r1,2                                             | Min | Мах | Unit |

|------------------|--------------------------------------------------|-----|-----|------|

| Timing Req       | uirements                                        |     |     |      |

| t <sub>BS</sub>  | BR Asserted to CLKOUT Low Setup                  | 4.6 |     | ns   |

| t <sub>BH</sub>  | CLKOUT Low to BR Deasserted Hold Time            | 0.0 |     | ns   |

| Switching        | Characteristics                                  |     |     |      |

| t <sub>SD</sub>  | CLKOUT Low to AMSx, Address, and ARE/AWE Disable |     | 4.5 | ns   |

| t <sub>se</sub>  | CLKOUT Low to AMSx, Address, and ARE/AWE Enable  |     | 4.5 | ns   |

| t <sub>DBG</sub> | CLKOUT High to BG Asserted Setup                 |     | 3.6 | ns   |

| t <sub>EBG</sub> | CLKOUT High to BG Deasserted Hold Time           |     | 3.6 | ns   |

| t <sub>DBH</sub> | CLKOUT High to BGH Asserted Setup                |     | 3.6 | ns   |

| t <sub>EBH</sub> | CLKOUT High to BGH Deasserted Hold Time          |     | 3.6 | ns   |

<sup>1</sup> These timing parameters are based on worst-case operating conditions.

<sup>2</sup> The pad loads for these timing parameters are 20 pF.

Figure 13. External Port Bus Request and Grant Cycle Timing

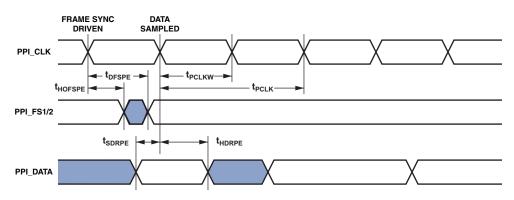

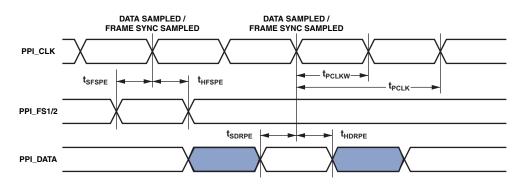

### Parallel Peripheral Interface Timing

Table 29 and Figure 16 on Page 36, Figure 20 on Page 39, and Figure 23 on Page 41 describe parallel peripheral interface operations.

### Table 29. Parallel Peripheral Interface Timing

| Parameter           |                                                  | Min  | Max | Unit |

|---------------------|--------------------------------------------------|------|-----|------|

| Timing Requ         | irements                                         |      |     |      |

| t <sub>PCLKW</sub>  | PPI_CLK Width <sup>1</sup>                       | 6.0  |     | ns   |

| t <sub>PCLK</sub>   | PPI_CLK Period <sup>1</sup>                      | 15.0 |     | ns   |

| Timing Requ         | irements—GP Input and Frame Capture Modes        |      |     |      |

| t <sub>SFSPE</sub>  | External Frame Sync Setup Before PPI_CLK         | 6.7  |     | ns   |

| t <sub>HFSPE</sub>  | External Frame Sync Hold After PPI_CLK           | 1.0  |     | ns   |

| t <sub>SDRPE</sub>  | Receive Data Setup Before PPI_CLK                | 3.5  |     | ns   |

| t <sub>HDRPE</sub>  | Receive Data Hold After PPI_CLK                  | 1.5  |     | ns   |

| Switching Cl        | haracteristics—GP Output and Frame Capture Modes |      |     |      |

| t <sub>DFSPE</sub>  | Internal Frame Sync Delay After PPI_CLK          |      | 8.0 | ns   |

| t <sub>HOFSPE</sub> | Internal Frame Sync Hold After PPI_CLK           | 1.7  |     | ns   |

| t <sub>DDTPE</sub>  | Transmit Data Delay After PPI_CLK                |      | 8.0 | ns   |

| t <sub>HDTPE</sub>  | Transmit Data Hold After PPI_CLK                 | 1.8  |     | ns   |

$^{1}$  PPI\_CLK frequency cannot exceed f<sub>SCLK</sub>/2.

Figure 16. PPI GP Rx Mode with Internal Frame Sync Timing

Figure 17. PPI GP Rx Mode with External Frame Sync Timing

#### Serial Port Timing

Table 30 through Table 33 on Page 41 and Figure 20 on Page 39 through Figure 23 on Page 41 describe serial port operations.

#### Table 30. Serial Ports-External Clock

| Parameter           |                                                                                  | Min                    | Max  | Unit |

|---------------------|----------------------------------------------------------------------------------|------------------------|------|------|

| Timing Requ         | irements                                                                         |                        |      |      |

| t <sub>SFSE</sub>   | TFSx/RFSx Setup Before TSCLKx/RSCLKx <sup>1</sup>                                | 3.0                    |      | ns   |

| t <sub>HFSE</sub>   | TFSx/RFSx Hold After TSCLKx/RSCLKx <sup>1</sup>                                  | 3.0                    |      | ns   |

| t <sub>SDRE</sub>   | Receive Data Setup Before RSCLKx <sup>1</sup>                                    | 3.0                    |      | ns   |

| t <sub>HDRE</sub>   | Receive Data Hold After RSCLKx <sup>1</sup>                                      | 3.0                    |      | ns   |

| t <sub>SCLKEW</sub> | TSCLKx/RSCLKx Width                                                              | 4.5                    |      | ns   |

| t <sub>SCLKE</sub>  | TSCLKx/RSCLKx Period                                                             | 15.0                   |      | ns   |

| t <sub>SUDTE</sub>  | Start-Up Delay From SPORT Enable To First External TFSx <sup>2</sup>             | $4.0 \times t_{SCLKI}$ |      | ns   |

| t <sub>SUDRE</sub>  | Start-Up Delay From SPORT Enable To First External RFSx <sup>2</sup>             | $4.0 \times t_{SCLKI}$ |      | ns   |

| Switching Ch        | paracteristics                                                                   |                        |      |      |

| t <sub>DFSE</sub>   | TFSx/RFSx Delay After TSCLKx/RSCLK (Internally Generated TFSx/RFSx) <sup>3</sup> |                        | 10.0 | ns   |

| t <sub>HOFSE</sub>  | TFSx/RFSx Hold After TSCLKx/RSCLK (Internally Generated TFSx/RFSx) <sup>2</sup>  | 0                      |      | ns   |

| t <sub>DDTE</sub>   | Transmit Data Delay After TSCLKx <sup>2</sup>                                    |                        | 10.0 | ns   |

| t <sub>HDTE</sub>   | Transmit Data Hold After TSCLKx <sup>2</sup>                                     | 0                      |      | ns   |

<sup>1</sup>Referenced to sample edge.

<sup>2</sup> Verified in design but untested. After being enabled, the serial port requires external clock pulses—before the first external frame sync edge—to initialize the serial port. <sup>3</sup> Referenced to drive edge.

#### Table 31. Serial Ports—Internal Clock

|                     |                                                                                   | 2.25 V | ≤ V <sub>DDEXT</sub> < 2.70 V<br>or             | $2.70 V \le V_{DDEXT} \le 3.60 V$<br>and |                                     |      |

|---------------------|-----------------------------------------------------------------------------------|--------|-------------------------------------------------|------------------------------------------|-------------------------------------|------|

|                     |                                                                                   | 0.80 V | $\leq$ V <sub>DDINT</sub> < 0.95 V <sup>1</sup> | 0.95 V                                   | $\leq V_{DDINT} \leq 1.43 V^{2, 3}$ |      |

| Paramet             | Parameter                                                                         |        | Мах                                             | Min                                      | Max                                 | Unit |

| Timing Re           | equirements                                                                       |        |                                                 |                                          |                                     |      |

| t <sub>SFSI</sub>   | TFSx/RFSx Setup Before TSCLKx/RSCLKx <sup>4</sup>                                 | 8.5    |                                                 | 8.0                                      |                                     | ns   |

| t <sub>HFSI</sub>   | TFSx/RFSx Hold After TSCLKx/RSCLKx <sup>4</sup>                                   | -1.5   |                                                 | -1.5                                     |                                     | ns   |

| t <sub>SDRI</sub>   | Receive Data Setup Before RSCLKx <sup>4</sup>                                     | 8.5    |                                                 | 8.0                                      |                                     | ns   |

| t <sub>HDRI</sub>   | Receive Data Hold After RSCLKx <sup>4</sup>                                       | -1.5   |                                                 | -1.5                                     |                                     | ns   |

| Switching           | Characteristics                                                                   |        |                                                 |                                          |                                     |      |

| t <sub>DFSI</sub>   | TFSx/RFSx Delay After TSCLKx/RSCLKx (Internally Generated TFSx/RFSx) <sup>5</sup> |        | 3.0                                             |                                          | 3.0                                 | ns   |

| t <sub>HOFSI</sub>  | TFSx/RFSx Hold After TSCLKx/RSCLKx (Internally Generated TFSx/RFSx) <sup>5</sup>  | -1.0   |                                                 | -1.0                                     |                                     | ns   |

| t <sub>DDTI</sub>   | Transmit Data Delay After TSCLKx⁵                                                 |        | 3.0                                             |                                          | 3.0                                 | ns   |

| t <sub>HDTI</sub>   | Transmit Data Hold After TSCLKx <sup>5</sup>                                      | -1.0   |                                                 | -1.0                                     |                                     | ns   |

| t <sub>SCLKIW</sub> | TSCLKx/RSCLKx Width                                                               | 4.5    |                                                 | 4.5                                      |                                     | ns   |

<sup>1</sup>Applies to all nonautomotive-grade devices when operated within either of these voltage ranges.

<sup>2</sup> Applies to all nonautomotive-grade devices when operated within these voltage ranges.

<sup>3</sup> All automotive-grade devices are within these specifications.

<sup>4</sup>Referenced to sample edge.

<sup>5</sup> Referenced to drive edge.

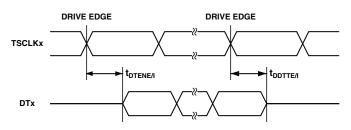

#### Table 32. Serial Ports-Enable and Three-State

| Parameter                 |                                                         | Min  | Мах  | Unit |

|---------------------------|---------------------------------------------------------|------|------|------|

| Switching Characteristics |                                                         |      |      |      |

| t <sub>DTENE</sub>        | Data Enable Delay from External TSCLKx <sup>1</sup>     | 0    |      | ns   |

| t <sub>DDTTE</sub>        | Data Disable Delay from External TSCLKx <sup>1, 2</sup> |      | 10.0 | ns   |

| t <sub>DTENI</sub>        | Data Enable Delay from Internal TSCLKx <sup>1</sup>     | -2.0 |      | ns   |

| t <sub>DDTTI</sub>        | Data Disable Delay from Internal TSCLKx <sup>1, 2</sup> |      | 3.0  | ns   |

<sup>1</sup> Referenced to drive edge.

<sup>2</sup> Applicable to multichannel mode only. TSCLKx is tied to RSCLKx.

Figure 22. Enable and Three-State

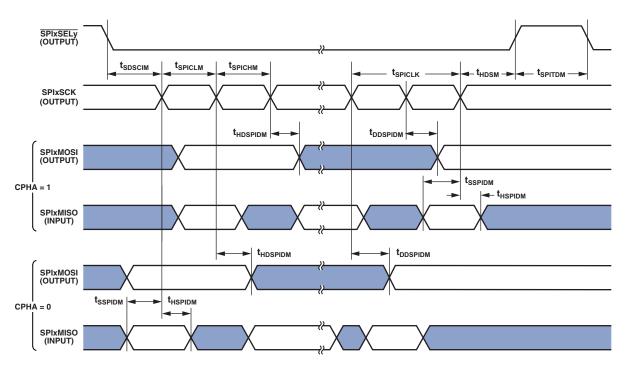

### Serial Peripheral Interface Port—Master Timing

Table 34 and Figure 24 describe SPI port master operations.

### Table 34. Serial Peripheral Interface (SPI) Port—Master Timing

|                     |                                                 | 2.25 V ≤ V <sub>DDEXT</sub> < 2<br>or<br>0.80 V ≤ V <sub>DDINT</sub> < 0. | and                       |      |

|---------------------|-------------------------------------------------|---------------------------------------------------------------------------|---------------------------|------|

| Parameter           |                                                 | Min Max                                                                   | Min Max                   | Unit |

| Timing Re           | equirements                                     |                                                                           |                           |      |

| t <sub>sspidm</sub> | Data Input Valid to SCK Edge (Data Input Setup) | 8.7                                                                       | 7.5                       | ns   |

| t <sub>hspidm</sub> | SCK Sampling Edge to Data Input Invalid         | -1.5                                                                      | -1.5                      | ns   |

| Switching           | Characteristics                                 |                                                                           |                           |      |

| t <sub>sdscim</sub> | SPISELx Low to First SCK Edge                   | $2 \times t_{SCLK} - 1.5$                                                 | $2 \times t_{SCLK} - 1.5$ | ns   |

| t <sub>spichm</sub> | Serial Clock High Period                        | $2 \times t_{SCLK} - 1.5$                                                 | $2 \times t_{SCLK} - 1.5$ | ns   |

| SPICLM              | Serial Clock Low Period                         | $2 \times t_{SCLK} - 1.5$                                                 | $2 \times t_{SCLK} - 1.5$ | ns   |

| SPICLK              | Serial Clock Period                             | $4 \times t_{SCLK} - 1.5$                                                 | $4 \times t_{SCLK} - 1.5$ | ns   |

| HDSM                | Last SCK Edge to SPISELx High                   | $2 \times t_{SCLK} - 1.5$                                                 | $2 \times t_{SCLK} - 1.5$ | ns   |

| SPITDM              | Sequential Transfer Delay                       | $2 \times t_{SCLK} - 1.5$                                                 | $2 \times t_{SCLK} - 1.5$ | ns   |

| DDSPIDM             | SCK Edge to Data Out Valid (Data Out Delay)     | 6                                                                         | 6                         | ns   |

| HDSPIDM             | SCK Edge to Data Out Invalid (Data Out Hold)    | -1.0                                                                      | -1.0                      | ns   |

<sup>1</sup>Applies to all nonautomotive-grade devices when operated within either of these voltage ranges.

<sup>2</sup> Applies to all nonautomotive-grade devices when operated within these voltage ranges.

<sup>3</sup> All automotive-grade devices are within these specifications.

Figure 24. Serial Peripheral Interface (SPI) Port—Master Timing

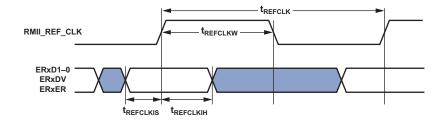

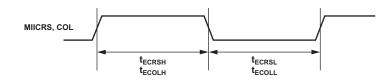

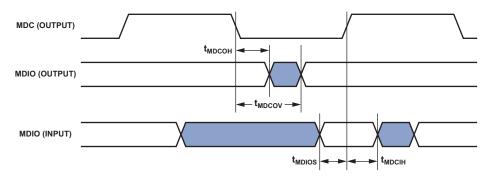

Figure 32. 10/100 Ethernet MAC Controller Timing: RMII Receive Signal

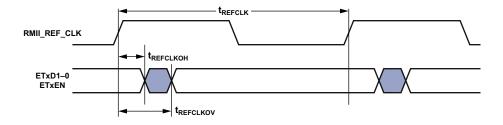

Figure 33. 10/100 Ethernet MAC Controller Timing: RMII Transmit Signal

Figure 34. 10/100 Ethernet MAC Controller Timing: Asynchronous Signal

Figure 35. 10/100 Ethernet MAC Controller Timing: MII Station Management

### THERMAL CHARACTERISTICS

To determine the junction temperature on the application printed circuit board use:

$$T_J = T_{CASE} + (\Psi_{JT} \times P_D)$$

where:

$T_I$  = Junction temperature (°C)

$T_{CASE}$  = Case temperature (°C) measured by customer at top center of package.

$\Psi_{TT}$  = From Table 46

$P_D$  = Power dissipation (see the power dissipation discussion and the tables on Page 27 for the method to calculate P<sub>D</sub>).

Values of  $\theta_{JA}$  are provided for package comparison and printed circuit board design considerations.  $\theta_{JA}$  can be used for a first order approximation of  $T_J$  by the equation:

$$T_I = T_A + (\theta_{IA} \times P_D)$$

where:

$T_A$  = Ambient temperature (°C)

Values of  $\theta_{JC}$  are provided for package comparison and printed circuit board design considerations when an external heat sink is required. Values of  $\theta_{JB}$  are provided for package comparison and printed circuit board design considerations.

In Table 46 through Table 48, airflow measurements comply with JEDEC standards JESD51-2 and JESD51-6, and the junction-to-board measurement complies with JESD51-8. Test board and thermal via design comply with JEDEC standards JESD51-9 (BGA). The junction-to-case measurement complies with MIL-STD-883 (Method 1012.1). All measurements use a 2S2P JEDEC test board.

Industrial applications using the 208-ball BGA package require thermal vias, to an embedded ground plane, in the PCB. Refer to JEDEC standard JESD51-9 for printed circuit board thermal ball land and thermal via design information.

| Table 46. | Thermal | Characteristics | (182-Ball BGA) |

|-----------|---------|-----------------|----------------|

|-----------|---------|-----------------|----------------|

| Parameter            | Condition            | Typical | Unit |

|----------------------|----------------------|---------|------|

| $\theta_{JA}$        | 0 Linear m/s Airflow | 32.80   | °C/W |

| $\theta_{JMA}$       | 1 Linear m/s Airflow | 29.30   | °C/W |

| $\theta_{JMA}$       | 2 Linear m/s Airflow | 28.00   | °C/W |

| $\theta_{JB}$        |                      | 20.10   | °C/W |

| $\theta_{\text{JC}}$ |                      | 7.92    | °C/W |

| $\Psi_{ m JT}$       | 0 Linear m/s Airflow | 0.19    | °C/W |

| $\Psi_{	extsf{JT}}$  | 1 Linear m/s Airflow | 0.35    | °C/W |

| $\Psi_{JT}$          | 2 Linear m/s Airflow | 0.45    | °C/W |

Table 47. Thermal Characteristics (208-Ball BGA withoutThermal Vias in PCB)

| Parameter            | Condition            | Typical | Unit |

|----------------------|----------------------|---------|------|

| $\theta_{JA}$        | 0 Linear m/s Airflow | 23.30   | °C/W |

| $\theta_{JMA}$       | 1 Linear m/s Airflow | 20.20   | °C/W |

| $\theta_{JMA}$       | 2 Linear m/s Airflow | 19.20   | °C/W |

| $\theta_{JB}$        |                      | 13.05   | °C/W |

| $\theta_{\text{JC}}$ |                      | 6.92    | °C/W |

| $\Psi_{ m T}$        | 0 Linear m/s Airflow | 0.18    | °C/W |

| $\Psi_{ m JT}$       | 1 Linear m/s Airflow | 0.27    | °C/W |

| $\Psi_{JT}$          | 2 Linear m/s Airflow | 0.32    | °C/W |

# Table 48. Thermal Characteristics (208-Ball BGA withThermal Vias in PCB)

| Parameter            | Condition            | Typical | Unit |

|----------------------|----------------------|---------|------|

| $\theta_{JA}$        | 0 Linear m/s Airflow | 22.60   | °C/W |

| $\theta_{JMA}$       | 1 Linear m/s Airflow | 19.40   | °C/W |

| $\theta_{JMA}$       | 2 Linear m/s Airflow | 18.40   | °C/W |

| $\theta_{\text{JB}}$ |                      | 13.20   | °C/W |

| $\theta_{\text{JC}}$ |                      | 6.85    | °C/W |

| $\Psi_{ m JT}$       | 0 Linear m/s Airflow | 0.16    | °C/W |

| $\Psi_{ m JT}$       | 1 Linear m/s Airflow | 0.27    | °C/W |

| $\Psi_{\text{JT}}$   | 2 Linear m/s Airflow | 0.32    | °C/W |

Table 50. 182-Ball CSP\_BGA Ball Assignment (Numerically by Ball Number)

| Ball No. | Mnemonic           |

|----------|--------------------|----------|--------------------|----------|--------------------|----------|--------------------|----------|--------------------|

| A1       | V <sub>DDEXT</sub> | C10      | RESET              | F5       | GND                | J14      | ADDR1              | M9       | DATA0              |