Welcome to E-XFL.COM

#### Understanding <u>Embedded - DSP (Digital</u> <u>Signal Processors)</u>

#### Embedded - DSP (Digital Signal Processors) are specialized microprocessors designed to perform complex mathematical computations on digital signals in real-time. Unlike general-purpose processors, DSPs are optimized for high-speed numeric processing tasks, making them ideal for applications that require efficient and precise manipulation of digital data. These processors are fundamental in converting and processing signals in various forms, including audio, video, and communication signals, ensuring that data is accurately interpreted and utilized in embedded systems.

### Applications of <u>Embedded - DSP (Digital</u> <u>Signal Processors)</u>

#### Details

E·XFI

| Product Status          | Active                                                                 |

|-------------------------|------------------------------------------------------------------------|

| Туре                    | Fixed Point                                                            |

| Interface               | CAN, SPI, SSP, TWI, UART                                               |

| Clock Rate              | 533MHz                                                                 |

| Non-Volatile Memory     | External                                                               |

| On-Chip RAM             | 132kB                                                                  |

| Voltage - I/O           | 3.30V                                                                  |

| Voltage - Core          | 1.25V                                                                  |

| Operating Temperature   | -40°C ~ 85°C (TA)                                                      |

| Mounting Type           | Surface Mount                                                          |

| Package / Case          | 208-FBGA, CSPBGA                                                       |

| Supplier Device Package | 208-CSPBGA (17x17)                                                     |

| Purchase URL            | https://www.e-xfl.com/product-detail/analog-devices/adsp-bf537bbcz-5bv |

|                         |                                                                        |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### **BLACKFIN PROCESSOR CORE**

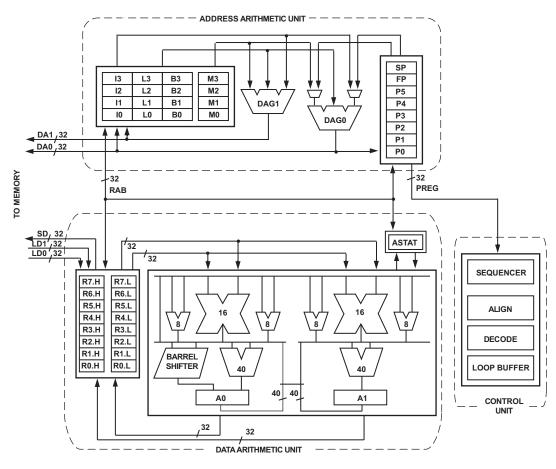

As shown in Figure 2, the Blackfin processor core contains two 16-bit multipliers, two 40-bit accumulators, two 40-bit ALUs, four video ALUs, and a 40-bit shifter. The computation units process 8-, 16-, or 32-bit data from the register file.

The compute register file contains eight 32-bit registers. When performing compute operations on 16-bit operand data, the register file operates as 16 independent 16-bit registers. All operands for compute operations come from the multiported register file and instruction constant fields.

Each MAC can perform a 16-bit by 16-bit multiply in each cycle, accumulating the results into the 40-bit accumulators. Signed and unsigned formats, rounding, and saturation are supported.

The ALUs perform a traditional set of arithmetic and logical operations on 16-bit or 32-bit data. In addition, many special instructions are included to accelerate various signal processing tasks. These include bit operations such as field extract and population count, modulo  $2^{32}$  multiply, divide primitives, saturation and rounding, and sign/exponent detection. The set of video

instructions include byte alignment and packing operations, 16-bit and 8-bit adds with clipping, 8-bit average operations, and 8-bit subtract/absolute value/accumulate (SAA) operations. Also provided are the compare/select and vector search instructions.

For certain instructions, two 16-bit ALU operations can be performed simultaneously on register pairs (a 16-bit high half and 16-bit low half of a compute register). If the second ALU is used, quad 16-bit operations are possible.

The 40-bit shifter can perform shifts and rotates, and is used to support normalization, field extract, and field deposit instructions.

The program sequencer controls the flow of instruction execution, including instruction alignment and decoding. For program flow control, the sequencer supports PC relative and indirect conditional jumps (with static branch prediction), and subroutine calls. Hardware is provided to support zero-overhead looping. The architecture is fully interlocked, meaning that the programmer need not manage the pipeline when executing instructions with data dependencies.

Figure 2. Blackfin Processor Core

### Core Event Controller (CEC)

The CEC supports nine general-purpose interrupts (IVG15–7), in addition to the dedicated interrupt and exception events. Of these general-purpose interrupts, the two lowest priority interrupts (IVG15–14) are recommended to be reserved for software interrupt handlers, leaving seven prioritized interrupt inputs to support the peripherals of the Blackfin processor. Table 2 describes the inputs to the CEC, identifies their names in the event vector table (EVT), and lists their priorities.

#### Table 2. Core Event Controller (CEC)

| Priority       |                              |           |

|----------------|------------------------------|-----------|

| (0 Is Highest) | Event Class                  | EVT Entry |

| 0              | Emulation/Test Control       | EMU       |

| 1              | Reset                        | RST       |

| 2              | Nonmaskable Interrupt        | NMI       |

| 3              | Exception                    | EVX       |

| 4              | Reserved                     | —         |

| 5              | Hardware Error               | IVHW      |

| 6              | Core Timer                   | IVTMR     |

| 7              | General-Purpose Interrupt 7  | IVG7      |

| 8              | General-Purpose Interrupt 8  | IVG8      |

| 9              | General-Purpose Interrupt 9  | IVG9      |

| 10             | General-Purpose Interrupt 10 | IVG10     |

| 11             | General-Purpose Interrupt 11 | IVG11     |

| 12             | General-Purpose Interrupt 12 | IVG12     |

| 13             | General-Purpose Interrupt 13 | IVG13     |

| 14             | General-Purpose Interrupt 14 | IVG14     |

| 15             | General-Purpose Interrupt 15 | IVG15     |

#### System Interrupt Controller (SIC)

The system interrupt controller provides the mapping and routing of events from the many peripheral interrupt sources to the prioritized general-purpose interrupt inputs of the CEC. Although the processor provides a default mapping, the user can alter the mappings and priorities of interrupt events by writing the appropriate values into the interrupt assignment registers (IAR). Table 3 describes the inputs into the SIC and the default mappings into the CEC. Table 3. System Interrupt Controller (SIC)

| Peripheral Interrupt Event                                     | Default<br>Mapping | Peripheral<br>Interrupt ID |

|----------------------------------------------------------------|--------------------|----------------------------|

| PLL Wakeup                                                     | IVG7               | 0                          |

| DMA Error (Generic)                                            | IVG7               | 1                          |

| DMAR0 Block Interrupt                                          | IVG7               | 1                          |

| DMAR1 Block Interrupt                                          | IVG7               | 1                          |

| DMAR0 Overflow Error                                           | IVG7               | 1                          |

| DMAR1 Overflow Error                                           | IVG7               | 1                          |

| CAN Error                                                      | IVG7               | 2                          |

| Ethernet Error (ADSP-BF536 and ADSP-BF537 only)                | IVG7               | 2                          |

| SPORT 0 Error                                                  | IVG7               | 2                          |

| SPORT 1 Error                                                  | IVG7               | 2                          |

| PPI Error                                                      | IVG7               | 2                          |

| SPI Error                                                      | IVG7               | 2                          |

| UART0 Error                                                    | IVG7               | 2                          |

| UART1 Error                                                    | IVG7               | 2                          |

| Real-Time Clock                                                | IVG8               | 3                          |

| DMA Channel 0 (PPI)                                            | IVG8               | 4                          |

| DMA Channel 3 (SPORT 0 Rx)                                     | IVG9               | 5                          |

| DMA Channel 4 (SPORT 0 Tx)                                     | IVG9               | 6                          |

| DMA Channel 5 (SPORT 1 Rx)                                     | IVG9               | 7                          |

| DMA Channel 6 (SPORT 1 Tx)                                     | IVG9               | 8                          |

| TWI                                                            | IVG10              | 9                          |

| DMA Channel 7 (SPI)                                            | IVG10              | 10                         |

| DMA Channel 8 (UARTO Rx)                                       | IVG10              | 11                         |

| DMA Channel 9 (UART0 Tx)                                       | IVG10              | 12                         |

| DMA Channel 10 (UART1 Rx)                                      | IVG10              | 13                         |

| DMA Channel 11 (UART1 Tx)                                      | IVG10              | 14                         |

| CAN Rx                                                         | IVG10              | 15                         |

| CAN Tx                                                         | IVG11              | 16                         |

| DMA Channel 1 (Ethernet Rx,<br>ADSP-BF536 and ADSP-BF537 only) | IVG11              | 17                         |

| Port H Interrupt A                                             | IVG11              | 17                         |

| DMA Channel 2 (Ethernet Tx,<br>ADSP-BF536 and ADSP-BF537 only) | IVG11              | 18                         |

| Port H Interrupt B                                             | IVG11              | 18                         |

| Timer 0                                                        | IVG12              | 19                         |

| Timer 1                                                        | IVG12              | 20                         |

| Timer 2                                                        | IVG12              | 21                         |

| Timer 3                                                        | IVG12              | 22                         |

| Timer 4                                                        | IVG12              | 23                         |

| Timer 5                                                        | IVG12              | 24                         |

| Timer 6                                                        | IVG12              | 25                         |

| Timer 7                                                        | IVG12              | 26                         |

| Port F, G Interrupt A                                          | IVG12              | 27                         |

| Port G Interrupt B                                             | IVG12              | 28                         |

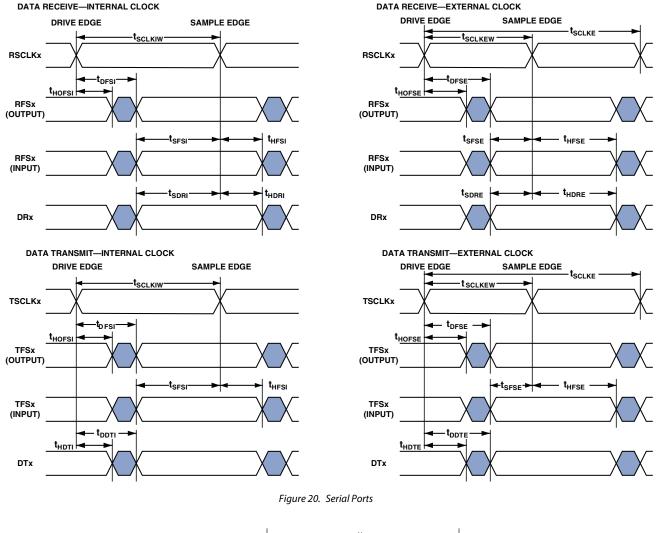

### SERIAL PORTS (SPORTs)

The ADSP-BF534/ADSP-BF536/ADSP-BF537 processors incorporate two dual-channel synchronous serial ports (SPORT0 and SPORT1) for serial and multiprocessor communications. The SPORTs support the following features:

- I<sup>2</sup>S capable operation.

- Bidirectional operation Each SPORT has two sets of independent transmit and receive pins, enabling eight channels of I<sup>2</sup>S stereo audio.

- Buffered (8-deep) transmit and receive ports Each port has a data register for transferring data words to and from other processor components and shift registers for shifting data in and out of the data registers.

- Clocking Each transmit and receive port can either use an external serial clock or generate its own, in frequencies ranging from ( $f_{SCLK}/131,070$ ) Hz to ( $f_{SCLK}/2$ ) Hz.

- Word length Each SPORT supports serial data words from 3 bits to 32 bits in length, transferred most significant bit first or least significant bit first.

- Framing Each transmit and receive port can run with or without frame sync signals for each data word. Frame sync signals can be generated internally or externally, active high or low, and with either of two pulse widths and early or late frame sync.

- Companding in hardware Each SPORT can perform A-law or μ-law companding according to ITU recommendation G.711. Companding can be selected on the transmit and/or receive channel of the SPORT without additional latencies.

- DMA operations with single-cycle overhead Each SPORT can automatically receive and transmit multiple buffers of memory data. The processor can link or chain sequences of DMA transfers between a SPORT and memory.

- Interrupts Each transmit and receive port generates an interrupt upon completing the transfer of a data word or after transferring an entire data buffer, or buffers, through DMA.

- Multichannel capability Each SPORT supports 128 channels out of a 1024-channel window and is compatible with the H.100, H.110, MVIP-90, and HMVIP standards.

### **SERIAL PERIPHERAL INTERFACE (SPI) PORT**

The ADSP-BF534/ADSP-BF536/ADSP-BF537 processors have an SPI-compatible port that enables the processor to communicate with multiple SPI-compatible devices.

The SPI interface uses three pins for transferring data: two data pins (Master Output-Slave Input, MOSI, and Master Input-Slave Output, MISO) and a clock pin (serial clock, SCK). An SPI chip select input pin (SPISS) lets other SPI devices select the processor, and seven SPI chip select output pins (SPISEL7–1) let the processor select other SPI devices. The SPI select pins are reconfigured programmable flag pins. Using these pins, the SPI port provides a full-duplex, synchronous serial interface, which supports both master/slave modes and multimaster environments.

The SPI port's baud rate and clock phase/polarities are programmable, and it has an integrated DMA controller, configurable to support transmit or receive data streams. The SPI's DMA controller can only service unidirectional accesses at any given time.

The SPI port's clock rate is calculated as:

$$SPI Clock Rate = \frac{f_{SCLK}}{2 \times SPI\_BAUD}$$

where the 16-bit SPI\_BAUD register contains a value of 2 to 65,535.

During transfers, the SPI port simultaneously transmits and receives by serially shifting data in and out on its two serial data lines. The serial clock line synchronizes the shifting and sampling of data on the two serial data lines.

### **UART PORTS**

The ADSP-BF534/ADSP-BF536/ADSP-BF537 processors provide two full-duplex universal asynchronous receiver and transmitter (UART) ports, which are fully compatible with PCstandard UARTs. Each UART port provides a simplified UART interface to other peripherals or hosts, supporting full-duplex, DMA-supported, asynchronous transfers of serial data. A UART port includes support for five to eight data bits, one or two stop bits, and none, even, or odd parity. Each UART port supports two modes of operation:

- PIO (programmed I/O) The processor sends or receives data by writing or reading I/O mapped UART registers. The data is double-buffered on both transmit and receive.

- DMA (direct memory access) The DMA controller transfers both transmit and receive data. This reduces the number and frequency of interrupts required to transfer data to and from memory. The UART has two dedicated DMA channels, one for transmit and one for receive. These DMA channels have lower default priority than most DMA channels because of their relatively low service rates.

Each UART port's baud rate, serial data format, error code generation and status, and interrupts are programmable:

- Supporting bit rates ranging from (f<sub>SCLK</sub>/1,048,576) to (f<sub>SCLK</sub>/16) bits per second.

- Supporting data formats from 7 bits to 12 bits per frame.

- Both transmit and receive operations can be configured to generate maskable interrupts to the processor.

The UART port's clock rate is calculated as:

$$UART Clock Rate = \frac{f_{SCLK}}{16 \times UARTx\_Divisor}$$

where the 16-bit *UARTx\_Divisor* comes from the UARTx\_DLH register (most significant 8 bits) and UARTx\_DLL register (least significant 8 bits).

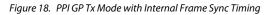

### **Output Mode**

Output mode is used for transmitting video or other data with up to three output frame syncs. Typically, a single frame sync is appropriate for data converter applications, whereas two or three frame syncs could be used for sending video with hardware signaling.

### ITU-R 656 Mode Descriptions

The ITU-R 656 modes of the PPI are intended to suit a wide variety of video capture, processing, and transmission applications. Three distinct submodes are supported:

- 1. Active video only mode

- 2. Vertical blanking only mode

- 3. Entire field mode

### Active Video Mode

Active video only mode is used when only the active video portion of a field is of interest and not any of the blanking intervals. The PPI does not read in any data between the end of active video (EAV) and start of active video (SAV) preamble symbols, or any data present during the vertical blanking intervals. In this mode, the control byte sequences are not stored to memory; they are filtered by the PPI. After synchronizing to the start of Field 1, the PPI ignores incoming samples until it sees an SAV code. The user specifies the number of active video lines per frame (in PPI\_COUNT register).

### Vertical Blanking Interval Mode

In this mode, the PPI only transfers vertical blanking interval (VBI) data.

#### **Entire Field Mode**

In this mode, the entire incoming bit stream is read in through the PPI. This includes active video, control preamble sequences, and ancillary data that may be embedded in horizontal and vertical blanking intervals. Data transfer starts immediately after synchronization to Field 1. Data is transferred to or from the synchronous channels through eight DMA engines that work autonomously from the processor core.

### **DYNAMIC POWER MANAGEMENT**

The ADSP-BF534/ADSP-BF536/ADSP-BF537 processors provide five operating modes, each with a different performance and power profile. In addition, dynamic power management provides the control functions to dynamically alter the processor core supply voltage, further reducing power dissipation. Control of clocking to each of the peripherals also reduces power consumption. See Table 4 for a summary of the power settings for each mode. Also, see Table 16, Table 15 and Table 17.

### Full-On Operating Mode—Maximum Performance

In the full-on mode, the PLL is enabled and is not bypassed, providing capability for maximum operational frequency. This is the power-up default execution state in which maximum performance can be achieved. The processor core and all enabled peripherals run at full speed.

# Active Operating Mode—Moderate Dynamic Power Savings

In the active mode, the PLL is enabled but bypassed. Because the PLL is bypassed, the processor's core clock (CCLK) and system clock (SCLK) run at the input clock (CLKIN) frequency. In this mode, the CLKIN to CCLK multiplier ratio can be changed, although the changes are not realized until the full-on mode is entered. DMA access is available to appropriately configured L1 memories.

In the active mode, it is possible to disable the PLL through the PLL control register (PLL\_CTL). If disabled, the PLL must be re-enabled before transitioning to the full-on or sleep modes.

### Sleep Operating Mode—High Dynamic Power Savings

The sleep mode reduces dynamic power dissipation by disabling the clock to the processor core (CCLK). The PLL and system clock (SCLK), however, continue to operate in this mode. Typically an external event or RTC activity wakes up the processor. When in the sleep mode, asserting wake-up causes the processor to sense the value of the BYPASS bit in the PLL control register (PLL\_CTL). If BYPASS is disabled, the processor transitions to the full on mode. If BYPASS is enabled, the processor transitions to the active mode.

System DMA access to L1 memory is not supported in sleep mode.

|               |                      | PLL      | Core<br>Clock | System<br>Clock | Internal<br>Power     |

|---------------|----------------------|----------|---------------|-----------------|-----------------------|

| Mode          | PLL                  | Bypassed | (CCLK)        | (SCLK)          | (V <sub>DDINT</sub> ) |

| Full On       | Enabled              | No       | Enabled       | Enabled         | On                    |

| Active        | Enabled/<br>Disabled | Yes      | Enabled       | Enabled         | On                    |

| Sleep         | Enabled              | _        | Disabled      | Enabled         | On                    |

| Deep<br>Sleep | Disabled             | _        | Disabled      | Disabled        | On                    |

| Hibernate     | Disabled             | —        | Disabled      | Disabled        | Off                   |

### Table 4. Power Settings

# Deep Sleep Operating Mode—Maximum Dynamic Power Savings

The deep sleep mode maximizes dynamic power savings by disabling the clocks to the processor core (CCLK) and to all synchronous peripherals (SCLK). Asynchronous peripherals, such as the RTC, may still be running but cannot access internal resources or external memory. This powered-down mode can only be exited by assertion of the reset interrupt (RESET) or by an asynchronous interrupt generated by the RTC. When in deep sleep mode, an RTC asynchronous interrupt causes the processor to transition to the active mode. Assertion of RESET while in deep sleep mode causes the processor to transition to the full-on mode.

### Table 9. Pin Descriptions (Continued)

| Pin Name                                                                          | Туре | Function                                                                                                                          | Driver<br>Type <sup>1</sup> |

|-----------------------------------------------------------------------------------|------|-----------------------------------------------------------------------------------------------------------------------------------|-----------------------------|

| <i>Port H: GPIO/10/100 Ethernet MAC</i> (On ADSP-BF534, these pins are GPIO only) |      |                                                                                                                                   |                             |

| PH0 – GPIO/ <i>ETxD0</i>                                                          | I/O  | GPIO/Ethernet MII or RMII Transmit D0                                                                                             | E                           |

| PH1 – GPIO/ <i>ETxD1</i>                                                          | I/O  | GPIO/Ethernet MII or RMII Transmit D1                                                                                             | E                           |

| PH2 – GPIO/ <i>ETxD2</i>                                                          | I/O  | GPIO/Ethernet MII Transmit D2                                                                                                     | E                           |

| PH3 – GPIO/ <i>ETxD3</i>                                                          | I/O  | GPIO/Ethernet MII Transmit D3                                                                                                     | E                           |

| PH4 – GPIO/ <i>ETxEN</i>                                                          | I/O  | GPIO/Ethernet MII or RMII Transmit Enable                                                                                         | E                           |

| PH5 – GPIO/ <i>MII TxCLK/RMII REF_CLK</i>                                         | I/O  | GPIO/Ethernet MII Transmit Clock/RMII Reference Clock                                                                             | E                           |

| PH6 – GPIO/ <i>MII <mark>PHYINT</mark>/RMII <mark>MDINT</mark></i>                | I/O  | GPIO/Ethernet MII PHY Interrupt/RMII Management Data Interrupt (This pin should be pulled high when used as a hibernate wake-up.) | E                           |

| PH7 – GPIO/ <i>COL</i>                                                            | I/O  | GPIO/Ethernet Collision                                                                                                           | E                           |

| PH8 – GPIO/ <i>ERxD0</i>                                                          | I/O  | GPIO/Ethernet MII or RMII Receive D0                                                                                              | E                           |

| PH9 – GPIO/ERxD1                                                                  | I/O  | GPIO/Ethernet MII or RMII Receive D1                                                                                              | E                           |

| PH10 – GPIO/ <i>ERxD2</i>                                                         | I/O  | GPIO/Ethernet MII Receive D2                                                                                                      | E                           |

| PH11 – GPIO/ <i>ERxD3</i>                                                         | I/O  | GPIO/Ethernet MII Receive D3                                                                                                      | E                           |

| PH12 – GPIO/ERxDV/TACLK5                                                          | I/O  | GPIO/Ethernet MII Receive Data Valid/Alternate Timer5 Input Clock                                                                 | E                           |

| PH13 – GPIO/ <i>ERxCLK/TACLK6</i>                                                 | I/O  | GPIO/Ethernet MII Receive Clock/Alternate Timer6 Input Clock                                                                      | E                           |

| PH14 – GPIO/ERxER/TACLK7                                                          | I/O  | GPIO/Ethernet MII or RMII Receive Error/Alternate Timer7 Input Clock                                                              | E                           |

| PH15 – GPIO/ <i>MII CRS/RMII CRS_DV</i>                                           | I/O  | GPIO/Ethernet MII Carrier Sense/Ethernet RMII Carrier Sense and Receive Data<br>Valid                                             | E                           |

| Port J: SPORT0/TWI/SPI Select/CAN                                                 |      |                                                                                                                                   |                             |

| PJO – MDC                                                                         | 0    | Ethernet Management Channel Clock (On ADSP-BF534 processors, do not connect this pin.)                                            | E                           |

| PJ1 – MDIO                                                                        | I/O  | Ethernet Management Channel Serial Data (On ADSP-BF534 processors, tie this pin to ground.)                                       | E                           |

| PJ2 – SCL                                                                         | I/O  | TWI Serial Clock (This pin is an open-drain output and requires a pull-up resistor.)                                              | F                           |

| PJ3 – SDA                                                                         | I/O  | TWI Serial Data (This pin is an open-drain output and requires a pull-up resistor.)                                               | F                           |

| PJ4 – DROSEC/CANRX/TACIO                                                          | I    | SPORT0 Receive Data Secondary/CAN Receive/Timer0 Alternate Input Capture                                                          |                             |

| PJ5 – DTOSEC/CANTX/SPI SSEL7                                                      | 0    | SPORT0 Transmit Data Secondary/CAN Transmit/SPI Slave Select Enable 7                                                             | С                           |

| PJ6 – RSCLK0/TACLK2                                                               | I/O  | SPORT0 Receive Serial Clock/Alternate Timer2 Clock Input                                                                          | D                           |

| PJ7 – RFSO/TACLK3                                                                 | I/O  | SPORT0 Receive Frame Sync/Alternate Timer3 Clock Input                                                                            | С                           |

| PJ8 – DROPRI/TACLK4                                                               | I    | SPORT0 Receive Data Primary/Alternate Timer4 Clock Input                                                                          |                             |

| PJ9 – TSCLK0/TACLK1                                                               | I/O  | SPORT0 Transmit Serial Clock/Alternate Timer1 Clock Input                                                                         | D                           |

| PJ10 – TFSO/SPI SSEL3                                                             | I/O  | SPORT0 Transmit Frame Sync/SPI Slave Select Enable 3                                                                              | С                           |

| PJ11 – DTOPRI/SPI SSEL2                                                           | 0    | SPORT0 Transmit Data Primary/SPI Slave Select Enable 2                                                                            | С                           |

| Real-Time Clock                                                                   |      |                                                                                                                                   |                             |

| RTXI                                                                              | I    | RTC Crystal Input (This pin should be pulled low when not used.)                                                                  |                             |

| RTXO                                                                              | 0    | RTC Crystal Output (Does not three-state in hibernate.)                                                                           |                             |

| JTAG Port                                                                         |      |                                                                                                                                   |                             |

| ТСК                                                                               | I    | JTAG Clock                                                                                                                        |                             |

| TDO                                                                               | 0    | JTAG Serial Data Out                                                                                                              | С                           |

| TDI                                                                               | 1    | JTAG Serial Data In                                                                                                               |                             |

| TMS                                                                               | 1    | JTAG Mode Select                                                                                                                  |                             |

| TRST                                                                              | I    | JTAG Reset (This pin should be pulled low if the JTAG port is not used.)                                                          |                             |

| EMU                                                                               | 0    | Emulation Output                                                                                                                  | С                           |

# Table 9. Pin Descriptions (Continued)

| Pin Name           | Туре | Function                                                                                                                         | Driver<br>Type <sup>1</sup> |

|--------------------|------|----------------------------------------------------------------------------------------------------------------------------------|-----------------------------|

| Clock              |      |                                                                                                                                  |                             |

| CLKIN              | I    | Clock/Crystal Input                                                                                                              |                             |

| XTAL               | 0    | Crystal Output (If CLKBUF is enabled, does not three-state during hibernate.)                                                    |                             |

| CLKBUF             | 0    | Buffered XTAL Output (If enabled, does not three-state during hibernate.)                                                        | Е                           |

| Mode Controls      |      |                                                                                                                                  |                             |

| RESET              | 1    | Reset                                                                                                                            |                             |

| NMI                | 1    | Nonmaskable Interrupt (This pin should be pulled high when not used.)                                                            |                             |

| BMODE2-0           | I    | Boot Mode Strap 2-0 (These pins must be pulled to the state required for the desired boot mode.)                                 |                             |

| Voltage Regulator  |      |                                                                                                                                  |                             |

| VROUT1-0           | 0    | External FET Drive (These pins should be left unconnected when not used and are driven high during hibernate.)                   |                             |

| Supplies           |      |                                                                                                                                  |                             |

| V <sub>DDEXT</sub> | Р    | I/O Power Supply                                                                                                                 |                             |

| V <sub>DDINT</sub> | Р    | Internal Power Supply                                                                                                            |                             |

| V <sub>DDRTC</sub> | Р    | Real-Time Clock Power Supply (This pin should be connected to $V_{DDEXT}$ when not used and should remain powered at all times.) |                             |

| GND                | G    | External Ground                                                                                                                  |                             |

<sup>1</sup>See Output Drive Currents on Page 50 for more information about each driver types.

# **SPECIFICATIONS**

Note that component specifications are subject to change without notice.

## **OPERATING CONDITIONS**

| Param              | eter                                                          | Conditions                                                                                        | Min                    | Nominal    | Max                    | Unit |

|--------------------|---------------------------------------------------------------|---------------------------------------------------------------------------------------------------|------------------------|------------|------------------------|------|

| V <sub>DDINT</sub> | Internal Supply Voltage <sup>1</sup>                          | Nonautomotive 300 MHz, 400 MHz, and 500 MHz speed grade models <sup>2</sup>                       | 0.8                    | 1.2        | 1.32                   | V    |

| V <sub>DDINT</sub> | Internal Supply Voltage <sup>1</sup>                          | Nonautomotive 533 MHz speed grade models <sup>2</sup>                                             | 0.8                    | 1.25       | 1.375                  | v    |

| V <sub>DDINT</sub> | Internal Supply Voltage <sup>1</sup>                          | Nonautomotive 600 MHz speed grade models <sup>2</sup>                                             | 0.8                    | 1.3        | 1.43                   | V    |

| V <sub>DDINT</sub> | Internal Supply Voltage <sup>1</sup>                          | Automotive grade models and +105°C nonautomotive grade models <sup>2</sup>                        | 0.95                   | 1.2        | 1.32                   | V    |

| V <sub>DDEXT</sub> | External Supply Voltage                                       | Nonautomotive grade models <sup>2</sup>                                                           | 2.25                   | 2.5 or 3.3 | 3.6                    | V    |

| V <sub>DDEXT</sub> | External Supply Voltage                                       | Automotive grade models and +105°C nonautomotive grade models <sup>2</sup>                        | 2.7                    | 3.0 or 3.3 | 3.6                    | V    |

| V <sub>DDRTC</sub> | Real-Time Clock Power<br>Supply Voltage                       |                                                                                                   | 2.25                   |            | 3.6                    | V    |

| V <sub>IH</sub>    | High Level Input Voltage <sup>3, 4</sup>                      | V <sub>DDEXT</sub> = Maximum                                                                      | 2.0                    |            |                        | V    |

| VIHCLKIN           | High Level Input Voltage⁵                                     | V <sub>DDEXT</sub> = Maximum                                                                      | 2.2                    |            |                        | V    |

| V <sub>IH5V</sub>  | 5.0 V Tolerant Pins, High<br>Level Input Voltage <sup>6</sup> |                                                                                                   | $0.7 \times V_{DDEXT}$ |            |                        | V    |

| V <sub>IH5V</sub>  | 5.0 V Tolerant Pins, High<br>Level Input Voltage <sup>7</sup> | V <sub>DDEXT</sub> = Maximum                                                                      | 2.0                    |            |                        | V    |

| V <sub>IL</sub>    | Low Level Input Voltage <sup>3, 8</sup>                       | V <sub>DDEXT</sub> = Minimum                                                                      |                        |            | +0.6                   | V    |

| V <sub>IL5V</sub>  | 5.0 V Tolerant Pins, Low<br>Level Input Voltage <sup>6</sup>  |                                                                                                   |                        |            | $0.3 \times V_{DDEXT}$ | V    |

| V <sub>IL5V</sub>  | 5.0 V Tolerant Pins, Low<br>Level Input Voltage <sup>7</sup>  | V <sub>DDEXT</sub> = Minimum                                                                      |                        |            | +0.8                   | V    |

| Tj                 | Junction Temperature                                          | 208-Ball Chip Scale Package Ball Grid Array (CSP_BGA) @<br>$T_{AMBIENT} = -40^{\circ}C$ to +105°C | -40                    |            | +120                   | °C   |

| TJ                 | Junction Temperature                                          | 208-Ball Chip Scale Package Ball Grid Array (CSP_BGA) @<br>$T_{AMBIENT} = -40^{\circ}C$ to +85°C  | -40                    |            | +105                   | °C   |

| TJ                 | Junction Temperature                                          | 208-Ball Chip Scale Package Ball Grid Array (CSP_BGA) @<br>$T_{AMBIENT} = 0^{\circ}C$ to +70°C    | 0                      |            | +95                    | °C   |

| TJ                 | Junction Temperature                                          | 182-Ball Chip Scale Package Ball Grid Array (CSP_BGA) @<br>$T_{AMBIENT} = -40^{\circ}C$ to +85°C  | -40                    |            | +105                   | °C   |

| TJ                 | Junction Temperature                                          | 182-Ball Chip Scale Package Ball Grid Array (CSP_BGA) @<br>$T_{AMBIENT} = 0^{\circ}C$ to +70°C    | 0                      |            | +100                   | °C   |

<sup>1</sup>The regulator can generate V<sub>DDINT</sub> at levels of 0.85 V to 1.2 V with -5% to +10% tolerance, 1.25 V with -4% to +10% tolerance, and 1.3 V with -0% to +10% tolerance. The required V<sub>DDINT</sub> is a function of speed grade and operating frequency. See Table 10, Table 11, and Table 12 for details.

<sup>2</sup> See Ordering Guide on Page 67.

<sup>3</sup> Bidirectional pins (DATA15-0, PF15-0, PG15-0, PH15-0, TFS0, TSCLK0, RSCLK0, RFS0, MDIO) and input pins (BR, ARDY, DR0PRI, DR0SEC, RTXI, TCK, TDI, TMS, TRST, CLKIN, RESET, NMI, and BMODE2-0) of the ADSP-BF534/ADSP-BF536/ADSP-BF537 are 3.3 V-tolerant (always accept up to 3.6 V maximum V<sub>IH</sub>). Voltage compliance (on outputs, V<sub>OH</sub>) is limited by the V<sub>DDEXT</sub> supply voltage.

<sup>4</sup> Parameter value applies to all input and bidirectional pins except CLKIN, SDA, and SCL.

<sup>5</sup> Parameter value applies to CLKIN pin only.

<sup>6</sup> Applies to pins PJ2/SCL and PJ3/SDA which are 5.0 V tolerant (always accept up to 5.5 V maximum V<sub>IH</sub>). Voltage compliance (on outputs, V<sub>OH</sub>) is limited by the V<sub>DDEXT</sub> supply voltage.

<sup>7</sup> Applies to pin PJ4/DR0SEC/CANRX/TACI0 which is 5.0 V tolerant (always accepts up to 5.5 V maximum V<sub>IH</sub>). Voltage compliance (on outputs, V<sub>OH</sub>) is limited by the V<sub>DDEXT</sub> supply voltage.

<sup>8</sup> Parameter value applies to all input and bidirectional pins except SDA and SCL.

# **ELECTRICAL CHARACTERISTICS**

|                              |                                                 |                                                                                         | 30                       | 0 MHz/ | 400 MHz <sup>1</sup> | 500 N                  | /Hz/533 | MHz/600 MHz <sup>2</sup> |      |

|------------------------------|-------------------------------------------------|-----------------------------------------------------------------------------------------|--------------------------|--------|----------------------|------------------------|---------|--------------------------|------|

| Parameter                    |                                                 | Test Conditions                                                                         | Min                      | Тур    | Max                  | Min                    | Тур     | Max                      | Unit |

| V <sub>OH</sub> <sup>3</sup> | High Level<br>Output Voltage                    | $V_{DDEXT} = 2.5 \text{ V}/3.0 \text{ V}/$<br>3.3 V ± 10%,<br>I <sub>OH</sub> = -0.5 mA | V <sub>DDEXT</sub> – 0.5 |        |                      | V <sub>DDEXT</sub> – 0 | .5      |                          | V    |

| V <sub>OH</sub> <sup>4</sup> |                                                 | $V_{\text{DDEXT}} = 3.3 \text{ V} \pm 10\%,$<br>$I_{\text{OH}} = -8 \text{ mA}$         | V <sub>DDEXT</sub> – 0.5 |        |                      | V <sub>DDEXT</sub> – 0 | .5      |                          | v    |

|                              |                                                 | $V_{DDEXT} = 2.5 \text{ V}/3.0 \text{ V} \pm 10\%, I_{OH} = -6 \text{ mA}$              | V <sub>DDEXT</sub> – 0.5 |        |                      | V <sub>DDEXT</sub> – 0 | .5      |                          | V    |

| V <sub>OH</sub> <sup>5</sup> |                                                 | $V_{DDEXT} = 2.5 \text{ V}/3.0 \text{ V}/$<br>3.3 V ± 10%,<br>I <sub>OH</sub> = -2.0 mA | V <sub>DDEXT</sub> – 0.5 |        |                      | V <sub>DDEXT</sub> – 0 | .5      |                          | V    |

| I <sub>OH</sub> <sup>6</sup> | High Level<br>Output Current                    | $V_{OH} = V_{DDEXT} - 0.5 V Min$                                                        |                          |        | -64                  |                        |         | -64                      | mA   |

| I <sub>OH</sub> <sup>7</sup> |                                                 | $V_{OH} = V_{DDEXT} - 0.5 V Min$                                                        |                          |        | -144                 |                        |         | -144                     | mA   |

| V <sub>OL</sub> <sup>3</sup> | Low Level<br>Output Voltage                     | $V_{DDEXT} = 2.5 V/3.0 V/$<br>3.3 V ± 10%,<br>$I_{OL} = 2.0 mA$                         |                          |        | 0.4                  |                        |         | 0.4                      | V    |

| V <sub>OL</sub> <sup>4</sup> |                                                 | $V_{\text{DDEXT}} = 3.3 \text{ V} \pm 10\%,$ $I_{\text{OL}} = 8 \text{ mA}$             |                          |        | 0.5                  |                        |         | 0.5                      | V    |

|                              |                                                 | $V_{DDEXT} = 2.5 \text{ V}/3.0 \text{ V} \pm 10\%, I_{OL} = 6 \text{ mA}$               |                          |        | 0.5                  |                        |         | 0.5                      | V    |

| V <sub>OL</sub> <sup>5</sup> |                                                 | $V_{DDEXT} = 2.5 \text{ V}/3.0 \text{ V}/$<br>3.3 V ± 10%,<br>$I_{OL} = 2.0 \text{ mA}$ |                          |        | 0.5                  |                        |         | 0.5                      | V    |

| I <sub>OL</sub> <sup>6</sup> | Low Level<br>Output Current                     | $V_{OL} = 0.5 V Max$                                                                    |                          |        | 64                   |                        |         | 64                       | mA   |

| l <sub>OL</sub> <sup>7</sup> |                                                 | V <sub>OL</sub> = 0.5 V Max                                                             |                          |        | 144                  |                        |         | 144                      | mA   |

| I <sub>IH</sub>              | High Level Input<br>Current <sup>8</sup>        | $V_{DDEXT} = 3.6 V, V_{IN} = 3.6 V$                                                     |                          |        | 10                   |                        |         | 10                       | μΑ   |

| I <sub>IH5V</sub>            | High Level Input<br>Current <sup>9</sup>        | $V_{DDEXT} = 3.6 V, V_{IN} = 5.5 V$                                                     |                          |        | 10                   |                        |         | 10                       | μΑ   |

| I <sub>IL</sub>              | Low Level Input<br>Current <sup>2</sup>         | $V_{DDEXT} = 3.6 V, V_{IN} = 0 V$                                                       |                          |        | 10                   |                        |         | 10                       | μΑ   |

| I <sub>IHP</sub>             | High Level Input<br>Current JTAG <sup>10</sup>  | $V_{DDEXT} = 3.6 V, V_{IN} = 3.6 V$                                                     |                          |        | 50                   |                        |         | 50                       | μΑ   |

| I <sub>оzн</sub>             | Three-State<br>Leakage<br>Current <sup>11</sup> | $V_{DDEXT} = 3.6 V, V_{IN} = 3.6 V$                                                     |                          |        | 10                   |                        |         | 10                       | μΑ   |

| I <sub>ozh5v</sub>           | Three-State<br>Leakage<br>Current <sup>12</sup> | $V_{DDEXT} = 3.6 V, V_{IN} = 5.5 V$                                                     |                          |        | 10                   |                        |         | 10                       | μΑ   |

| I <sub>OZL</sub>             | Three-State<br>Leakage<br>Current⁵              | $V_{DDEXT} = 3.6 \text{ V}, V_{IN} = 0 \text{ V}$                                       |                          |        | 10                   |                        |         | 10                       | μA   |

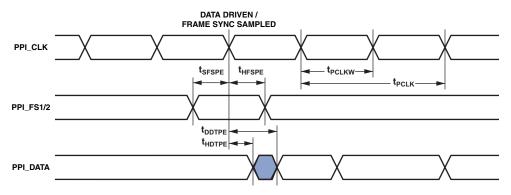

Figure 19. PPI GP Tx Mode with External Frame Sync Timing

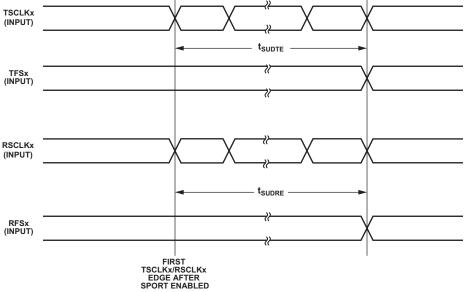

Figure 21. Serial Port Start Up with External Clock and Frame Sync

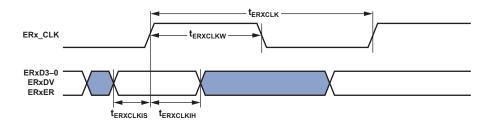

#### 10/100 Ethernet MAC Controller Timing

Table 40 through Table 45 and Figure 30 through Figure 35 describe the 10/100 Ethernet MAC controller operations. This feature is only available on the ADSP-BF536 and ADSP-BF537 processors.

### Table 40. 10/100 Ethernet MAC Controller Timing: MII Receive Signal

| Parameter             | 1                                                     | Min                     | Max                               | Unit |

|-----------------------|-------------------------------------------------------|-------------------------|-----------------------------------|------|

| f <sub>erxclk</sub>   | ERxCLK Frequency (f <sub>SCLK</sub> = SCLK Frequency) | None                    | 25 + 1%<br>f <sub>sCLK</sub> + 1% | MHz  |

| t <sub>ERXCLKW</sub>  | ERxCLK Width (t <sub>ERxCLK</sub> = ERxCLK Period)    | $t_{ERxCLK} 	imes 35\%$ | $t_{ERxCLK} \times 65\%$          | ns   |

| t <sub>ERXCLKIS</sub> | Rx Input Valid to ERxCLK Rising Edge (Data In Setup)  | 7.5                     |                                   | ns   |

| t <sub>erxclkih</sub> | ERxCLK Rising Edge to Rx Input Invalid (Data In Hold) | 7.5                     |                                   | ns   |

<sup>1</sup>MII inputs synchronous to ERxCLK are ERxD3–0, ERxDV, and ERxER.

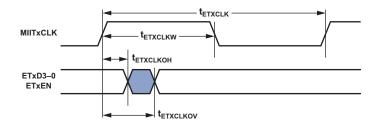

### Table 41. 10/100 Ethernet MAC Controller Timing: MII Transmit Signal

| Parameter <sup>1</sup> |                                                         | Min                      | Мах                      | Unit |

|------------------------|---------------------------------------------------------|--------------------------|--------------------------|------|

| f <sub>etxclk</sub>    | ETxCLK Frequency (f <sub>SCLK</sub> = SCLK Frequency)   | None                     | 25 + 1%                  | MHz  |

|                        |                                                         |                          | f <sub>SCLK</sub> + 1%   |      |

| t <sub>ETXCLKW</sub>   | ETxCLK Width (t <sub>ETXCLK</sub> = ETxCLK Period)      | $t_{ETxCLK} \times 35\%$ | $t_{ETxCLK} \times 65\%$ | ns   |

| t <sub>ETXCLKOV</sub>  | ETxCLK Rising Edge to Tx Output Valid (Data Out Valid)  |                          | 20                       | ns   |

| t <sub>etxclkoh</sub>  | ETxCLK Rising Edge to Tx Output Invalid (Data Out Hold) | 0                        |                          | ns   |

<sup>1</sup> MII outputs synchronous to ETxCLK are ETxD3–0.

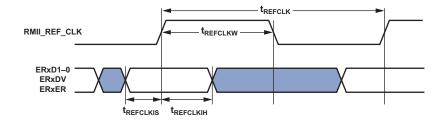

### Table 42. 10/100 Ethernet MAC Controller Timing: RMII Receive Signal

| Parameter <sup>1</sup> |                                                             | Min                     | Max                       | Unit |

|------------------------|-------------------------------------------------------------|-------------------------|---------------------------|------|

| f <sub>REFCLK</sub>    | REF_CLK Frequency (f <sub>SCLK</sub> = SCLK Frequency)      | None                    | 50 + 1%                   | MHz  |

|                        |                                                             |                         | $2 \times f_{SCLK} + 1\%$ |      |

| t <sub>REFCLKW</sub>   | REF_CLK Width (t <sub>REFCLK</sub> = REFCLK Period)         | $t_{REFCLK} 	imes 35\%$ | $t_{REFCLK} \times 65\%$  | ns   |

| t <sub>REFCLKIS</sub>  | Rx Input Valid to RMII REF_CLK Rising Edge (Data In Setup)  | 4                       |                           | ns   |

| t <sub>refclkih</sub>  | RMII REF_CLK Rising Edge to Rx Input Invalid (Data In Hold) | 2                       |                           | ns   |

<sup>1</sup> RMII inputs synchronous to RMII REF\_CLK are ERxD1–0, RMII CRS\_DV, and ERxER.

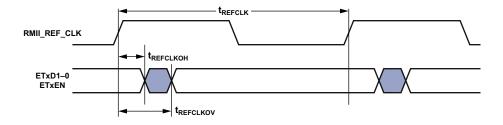

#### Table 43. 10/100 Ethernet MAC Controller Timing: RMII Transmit Signal

| Parameter <sup>1</sup> |                                                               | Min | Max | Unit |

|------------------------|---------------------------------------------------------------|-----|-----|------|

| t <sub>REFCLKOV</sub>  | RMII REF_CLK Rising Edge to Tx Output Valid (Data Out Valid)  |     | 7.5 | ns   |

| t <sub>REFCLKOH</sub>  | RMII REF_CLK Rising Edge to Tx Output Invalid (Data Out Hold) | 2   |     | ns   |

<sup>1</sup> RMII outputs synchronous to RMII REF\_CLK are ETxD1–0.

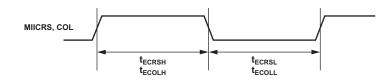

#### Table 44. 10/100 Ethernet MAC Controller Timing: MII/RMII Asynchronous Signal

| Parameter <sup>1,</sup> | ,2                   | Min Max                                                                                     | Unit |

|-------------------------|----------------------|---------------------------------------------------------------------------------------------|------|

| t <sub>ECOLH</sub>      | COL Pulse Width High | t <sub>ETxCLK</sub> × 1.5                                                                   | ns   |

|                         |                      | $\begin{array}{l} t_{\text{ETxCLK}} \times 1.5 \\ t_{\text{ERxCLK}} \times 1.5 \end{array}$ | ns   |

| t <sub>ECOLL</sub>      | COL Pulse Width Low  | $t_{ETxCLK} \times 1.5$                                                                     | ns   |

|                         |                      | $\begin{array}{l} t_{\text{ETXCLK}} \times 1.5 \\ t_{\text{ERXCLK}} \times 1.5 \end{array}$ | ns   |

| t <sub>ECRSH</sub>      | CRS Pulse Width High | $t_{ETxCLK} \times 1.5$                                                                     | ns   |

| t <sub>ECRSL</sub>      | CRS Pulse Width Low  | $t_{ETxCLK} \times 1.5$                                                                     | ns   |

<sup>1</sup>MII/RMII asynchronous signals are COL, CRS. These signals are applicable in both MII and RMII modes. The asynchronous COL input is synchronized separately to both the ETxCLK and the ERxCLK, and must have a minimum pulse width high or low at least 1.5 times the period of the slower of the two clocks.

<sup>2</sup> The asynchronous CRS input is synchronized to the ETxCLK, and must have a minimum pulse width high or low at least 1.5 times the period of ETxCLK.

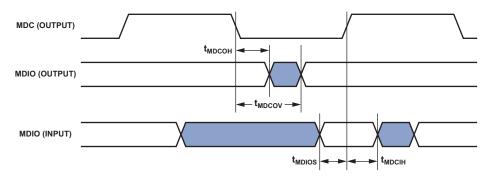

| Table 45. | 10/100 Ethernet MAC Control | ler Timing: MII Stat | ion Management |

|-----------|-----------------------------|----------------------|----------------|

|           |                             |                      |                |

| Parameter <sup>1</sup> |                                                | Min | Мах | Unit |

|------------------------|------------------------------------------------|-----|-----|------|

| t <sub>MDIOS</sub>     | MDIO Input Valid to MDC Rising Edge (Setup)    | 10  |     | ns   |

| t <sub>MDCIH</sub>     | MDC Rising Edge to MDIO Input Invalid (Hold)   | 10  |     | ns   |

| t <sub>MDCOV</sub>     | MDC Falling Edge to MDIO Output Valid          | 25  |     | ns   |

| t <sub>MDCOH</sub>     | MDC Falling Edge to MDIO Output Invalid (Hold) | -1  |     | ns   |

<sup>1</sup> MDC/MDIO is a 2-wire serial bidirectional port for controlling one or more external PHYs. MDC is an output clock whose minimum period is programmable as a multiple of the system clock SCLK. MDIO is a bidirectional data line.

*Figure 30.* 10/100 *Ethernet MAC Controller Timing: MII Receive Signal*

Figure 31. 10/100 Ethernet MAC Controller Timing: Mll Transmit Signal

Figure 32. 10/100 Ethernet MAC Controller Timing: RMII Receive Signal

Figure 33. 10/100 Ethernet MAC Controller Timing: RMII Transmit Signal

Figure 34. 10/100 Ethernet MAC Controller Timing: Asynchronous Signal

Figure 35. 10/100 Ethernet MAC Controller Timing: MII Station Management

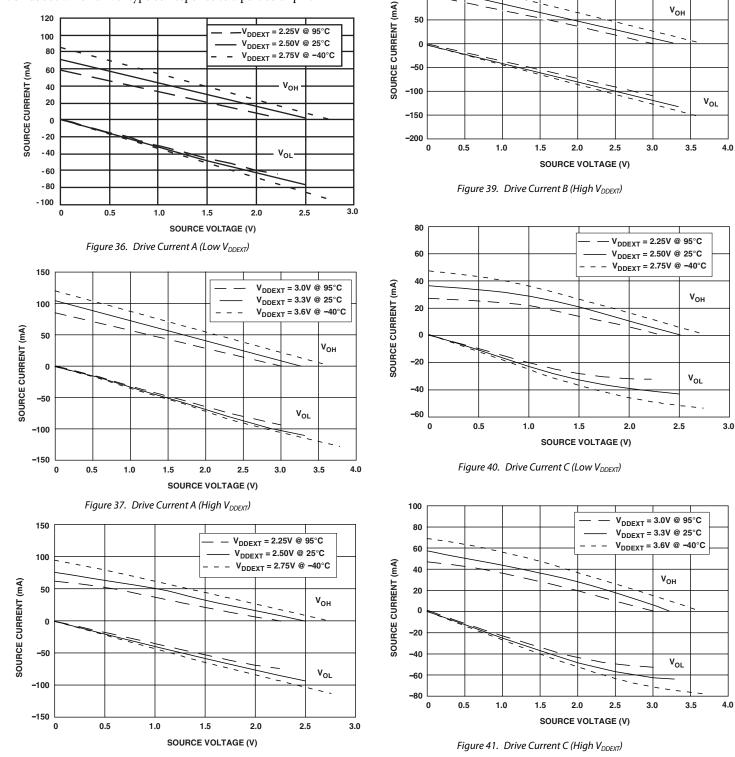

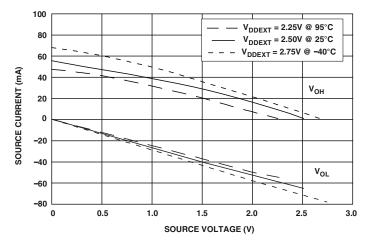

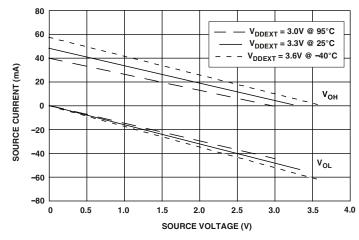

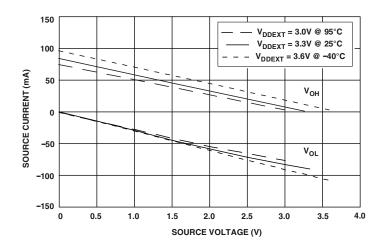

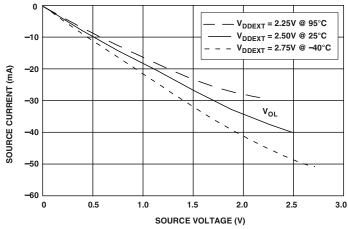

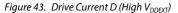

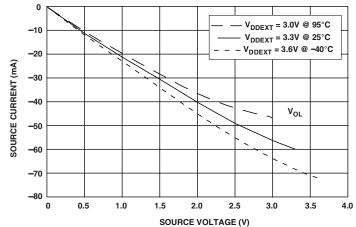

### **OUTPUT DRIVE CURRENTS**

Figure 36 through Figure 47 show typical current-voltage characteristics for the output drivers of the processors. The curves represent the current drive capability of the output drivers as a function of output voltage. See Table 9 on Page 19 for information about which driver type corresponds to a particular pin.

200

150

100

V<sub>DDEXT</sub> = 3.0V @ 95°C

V<sub>DDEXT</sub> = 3.3V @ 25°C

V<sub>DDEXT</sub> = 3.6V @ -40°C

Figure 38. Drive Current B (Low V<sub>DDEXT</sub>)

Figure 42. Drive Current D (Low V<sub>DDEXT</sub>)

Figure 45. Drive Current E (High V<sub>DDEXT</sub>)

Figure 44. Drive Current E (Low V<sub>DDEXT</sub>)

Figure 46. Drive Current F (Low V<sub>DDEXT</sub>)

Figure 47. Drive Current F (High V<sub>DDEXT</sub>)

### **TEST CONDITIONS**

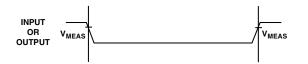

All timing parameters appearing in this data sheet were measured under the conditions described in this section. Figure 48 shows the measurement point for ac measurements (other than output enable/disable). The measurement point is  $V_{MEAS} = V_{DDEXT}/2$ .

Figure 48. Voltage Reference Levels for AC Measurements (Except Output Enable/Disable)

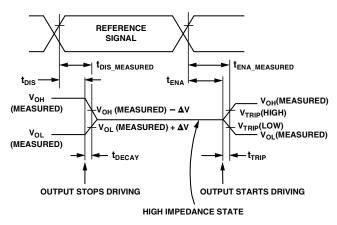

### **Output Enable Time**

Output pins are considered to be enabled when they have made a transition from a high impedance state to the point when they start driving. The output enable time  $t_{ENA}$  is the interval from the point when a reference signal reaches a high or low voltage level to the point when the output starts driving as shown in the Output Enable/Disable diagram (Figure 49). The time  $t_{ENA\_MEA}$ . SURED is the interval from when the reference signal switches to when the output voltage reaches 2.0 V (output high) or 1.0 V (output low). Time  $t_{TRIP}$  is the interval from when the output starts driving to when the output reaches the 1.0 V or 2.0 V trip voltage. Time  $t_{ENA}$  is calculated as shown in the equation:

$$t_{ENA} = t_{ENA\_MEASURED} - t_{TRIP}$$

If multiple pins (such as the data bus) are enabled, the measurement value is that of the first pin to start driving.

### **Output Disable Time**

Output pins are considered to be disabled when they stop driving, go into a high impedance state, and start to decay from their output high or low voltage. The time for the voltage on the bus to decay by  $\Delta V$  is dependent on the capacitive load, C<sub>L</sub>, and the load current, I<sub>L</sub>. This decay time can be approximated by the equation:

$$t_{DECAY} = (C_L \Delta V) / I_L$$

The output disable time  $t_{DIS}$  is the difference between  $t_{DIS\_MEA-SURED}$  and  $t_{DECAY}$  as shown in Figure 49. The time  $t_{DIS\_MEASURED}$  is the interval from when the reference signal switches to when the output voltage decays  $\Delta V$  from the measured output-high or output-low voltage. The time  $t_{DECAY}$  is calculated with the test loads  $C_L$  and  $I_L$ , and with  $\Delta V$  equal to 0.5 V.

Figure 49. Output Enable/Disable

### **Example System Hold Time Calculation**

To determine the data output hold time in a particular system, first calculate  $t_{DECAY}$  using the equation given above. Choose  $\Delta V$  to be the difference between the processor's output voltage and the input threshold for the device requiring the hold time. A typical  $\Delta V$  is 0.4 V.  $C_L$  is the total bus capacitance (per data line), and  $I_L$  is the total leakage or three-state current (per data line). The hold time is  $t_{DECAY}$  plus the minimum disable time (for example,  $t_{DSDAT}$  for an SDRAM write cycle).

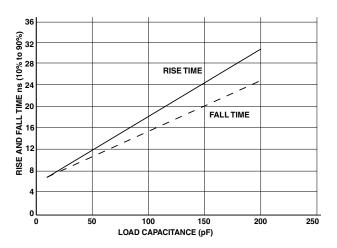

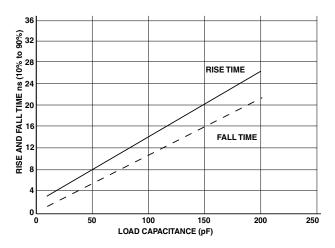

Figure 59. Typical Output Delay or Hold for Driver E at V<sub>DDEXT</sub> Min

Figure 60. Typical Output Delay or Hold for Driver E at  $V_{DDEXT}$  Max

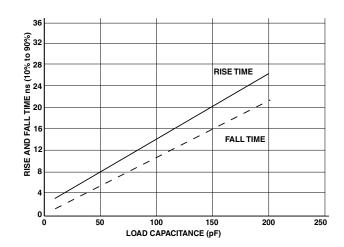

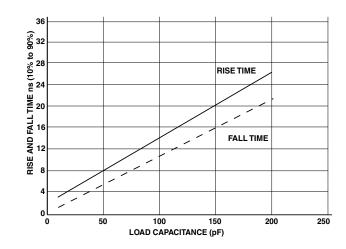

Figure 61. Typical Output Delay or Hold for Driver F at  $V_{DDEXT}$  Min

Figure 62. Typical Output Delay or Hold for Driver F at  $V_{DDEXT}$  Max

### THERMAL CHARACTERISTICS

To determine the junction temperature on the application printed circuit board use:

$$T_J = T_{CASE} + (\Psi_{JT} \times P_D)$$

where:

$T_I$  = Junction temperature (°C)

$T_{CASE}$  = Case temperature (°C) measured by customer at top center of package.

$\Psi_{TT}$  = From Table 46

$P_D$  = Power dissipation (see the power dissipation discussion and the tables on Page 27 for the method to calculate P<sub>D</sub>).

Values of  $\theta_{JA}$  are provided for package comparison and printed circuit board design considerations.  $\theta_{JA}$  can be used for a first order approximation of  $T_J$  by the equation:

$$T_I = T_A + (\theta_{IA} \times P_D)$$

where:

$T_A$  = Ambient temperature (°C)

Values of  $\theta_{JC}$  are provided for package comparison and printed circuit board design considerations when an external heat sink is required. Values of  $\theta_{JB}$  are provided for package comparison and printed circuit board design considerations.

In Table 46 through Table 48, airflow measurements comply with JEDEC standards JESD51-2 and JESD51-6, and the junction-to-board measurement complies with JESD51-8. Test board and thermal via design comply with JEDEC standards JESD51-9 (BGA). The junction-to-case measurement complies with MIL-STD-883 (Method 1012.1). All measurements use a 2S2P JEDEC test board.

Industrial applications using the 208-ball BGA package require thermal vias, to an embedded ground plane, in the PCB. Refer to JEDEC standard JESD51-9 for printed circuit board thermal ball land and thermal via design information.

| Table 46. | Thermal | Characteristics | (182-Ball BGA) |

|-----------|---------|-----------------|----------------|

|-----------|---------|-----------------|----------------|

| Parameter            | Condition            | Typical | Unit |

|----------------------|----------------------|---------|------|

| $\theta_{JA}$        | 0 Linear m/s Airflow | 32.80   | °C/W |

| $\theta_{JMA}$       | 1 Linear m/s Airflow | 29.30   | °C/W |

| $\theta_{JMA}$       | 2 Linear m/s Airflow | 28.00   | °C/W |

| $\theta_{JB}$        |                      | 20.10   | °C/W |

| $\theta_{\text{JC}}$ |                      | 7.92    | °C/W |

| $\Psi_{ m JT}$       | 0 Linear m/s Airflow | 0.19    | °C/W |

| $\Psi_{	extsf{JT}}$  | 1 Linear m/s Airflow | 0.35    | °C/W |

| $\Psi_{JT}$          | 2 Linear m/s Airflow | 0.45    | °C/W |

Table 47. Thermal Characteristics (208-Ball BGA withoutThermal Vias in PCB)

| Parameter            | Condition            | Typical | Unit |

|----------------------|----------------------|---------|------|

| $\theta_{JA}$        | 0 Linear m/s Airflow | 23.30   | °C/W |

| $\theta_{JMA}$       | 1 Linear m/s Airflow | 20.20   | °C/W |

| $\theta_{JMA}$       | 2 Linear m/s Airflow | 19.20   | °C/W |

| $\theta_{JB}$        |                      | 13.05   | °C/W |

| $\theta_{\text{JC}}$ |                      | 6.92    | °C/W |

| $\Psi_{ m T}$        | 0 Linear m/s Airflow | 0.18    | °C/W |

| $\Psi_{ m JT}$       | 1 Linear m/s Airflow | 0.27    | °C/W |

| $\Psi_{JT}$          | 2 Linear m/s Airflow | 0.32    | °C/W |

# Table 48. Thermal Characteristics (208-Ball BGA withThermal Vias in PCB)

| Parameter            | Condition            | Typical | Unit |

|----------------------|----------------------|---------|------|

| $\theta_{JA}$        | 0 Linear m/s Airflow | 22.60   | °C/W |

| $\theta_{JMA}$       | 1 Linear m/s Airflow | 19.40   | °C/W |

| $\theta_{JMA}$       | 2 Linear m/s Airflow | 18.40   | °C/W |

| $\theta_{JB}$        |                      | 13.20   | °C/W |

| $\theta_{\text{JC}}$ |                      | 6.85    | °C/W |

| $\Psi_{ m JT}$       | 0 Linear m/s Airflow | 0.16    | °C/W |

| $\Psi_{ m JT}$       | 1 Linear m/s Airflow | 0.27    | °C/W |

| $\Psi_{ m JT}$       | 2 Linear m/s Airflow | 0.32    | °C/W |

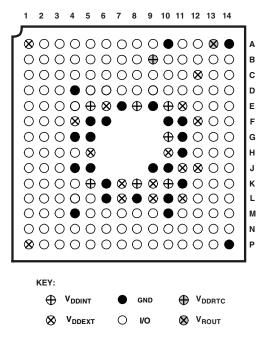

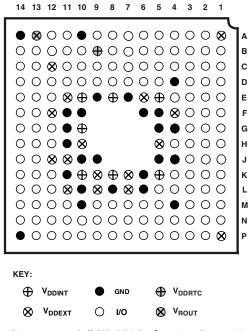

Figure 63 shows the top view of the CSP\_BGA ball configuration. Figure 64 shows the bottom view of the CSP\_BGA ball configuration.

*Figure 63.* 182-Ball CSP\_BGA Configuration (Top View)

Figure 64. 182-Ball CSP\_BGA Configuration (Bottom View)

# **AUTOMOTIVE PRODUCTS**

The ADBF534W model is available with controlled manufacturing to support the quality and reliability requirements of automotive applications. Note that these automotive models may have specifications that differ from the commercial models and designers should review the Specifications section of this data sheet carefully. Only the automotive grade products shown in Table 53 are available for use in automotive applications. Contact your local ADI account representative for specific product ordering information and to obtain the specific Automotive Reliability reports for these models.

### Table 53. Automotive Products

| Product Family <sup>1,2</sup> | Temperature Range <sup>3</sup> | Speed Grade (Max) | Package Description | Package<br>Option |

|-------------------------------|--------------------------------|-------------------|---------------------|-------------------|

| ADBF534WBBCZ4Axx              | -40°C to +85°C                 | 400 MHz           | 182-Ball CSP_BGA    | BC-182            |

| ADBF534WBBCZ4Bxx              | -40°C to +85°C                 | 400 MHz           | 208-Ball CSP_BGA    | BC-208-2          |

| ADBF534WYBCZ4Bxx              | -40°C to +105°C                | 400 MHz           | 208-Ball CSP_BGA    | BC-208-2          |

$^{1}$ Z = RoHS compliant part.

<sup>2</sup> xx denotes silicon revision.

<sup>3</sup>Referenced temperature is ambient temperature.