Welcome to E-XFL.COM

#### Understanding <u>Embedded - DSP (Digital</u> <u>Signal Processors)</u>

#### Embedded - DSP (Digital Signal Processors) are specialized microprocessors designed to perform complex mathematical computations on digital signals in real-time. Unlike general-purpose processors, DSPs are optimized for high-speed numeric processing tasks, making them ideal for applications that require efficient and precise manipulation of digital data. These processors are fundamental in converting and processing signals in various forms, including audio, video, and communication signals, ensuring that data is accurately interpreted and utilized in embedded systems.

#### Applications of <u>Embedded - DSP (Digital</u> <u>Signal Processors)</u>

### Details

E·XFl

| Product Status          | Active                                                                 |

|-------------------------|------------------------------------------------------------------------|

| Туре                    | Fixed Point                                                            |

| Interface               | CAN, SPI, SSP, TWI, UART                                               |

| Clock Rate              | 600MHz                                                                 |

| Non-Volatile Memory     | External                                                               |

| On-Chip RAM             | 132kB                                                                  |

| Voltage - I/O           | 3.30V                                                                  |

| Voltage - Core          | 1.30V                                                                  |

| Operating Temperature   | 0°C ~ 70°C (TA)                                                        |

| Mounting Type           | Surface Mount                                                          |

| Package / Case          | 182-LFBGA, CSPBGA                                                      |

| Supplier Device Package | 182-CSPBGA (12x12)                                                     |

| Purchase URL            | https://www.e-xfl.com/product-detail/analog-devices/adsp-bf537kbcz-6av |

|                         |                                                                        |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### TABLE OF CONTENTS

| F | eatures                                | . 1 |

|---|----------------------------------------|-----|

| N | 1emory                                 | . 1 |

| P | eripherals                             | . 1 |

| G | General Description                    | . 3 |

|   | Portable Low Power Architecture        | . 3 |

|   | System Integration                     | . 3 |

|   | Blackfin Processor Peripherals         | . 3 |

|   | Blackfin Processor Core                | . 4 |

|   | Memory Architecture                    | . 5 |

|   | DMA Controllers                        | . 8 |

|   | Real-Time Clock                        | . 9 |

|   | Watchdog Timer                         | . 9 |

|   | Timers                                 | . 9 |

|   | Serial Ports (SPORTs)                  | 10  |

|   | Serial Peripheral Interface (SPI) Port |     |

|   | UART Ports                             | 10  |

|   | Controller Area Network (CAN)          | 11  |

|   | TWI Controller Interface               | 11  |

|   | 10/100 Ethernet MAC                    | 11  |

|   | Ports                                  | 12  |

|   | Parallel Peripheral Interface (PPI)    | 12  |

|   | Dynamic Power Management               | 13  |

|   | Voltage Regulation                     | 14  |

|   | Clock Signals                          | 15  |

|   |                                        |     |

### Booting Modes ..... 16 Instruction Set Description ...... 17 Development Tools ..... 17 Additional Information ...... 18 Related Signal Chains ..... 18 Operating Conditions ..... 23 Absolute Maximum Ratings ...... 29 Timing Specifications ...... 30 Output Drive Currents ...... 50 Thermal Characteristics ...... 56 182-Ball CSP\_BGA Ball Assignment ..... 57 208-Ball CSP\_BGA Ball Assignment ...... 60

### **REVISION HISTORY**

| 2/14—Rev. I to Rev. J                                                           |    |

|---------------------------------------------------------------------------------|----|

| Corrected typographical error from Three 16-bit MACs to 16-bit MACs in Features |    |

| Updated Development Tools                                                       | 17 |

| Added t <sub>HDRE</sub> parameter to Serial Port Timing                         | 38 |

| Added footnotes in Serial Port Timing                                           | 38 |

The address arithmetic unit provides two addresses for simultaneous dual fetches from memory. It contains a multiported register file consisting of four sets of 32-bit index, modify, length, and base registers (for circular buffering), and eight additional 32-bit pointer registers (for C-style indexed stack manipulation).

Blackfin processors support a modified Harvard architecture in combination with a hierarchical memory structure. Level 1 (L1) memories are those that typically operate at the full processor speed with little or no latency. At the L1 level, the instruction memory holds instructions only. The two data memories hold data, and a dedicated scratchpad data memory stores stack and local variable information.

In addition, multiple L1 memory blocks are provided, offering a configurable mix of SRAM and cache. The memory management unit (MMU) provides memory protection for individual tasks that may be operating on the core and can protect system registers from unintended access.

The architecture provides three modes of operation: user mode, supervisor mode, and emulation mode. User mode has restricted access to certain system resources, thus providing a protected software environment, while supervisor mode has unrestricted access to the system and core resources.

The Blackfin processor instruction set has been optimized so that 16-bit opcodes represent the most frequently used instructions, resulting in excellent compiled code density. Complex DSP instructions are encoded into 32-bit opcodes, representing fully featured multifunction instructions. Blackfin processors support a limited multi-issue capability, where a 32-bit instruction can be issued in parallel with two 16-bit instructions, allowing the programmer to use many of the core resources in a single instruction cycle.

The Blackfin processor assembly language uses an algebraic syntax for ease of coding and readability. The architecture has been optimized for use in conjunction with the C/C++ compiler, resulting in fast and efficient software implementations.

### MEMORY ARCHITECTURE

The ADSP-BF534/ADSP-BF536/ADSP-BF537 processors view memory as a single unified 4G byte address space, using 32-bit addresses. All resources, including internal memory, external memory, and I/O control registers, occupy separate sections of this common address space. The memory portions of this address space are arranged in a hierarchical structure to provide a good cost/performance balance of some very fast, low latency on-chip memory as cache or SRAM, and larger, lower cost, and performance off-chip memory systems. (See Figure 3).

The on-chip L1 memory system is the highest performance memory available to the Blackfin processor. The off-chip memory system, accessed through the external bus interface unit (EBIU), provides expansion with SDRAM, flash memory, and SRAM, optionally accessing up to 516M bytes of physical memory. The memory DMA controller provides high bandwidth datamovement capability. It can perform block transfers of code or data between the internal memory and the external memory spaces.

#### Internal (On-Chip) Memory

The ADSP-BF534/ADSP-BF536/ADSP-BF537 processors have three blocks of on-chip memory providing high-bandwidth access to the core.

The first block is the L1 instruction memory, consisting of 64K bytes SRAM, of which 16K bytes can be configured as a four-way set-associative cache. This memory is accessed at full processor speed.

The second on-chip memory block is the L1 data memory, consisting of up to two banks of up to 32K bytes each. Each memory bank is configurable, offering both cache and SRAM functionality. This memory block is accessed at full processor speed.

The third memory block is a 4K byte scratchpad SRAM, which runs at the same speed as the L1 memories, but is only accessible as data SRAM, and cannot be configured as cache memory.

### External (Off-Chip) Memory

External memory is accessed via the EBIU. This 16-bit interface provides a glueless connection to a bank of synchronous DRAM (SDRAM) as well as up to four banks of asynchronous memory devices including flash, EPROM, ROM, SRAM, and memory mapped I/O devices.

The PC133-compliant SDRAM controller can be programmed to interface to up to 128M bytes of SDRAM. A separate row can be open for each SDRAM internal bank, and the SDRAM controller supports up to 4 internal SDRAM banks, improving overall performance.

The asynchronous memory controller can be programmed to control up to four banks of devices with very flexible timing parameters for a wide variety of devices. Each bank occupies a 1M byte segment regardless of the size of the devices used, so that these banks are only contiguous if each is fully populated with 1M byte of memory.

### I/O Memory Space

The ADSP-BF534/ADSP-BF536/ADSP-BF537 processors do not define a separate I/O space. All resources are mapped through the flat 32-bit address space. On-chip I/O devices have their control registers mapped into memory-mapped registers (MMRs) at addresses near the top of the 4G byte address space. These are separated into two smaller blocks, one which contains the control MMRs for all core functions, and the other which contains the registers needed for setup and control of the onchip peripherals outside of the core. The MMRs are accessible only in supervisor mode and appear as reserved space to onchip peripherals.

### Booting

The Blackfin processor contains a small on-chip boot kernel, which configures the appropriate peripheral for booting. If the Blackfin processor is configured to boot from boot ROM

| Peripheral Interrupt Event                      | Default<br>Mapping | Peripheral<br>Interrupt ID |

|-------------------------------------------------|--------------------|----------------------------|

| DMA Channels 12 and 13<br>(Memory DMA Stream 0) | IVG13              | 29                         |

| DMA Channels 14 and 15<br>(Memory DMA Stream 1) | IVG13              | 30                         |

| Software Watchdog Timer                         | IVG13              | 31                         |

| Port F Interrupt B                              | IVG13              | 31                         |

Table 3. System Interrupt Controller (SIC) (Continued)

### **Event Control**

The Blackfin processor provides a very flexible mechanism to control the processing of events. In the CEC, three registers are used to coordinate and control events. Each register is 32 bits wide:

- CEC interrupt latch register (ILAT) Indicates when events have been latched. The appropriate bit is set when the processor has latched the event and cleared when the event has been accepted into the system. This register is updated automatically by the controller, but it can be written only when its corresponding IMASK bit is cleared.

- CEC interrupt mask register (IMASK) Controls the masking and unmasking of individual events. When a bit is set in the IMASK register, that event is unmasked and is processed by the CEC when asserted. A cleared bit in the IMASK register masks the event, preventing the processor from servicing the event even though the event may be latched in the ILAT register. This register can be read or written while in supervisor mode. (Note that general-purpose interrupts can be globally enabled and disabled with the STI and CLI instructions, respectively.)

- CEC interrupt pending register (IPEND) The IPEND register keeps track of all nested events. A set bit in the IPEND register indicates the event is currently active or nested at some level. This register is updated automatically by the controller but can be read while in supervisor mode.

The SIC allows further control of event processing by providing three 32-bit interrupt control and status registers. Each register contains a bit corresponding to each of the peripheral interrupt events shown in Table 3 on Page 7.

- SIC interrupt mask register (SIC\_IMASK) Controls the masking and unmasking of each peripheral interrupt event. When a bit is set in the register, that peripheral event is unmasked and is processed by the system when asserted. A cleared bit in the register masks the peripheral event, preventing the processor from servicing the event.

- SIC interrupt status register (SIC\_ISR) As multiple peripherals can be mapped to a single event, this register allows the software to determine which peripheral event source triggered the interrupt. A set bit indicates the peripheral is asserting the interrupt, and a cleared bit indicates the peripheral is not asserting the event.

SIC interrupt wake-up enable register (SIC\_IWR) – By enabling the corresponding bit in this register, a peripheral can be configured to wake up the processor, should the core be idled when the event is generated. (For more information, see Dynamic Power Management on Page 13.)

Because multiple interrupt sources can map to a single generalpurpose interrupt, multiple pulse assertions can occur simultaneously, before or during interrupt processing for an interrupt event already detected on this interrupt input. The IPEND register contents are monitored by the SIC as the interrupt acknowledgement.

The appropriate ILAT register bit is set when an interrupt rising edge is detected (detection requires two core clock cycles). The bit is cleared when the respective IPEND register bit is set. The IPEND bit indicates that the event has entered into the processor pipeline. At this point the CEC recognizes and queues the next rising edge event on the corresponding event input. The minimum latency from the rising edge transition of the generalpurpose interrupt to the IPEND output asserted is three core clock cycles; however, the latency can be much higher, depending on the activity within and the state of the processor.

### DMA CONTROLLERS

The Blackfin processors have multiple, independent DMA channels that support automated data transfers with minimal overhead for the processor core. DMA transfers can occur between the processor's internal memories and any of its DMAcapable peripherals. Additionally, DMA transfers can be accomplished between any of the DMA-capable peripherals and external devices connected to the external memory interfaces, including the SDRAM controller and the asynchronous memory controller. DMA-capable peripherals include the Ethernet MAC (ADSP-BF536 and ADSP-BF537 only), SPORT's, SPI port, UART's, and PPI. Each individual DMA-capable peripheral has at least one dedicated DMA channel.

The DMA controller supports both one-dimensional (1-D) and two-dimensional (2-D) DMA transfers. DMA transfer initialization can be implemented from registers or from sets of parameters called descriptor blocks.

The 2-D DMA capability supports arbitrary row and column sizes up to 64K elements by 64K elements, and arbitrary row and column step sizes up to  $\pm$ 32K elements. Furthermore, the column step size can be less than the row step size, allowing implementation of interleaved data streams. This feature is especially useful in video applications where data can be deinterleaved on the fly.

Examples of DMA types supported by the DMA controller include

- A single, linear buffer that stops upon completion

- A circular, auto-refreshing buffer that interrupts on each full or fractionally full buffer

- 1-D or 2-D DMA using a linked list of descriptors

- 2-D DMA using an array of descriptors, specifying only the base DMA address within a common page.

hibernate state,  $V_{DDEXT}$  can still be applied, eliminating the need for external buffers. The voltage regulator can be activated from this power-down state by asserting the RESET pin, which then initiates a boot sequence. The regulator can also be disabled and bypassed at the user's discretion. For additional information on voltage regulation, see *Switching Regulator Design Considerations for the ADSP-BF533 Blackfin Processors (EE-228).*

### **CLOCK SIGNALS**

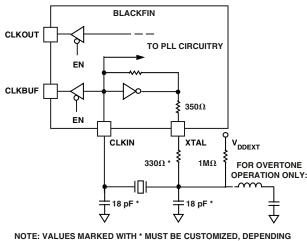

The ADSP-BF534/ADSP-BF536/ADSP-BF537 processors can be clocked by an external crystal, a sine wave input, or a buffered, shaped clock derived from an external clock oscillator.

If an external clock is used, it should be a TTL compatible signal and must not be halted, changed, or operated below the specified frequency during normal operation. This signal is connected to the processor's CLKIN pin. When an external clock is used, the XTAL pin must be left unconnected.

Alternatively, because the processors include an on-chip oscillator circuit, an external crystal can be used. For fundamental frequency operation, use the circuit shown in Figure 6. A parallel-resonant, fundamental frequency, microprocessorgrade crystal is connected across the CLKIN and XTAL pins. The on-chip resistance between CLKIN and the XTAL pin is in the 500 k $\Omega$  range. Further parallel resistors are typically not recommended. The two capacitors and the series resistor shown in Figure 6 fine-tune phase and amplitude of the sine frequency.

The capacitor and resistor values shown in Figure 6 are typical values only. The capacitor values are dependent upon the crystal manufacturers' load capacitance recommendations and the PCB physical layout. The resistor value depends on the drive level specified by the crystal manufacturer. The user should verify the customized values based on careful investigations of multiple devices over temperature range.

ON THE CRYSTAL AND LAYOUT. PLEASE ANALYZE CAREFULLY.

Figure 6. External Crystal Connections

A third-overtone crystal can be used for frequencies above 25 MHz. The circuit is then modified to ensure crystal operation only at the third overtone, by adding a tuned inductor circuit as

shown in Figure 6. A design procedure for third-overtone operation is discussed in detail in the application note *Using Third Overtone Crystals with the ADSP-218x DSP (EE-168).*

The CLKBUF pin is an output pin, and is a buffer version of the input clock. This pin is particularly useful in Ethernet applications to limit the number of required clock sources in the system. In this type of application, a single 25 MHz or 50 MHz crystal can be applied directly to the processors. The 25 MHz or 50 MHz output of CLKBUF can then be connected to an external Ethernet MII or RMII PHY device.

Because of the default 10× PLL multiplier, providing a 50 MHz CLKIN exceeds the recommended operating conditions of the lower speed grades. Because of this restriction, an RMII PHY requiring a 50 MHz clock input cannot be clocked directly from the CLKBUF pin for the lower speed grades. In this case, either provide a separate 50 MHz clock source, or use an RMII PHY with 25 MHz clock input options. The CLKBUF output is active by default and can be disabled using the VR\_CTL register for power savings.

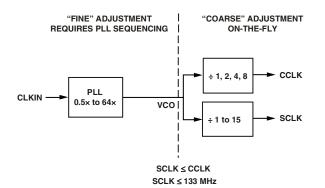

The Blackfin core runs at a different clock rate than the on-chip peripherals. As shown in Figure 7, the core clock (CCLK) and system peripheral clock (SCLK) are derived from the input clock (CLKIN) signal. An on-chip PLL is capable of multiplying the CLKIN signal by a programmable 0.5× to 64× multiplication factor (bounded by specified minimum and maximum VCO frequencies). The default multiplier is 10×, but it can be modified by a software instruction sequence in the PLL\_CTL register.

Figure 7. Frequency Modification Methods

On-the-fly CCLK and SCLK frequency changes can be effected by simply writing to the PLL\_DIV register. Whereas the maximum allowed CCLK and SCLK rates depend on the applied voltages  $V_{DDINT}$  and  $V_{DDEXT}$ , the VCO is always permitted to run up to the frequency specified by the part's speed grade. The CLKOUT pin reflects the SCLK frequency to the off-chip world. It belongs to the SDRAM interface, but it functions as a reference signal in other timing specifications as well. While active by default, it can be disabled using the EBIU\_SDGCTL and EBIU\_AMGCTL registers.

All on-chip peripherals are clocked by the system clock (SCLK). The system clock frequency is programmable by means of the SSEL3–0 bits of the PLL\_DIV register. The values programmed into the SSEL fields define a divide ratio between the PLL output

(VCO) and the system clock. SCLK divider values are 1 through 15. Table 6 illustrates typical system clock ratios.

| Signal Name | Divider Ratio | Example Frequency Ratio<br>(MHz) |      |

|-------------|---------------|----------------------------------|------|

| SSEL3-0     | VCO:SCLK      | VCO                              | SCLK |

| 0001        | 1:1           | 100                              | 100  |

| 0110        | 6:1           | 300                              | 50   |

| 1010        | 10:1          | 500                              | 50   |

#### Table 6. Example System Clock Ratios

Note that the divisor ratio must be chosen to limit the system clock frequency to its maximum of  $f_{SCLK}$ . The SSEL value can be changed dynamically without any PLL lock latencies by writing the appropriate values to the PLL divisor register (PLL\_DIV).

The core clock (CCLK) frequency can also be dynamically changed by means of the CSEL1–0 bits of the PLL\_DIV register. Supported CCLK divider ratios are 1, 2, 4, and 8, as shown in Table 7. This programmable core clock capability is useful for fast core frequency modifications.

### Table 7. Core Clock Ratios

| Signal Name | Divider Ratio | Example Frequency Ratio<br>(MHz) |      |

|-------------|---------------|----------------------------------|------|

| CSEL1-0     | -             |                                  | CCLK |

| 00          | 1:1           | 300                              | 300  |

| 01          | 2:1           | 300                              | 150  |

| 10          | 4:1           | 500                              | 125  |

| 11          | 8:1           | 200                              | 25   |

The maximum CCLK frequency not only depends on the part's speed grade (see Ordering Guide on Page 67), it also depends on the applied  $V_{DDINT}$  voltage (see Table 10, Table 11, and Table 12 on Page 24 for details). The maximal system clock rate (SCLK) depends on the chip package and the applied  $V_{DDEXT}$  voltage (see Table 14 on Page 24).

### **BOOTING MODES**

The ADSP-BF534/ADSP-BF536/ADSP-BF537 processor has six mechanisms (listed in Table 8) for automatically loading internal and external memory after a reset. A seventh mode is provided to execute from external memory, bypassing the boot sequence.

#### Table 8. Booting Modes

| BMODE2-0 | Description                                           |

|----------|-------------------------------------------------------|

| 000      | Execute from 16-bit external memory (bypass boot ROM) |

| 001      | Boot from 8-bit or 16-bit memory<br>(EPROM/flash)     |

| 010      | Reserved                                              |

| 011      | Boot from serial SPI memory (EEPROM/flash)            |

| 100      | Boot from SPI host (slave mode)                       |

#### Table 8. Booting Modes (Continued)

| BMODE2-0 | Description                                |

|----------|--------------------------------------------|

| 101      | Boot from serial TWI memory (EEPROM/flash) |

| 110      | Boot from TWI host (slave mode)            |

| 111      | Boot from UART host (slave mode)           |

The BMODE pins of the reset configuration register, sampled during power-on resets and software-initiated resets, implement the following modes:

- Execute from 16-bit external memory Execution starts from address 0x2000 0000 with 16-bit packing. The boot ROM is bypassed in this mode. All configuration settings are set for the slowest device possible (3-cycle hold time; 15-cycle R/W access times; 4-cycle setup).

- Boot from 8-bit and 16-bit external flash memory The 8-bit or 16-bit flash boot routine located in Boot ROM memory space is set up using asynchronous memory bank 0. All configuration settings are set for the slowest device possible (3-cycle hold time; 15-cycle R/W access times; 4-cycle setup). The Boot ROM evaluates the first byte of the boot stream at address 0x2000 0000. If it is 0x40, 8-bit boot is performed. A 0x60 byte assumes a 16-bit memory device and performs 8-bit DMA. A 0x20 byte also assumes 16-bit memory but performs 16-bit DMA.

- Boot from serial SPI memory (EEPROM or flash) 8-, 16-, or 24-bit addressable devices are supported as well as AT45DB041, AT45DB081, AT45DB161, AT45DB321, AT45DB642, and AT45DB1282 DataFlash<sup>®</sup> devices from Atmel. The SPI uses the PF10/SPI SSEL1 output pin to select a single SPI EEPROM/flash device, submits a read command and successive address bytes (0x00) until a valid 8-, 16-, or 24-bit, or Atmel addressable device is detected, and begins clocking data into the processor.

- Boot from SPI host device The Blackfin processor operates in SPI slave mode and is configured to receive the bytes of the .LDR file from an SPI host (master) agent. To hold off the host device from transmitting while the boot ROM is busy, the Blackfin processor asserts a GPIO pin, called host wait (HWAIT), to signal the host device not to send any more bytes until the flag is deasserted. The flag is chosen by the user and this information is transferred to the Blackfin processor via bits 10:5 of the FLAG header.

- Boot from UART Using an autobaud handshake sequence, a boot-stream-formatted program is downloaded by the host. The host agent selects a baud rate within the UART's clocking capabilities. When performing the autobaud, the UART expects an "@" (boot stream) character (8 bits data, 1 start bit, 1 stop bit, no parity bit) on the RXD pin to determine the bit rate. It then replies with an acknowledgement that is composed of 4 bytes: 0xBF, the value of UART\_DLL, the value of UART\_DLH, and 0x00. The host can then download the boot stream. When the processor needs to hold off the host, it deasserts CTS. Therefore, the host must monitor this signal.

### Table 9. Pin Descriptions (Continued)

| Pin Name                           | Туре | Function                                                                                                                     | Driver<br>Type <sup>1</sup> |

|------------------------------------|------|------------------------------------------------------------------------------------------------------------------------------|-----------------------------|

| Port F: GPIO/UART1–0/Timer7–0/SPI/ |      |                                                                                                                              |                             |

| External DMA Request/PPI           |      |                                                                                                                              |                             |

| (* = High Source/High Sink Pin)    |      |                                                                                                                              |                             |

| PF0* – GPIO/UART0 TX/DMAR0         | I/O  | GPIO/UART0 Transmit/DMA Request 0                                                                                            | С                           |

| PF1* – GPIO/UART0 RX/DMAR1/TACI1   | I/O  | GPIO/UART0 Receive/DMA Request 1/Timer1 Alternate Input Capture                                                              | С                           |

| PF2* – GPIO/UART1 TX/TMR7          | I/O  | GPIO/UART1 Transmit/Timer7                                                                                                   | С                           |

| PF3* – GPIO/UART1 RX/TMR6/TACI6    | I/O  | GPIO/UART1 Receive/Timer6/Timer6 Alternate Input Capture                                                                     | С                           |

| PF4* – GPIO/ <i>TMR5/SPI SSEL6</i> | I/O  | GPIO/Timer5/SPI Slave Select Enable 6                                                                                        | С                           |

| PF5* – GPIO/ <i>TMR4/SPI SSEL5</i> | I/O  | GPIO/Timer4/SPI Slave Select Enable 5                                                                                        | С                           |

| PF6* – GPIO/ <i>TMR3/SPI SSEL4</i> | I/O  | GPIO/Timer3/SPI Slave Select Enable 4                                                                                        | С                           |

| PF7* – GPIO/TMR2/PPI FS3           | I/O  | GPIO/Timer2/PPI Frame Sync 3                                                                                                 | С                           |

| PF8 – GPIO/TMR1/PPI FS2            | I/O  | GPIO/Timer1/PPI Frame Sync 2                                                                                                 | С                           |

| PF9 – GPIO/TMR0/PPI FS1            | I/O  | GPIO/Timer0/PPI Frame Sync 1                                                                                                 | С                           |

| PF10 – GPIO/SPI SSEL1              | I/O  | GPIO/SPI Slave Select Enable 1                                                                                               | С                           |

| PF11 – GPIO/SPI MOSI               | I/O  | GPIO/SPI Master Out Slave In                                                                                                 | С                           |

| PF12 – GPIO/ <i>SPI MISO</i>       | I/O  | GPIO/SPI Master In Slave Out (This pin should be pulled high through a 4.7 k $\Omega$ resistor if booting via the SPI port.) | С                           |

| PF13 – GPIO/SPI SCK                | I/O  | GPIO/SPI Clock                                                                                                               | D                           |

| PF14 – GPIO/SPI SS/TACLKO          | I/O  | GPIO/SPI Slave Select/Alternate Timer0 Clock Input                                                                           | С                           |

| PF15 – GPIO/PPI CLK/TMRCLK         | I/O  | GPIO/PPI Clock/External Timer Reference                                                                                      | С                           |

| Port G: GPIO/PPI/SPORT1            |      |                                                                                                                              |                             |

| PG0 – GPIO/ <i>PPI D0</i>          | I/O  | GPIO/PPI Data 0                                                                                                              | С                           |

| PG1 – GPIO/ <i>PPI D1</i>          | I/O  | GPIO/PPI Data 1                                                                                                              | С                           |

| PG2 – GPIO/ <i>PPI D2</i>          | I/O  | GPIO/PPI Data 2                                                                                                              | С                           |

| PG3 – GPIO/ <i>PPI D3</i>          | I/O  | GPIO/PPI Data 3                                                                                                              | С                           |

| PG4 – GPIO/ <i>PPI D4</i>          | I/O  | GPIO/PPI Data 4                                                                                                              | с                           |

| PG5 – GPIO/ <i>PPI D5</i>          | I/O  | GPIO/PPI Data 5                                                                                                              | с                           |

| PG6 – GPIO/ <i>PPI D6</i>          | I/O  | GPIO/PPI Data 6                                                                                                              | С                           |

| PG7 – GPIO/ <i>PPI D7</i>          | I/O  | GPIO/PPI Data 7                                                                                                              | С                           |

| PG8 – GPIO/PPI D8/DR1SEC           | I/O  | GPIO/PPI Data 8/SPORT1 Receive Data Secondary                                                                                | с                           |

| PG9 – GPIO/PPI D9/DT1SEC           | I/O  | GPIO/PPI Data 9/SPORT1 Transmit Data Secondary                                                                               | с                           |

| PG10 – GPIO/PPI D10/RSCLK1         | I/O  | GPIO/PPI Data 10/SPORT1 Receive Serial Clock                                                                                 | D                           |

| PG11 – GPIO/PPI D11/RFS1           | I/O  | GPIO/PPI Data 11/SPORT1 Receive Frame Sync                                                                                   | с                           |

| PG12 – GPIO/PPI D12/DR1PRI         | I/O  | GPIO/PPI Data 12/SPORT1 Receive Data Primary                                                                                 | с                           |

| PG13 – GPIO/PPI D13/TSCLK1         | I/O  | GPIO/PPI Data 13/SPORT1 Transmit Serial Clock                                                                                | D                           |

| PG14 – GPIO/PPI D14/TFS1           | I/O  | GPIO/PPI Data 14/SPORT1 Transmit Frame Sync                                                                                  | С                           |

| PG15 – GPIO/PPI D15/DT1PRI         | 1/0  | GPIO/PPI Data 15/SPORT1 Transmit Data Primary                                                                                | c                           |

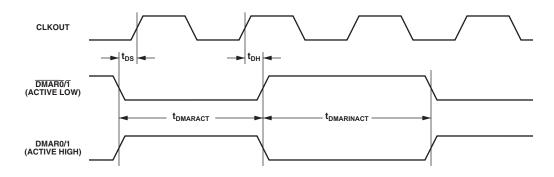

#### **External DMA Request Timing**

Table 28 and Figure 15 describe the external DMA requestoperations.

#### Table 28. External DMA Request Timing

| Parameter              |                                           | Min                    | Max | Unit |

|------------------------|-------------------------------------------|------------------------|-----|------|

| Timing Requir          | Timing Requirements                       |                        |     |      |

| t <sub>DS</sub>        | DMARx Asserted to CLKOUT High Setup       | 6.0                    |     | ns   |

| t <sub>DH</sub>        | CLKOUT High to DMARx Deasserted Hold Time | 0.0                    |     | ns   |

| t <sub>DMARACT</sub>   | DMARx Active Pulse Width                  | $1.0 \times t_{SCLK}$  |     | ns   |

| t <sub>DMARINACT</sub> | DMARx Inactive Pulse Width                | $1.75 \times t_{SCLK}$ |     | ns   |

Figure 15. External DMA Request Timing

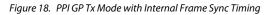

Figure 19. PPI GP Tx Mode with External Frame Sync Timing

#### Serial Port Timing

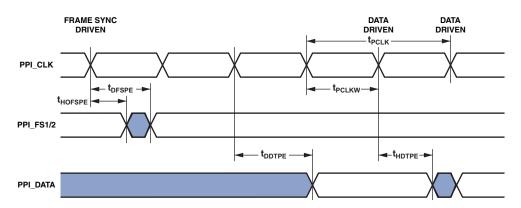

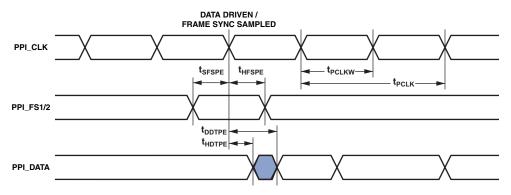

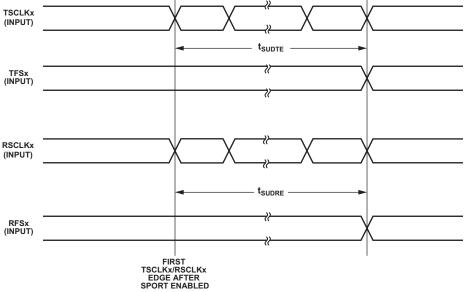

Table 30 through Table 33 on Page 41 and Figure 20 on Page 39 through Figure 23 on Page 41 describe serial port operations.

#### Table 30. Serial Ports-External Clock

| Parameter           |                                                                                  | Min                    | Max  | Unit |

|---------------------|----------------------------------------------------------------------------------|------------------------|------|------|

| Timing Requ         | irements                                                                         |                        |      |      |

| t <sub>SFSE</sub>   | TFSx/RFSx Setup Before TSCLKx/RSCLKx <sup>1</sup>                                | 3.0                    |      | ns   |

| t <sub>HFSE</sub>   | TFSx/RFSx Hold After TSCLKx/RSCLKx <sup>1</sup>                                  | 3.0                    |      | ns   |

| t <sub>SDRE</sub>   | Receive Data Setup Before RSCLKx <sup>1</sup>                                    | 3.0                    |      | ns   |

| t <sub>HDRE</sub>   | Receive Data Hold After RSCLKx <sup>1</sup>                                      | 3.0                    |      | ns   |

| t <sub>SCLKEW</sub> | TSCLKx/RSCLKx Width                                                              | 4.5                    |      | ns   |

| t <sub>SCLKE</sub>  | TSCLKx/RSCLKx Period                                                             | 15.0                   |      | ns   |

| t <sub>SUDTE</sub>  | Start-Up Delay From SPORT Enable To First External TFSx <sup>2</sup>             | $4.0 \times t_{SCLKI}$ |      | ns   |

| t <sub>SUDRE</sub>  | Start-Up Delay From SPORT Enable To First External RFSx <sup>2</sup>             | $4.0 \times t_{SCLKI}$ |      | ns   |

| Switching Ch        | paracteristics                                                                   |                        |      |      |

| t <sub>DFSE</sub>   | TFSx/RFSx Delay After TSCLKx/RSCLK (Internally Generated TFSx/RFSx) <sup>3</sup> |                        | 10.0 | ns   |

| t <sub>HOFSE</sub>  | TFSx/RFSx Hold After TSCLKx/RSCLK (Internally Generated TFSx/RFSx) <sup>2</sup>  | 0                      |      | ns   |

| t <sub>DDTE</sub>   | Transmit Data Delay After TSCLKx <sup>2</sup>                                    |                        | 10.0 | ns   |

| t <sub>HDTE</sub>   | Transmit Data Hold After TSCLKx <sup>2</sup>                                     | 0                      |      | ns   |

<sup>1</sup>Referenced to sample edge.

<sup>2</sup> Verified in design but untested. After being enabled, the serial port requires external clock pulses—before the first external frame sync edge—to initialize the serial port. <sup>3</sup> Referenced to drive edge.

#### Table 31. Serial Ports—Internal Clock

|                     |                                                                                   | 2.25 V | ≤ V <sub>DDEXT</sub> < 2.70 V<br>or             |        | $V \le V_{DDEXT} \le 3.60 V$ and    |      |

|---------------------|-----------------------------------------------------------------------------------|--------|-------------------------------------------------|--------|-------------------------------------|------|

|                     |                                                                                   | 0.80 V | $\leq$ V <sub>DDINT</sub> < 0.95 V <sup>1</sup> | 0.95 V | $\leq V_{DDINT} \leq 1.43 V^{2, 3}$ |      |

| Paramet             | er                                                                                | Min    | Мах                                             | Min    | Max                                 | Unit |

| Timing Re           | equirements                                                                       |        |                                                 |        |                                     |      |

| t <sub>SFSI</sub>   | TFSx/RFSx Setup Before TSCLKx/RSCLKx <sup>4</sup>                                 | 8.5    |                                                 | 8.0    |                                     | ns   |

| t <sub>HFSI</sub>   | TFSx/RFSx Hold After TSCLKx/RSCLKx <sup>4</sup>                                   | -1.5   |                                                 | -1.5   |                                     | ns   |

| t <sub>SDRI</sub>   | Receive Data Setup Before RSCLKx <sup>4</sup>                                     | 8.5    |                                                 | 8.0    |                                     | ns   |

| t <sub>HDRI</sub>   | Receive Data Hold After RSCLKx <sup>4</sup>                                       | -1.5   |                                                 | -1.5   |                                     | ns   |

| Switching           | Characteristics                                                                   |        |                                                 |        |                                     |      |

| t <sub>DFSI</sub>   | TFSx/RFSx Delay After TSCLKx/RSCLKx (Internally Generated TFSx/RFSx) <sup>5</sup> |        | 3.0                                             |        | 3.0                                 | ns   |

| t <sub>HOFSI</sub>  | TFSx/RFSx Hold After TSCLKx/RSCLKx (Internally Generated TFSx/RFSx) <sup>5</sup>  | -1.0   |                                                 | -1.0   |                                     | ns   |

| t <sub>DDTI</sub>   | Transmit Data Delay After TSCLKx⁵                                                 |        | 3.0                                             |        | 3.0                                 | ns   |

| t <sub>HDTI</sub>   | Transmit Data Hold After TSCLKx <sup>5</sup>                                      | -1.0   |                                                 | -1.0   |                                     | ns   |

| t <sub>SCLKIW</sub> | TSCLKx/RSCLKx Width                                                               | 4.5    |                                                 | 4.5    |                                     | ns   |

<sup>1</sup>Applies to all nonautomotive-grade devices when operated within either of these voltage ranges.

<sup>2</sup> Applies to all nonautomotive-grade devices when operated within these voltage ranges.

<sup>3</sup> All automotive-grade devices are within these specifications.

<sup>4</sup>Referenced to sample edge.

<sup>5</sup> Referenced to drive edge.

Figure 21. Serial Port Start Up with External Clock and Frame Sync

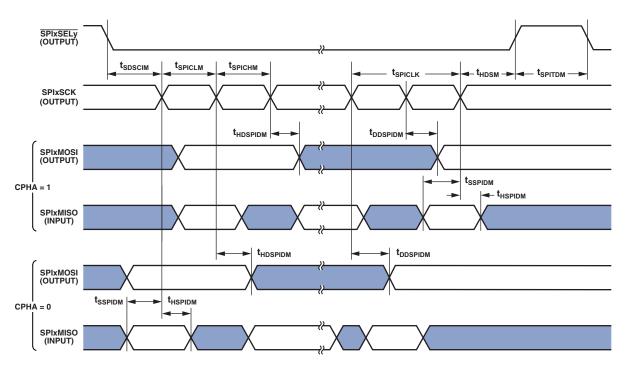

### Serial Peripheral Interface Port—Master Timing

Table 34 and Figure 24 describe SPI port master operations.

### Table 34. Serial Peripheral Interface (SPI) Port—Master Timing

|                     |                                                 | 2.25 V ≤ V <sub>DDEXT</sub> < 2<br>or<br>0.80 V ≤ V <sub>DDINT</sub> < 0. | and                       |      |

|---------------------|-------------------------------------------------|---------------------------------------------------------------------------|---------------------------|------|

| Parameter           |                                                 | Min Max                                                                   | Min Max                   | Unit |

| Timing Re           | equirements                                     |                                                                           |                           |      |

| t <sub>sspidm</sub> | Data Input Valid to SCK Edge (Data Input Setup) | 8.7                                                                       | 7.5                       | ns   |

| t <sub>hspidm</sub> | SCK Sampling Edge to Data Input Invalid         | -1.5                                                                      | -1.5                      | ns   |

| Switching           | Characteristics                                 |                                                                           |                           |      |

| t <sub>sdscim</sub> | SPISELx Low to First SCK Edge                   | $2 \times t_{SCLK} - 1.5$                                                 | $2 \times t_{SCLK} - 1.5$ | ns   |

| t <sub>spichm</sub> | Serial Clock High Period                        | $2 \times t_{SCLK} - 1.5$                                                 | $2 \times t_{SCLK} - 1.5$ | ns   |

| SPICLM              | Serial Clock Low Period                         | $2 \times t_{SCLK} - 1.5$                                                 | $2 \times t_{SCLK} - 1.5$ | ns   |

| SPICLK              | Serial Clock Period                             | $4 \times t_{SCLK} - 1.5$                                                 | $4 \times t_{SCLK} - 1.5$ | ns   |

| L<br>HDSM           | Last SCK Edge to SPISELx High                   | $2 \times t_{SCLK} - 1.5$                                                 | $2 \times t_{SCLK} - 1.5$ | ns   |

| SPITDM              | Sequential Transfer Delay                       | $2 \times t_{SCLK} - 1.5$                                                 | $2 \times t_{SCLK} - 1.5$ | ns   |

| DDSPIDM             | SCK Edge to Data Out Valid (Data Out Delay)     | 6                                                                         | 6                         | ns   |

| HDSPIDM             | SCK Edge to Data Out Invalid (Data Out Hold)    | -1.0                                                                      | -1.0                      | ns   |

<sup>1</sup>Applies to all nonautomotive-grade devices when operated within either of these voltage ranges.

<sup>2</sup> Applies to all nonautomotive-grade devices when operated within these voltage ranges.

<sup>3</sup> All automotive-grade devices are within these specifications.

Figure 24. Serial Peripheral Interface (SPI) Port—Master Timing

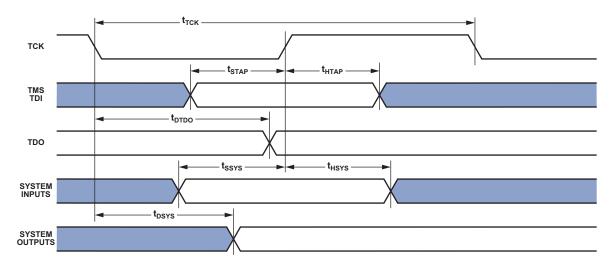

### JTAG Test and Emulation Port Timing

Table 39 and Figure 29 describe JTAG port operations.

#### Table 39. JTAG Port Timing

| Parameter          |                                                        | Min | Max | Unit |

|--------------------|--------------------------------------------------------|-----|-----|------|

| Timing Para        | meters                                                 |     |     |      |

| t <sub>TCK</sub>   | TCK Period                                             | 20  |     | ns   |

| t <sub>STAP</sub>  | TDI, TMS Setup Before TCK High                         | 4   |     | ns   |

| t <sub>HTAP</sub>  | TDI, TMS Hold After TCK High                           | 4   |     | ns   |

| t <sub>ssys</sub>  | System Inputs Setup Before TCK High <sup>1</sup>       | 4   |     | ns   |

| t <sub>HSYS</sub>  | System Inputs Hold After TCK High <sup>1</sup>         | 5   |     | ns   |

| t <sub>TRSTW</sub> | TRST Pulse Width <sup>2</sup> (Measured in TCK Cycles) | 4   |     | TCK  |

| Switching Cl       | haracteristics                                         |     |     |      |

| t <sub>DTDO</sub>  | TDO Delay From TCK Low                                 |     | 10  | ns   |

| t <sub>DSYS</sub>  | System Outputs Delay After TCK Low <sup>3</sup>        | 0   | 12  | ns   |

<sup>1</sup>System Inputs = DATA15-0, BR, ARDY, SCL, SDA, TFS0, TSCLK0, RSCLK0, RFS0, DR0PRI, DR0SEC, PF15-0, PG15-0, PH15-0, MDIO, TCK, TRST, RESET, NMI, RTXI, BMODE2-0.

<sup>2</sup> 50 MHz maximum.

<sup>3</sup> System Outputs = DATA15-0, ADDR19-1, <u>ABE1-0</u>, <u>BG</u>, <u>BGH</u>, <u>AOE</u>, <u>ARE</u>, <u>AWE</u>, <u>AMS3-0</u>, <u>SRAS</u>, <u>SCAS</u>, <u>SWE</u>, SCKE, CLKOUT, SA10, <u>SMS</u>, SCL, SDA, MDC, MDIO, TSCLK0, TFS0, RFS0, RSCLK0, DT0PRI, DT0SEC, PF15-0, PH15-0, RTXO, TDO, <u>EMU</u>, XTAL, VROUT1-0.

Figure 29. JTAG Port Timing

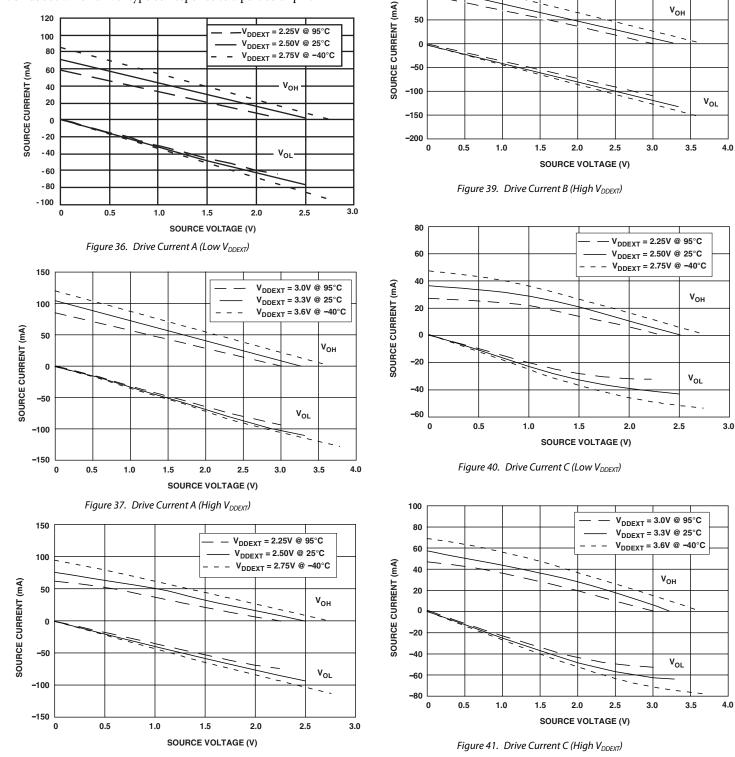

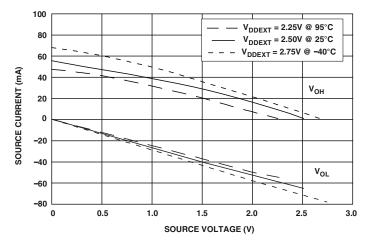

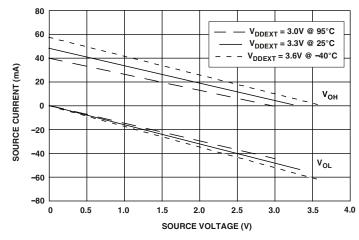

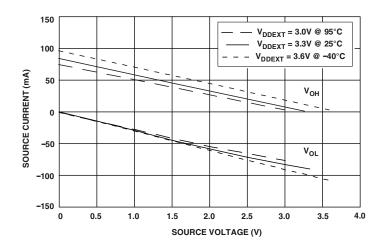

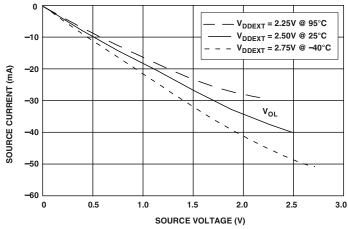

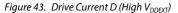

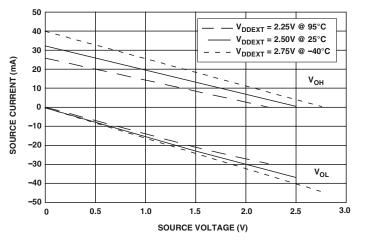

### **OUTPUT DRIVE CURRENTS**

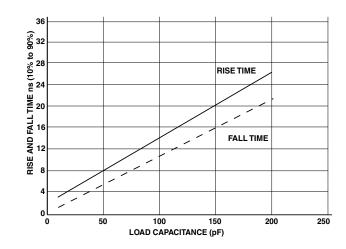

Figure 36 through Figure 47 show typical current-voltage characteristics for the output drivers of the processors. The curves represent the current drive capability of the output drivers as a function of output voltage. See Table 9 on Page 19 for information about which driver type corresponds to a particular pin.

200

150

100

V<sub>DDEXT</sub> = 3.0V @ 95°C

V<sub>DDEXT</sub> = 3.3V @ 25°C

V<sub>DDEXT</sub> = 3.6V @ -40°C

Figure 38. Drive Current B (Low V<sub>DDEXT</sub>)

Figure 42. Drive Current D (Low V<sub>DDEXT</sub>)

Figure 45. Drive Current E (High V<sub>DDEXT</sub>)

Figure 44. Drive Current E (Low V<sub>DDEXT</sub>)

Figure 46. Drive Current F (Low V<sub>DDEXT</sub>)

Figure 47. Drive Current F (High V<sub>DDEXT</sub>)

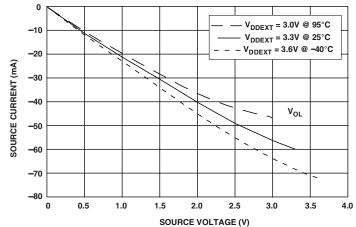

### **TEST CONDITIONS**

All timing parameters appearing in this data sheet were measured under the conditions described in this section. Figure 48 shows the measurement point for ac measurements (other than output enable/disable). The measurement point is  $V_{MEAS} = V_{DDEXT}/2$ .

Figure 48. Voltage Reference Levels for AC Measurements (Except Output Enable/Disable)

### **Output Enable Time**

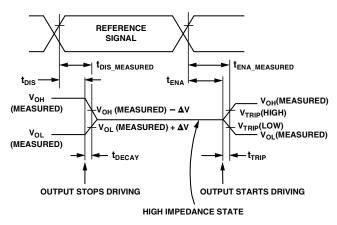

Output pins are considered to be enabled when they have made a transition from a high impedance state to the point when they start driving. The output enable time  $t_{ENA}$  is the interval from the point when a reference signal reaches a high or low voltage level to the point when the output starts driving as shown in the Output Enable/Disable diagram (Figure 49). The time  $t_{ENA\_MEA}$ . SURED is the interval from when the reference signal switches to when the output voltage reaches 2.0 V (output high) or 1.0 V (output low). Time  $t_{TRIP}$  is the interval from when the output starts driving to when the output reaches the 1.0 V or 2.0 V trip voltage. Time  $t_{ENA}$  is calculated as shown in the equation:

$$t_{ENA} = t_{ENA\_MEASURED} - t_{TRIP}$$

If multiple pins (such as the data bus) are enabled, the measurement value is that of the first pin to start driving.

### **Output Disable Time**

Output pins are considered to be disabled when they stop driving, go into a high impedance state, and start to decay from their output high or low voltage. The time for the voltage on the bus to decay by  $\Delta V$  is dependent on the capacitive load, C<sub>L</sub>, and the load current, I<sub>L</sub>. This decay time can be approximated by the equation:

$$t_{DECAY} = (C_L \Delta V) / I_L$$

The output disable time  $t_{DIS}$  is the difference between  $t_{DIS\_MEA-SURED}$  and  $t_{DECAY}$  as shown in Figure 49. The time  $t_{DIS\_MEASURED}$  is the interval from when the reference signal switches to when the output voltage decays  $\Delta V$  from the measured output-high or output-low voltage. The time  $t_{DECAY}$  is calculated with the test loads  $C_L$  and  $I_L$ , and with  $\Delta V$  equal to 0.5 V.

Figure 49. Output Enable/Disable

### **Example System Hold Time Calculation**

To determine the data output hold time in a particular system, first calculate  $t_{DECAY}$  using the equation given above. Choose  $\Delta V$  to be the difference between the processor's output voltage and the input threshold for the device requiring the hold time. A typical  $\Delta V$  is 0.4 V.  $C_L$  is the total bus capacitance (per data line), and  $I_L$  is the total leakage or three-state current (per data line). The hold time is  $t_{DECAY}$  plus the minimum disable time (for example,  $t_{DSDAT}$  for an SDRAM write cycle).

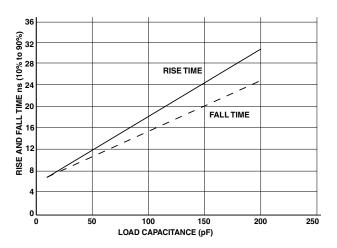

Figure 59. Typical Output Delay or Hold for Driver E at V<sub>DDEXT</sub> Min

Figure 60. Typical Output Delay or Hold for Driver E at  $V_{DDEXT}$  Max

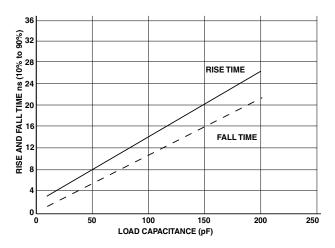

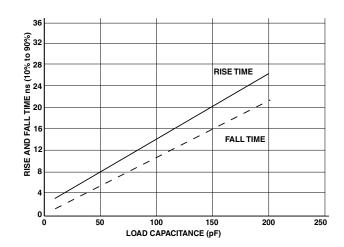

Figure 61. Typical Output Delay or Hold for Driver F at  $V_{DDEXT}$  Min

Figure 62. Typical Output Delay or Hold for Driver F at  $V_{DDEXT}$  Max

### THERMAL CHARACTERISTICS

To determine the junction temperature on the application printed circuit board use:

$$T_J = T_{CASE} + (\Psi_{JT} \times P_D)$$

where:

$T_I$  = Junction temperature (°C)

$T_{CASE}$  = Case temperature (°C) measured by customer at top center of package.

$\Psi_{TT}$  = From Table 46

$P_D$  = Power dissipation (see the power dissipation discussion and the tables on Page 27 for the method to calculate P<sub>D</sub>).

Values of  $\theta_{JA}$  are provided for package comparison and printed circuit board design considerations.  $\theta_{JA}$  can be used for a first order approximation of  $T_J$  by the equation:

$$T_I = T_A + (\theta_{IA} \times P_D)$$

where:

$T_A$  = Ambient temperature (°C)

Values of  $\theta_{JC}$  are provided for package comparison and printed circuit board design considerations when an external heat sink is required. Values of  $\theta_{JB}$  are provided for package comparison and printed circuit board design considerations.

In Table 46 through Table 48, airflow measurements comply with JEDEC standards JESD51-2 and JESD51-6, and the junction-to-board measurement complies with JESD51-8. Test board and thermal via design comply with JEDEC standards JESD51-9 (BGA). The junction-to-case measurement complies with MIL-STD-883 (Method 1012.1). All measurements use a 2S2P JEDEC test board.

Industrial applications using the 208-ball BGA package require thermal vias, to an embedded ground plane, in the PCB. Refer to JEDEC standard JESD51-9 for printed circuit board thermal ball land and thermal via design information.

| Table 46. | Thermal | Characteristics | (182-Ball BGA) |

|-----------|---------|-----------------|----------------|

|-----------|---------|-----------------|----------------|

| Parameter            | Condition            | Typical | Unit |

|----------------------|----------------------|---------|------|

| $\theta_{JA}$        | 0 Linear m/s Airflow | 32.80   | °C/W |

| $\theta_{JMA}$       | 1 Linear m/s Airflow | 29.30   | °C/W |

| $\theta_{JMA}$       | 2 Linear m/s Airflow | 28.00   | °C/W |

| $\theta_{JB}$        |                      | 20.10   | °C/W |

| $\theta_{\text{JC}}$ |                      | 7.92    | °C/W |

| $\Psi_{ m JT}$       | 0 Linear m/s Airflow | 0.19    | °C/W |

| $\Psi_{	extsf{JT}}$  | 1 Linear m/s Airflow | 0.35    | °C/W |

| $\Psi_{JT}$          | 2 Linear m/s Airflow | 0.45    | °C/W |

Table 47. Thermal Characteristics (208-Ball BGA withoutThermal Vias in PCB)

| Parameter            | Condition            | Typical | Unit |

|----------------------|----------------------|---------|------|

| $\theta_{JA}$        | 0 Linear m/s Airflow | 23.30   | °C/W |

| $\theta_{JMA}$       | 1 Linear m/s Airflow | 20.20   | °C/W |

| $\theta_{JMA}$       | 2 Linear m/s Airflow | 19.20   | °C/W |

| $\theta_{JB}$        |                      | 13.05   | °C/W |

| $\theta_{\text{JC}}$ |                      | 6.92    | °C/W |

| $\Psi_{ m T}$        | 0 Linear m/s Airflow | 0.18    | °C/W |

| $\Psi_{ m JT}$       | 1 Linear m/s Airflow | 0.27    | °C/W |

| $\Psi_{JT}$          | 2 Linear m/s Airflow | 0.32    | °C/W |

### Table 48. Thermal Characteristics (208-Ball BGA withThermal Vias in PCB)

| Parameter      | Condition            | Typical | Unit |

|----------------|----------------------|---------|------|

| $\theta_{JA}$  | 0 Linear m/s Airflow | 22.60   | °C/W |

| $\theta_{JMA}$ | 1 Linear m/s Airflow | 19.40   | °C/W |

| $\theta_{JMA}$ | 2 Linear m/s Airflow | 18.40   | °C/W |

| $\theta_{JB}$  |                      | 13.20   | °C/W |

| $\theta_{JC}$  |                      | 6.85    | °C/W |

| $\Psi_{ m T}$  | 0 Linear m/s Airflow | 0.16    | °C/W |

| $\Psi_{ m T}$  | 1 Linear m/s Airflow | 0.27    | °C/W |

| $\Psi_{ m JT}$ | 2 Linear m/s Airflow | 0.32    | °C/W |

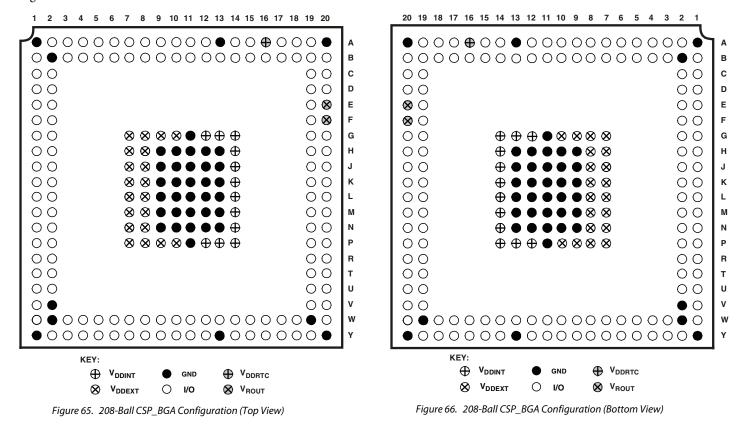

Figure 65 shows the top view of the CSP\_BGA ball configuration. Figure 66 shows the bottom view of the CSP\_BGA ball configuration.

### **OUTLINE DIMENSIONS**

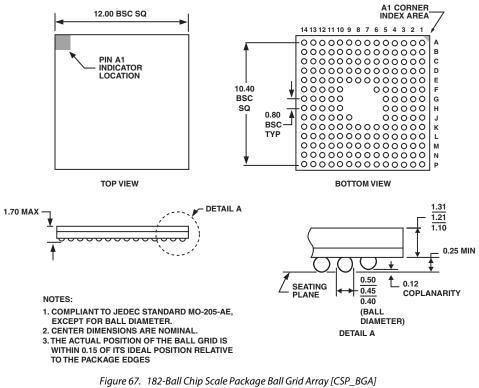

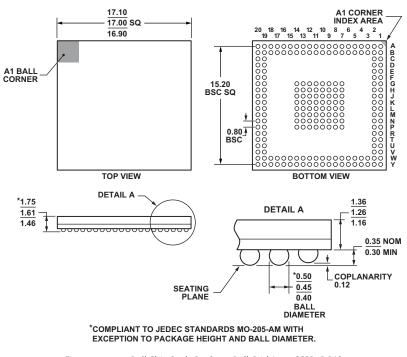

Dimensions in Figure 67 and Figure 68 are shown in millimeters.

(BC-182)

Dimensions shown in millimeters

Figure 68. 208-Ball Chip Scale Package Ball Grid Array [CSP\_BGA] (BC-208-2) Dimensions shown in millimeters