Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                                           |

|----------------------------|-----------------------------------------------------------------------------------------------------------|

| Product Status             | Active                                                                                                    |

| Core Processor             | ARM® Cortex®-M4/M0                                                                                        |

| Core Size                  | 32-Bit Dual-Core                                                                                          |

| Speed                      | 204MHz                                                                                                    |

| Connectivity               | CANbus, EBI/EMI, Ethernet, I <sup>2</sup> C, IrDA, Microwire, SD, SPI, SSI, SSP, UART/USART, USB, USB OTG |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, Motor Control PWM, POR, PWM, WDT                           |

| Number of I/O              | 118                                                                                                       |

| Program Memory Size        | -                                                                                                         |

| Program Memory Type        | ROMIess                                                                                                   |

| EEPROM Size                | •                                                                                                         |

| RAM Size                   | 264K x 8                                                                                                  |

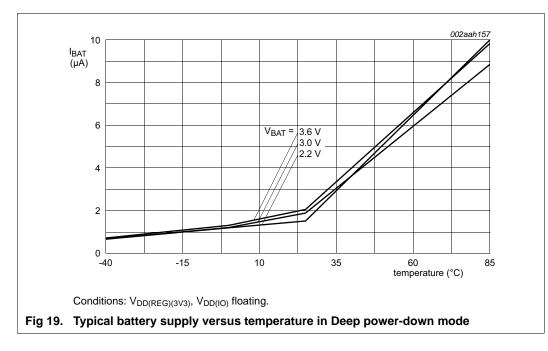

| Voltage - Supply (Vcc/Vdd) | 2.2V ~ 3.6V                                                                                               |

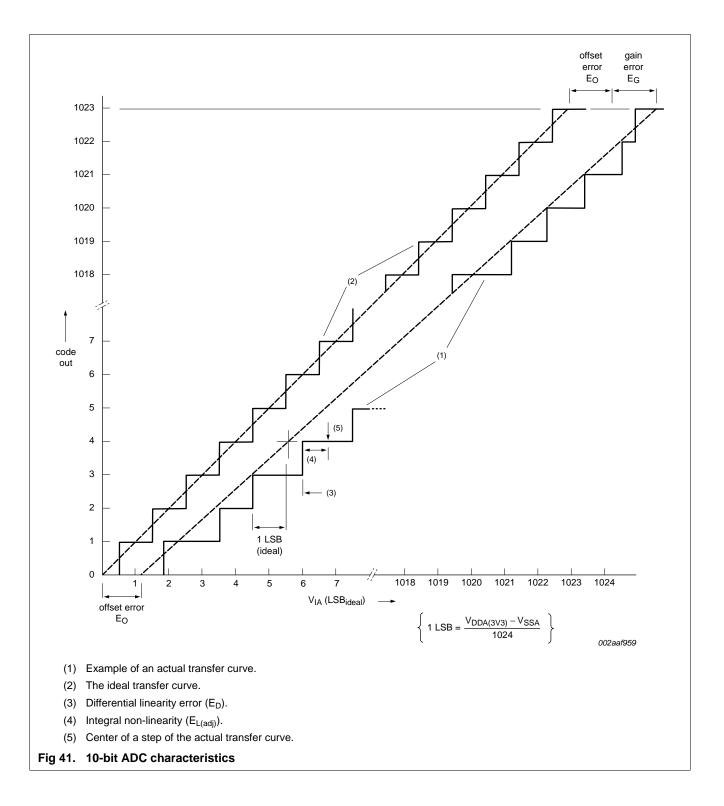

| Data Converters            | A/D 8x10b; D/A 1x10b                                                                                      |

| Oscillator Type            | Internal                                                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                                         |

| Mounting Type              | Surface Mount                                                                                             |

| Package / Case             | 180-TFBGA                                                                                                 |

| Supplier Device Package    | 180-TFBGA (12x12)                                                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/lpc4330fet180y                                    |

|                            |                                                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### 32-bit ARM Cortex-M4/M0 microcontroller

|        | 0360,   |          |          |         | are | 1           |      | e on all parts. See <u>Table 2</u> .                                |

|--------|---------|----------|----------|---------|-----|-------------|------|---------------------------------------------------------------------|

| Symbol | LBGA256 | TFBGA180 | TFBGA100 | LQFP144 |     | Reset state | Type | Description                                                         |

| P1_8   | R7      | M5       | H5       | 51      | [2] | N;          | I/O  | <b>GPIO1[1]</b> — General purpose digital input/output pin.         |

|        |         |          |          |         |     | PU          | 0    | <b>U1_DTR</b> — Data Terminal Ready output for UART1.               |

|        |         |          |          |         |     |             | 0    | <b>CTOUT_12</b> — SCTimer/PWM output 12. Match output 3 of timer 3. |

|        |         |          |          |         |     |             | I/O  | <b>EMC_D1</b> — External memory data line 1.                        |

|        |         |          |          |         |     |             | -    | R — Function reserved.                                              |

|        |         |          |          |         |     |             | -    | R — Function reserved.                                              |

|        |         |          |          |         |     |             | -    | R — Function reserved.                                              |

|        |         |          |          |         |     |             | 0    | <b>SD_VOLT0</b> — SD/MMC bus voltage select output 0.               |

| P1_9   | T7      | N5       | J5       | 52      | [2] | N;          | I/O  | GPI01[2] — General purpose digital input/output pin.                |

|        |         |          |          |         |     | PU          | 0    | U1_RTS — Request to Send output for UART1.                          |

|        |         |          |          |         |     |             | 0    | <b>CTOUT_11</b> — SCTimer/PWM output 11. Match output 3 of timer 2. |

|        |         |          |          |         |     |             | I/O  | EMC_D2 — External memory data line 2.                               |

|        |         |          |          |         |     |             | -    | R — Function reserved.                                              |

|        |         |          |          |         |     |             | -    | R — Function reserved.                                              |

|        |         |          |          |         |     |             | -    | R — Function reserved.                                              |

|        |         |          |          |         |     |             | I/O  | <b>SD_DAT0</b> — SD/MMC data bus line 0.                            |

| P1_10  | R8      | N6       | H6       | 53      | [2] | N;          | I/O  | GPIO1[3] — General purpose digital input/output pin.                |

|        |         |          |          |         |     | PU          | I    | U1_RI — Ring Indicator input for UART1.                             |

|        |         |          |          |         |     |             | 0    | <b>CTOUT_14</b> — SCTimer/PWM output 14. Match output 2 of timer 3. |

|        |         |          |          |         |     |             | I/O  | EMC_D3 — External memory data line 3.                               |

|        |         |          |          |         |     |             | -    | R — Function reserved.                                              |

|        |         |          |          |         |     |             | -    | R — Function reserved.                                              |

|        |         |          |          |         |     |             | -    | R — Function reserved.                                              |

|        |         |          |          |         |     |             | I/O  | <b>SD_DAT1</b> — SD/MMC data bus line 1.                            |

| P1_11  | Т9      | P8       | J7       | 55      | [2] | N;          | I/O  | GPIO1[4] — General purpose digital input/output pin.                |

|        |         |          |          |         |     | PU          | I    | U1_CTS — Clear to Send input for UART1.                             |

|        |         |          |          |         |     |             | 0    | <b>CTOUT_15</b> — SCTimer/PWM output 15. Match output 3 of timer 3. |

|        |         |          |          |         |     |             | I/O  | EMC_D4 — External memory data line 4.                               |

|        |         |          |          |         |     |             | -    | R — Function reserved.                                              |

|        |         |          |          |         |     |             | -    | R — Function reserved.                                              |

|        |         |          |          |         |     |             | -    | R — Function reserved.                                              |

|        |         |          |          |         |     |             | I/O  | SD_DAT2 — SD/MMC data bus line 2.                                   |

#### Table 3. Pin description ...continued

LCD, Ethernet, USB0, and USB1 functions are not available on all parts. See <u>Table 2</u>.

### 32-bit ARM Cortex-M4/M0 microcontroller

| LCD, Ethernet, | , USBU, 8 | ana US   | Бтип     |         | are |                    |      |                                                                                                                                                                           |

|----------------|-----------|----------|----------|---------|-----|--------------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Symbol         | LBGA256   | TFBGA180 | TFBGA100 | LQFP144 |     | Reset state<br>[1] | Type | Description                                                                                                                                                               |

| P1_16          | M7        | L5       | H9       | 64      | [2] | N;                 | I/O  | GPIO0[3] — General purpose digital input/output pin.                                                                                                                      |

|                |           |          |          |         |     | PU                 | Ι    | U2_RXD — Receiver input for USART2.                                                                                                                                       |

|                |           |          |          |         |     |                    | I/O  | SGPIO3 — General purpose digital input/output pin.                                                                                                                        |

|                |           |          |          |         |     |                    | Ι    | ENET_CRS — Ethernet Carrier Sense (MII interface).                                                                                                                        |

|                |           |          |          |         |     |                    | 0    | T0_MAT0 — Match output 0 of timer 0.                                                                                                                                      |

|                |           |          |          |         |     |                    | -    | R — Function reserved.                                                                                                                                                    |

|                |           |          |          |         |     |                    | -    | R — Function reserved.                                                                                                                                                    |

|                |           |          |          |         |     |                    | I    | <b>ENET_RX_DV</b> — Ethernet Receive Data Valid (RMII/MII interface).                                                                                                     |

| P1_17          | M8        | L6       | H10      | 66      | [3] | N;                 | I/O  | <b>GPIO0[12]</b> — General purpose digital input/output pin.                                                                                                              |

|                |           |          |          |         |     | PU                 | I/O  | <b>U2_UCLK</b> — Serial clock input/output for USART2 in synchronous mode.                                                                                                |

|                |           |          |          |         |     |                    | -    | R — Function reserved.                                                                                                                                                    |

|                |           |          |          |         |     |                    | I/O  | <b>ENET_MDIO</b> — Ethernet MIIM data input and output.                                                                                                                   |

|                |           |          |          |         |     |                    | Ι    | T0_CAP3 — Capture input 3 of timer 0.                                                                                                                                     |

|                |           |          |          |         |     |                    | 0    | CAN1_TD — CAN1 transmitter output.                                                                                                                                        |

|                |           |          |          |         |     |                    | I/O  | SGPI011 — General purpose digital input/output pin.                                                                                                                       |

|                |           |          |          |         |     |                    | -    | R — Function reserved.                                                                                                                                                    |

| P1_18          | N12       | N10      | J10      | 67      | [2] | N;                 | I/O  | <b>GPIO0[13]</b> — General purpose digital input/output pin.                                                                                                              |

|                |           |          |          |         |     | PU                 | I/O  | <b>U2_DIR</b> — RS-485/EIA-485 output enable/direction control for USART2.                                                                                                |

|                |           |          |          |         |     |                    | -    | R — Function reserved.                                                                                                                                                    |

|                |           |          |          |         |     |                    | 0    | <b>ENET_TXD0</b> — Ethernet transmit data 0 (RMII/MII interface).                                                                                                         |

|                |           |          |          |         |     |                    | 0    | T0_MAT3 — Match output 3 of timer 0.                                                                                                                                      |

|                |           |          |          |         |     |                    | Ι    | CAN1_RD — CAN1 receiver input.                                                                                                                                            |

|                |           |          |          |         |     |                    | I/O  | SGPI012 — General purpose digital input/output pin.                                                                                                                       |

|                |           |          |          |         |     |                    | -    | R — Function reserved.                                                                                                                                                    |

| P1_19          | M11       | N9       | K9       | 68      | [2] | N;<br>PU           | I    | <b>ENET_TX_CLK (ENET_REF_CLK)</b> — Ethernet Transmit<br>Clock (MII interface) or Ethernet Reference Clock (RMII<br>interface).                                           |

|                |           |          |          |         |     |                    | I/O  | SSP1_SCK — Serial clock for SSP1.                                                                                                                                         |

|                |           |          |          |         |     |                    | -    | R — Function reserved.                                                                                                                                                    |

|                |           |          |          |         |     |                    | -    | R — Function reserved.                                                                                                                                                    |

|                |           |          |          |         |     |                    | 0    | CLKOUT — Clock output pin.                                                                                                                                                |

|                |           |          |          |         |     |                    | -    | R — Function reserved.                                                                                                                                                    |

|                |           |          |          |         |     |                    | 0    | I2S0_RX_MCLK — I2S receive master clock.                                                                                                                                  |

|                |           |          |          |         |     |                    | I/O  | <b>I2S1_TX_SCK</b> — Transmit Clock. It is driven by the master<br>and received by the slave. Corresponds to the signal SCK in<br>the I <sup>2</sup> S-bus specification. |

#### Table 3. Pin description ...continued

LCD, Ethernet, USB0, and USB1 functions are not available on all parts. See <u>Table 2</u>.

LPC4350\_30\_20\_10

### 32-bit ARM Cortex-M4/M0 microcontroller

| Symbol | LBGA256 | TFBGA180 | TFBGA100 | LQFP144 |     | Reset state | Type | Description                                                                                 |

|--------|---------|----------|----------|---------|-----|-------------|------|---------------------------------------------------------------------------------------------|

| P2_8   | J16     | H14      | C6       | 98      | [2] | N;<br>PU    | I/O  | <b>SGPIO15</b> — General purpose digital input/output pin. Boot pin (see <u>Table 5</u> ).  |

|        |         |          |          |         |     |             | 0    | <b>CTOUT_0</b> — SCTimer/PWM output 0. Match output 0 of timer 0.                           |

|        |         |          |          |         |     |             | I/O  | <b>U3_DIR</b> — RS-485/EIA-485 output enable/direction control for USART3.                  |

|        |         |          |          |         |     |             | I/O  | EMC_A8 — External memory address line 8.                                                    |

|        |         |          |          |         |     |             | I/O  | GPI05[7] — General purpose digital input/output pin.                                        |

|        |         |          |          |         |     |             | -    | R — Function reserved.                                                                      |

|        |         |          |          |         |     |             | -    | R — Function reserved.                                                                      |

|        |         |          |          |         |     |             | -    | R — Function reserved.                                                                      |

| P2_9   | H16     | G14      | B10      | 102     | [2] | N;<br>PU    | I/O  | <b>GPIO1[10]</b> — General purpose digital input/output pin. Boot pin (see <u>Table 5</u> . |

|        |         |          |          |         |     |             | 0    | <b>CTOUT_3</b> — SCTimer/PWM output 3. Match output 3 of timer 0.                           |

|        |         |          |          |         |     |             | I/O  | U3_BAUD — Baud pin for USART3.                                                              |

|        |         |          |          |         |     |             | I/O  | EMC_A0 — External memory address line 0.                                                    |

|        |         |          |          |         |     |             | -    | R — Function reserved.                                                                      |

|        |         |          |          |         |     |             | -    | R — Function reserved.                                                                      |

|        |         |          |          |         |     |             | -    | R — Function reserved.                                                                      |

|        |         |          |          |         |     |             | -    | R — Function reserved.                                                                      |

| P2_10  | G16     | F14      | E8       | 104     | [2] | N;          | I/O  | GPIO0[14] — General purpose digital input/output pin.                                       |

|        |         |          |          |         |     | PU          | 0    | <b>CTOUT_2</b> — SCTimer/PWM output 2. Match output 2 of timer 0.                           |

|        |         |          |          |         |     |             | 0    | U2_TXD — Transmitter output for USART2.                                                     |

|        |         |          |          |         |     |             | I/O  | EMC_A1 — External memory address line 1.                                                    |

|        |         |          |          |         |     |             | -    | R — Function reserved.                                                                      |

|        |         |          |          |         |     |             | -    | R — Function reserved.                                                                      |

|        |         |          |          |         |     |             | -    | R — Function reserved.                                                                      |

|        |         |          |          |         |     |             | -    | R — Function reserved.                                                                      |

| P2_11  | F16     | E13      | A9       | 105     | [2] | N;          | I/O  | GPIO1[11] — General purpose digital input/output pin.                                       |

|        |         |          |          |         |     | PU          | 0    | <b>CTOUT_5</b> — SCTimer/PWM output 5. Match output 3 of timer 3.                           |

|        |         |          |          |         |     |             | I    | U2_RXD — Receiver input for USART2.                                                         |

|        |         |          |          |         |     |             | I/O  | EMC_A2 — External memory address line 2.                                                    |

|        |         |          |          |         |     |             | -    | R — Function reserved.                                                                      |

|        |         |          |          |         |     |             | -    | R — Function reserved.                                                                      |

|        |         |          |          |         |     |             | -    | R — Function reserved.                                                                      |

|        |         |          |          |         |     |             | -    | R — Function reserved.                                                                      |

#### Table 3. Pin description ...continued

LCD, Ethernet, USB0, and USB1 functions are not available on all parts. See <u>Table 2</u>.

LPC4350\_30\_20\_10

All information provided in this document is subject to legal disclaimers.

### 32-bit ARM Cortex-M4/M0 microcontroller

| Symbol | LBGA256 | TFBGA180 | TFBGA100 | LQFP144 |     | Reset state<br>[1] | Type | Description                                                                                                                                                      |

|--------|---------|----------|----------|---------|-----|--------------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PB_6   | A6      | C5       | -        | -       | [5] | N;                 | -    | R — Function reserved.                                                                                                                                           |

|        |         |          |          |         |     | PU                 | I/O  | USB1_ULPI_D3 — ULPI link bidirectional data line 3.                                                                                                              |

|        |         |          |          |         |     |                    | 0    | LCD_VD13 — LCD data.                                                                                                                                             |

|        |         |          |          |         |     |                    | -    | R — Function reserved.                                                                                                                                           |

|        |         |          |          |         |     |                    | I/O  | GPIO5[26] — General purpose digital input/output pin.                                                                                                            |

|        |         |          |          |         |     |                    | I    | CTIN_6 — SCTimer/PWM input 6. Capture input 1 of timer 3.                                                                                                        |

|        |         |          |          |         |     |                    | 0    | LCD_VD19 — LCD data.                                                                                                                                             |

|        |         |          |          |         |     |                    | -    | R — Function reserved.                                                                                                                                           |

|        |         |          |          |         |     |                    | AI   | <b>ADC0_6</b> — ADC0 and ADC1, input channel 6. Configure the pin as GPIO input and use the ADC function select register in the SCU to select the ADC.           |

| PC_0   | D4      | -        | -        | -       | [5] | N;                 | -    | R — Function reserved.                                                                                                                                           |

|        |         |          |          |         |     | PU                 | I    | <b>USB1_ULPI_CLK</b> — ULPI link CLK signal. 60 MHz clock generated by the PHY.                                                                                  |

|        |         |          |          |         |     |                    | -    | R — Function reserved.                                                                                                                                           |

|        |         |          |          |         |     |                    | I/O  | ENET_RX_CLK — Ethernet Receive Clock (MII interface).                                                                                                            |

|        |         |          |          |         |     |                    | 0    | LCD_DCLK — LCD panel clock.                                                                                                                                      |

|        |         |          |          |         |     |                    | -    | R — Function reserved.                                                                                                                                           |

|        |         |          |          |         |     |                    | -    | R — Function reserved.                                                                                                                                           |

|        |         |          |          |         |     |                    | I/O  | SD_CLK — SD/MMC card clock.                                                                                                                                      |

|        |         |          |          |         |     |                    | AI   | <b>ADC1_1</b> — ADC1 and ADC0, input channel 1. Configure the pin as input (USB_ULPI_CLK) and use the ADC function select register in the SCU to select the ADC. |

| PC_1   | E4      | -        | -        | -       | [2] | N;                 | I/O  | USB1_ULPI_D7 — ULPI link bidirectional data line 7.                                                                                                              |

|        |         |          |          |         |     | PU                 | -    | R — Function reserved.                                                                                                                                           |

|        |         |          |          |         |     |                    | I    | U1_RI — Ring Indicator input for UART 1.                                                                                                                         |

|        |         |          |          |         |     |                    | 0    | ENET_MDC — Ethernet MIIM clock.                                                                                                                                  |

|        |         |          |          |         |     |                    | I/O  | GPIO6[0] — General purpose digital input/output pin.                                                                                                             |

|        |         |          |          |         |     |                    | -    | R — Function reserved.                                                                                                                                           |

|        |         |          |          |         |     |                    | I    | T3_CAP0 — Capture input 0 of timer 3.                                                                                                                            |

|        |         |          |          |         |     |                    | 0    | <b>SD_VOLT0</b> — SD/MMC bus voltage select output 0.                                                                                                            |

| PC_2   | F6      | -        | -        | -       | [2] | N;                 | I/O  | USB1_ULPI_D6 — ULPI link bidirectional data line 6.                                                                                                              |

|        |         |          |          |         |     | PU                 | -    | R — Function reserved.                                                                                                                                           |

|        |         |          |          |         |     |                    | I    | U1_CTS — Clear to Send input for UART 1.                                                                                                                         |

|        |         |          |          |         |     |                    | 0    | ENET_TXD2 — Ethernet transmit data 2 (MII interface).                                                                                                            |

|        |         |          |          |         |     |                    | I/O  | GPIO6[1] — General purpose digital input/output pin.                                                                                                             |

|        |         |          |          |         |     |                    | -    | R — Function reserved.                                                                                                                                           |

|        |         |          |          |         |     |                    | -    | R — Function reserved.                                                                                                                                           |

|        |         |          |          |         |     |                    | 0    | <b>SD_RST</b> — SD/MMC reset signal for MMC4.4 card.                                                                                                             |

#### Table 3. Pin description ... continued

ilahla ~!! a Tabla D 0

LPC4350\_30\_20\_10 Product data sheet © NXP Semiconductors N.V. 2016. All rights reserved.

#### 32-bit ARM Cortex-M4/M0 microcontroller

| LOD, Linemei, O | ,                                                                                                 |          |                                       | 1                       | 1                            |                    | 1    |                |

|-----------------|---------------------------------------------------------------------------------------------------|----------|---------------------------------------|-------------------------|------------------------------|--------------------|------|----------------|

| Symbol          | LBGA256                                                                                           | TFBGA180 | TFBGA100                              | LQFP144                 |                              | Reset state<br>[1] | Type | Description    |

| VSSIO           | C4,<br>D13,<br>G6,<br>G7,<br>G8,<br>H8,<br>H9,<br>J8,<br>J9,<br>K9,<br>K10,<br>M13,<br>P7,<br>P13 | -        | C8,<br>D4,<br>D5,<br>G8,<br>J3,<br>J6 | 4,<br>40,<br>76,<br>109 | [ <u>13]</u><br>[ <u>14]</u> | -                  | -    | Ground.        |

| VSSA            | B2                                                                                                | A3       | C2                                    | 135                     |                              | -                  | -    | Analog ground. |

| Not connected   |                                                                                                   |          |                                       |                         |                              |                    |      |                |

| -               | B9                                                                                                | B8       | -                                     | -                       |                              | -                  | -    | n.c.           |

#### Table 3. Pin description ...continued

LCD, Ethernet, USB0, and USB1 functions are not available on all parts. See Table 2.

[1] N = neutral, input buffer disabled; no extra VDDIO current consumption if the input is driven midway between supplies; set the EZI bit in the SFS register to enable the input buffer; I = input; OL = output driving LOW; OH = output driving HIGH; AI/O = analog input/output; IA = inactive; PU = pull-up enabled (weak pull-up resistor pulls up pin to VDDIO; F = floating. Reset state reflects the pin state at reset without boot code operation.

[2] 5 V tolerant pad with 15 ns glitch filter (5 V tolerant if VDDIO present; if VDDIO not present, do not exceed 3.6 V); provides digital I/O functions with TTL levels and hysteresis; normal drive strength.

- [3] 5 V tolerant pad with 15 ns glitch filter (5 V tolerant if VDDIO present; if VDDIO not present, do not exceed 3.6 V); provides digital I/O functions with TTL levels, and hysteresis; high drive strength.

- [4] 5 V tolerant pad with 15 ns glitch filter (5 V tolerant if VDDIO present; if VDDIO not present, do not exceed 3.6 V); provides high-speed digital I/O functions with TTL levels and hysteresis.

- [5] 5 V tolerant pad providing digital I/O functions (with TTL levels and hysteresis) and analog input or output (5 V tolerant if VDDIO present; if VDDIO not present, do not exceed 3.6 V). When configured as an ADC input or DAC output, the pin is not 5 V tolerant and the digital section of the pad must be disabled by setting the pin to an input function and disabling the pull-up resistor through the pin's SFSP register.

- [6] 5 V tolerant transparent analog pad.

- [7] For maximum load  $C_L = 6.5 \,\mu$ F and maximum pull-down resistance  $R_{pd} = 80 \,k\Omega$ , the VBUS signal takes about 2 s to fall from VBUS = 5 V to VBUS = 0.2 V when it is no longer driven.

- [8] Transparent analog pad. Not 5 V tolerant.

- [9] Pad provides USB functions 5 V tolerant if VDDIO present; if VDDIO not present, do not exceed 3.6 V. It is designed in accordance with the USB specification, revision 2.0 (Full-speed and Low-speed mode only).

- [10] Open-drain 5 V tolerant digital I/O pad, compatible with I2C-bus Fast Mode Plus specification. This pad requires an external pull-up to provide output functionality. When power is switched off, this pin connected to the I2C-bus is floating and does not disturb the I2C lines.

- [11] 5 V tolerant pad with 20 ns glitch filter; provides digital I/O functions with open-drain output and hysteresis.

- [12] VPP is internally connected to VDDIO for all packages with the exception of the LBGA256 package.

- [13] On the LQFP144 package, VSSIO and VSS are connected to a common ground plane.

- [14] On the TFBGA100 package, VSS is internally connected to VSSIO.

32-bit ARM Cortex-M4/M0 microcontroller

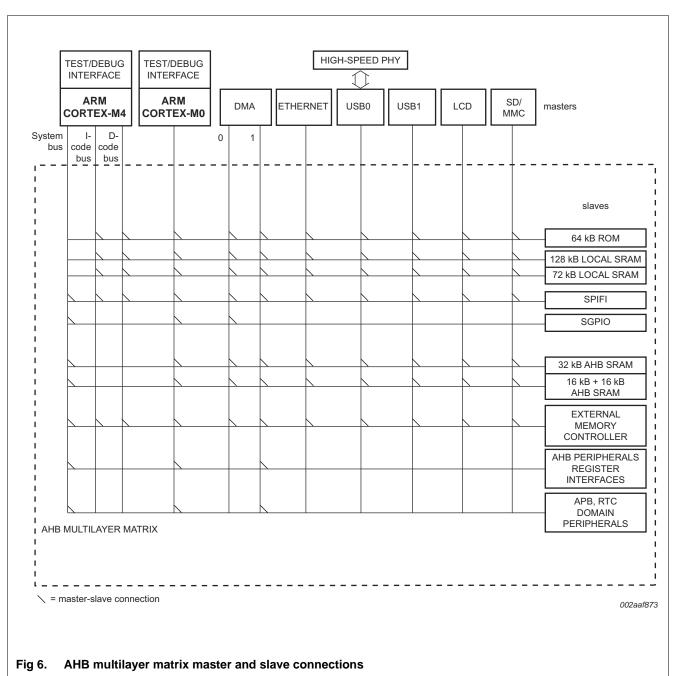

### 7.5 AHB multilayer matrix

7.6 Nested Vectored Interrupt Controller (NVIC)

The NVIC is an integral part of the Cortex-M4. The tight coupling to the CPU allows for low interrupt latency and efficient processing of late arriving interrupts.

The ARM Cortex-M0 co-processor has its own NVIC with 32 vectored interrupts. Most peripheral interrupts are shared between the Cortex-M0 and Cortex-M4 NVICs.

LPC4350\_30\_20\_10

### 32-bit ARM Cortex-M4/M0 microcontroller

• LCD panel clock may be generated from the peripheral clock, or from a clock input pin.

### 7.17.8 Ethernet

**Remark:** The Ethernet peripheral is available on parts LPC4350/30. See <u>Table 2</u>.

### 7.17.8.1 Features

- 10/100 Mbit/s.

- DMA support.

- Power management remote wake-up frame and magic packet detection.

- Supports both full-duplex and half-duplex operation

- Supports CSMA/CD Protocol for half-duplex operation.

- Supports IEEE 802.3x flow control for full-duplex operation.

- Optional forwarding of received pause control frames to the user application in full-duplex operation.

- Back-pressure support for half-duplex operation.

- Automatic transmission of zero-quanta pause frame on deassertion of flow control input in full-duplex operation.

- Supports IEEE1588 time stamping and IEEE 1588 advanced time stamping (IEEE 1588-2008 v2).

### 7.18 Digital serial peripherals

### 7.18.1 UART1

The LPC4350/30/20/10 contain one UART with standard transmit and receive data lines. UART1 also provides a full modem control handshake interface and support for RS-485/9-bit mode allowing both software address detection and automatic address detection using 9-bit mode.

UART1 includes a fractional baud rate generator. Standard baud rates such as 115200 Bd can be achieved with any crystal frequency above 2 MHz.

#### 7.18.1.1 Features

- Maximum UART data bit rate of 8 MBit/s.

- 16 B Receive and Transmit FIFOs.

- Register locations conform to 16C550 industry standard.

- Receiver FIFO trigger points at 1 B, 4 B, 8 B, and 14 B.

- Built-in fractional baud rate generator covering wide range of baud rates without a need for external crystals of particular values.

- Auto baud capabilities and FIFO control mechanism that enables software flow control implementation.

- Equipped with standard modem interface signals. This module also provides full support for hardware flow control.

- Support for RS-485/9-bit/EIA-485 mode (UART1).

### 32-bit ARM Cortex-M4/M0 microcontroller

The I<sup>2</sup>S-bus provides a standard communication interface for digital audio applications.

The  $l^2S$ -bus specification defines a 3-wire serial bus using one data line, one clock line, and one word select signal. The basic  $l^2S$ -bus connection has one master, which is always the master, and one slave. The  $l^2S$ -bus interface provides a separate transmit and receive channel, each of which can operate as either a master or a slave.

### 7.18.6.1 Features

- The I<sup>2</sup>S interface has separate input/output channels, each of which can operate in master or slave mode.

- Capable of handling 8-bit, 16-bit, and 32-bit word sizes.

- Mono and stereo audio data supported.

- The sampling frequency can range from 16 kHz to 192 kHz (16, 22.05, 32, 44.1, 48, 96, 192) kHz.

- Support for an audio master clock.

- Configurable word select period in master mode (separately for I<sup>2</sup>S-bus input and output).

- Two 8-word FIFO data buffers are provided, one for transmit and one for receive.

- Generates interrupt requests when buffer levels cross a programmable boundary.

- Two DMA requests controlled by programmable buffer levels. The DMA requests are connected to the GPDMA block.

- Controls include reset, stop and mute options separately for I<sup>2</sup>S-bus input and I<sup>2</sup>S-bus output.

### 7.18.7 C\_CAN

Remark: The LPC4350/30/20/10 contain two C\_CAN controllers.

Controller Area Network (CAN) is the definition of a high performance communication protocol for serial data communication. The C\_CAN controller is designed to provide a full implementation of the CAN protocol according to the CAN Specification Version 2.0B. The C\_CAN controller can create powerful local networks with low-cost multiplex wiring by supporting distributed real-time control with a high level of reliability.

#### 7.18.7.1 Features

- Conforms to protocol version 2.0 parts A and B.

- Supports bit rate of up to 1 Mbit/s.

- Supports 32 Message Objects.

- Each Message Object has its own identifier mask.

- Provides programmable FIFO mode (concatenation of Message Objects).

- Provides maskable interrupts.

- Supports Disabled Automatic Retransmission (DAR) mode for time-triggered CAN applications.

- Provides programmable loop-back mode for self-test operation.

### 32-bit ARM Cortex-M4/M0 microcontroller

- Increments/decrements depending on direction.

- Programmable for 2× or 4× position counting.

- Velocity capture using built-in timer.

- Velocity compare function with "less than" interrupt.

- Uses 32-bit registers for position and velocity.

- Three position-compare registers with interrupts.

- Index counter for revolution counting.

- Index compare register with interrupts.

- Can combine index and position interrupts to produce an interrupt for whole and partial revolution displacement.

- Digital filter with programmable delays for encoder input signals.

- Can accept decoded signal inputs (clk and direction).

### 7.19.4 Repetitive Interrupt (RI) timer

The repetitive interrupt timer provides a free-running 32-bit counter which is compared to a selectable value, generating an interrupt when a match occurs. Any bits of the timer/compare function can be masked such that they do not contribute to the match detection. The repetitive interrupt timer can be used to create an interrupt that repeats at predetermined intervals.

### 7.19.4.1 Features

- 32-bit counter. Counter can be free-running or be reset by a generated interrupt.

- 32-bit compare value.

- 32-bit compare mask. An interrupt is generated when the counter value equals the compare value, after masking. This mechanism allows for combinations not possible with a simple compare.

### 7.19.5 Windowed WatchDog Timer (WWDT)

The purpose of the watchdog is to reset the controller if software fails to periodically service it within a programmable time window.

#### 7.19.5.1 Features

- Internally resets chip if not periodically reloaded during the programmable time-out period.

- Optional windowed operation requires reload to occur between a minimum and maximum time period, both programmable.

- Optional warning interrupt can be generated at a programmable time prior to watchdog time-out.

- Enabled by software but requires a hardware reset or a watchdog reset/interrupt to be disabled.

- Incorrect feed sequence causes reset or interrupt if enabled.

- Flag to indicate watchdog reset.

- Programmable 24-bit timer with internal prescaler.

LPC4350 30 20 10

### 32-bit ARM Cortex-M4/M0 microcontroller

### 7.22.4 Internal RC oscillator (IRC)

The IRC is used as the clock source for the WWDT and/or as the clock that drives the PLLs and the CPU. The nominal IRC frequency is 12 MHz. The IRC is trimmed to 1.5 % accuracy over the entire voltage and temperature range.

Upon power-up or any chip reset, the LPC4350/30/20/10 use the IRC as the clock source. The boot loader then configures the PLL1 to provide a 96 MHz clock for the core and the PLL0USB or PLL0AUDIO as needed if an external boot source is selected.

### 7.22.5 PLL0USB (for USB0)

PLL0 is a dedicated PLL for the USB0 High-speed controller.

PLL0 accepts an input clock frequency from an external oscillator in the range of 14 kHz to 25 MHz. The input frequency is multiplied up to a high frequency with a Current Controlled Oscillator (CCO). The CCO operates in the range of 4.3 MHz to 550 MHz.

### 7.22.6 PLL0AUDIO (for audio)

The audio PLL PLL0AUDIO is a general-purpose PLL with a small step size. This PLL accepts an input clock frequency derived from an external oscillator or internal IRC. The input frequency is multiplied up to a high frequency with a Current Controlled Oscillator (CCO). A sigma-delta converter modulates the PLL divider ratios to obtain the desired output frequency. The output frequency can be set as a multiple of the sampling frequency  $f_s$  to  $32 \times f_s$ ,  $64 \times f_s$ ,  $128 \times f_s$ ,  $256 \times f_s$ ,  $384 \times f_s$ ,  $512 \times f_s$  and the sampling frequency  $f_s$  can range from 16 kHz to 192 kHz (16, 22.05, 32, 44.1, 48, 96,192) kHz. Many other frequencies are possible as well using the integrated fractional divider.

### 7.22.7 System PLL1

The PLL1 accepts an input clock frequency from an external oscillator in the range of 1 MHz to 25 MHz. The input frequency is multiplied up to a high frequency with a Current Controlled Oscillator (CCO). The multiplier can be an integer value from 1 to 32. The CCO operates in the range of 156 MHz to 320 MHz. This range is possible through an additional divider in the loop to keep the CCO within its frequency range while the PLL is providing the desired output frequency. The output divider can be set to divide by 2, 4, 8, or 16 to produce the output clock. Since the minimum output divider value is 2, it is insured that the PLL output has a 50 % duty cycle. The PLL is turned off and bypassed following a chip reset. After reset, software can enable the PLL. The program must configure and activate the PLL, wait for the PLL to lock, and then connect to the PLL as a clock source. The PLL settling time is 100  $\mu$ s.

### 7.22.8 Reset Generation Unit (RGU)

The RGU allows generation of independent reset signals for individual blocks and peripherals on the LPC4350/30/20/10.

### 7.22.9 Power control

The LPC4350/30/20/10 feature several independent power domains to control power to the core and the peripherals (see Figure 9). The RTC and its associated peripherals (the alarm timer, the CREG block, the OTP controller, the back-up registers, and the event router) are located in the RTC power-domain. The main regulator or a battery supply can power the RTC. A power selector switch ensures that the RTC block is always powered on.

### 32-bit ARM Cortex-M4/M0 microcontroller

### 10.2 Peripheral power consumption

The typical power consumption at T = 25  $^{\circ}$ C for each individual peripheral is measured as follows:

- 1. Enable all branch clocks and measure the current I<sub>DD(REG)(3V3)</sub>.

- 2. Disable the branch clock to the peripheral to be measured and keep all other branch clocks enabled.

- 3. Calculate the difference between measurement 1 and 2. The result is the peripheral power consumption.

| Peripheral | Branch clock               | I <sub>DD(REG)(3V3)</sub> in mA    |                                    |

|------------|----------------------------|------------------------------------|------------------------------------|

|            |                            | Branch clock<br>frequency = 48 MHz | Branch clock<br>frequency = 96 MHz |

| M0 core    | CLK_M4_M0APP               | 3.3                                | 6.6                                |

| I2C1       | CLK_APB3_I2C1              | 0.01                               | 0.02                               |

| I2C0       | CLK_APB1_I2C0              | 0.02                               | 0.01                               |

| DAC        | CLK_APB3_DAC               | 0.01                               | 0.02                               |

| ADC0       | CLK_APB3_ADC0              | 0.05                               | 0.05                               |

| ADC1       | CLK_APB3_ADC1              | 0.04                               | 0.04                               |

| CAN0       | CLK_APB3_CAN0              | 0.17                               | 0.17                               |

| CAN1       | CLK_APB1_CAN1              | 0.17                               | 0.17                               |

| MOTOCON    | CLK_APB1_MOTOCON           | 0.05                               | 0.05                               |

| 12S        | CLK_APB1_I2S               | 0.11                               | 0.11                               |

| SPIFI      | CLK_SPIFI,<br>CLK_M4_SPIFI | 0.95                               | 1.85                               |

| GPIO       | CLK_M4_GPIO                | 0.66                               | 1.31                               |

Table 11. Peripheral power consumption

32-bit ARM Cortex-M4/M0 microcontroller

LPC4350\_30\_20\_10

### 32-bit ARM Cortex-M4/M0 microcontroller

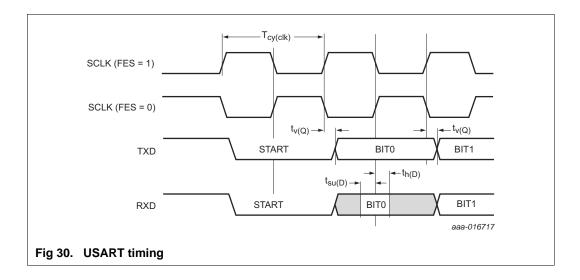

### 11.11 SSP interface

#### Table 24. Dynamic characteristics: SSP pins in SPI mode

$T_{amb} = -40$  °C to +85 °C; 2.2 V  $\leq V_{DD(REG)(3V3)} \leq 3.6$  V; 2.7 V  $\leq V_{DD(IO)} \leq 3.6$  V;  $C_L = 20$  pF. Sampled at 10 % and 90 % of the signal level; EHS = 1 for all pins. Simulated values.

| Symbol               | Parameter                 | Conditions                                                  |     | Min                           | Тур | Мах                           | Unit |

|----------------------|---------------------------|-------------------------------------------------------------|-----|-------------------------------|-----|-------------------------------|------|

| SSP mas              | ter                       |                                                             |     |                               |     |                               |      |

| T <sub>cy(clk)</sub> | clock cycle time          | full-duplex mode                                            | [1] | 1/(25.5 × 10 <sup>6</sup> )   | -   | -                             | s    |

|                      |                           | when only transmitting                                      |     | 1/(51 × 10 <sup>6</sup> )     | -   | -                             | s    |

| t <sub>DS</sub>      | data set-up time          | in SPI mode                                                 |     | 13.6                          | -   | -                             | ns   |

| t <sub>DH</sub>      | data hold time            | in SPI mode                                                 |     | -3.8                          | -   | -                             | ns   |

| t <sub>v(Q)</sub>    | data output valid<br>time | in SPI mode                                                 |     | -                             | -   | 6.0                           | ns   |

| t <sub>h(Q)</sub>    | data output hold<br>time  | in SPI mode                                                 |     | -1.1                          | -   | -                             | ns   |

| t <sub>lead</sub>    | lead time                 | continuous transfer mode<br>SPI mode; CPOL = 0;<br>CPHA = 0 |     | T <sub>cy(clk)</sub> + 3.2    | -   | T <sub>cy(clk)</sub> + 6.1    | ns   |

|                      |                           | SPI mode; CPOL = 0;<br>CPHA = 1                             |     | $0.5\times T_{cy(clk)} + 3.2$ | -   | $0.5 	imes T_{cy(clk)}$ + 6.1 | ns   |

|                      |                           | SPI mode; CPOL = 1;<br>CPHA = 0                             |     | T <sub>cy(clk)</sub> + 3.2    | -   | T <sub>cy(clk)</sub> + 6.1    | ns   |

|                      |                           | SPI mode; CPOL = 1;<br>CPHA = 1                             |     | $0.5\times T_{cy(clk)} + 3.2$ | -   | $0.5 	imes T_{cy(clk)}$ + 6.1 | ns   |

|                      |                           | synchronous serial frame mode                               |     | $0.5\times T_{cy(clk)} + 3.2$ | -   | $0.5 	imes T_{cy(clk)}$ + 6.1 | ns   |

|                      |                           | microwire frame format                                      |     | T <sub>cy(clk)</sub> + 3.2    | -   | T <sub>cy(clk)</sub> + 6.1    | ns   |

| t <sub>lag</sub>     | lag time                  | continuous transfer mode<br>SPI mode; CPOL = 0;<br>CPHA = 0 |     | $0.5 \times T_{cy(clk)}$      | -   | -                             | ns   |

|                      |                           | SPI mode; CPOL = 0;<br>CPHA = 1                             |     | T <sub>cy(clk)</sub>          | -   | -                             | ns   |

|                      |                           | SPI mode; CPOL = 1;<br>CPHA = 0                             |     | $0.5 \times T_{cy(clk)}$      | -   | -                             | ns   |

|                      |                           | SPI mode; CPOL = 1;<br>CPHA = 1                             |     | T <sub>cy(clk)</sub>          | -   | -                             | ns   |

|                      |                           | synchronous serial<br>frame mode                            |     | T <sub>cy(clk)</sub>          | -   | -                             | ns   |

|                      |                           | microwire frame format                                      |     | $0.5 	imes T_{cy(clk)}$       | -   | -                             | ns   |

#### 32-bit ARM Cortex-M4/M0 microcontroller

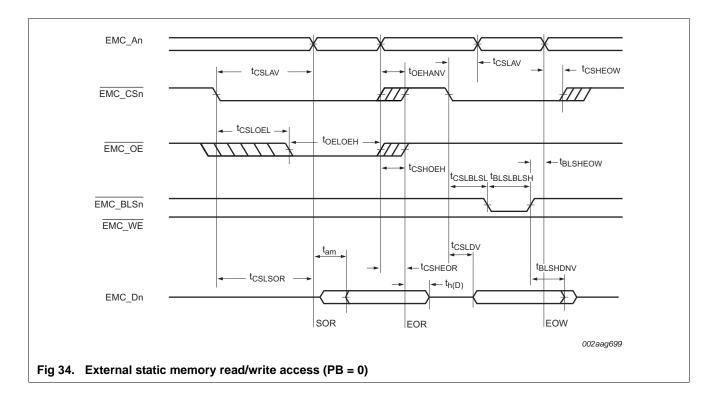

#### Table 27. Dynamic characteristics: Static asynchronous external memory interface ...continued

$C_L = 22 \text{ pF}$  for EMC\_Dn  $C_L = 20 \text{ pF}$  for all others;  $T_{amb} = -40 \text{ °C}$  to +85 °C;  $2.2 \text{ V} \le V_{DD(REG)(3V3)} \le 3.6 \text{ V}$ ; 2.7  $\text{V} \le V_{DD(IO)} \le 3.6 \text{ V}$ ; values guaranteed by design; the values in the table have been calculated with WAITTURN = 0x0 in STATICWAITTURN register. Timing parameters are given for single memory access cycles. In a normal read operation, the EMC changes the address while CS is asserted resulting in multiple memory accesses.

| Symbol                | Parameter <sup>[1]</sup>        | Conditions |                | Min                                                           | Тур | Max                                                                                      | Unit |

|-----------------------|---------------------------------|------------|----------------|---------------------------------------------------------------|-----|------------------------------------------------------------------------------------------|------|

| t <sub>BLSLBLSH</sub> | BLS LOW to BLS HIGH time        | PB = 0     | [2]            | -0.9 +<br>(WAITWR –<br>WAITWEN + 1) ×<br>T <sub>cy(clk)</sub> | -   | $\begin{array}{c} -0.1 + \\ (WAITWR - \\ WAITWEN + 1) \times \\ T_{cy(clk)} \end{array}$ | ns   |

| t <sub>BLSHEOW</sub>  | BLS HIGH to end of write time   | PB = 0     | [2]<br>[5]     | -1.9 + T <sub>cy(clk)</sub>                                   | -   | $-0.5 + T_{cy(clk)}$                                                                     | ns   |

| t <sub>BLSHDNV</sub>  | BLS HIGH to data invalid time   | PB = 0     | [1]<br>[2<br>] | -2.5 + T <sub>cy(clk)</sub>                                   | -   | 1.4 + T <sub>cy(clk)</sub>                                                               | ns   |

| t <sub>CSHEOW</sub>   | CS HIGH to end of write time    |            | [5]            | -2.0                                                          | -   | 0                                                                                        | ns   |

| t <sub>BLSHDNV</sub>  | BLS HIGH to data invalid time   | PB = 1     |                | -2.5                                                          | -   | 1.4                                                                                      | ns   |

| t <sub>WEHANV</sub>   | WE HIGH to address invalid time | PB = 1     |                | -0.9 + T <sub>cy(clk)</sub>                                   | -   | 2.4 + T <sub>cy(clk)</sub>                                                               | ns   |

[1] Parameters specified for 40 % of  $V_{DD(IO)}$  for rising edges and 60 % of  $V_{DD(IO)}$  for falling edges.

[2]  $T_{cy(clk)} = 1/CCLK$  (see LPC43xx User manual).

[4] Start Of Read (SOR): longest of t<sub>CSLAV</sub>, t<sub>CSLOEL</sub>, t<sub>CSLBLSL</sub>.

[5] End Of Write (EOW): earliest of address not valid or EMC\_BLSn HIGH.

All information provided in this document is subject to legal disclaimers

LPC4350 30 20 10

### 32-bit ARM Cortex-M4/M0 microcontroller

| Symbol                | Parameter                     | Conditions                     |     | Min | Тур | Max | Unit |

|-----------------------|-------------------------------|--------------------------------|-----|-----|-----|-----|------|

| High-spe              | ed mode                       |                                |     |     |     |     |      |

| P <sub>cons</sub>     | power consumption             |                                | [2] | -   | 68  | -   | mW   |

| I <sub>DDA(3V3)</sub> | analog supply current (3.3 V) | on pin USB0_VDDA3V3_DRIVER;    | [3] |     |     |     |      |

|                       |                               | total supply current           |     | -   | 18  | -   | mA   |

|                       |                               | during transmit                |     | -   | 31  | -   | mA   |

|                       |                               | during receive                 |     | -   | 14  | -   | mA   |

|                       |                               | with driver tri-stated         |     | -   | 14  | -   | mA   |

| I <sub>DDD</sub>      | digital supply current        |                                |     | -   | 7   | -   | mA   |

| Full-spee             | d/low-speed mode              |                                |     |     | -   | -   |      |

| P <sub>cons</sub>     | power consumption             |                                | [2] | -   | 15  | -   | mW   |

| I <sub>DDA(3V3)</sub> | analog supply current (3.3 V) | on pin USB0_VDDA3V3_DRIVER;    |     |     |     |     |      |

|                       |                               | total supply current           |     | -   | 3.5 | -   | mA   |

|                       |                               | during transmit                |     | -   | 5   | -   | mA   |

|                       |                               | during receive                 |     | -   | 3   | -   | mA   |

|                       |                               | with driver tri-stated         |     | -   | 3   | -   | mA   |

| I <sub>DDD</sub>      | digital supply current        |                                |     | -   | 3   | -   | mA   |

| Suspend               | mode                          |                                |     |     |     |     | 1    |

| I <sub>DDA(3V3)</sub> | analog supply current (3.3 V) |                                |     | -   | 24  | -   | μA   |

|                       |                               | with driver tri-stated         |     | -   | 24  | -   | μA   |

|                       |                               | with OTG functionality enabled |     | -   | 3   | -   | mA   |

| I <sub>DDD</sub>      | digital supply current        |                                |     | -   | 30  | -   | μA   |

| VBUS de               | tector outputs                |                                |     |     |     |     | 1    |

| V <sub>th</sub>       | threshold voltage             | for VBUS valid                 |     | 4.4 | -   | -   | V    |

|                       |                               | for session end                |     | 0.2 | -   | 0.8 | V    |

|                       |                               | for A valid                    |     | 0.8 | -   | 2   | V    |

|                       |                               | for B valid                    |     | 2   | -   | 4   | V    |

| V <sub>hys</sub>      | hysteresis voltage            | for session end                |     | -   | 150 | 10  | mV   |

|                       |                               | A valid                        |     | -   | 200 | 10  | mV   |

|                       |                               | B valid                        |     | -   | 200 | 10  | mV   |

#### Table 31. Static characteristics: USB0 PHY pins<sup>[1]</sup>

[1] Characterized but not implemented as production test.

[2] Total average power consumption.

[3] The driver is active only 20 % of the time.

### 11.17 Ethernet

**Remark:** The timing characteristics of the ENET\_MDC and ENET\_MDIO signals comply with the *IEEE standard 802.3*.

LPC4350\_30\_20\_10

### **NXP Semiconductors**

# LPC4350/30/20/10

32-bit ARM Cortex-M4/M0 microcontroller

32-bit ARM Cortex-M4/M0 microcontroller

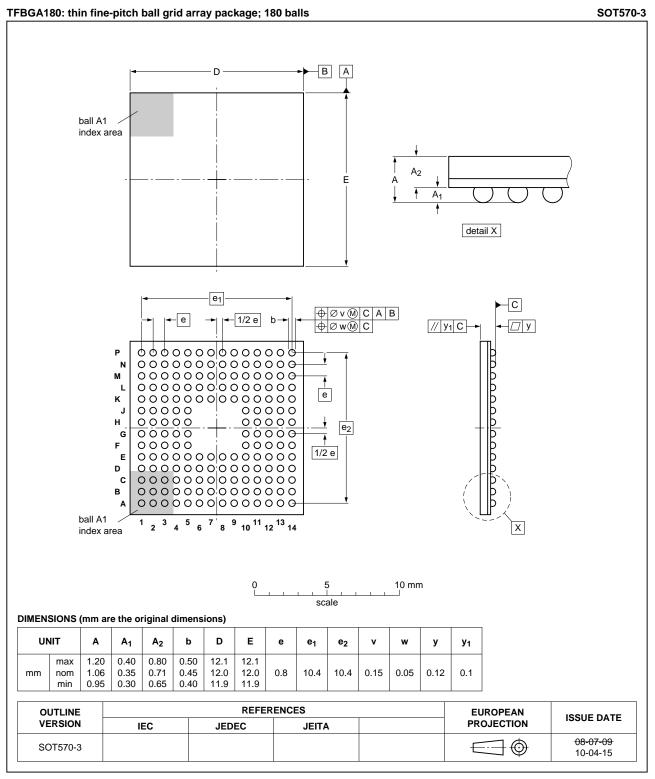

Fig 52. Package outline of the TFBGA180 package

LPC4350\_30\_20\_10

#### 32-bit ARM Cortex-M4/M0 microcontroller

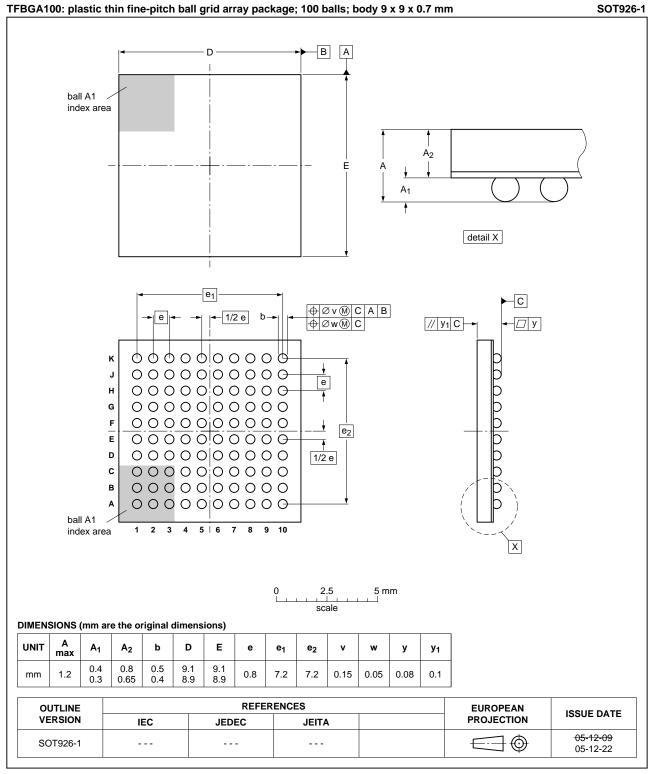

Fig 53. Package outline of the TFBGA100 package

All information provided in this document is subject to legal disclaimers.

LPC4350 30 20 10

### **NXP Semiconductors**

# LPC4350/30/20/10

### 32-bit ARM Cortex-M4/M0 microcontroller

32-bit ARM Cortex-M4/M0 microcontroller

## 16. Abbreviations

| Acronym         Description           ADC         Analog-to-Digital Converter           AHB         Advanced High-performance Bus           APB         Advanced Peripheral Bus           API         Application Programming Interface           BOD         BrownOut Detection           CAN         Controller Area Network           CMAC         Cipher-based Message Authentication Code           CSMA/CD         Carrier Sense Multiple Access with Collision Detection           DAC         Digital-to-Analog Converter           DC-DC         Direct Current-to-Direct Current           DMA         Direct Memory Access           GPIO         General-Purpose Input/Output           IRC         Internal RC           IrDA         Infrared Data Association           JTAG         Joint Test Action Group           LCD         Liquid Crystal Display           LSB         Least Significant Bit           MAC         Media Access Control           MCU         MicroController Unit           MIIM         Media Independent Interface Management           n.c.         not connected           OHCI         Open Host Controller Interface           OTG         On-The-Go           PHY |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AHB       Advanced High-performance Bus         APB       Advanced Peripheral Bus         API       Application Programming Interface         BOD       BrownOut Detection         CAN       Controller Area Network         CMAC       Cipher-based Message Authentication Code         CSMA/CD       Carrier Sense Multiple Access with Collision Detection         DAC       Digital-to-Analog Converter         DC-DC       Direct Current-to-Direct Current         DMA       Direct Memory Access         GPIO       General-Purpose Input/Output         IRC       Internal RC         IrDA       Infrared Data Association         JTAG       Joint Test Action Group         LCD       Liquid Crystal Display         LSB       Least Significant Bit         MAC       Media Access Control         MCU       MicroController Unit         MIIM       Media Independent Interface Management         n.c.       not connected         OHCI       Open Host Controller Interface         OTG       On-The-Go         PHY       Physical Layer         PLL       Phase-Locked Loop                                                                                                                        |

| APBAdvanced Peripheral BusAPIApplication Programming InterfaceBODBrownOut DetectionCANController Area NetworkCMACCipher-based Message Authentication CodeCSMA/CDCarrier Sense Multiple Access with Collision DetectionDACDigital-to-Analog ConverterDC-DCDirect Current-to-Direct CurrentDMADirect Memory AccessGPIOGeneral-Purpose Input/OutputIRCInternal RCIrDAInfrared Data AssociationJTAGJoint Test Action GroupLCDLiquid Crystal DisplayLSBLeast Significant BitMACMedia Access ControlMCUMicroController UnitMIIMMedia Independent Interface Managementn.c.not connectedOHCIOpen Host Controller InterfaceOTGOn-The-GoPHYPhysical LayerPLLPhase-Locked Loop                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| APIApplication Programming InterfaceBODBrownOut DetectionCANController Area NetworkCMACCipher-based Message Authentication CodeCSMA/CDCarrier Sense Multiple Access with Collision DetectionDACDigital-to-Analog ConverterDC-DCDirect Current-to-Direct CurrentDMADirect Memory AccessGPIOGeneral-Purpose Input/OutputIRCInternal RCIrDAInfrared Data AssociationJTAGJoint Test Action GroupLCDLiquid Crystal DisplayLSBLeast Significant BitMACMedia Access ControlMCUMicroController UnitMIIMMedia Independent Interface Managementn.c.not connectedOTGOn-The-GoPHYPhysical LayerPLLPhase-Locked Loop                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| BODBrownOut DetectionCANController Area NetworkCMACCipher-based Message Authentication CodeCSMA/CDCarrier Sense Multiple Access with Collision DetectionDACDigital-to-Analog ConverterDC-DCDirect Current-to-Direct CurrentDMADirect Memory AccessGPIOGeneral-Purpose Input/OutputIRCInternal RCIrDAInfrared Data AssociationJTAGJoint Test Action GroupLCDLiquid Crystal DisplayLSBLeast Significant BitMACMedia Access ControlMCUMicroController UnitMIIMMedia Independent Interface Managementn.c.not connectedOHCIOpen Host Controller InterfaceOTGOn-The-GoPHYPhysical LayerPLLPhase-Locked Loop                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| CANController Area NetworkCMACCipher-based Message Authentication CodeCSMA/CDCarrier Sense Multiple Access with Collision DetectionDACDigital-to-Analog ConverterDC-DCDirect Current-to-Direct CurrentDMADirect Memory AccessGPIOGeneral-Purpose Input/OutputIRCInternal RCIrDAInfrared Data AssociationJTAGJoint Test Action GroupLCDLiquid Crystal DisplayLSBLeast Significant BitMACMedia Access ControlMCUMicroController UnitMIIMMedia Independent Interface Managementn.c.not connectedOTGOn-The-GoPHYPhysical LayerPLLPhase-Locked Loop                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| CMACCipher-based Message Authentication CodeCSMA/CDCarrier Sense Multiple Access with Collision DetectionDACDigital-to-Analog ConverterDC-DCDirect Current-to-Direct CurrentDMADirect Memory AccessGPIOGeneral-Purpose Input/OutputIRCInternal RCIrDAInfrared Data AssociationJTAGJoint Test Action GroupLCDLiquid Crystal DisplayLSBLeast Significant BitMACMedia Access ControlMCUMicroController UnitMIIMMedia Independent Interface Managementn.c.not connectedOTGOn-The-GoPHYPhysical LayerPLLPhase-Locked Loop                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| CSMA/CDCarrier Sense Multiple Access with Collision DetectionDACDigital-to-Analog ConverterDC-DCDirect Current-to-Direct CurrentDMADirect Memory AccessGPIOGeneral-Purpose Input/OutputIRCInternal RCIrDAInfrared Data AssociationJTAGJoint Test Action GroupLCDLiquid Crystal DisplayLSBLeast Significant BitMACMedia Access ControlMCUMicroController UnitMIIMMedia Independent Interface Managementn.c.not connectedOHCIOpen Host Controller InterfaceOTGOn-The-GoPHYPhysical LayerPLLPhase-Locked Loop                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| DACDigital-to-Analog ConverterDC-DCDirect Current-to-Direct CurrentDMADirect Memory AccessGPIOGeneral-Purpose Input/OutputIRCInternal RCIrDAInfrared Data AssociationJTAGJoint Test Action GroupLCDLiquid Crystal DisplayLSBLeast Significant BitMACMedia Access ControlMCUMicroController UnitMIIMMedia Independent Interface Managementn.c.not connectedOHCIOpen Host Controller InterfaceOTGOn-The-GoPHYPhysical LayerPLLPhase-Locked Loop                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| DC-DCDirect Current-to-Direct CurrentDMADirect Memory AccessGPIOGeneral-Purpose Input/OutputIRCInternal RCIrDAInfrared Data AssociationJTAGJoint Test Action GroupLCDLiquid Crystal DisplayLSBLeast Significant BitMACMedia Access ControlMCUMicroController UnitMIIMMedia Independent Interface Managementn.c.not connectedOTGOn-The-GoPHYPhysical LayerPLLPhase-Locked Loop                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |