Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                        |

|----------------------------|--------------------------------------------------------|

| Product Status             | Obsolete                                               |

| Core Processor             | Z8                                                     |

| Core Size                  | 8-Bit                                                  |

| Speed                      | 16MHz                                                  |

| Connectivity               | -                                                      |

| Peripherals                | POR, WDT                                               |

| Number of I/O              | 24                                                     |

| Program Memory Size        | 4KB (4K x 8)                                           |

| Program Memory Type        | OTP                                                    |

| EEPROM Size                | -                                                      |

| RAM Size                   | 237 x 8                                                |

| Voltage - Supply (Vcc/Vdd) | 3.5V ~ 5.5V                                            |

| Data Converters            | -                                                      |

| Oscillator Type            | Internal                                               |

| Operating Temperature      | 0°C ~ 70°C (TA)                                        |

| Mounting Type              | Surface Mount                                          |

| Package / Case             | 28-LCC (J-Lead)                                        |

| Supplier Device Package    | -                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z86e3016vsg |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Power connections follow conventional descriptions below:

| Connection | Circuit         | Device          |

|------------|-----------------|-----------------|

| Power      | V <sub>CC</sub> | $V_{DD}$        |

| Ground     | GND             | V <sub>SS</sub> |

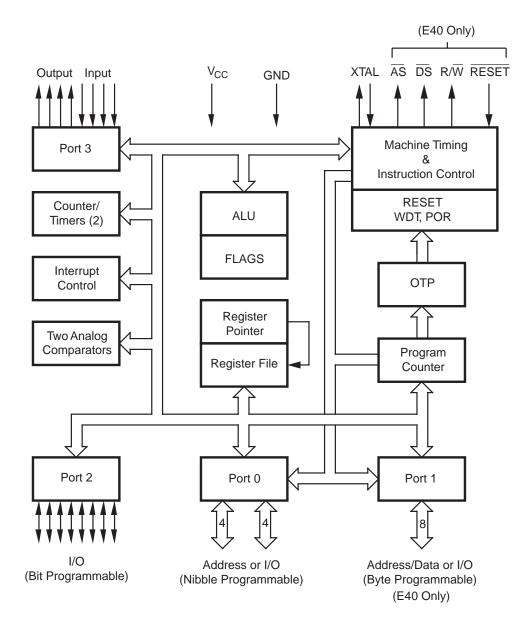

Figure 1. Z86E30/E31/E40 Functional Block Diagram

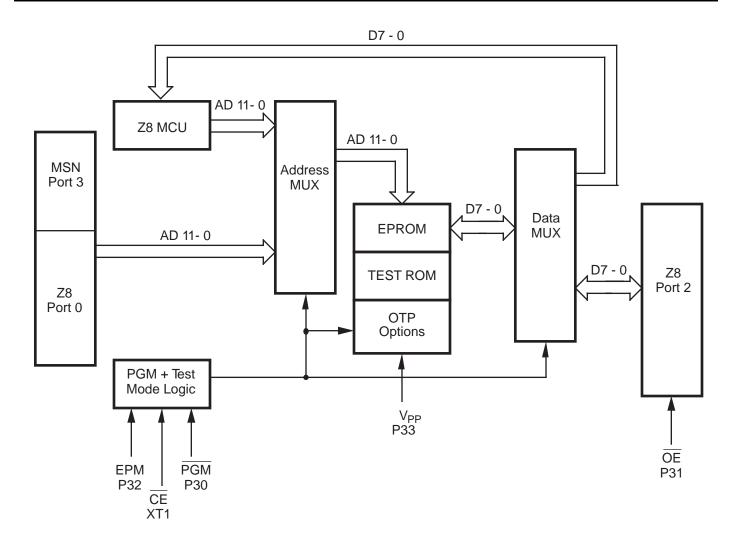

Figure 2. EPROM Programming Block Diagram

#### PIN IDENTIFICATION

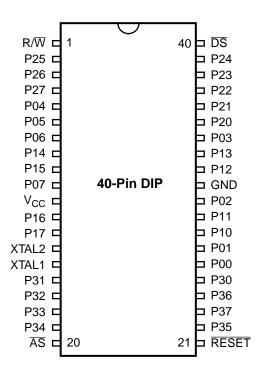

Figure 3. 40-Pin DIP Pin Configuration Standard Mode

Table 1. 40-Pin DIP Pin Identification Standard Mode

| Pin # | Symbol          | Function               | Direction |

|-------|-----------------|------------------------|-----------|

| 1     | R/W             | Read/Write             | Output    |

| 2–4   | P25-P27         | Port 2, Pins 5,6,7     | In/Output |

| 5–7   | P04-P06         | Port 0, Pins 4,5,6     | In/Output |

| 8–9   | P14-P15         | Port 1, Pins 4,5       | In/Output |

| 10    | P07             | Port 0, Pin 7          | In/Output |

| 11    | V <sub>CC</sub> | Power Supply           |           |

| 12–13 | P16-P17         | Port 1, Pins 6,7       | In/Output |

| 14    | XTAL2           | Crystal Oscillator     | Output    |

| 15    | XTAL1           | Crystal Oscillator     | Input     |

| 16–18 | P31-P33         | Port 3, Pins 1,2,3     | Input     |

| 19    | P34             | Port 3, Pin 4          | Output    |

| 20    | ĀS              | Address Strobe         | Output    |

| 21    | RESET           | Reset                  | Input     |

| 22    | P35             | Port 3, Pin 5          | Output    |

| 23    | P37             | Port 3, Pin 7          | Output    |

| 24    | P36             | Port 3, Pin 6          | Output    |

| 25    | P30             | Port 3, Pin 0          | Input     |

| 26–27 | P00-P01         | Port 0, Pins 0,1       | In/Output |

| 28–29 | P10-P11         | Port 1, Pins 0,1       | In/Output |

| 30    | P02             | Port 0, Pin 2          | In/Output |

| 31    | GND             | Ground                 |           |

| 32–33 | P12-P13         | Port 1, Pins 2,3       | In/Output |

| 34    | P03             | Port 0, Pin 3          | In/Output |

| 35–39 | P20-P24         | Port 2, Pins 0,1,2,3,4 | In/Output |

| 40    | DS              | Data Strobe            | Output    |

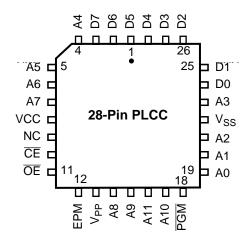

Figure 12. EPROM Programming Mode 28-Pin PLCC Pin Configuration

# Table 8. 28-Pin EPROM Pin Identification

| Pin # | Symbol          | Function        | Direction |

|-------|-----------------|-----------------|-----------|

| 1–3   | D5-D7           | Data 5,6,7      | In/Output |

| 4–7   | A4-A7           | Address 4,5,6,7 | Input     |

| 8     | V <sub>CC</sub> | Power Supply    |           |

| 9     | NC              | No connection   |           |

| 10    | CE              | Chip Select     | Input     |

| 11    | ŌĒ              | Output Enable   | Input     |

| 12    | EPM             | EPROM Prog.     | Input     |

|       |                 | Mode            |           |

| 13    | $V_{PP}$        | Prog. Voltage   | Input     |

| 14–15 | A8–A9           | Address 8,9     | Input     |

| 16    | A11             | Address 11      | Input     |

| 17    | A10             | Address 10      | Input     |

| 18    | PGM             | Prog. Mode      | Input     |

| 19–21 | A0-A2           | Address 0,1,2   | Input     |

| 22    | V <sub>SS</sub> | Ground          |           |

| 23    | A3              | Address 3       | Input     |

| 24–28 | D0-D4           | Data 0,1,2,3,4  | In/Output |

# DC ELECTRICAL CHARACTERISTICS (Continued)

|                     | $T_A = 0  ^{\circ}C \text{ to } +70  ^{\circ}C$ |          |      |     |         |       |                                       |        |

|---------------------|-------------------------------------------------|----------|------|-----|---------|-------|---------------------------------------|--------|

|                     |                                                 | $v_{cc}$ | **   |     | Typical |       |                                       |        |

| Sym                 | Parameter                                       | Note [3] | Min  | Max | @ 25°C  | Units | Conditions                            | Notes  |

| I <sub>CC</sub>     | Supply Current                                  | 3.5V     |      | 20  | 7       | mA    | @ 16 MHz                              | 4,5    |

|                     |                                                 | 5.5V     |      | 25  | 20      | mΑ    | @ 16 MHz                              | 4,5    |

| I <sub>CC1</sub>    | Standby Current                                 | 3.5V     |      | 8   | 3.7     | mA    | $V_{IN} = 0V, V_{CC}$                 | 4,5    |

|                     | Halt Mode                                       | 5.5V     |      | 8   | 3.7     | mΑ    | @ 16 MHz                              | 4,5    |

|                     |                                                 | 3.5V     |      | 7.0 | 2.9     | mA    | Clock Divide by                       | 4,5    |

|                     |                                                 | 5.5V     |      | 7.0 | 2.9     | mΑ    | 16 @ 16 MHz                           | 4,5    |

| I <sub>CC2</sub>    | Standby Current                                 | 3.5V     |      | 10  | 2       | μΑ    | $V_{IN} = 0V, V_{CC}$                 | 6,11   |

| 002                 | Stop Mode                                       | 5.5V     |      | 10  | 3       | μΑ    | $V_{IN} = 0V, V_{CC}$                 | 6,11   |

|                     |                                                 | 3.5V     |      | 800 | 600     | μΑ    | $V_{IN} = 0V, V_{CC}$                 | 6,11,1 |

|                     |                                                 | 5.5V     |      | 800 | 600     | μΑ    |                                       | 4      |

|                     |                                                 |          |      |     |         | ·     | $V_{IN} = 0V, V_{CC}$                 | 6,11,1 |

|                     |                                                 |          |      |     |         |       |                                       | 4      |

| I <sub>ALL</sub>    | Auto Latch                                      | 3.5V     | 0.7  | 8   | 2.4     | μΑ    | 0V <v<sub>IN<v<sub>CC</v<sub></v<sub> | 9      |

|                     | Low Current                                     | 5.5V     | 1.4  | 15  | 4.7     | μΑ    | 0V <v<sub>IN<v<sub>CC</v<sub></v<sub> | 9      |

| I <sub>ALH</sub>    | Auto Latch                                      | 3.5V     | -0.6 | -5  | -1.8    | μΑ    | 0V <v<sub>IN<v<sub>CC</v<sub></v<sub> | 9      |

| ALIT                | High Current                                    | 5.5V     | -1   | -8  | -3.8    | μA    | 0V <v<sub>IN<v<sub>CC</v<sub></v<sub> | 9      |

| T <sub>POR</sub>    | Power On Reset                                  | 3.5V     | 3.0  | 24  | 7       | ms    |                                       |        |

| . •                 |                                                 | 5.5V     | 2.0  | 13  | 4       | ms    |                                       |        |

| $\overline{V_{LV}}$ | Auto Reset Voltage                              |          | 2.3  | 3.1 | 2.9     | V     |                                       | 1,7    |

#### Notes:

- 1. Device does function down to the Auto Reset voltage.

- 2. GND=0V

- 3. The V<sub>CC</sub> voltage specification of 5.5V guarantees 5.0V  $\pm$  0.5V and the V<sub>CC</sub> voltage specification of 3.5V guarantees only 3.5V.

- 4. All outputs unloaded, I/O pins floating, inputs at rail.

- 5. CL1= CL2 = 22 pF

- 6. Same as note [4] except inputs at  $V_{CC.}$

- 7. Max. temperature is 70°C.

- 8. STD Mode (not Low EMI Mode)

- 9. Auto Latch (mask option) selected

- 10. For analog comparator inputs when analog comparators are enabled.

- 11. Clock must be forced Low, when XTAL1 is clock driven and XTAL2 is floating.

- 12. Typicals are at  $V_{CC} = 5.0V$  and  $V_{CC} = 3.5V$

- 13. Z86E40 only

- 14. WDT running

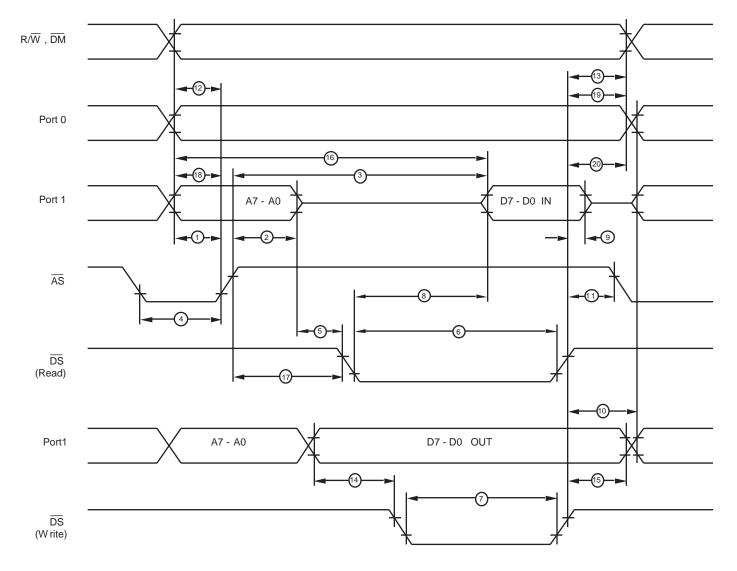

Figure 14. External I/O or Memory Read/Write Timing Z86E40 Only

# **DC ELECTRICAL CHARACTERISTICS** (Continued)

|    |           |                                                      | Note [3]        | T <sub>A</sub> = 0°C to 70°C<br>16 MHz<br>Note [3] |     |       |       |

|----|-----------|------------------------------------------------------|-----------------|----------------------------------------------------|-----|-------|-------|

| No | Symbol    | Parameter                                            | V <sub>CC</sub> | Min                                                | Max | Units | Notes |

| 1  | TdA(AS)   | Address Valid to AS Rise                             | 3.5V            | 25                                                 |     | ns    | 2     |

|    | ,         | Delay                                                | 5.5V            | 25                                                 |     | ns    |       |

| 2  | TdAS(A)   | AS Rise to Address Float                             | 3.5V            | 35                                                 |     | ns    | 2     |

|    |           | Delay                                                | 5.5V            | 35                                                 |     | ns    |       |

| 3  | TdAS(DR)  | AS Rise to Read Data Req'd                           | 3.5V            |                                                    | 180 | ns    | 1,2   |

|    |           | Valid                                                | 5.5V            |                                                    | 180 | ns    |       |

| 4  | TwAS      | AS Low Width                                         | 3.5V            | 40                                                 |     | ns    | 2     |

|    |           |                                                      | 5.5V            | 40                                                 |     | ns    |       |

| 5  | TdAS(DS)  | Address Float to DS Fall                             | 3.5V            | 0                                                  |     | ns    |       |

|    |           |                                                      | 5.5V            | 0                                                  |     | ns    |       |

| 6  | TwDSR     | DS (Read) Low Width                                  | 3.5V            | 135                                                |     | ns    | 1,2   |

|    |           |                                                      | 5.5V            | 135                                                |     | ns    |       |

| 7  | TwDSW     | DS (Write) Low Width                                 | 3.5V            | 80                                                 |     | ns    | 1,2   |

|    |           |                                                      | 5.5V            | 80                                                 |     | ns    |       |

| 8  | TdDSR(DR) | DS Fall to Read Data Req'd                           | 3.5V            |                                                    | 75  | ns    | 1,2   |

|    |           | Valid                                                | 5.5V            |                                                    | 75  | ns    |       |

| 9  | ThDR(DS)  | Read Data to DS Rise Hold                            | 3.5V            | 0                                                  |     | ns    | 2     |

|    |           | Time                                                 | 5.5V            | 0                                                  |     | ns    |       |

| 10 | TdDS(A)   | DS Rise to Address Active                            | 3.5V            | 50                                                 |     | ns    | 2     |

|    |           | Delay                                                | 5.5V            | 50                                                 |     | ns    |       |

| 11 | TdDS(AS)  | DS Rise to AS Fall Delay                             | 3.5V            | 35                                                 |     | ns    | 2     |

|    | , ,       | •                                                    | 5.5V            | 35                                                 |     | ns    |       |

| 12 | TdR/W(AS) | $R/\overline{W}$ Valid to $\overline{AS}$ Rise Delay | 3.5V            | 25                                                 |     | ns    | 2     |

|    | , ,       | ·                                                    | 5.5V            | 25                                                 |     | ns    |       |

| 13 | TdDS(R/W) | DS Rise to R/W Not Valid                             | 3.5V            | 35                                                 |     | ns    | 2     |

|    | , ,       |                                                      | 5.5V            | 35                                                 |     | ns    |       |

| 14 | TdDW(DSW) | Write Data Valid to DS Fall                          | 3.5V            | 55                                                 | 25  | ns    | 2     |

|    | ,         | (Write) Delay                                        | 5.5V            | 55                                                 | 25  | ns    |       |

| 15 | TdDS(DW)  | DS Rise to Write Data Not                            | 3.5V            | 35                                                 |     | ns    | 2     |

|    | ,         | Valid Delay                                          | 5.5V            | 35                                                 |     | ns    |       |

| 16 | TdA(DR)   | Address Valid to Read Data                           | 3.5V            |                                                    | 230 | ns    | 1,2   |

|    | ` ,       | Req'd Valid                                          | 5.5V            |                                                    | 230 | ns    | •     |

| 17 | TdAS(DS)  | AS Rise to DS Fall Delay                             | 3.5V            | 45                                                 |     | ns    | 2     |

|    | , ,       | •                                                    | 5.5V            | 45                                                 |     | ns    |       |

| 18 | TdDM(AS)  | DM Valid to AS Fall Delay                            | 3.5V            | 30                                                 |     | ns    | 2     |

|    | ` '       | ,                                                    | 5.5V            | 30                                                 |     | ns    |       |

| 20 | ThDS(AS)  | DS Valid to Address Valid                            | 3.5V            | 35                                                 |     | ns    |       |

| -  | · - /     | Hold Time                                            | 5.5V            | 35                                                 |     | ns    |       |

#### Notes:

- 1. When using extended memory timing, add 2 TpC.

- 2. Timing numbers given are for minimum TpC.

- 3. The V<sub>CC</sub> voltage specification of 5.5V guarantees 5.0V  $\pm$ 0.5V and the V<sub>CC</sub> voltage specification of 3.5V guarantees only 3.5V

# **Standard Test Load**

All timing references use 0.7  $\rm V_{CC}$  for a logic 1 and 0.2  $\rm V_{CC}$  for a logic 0.

For Standard Mode (not Low-EMI Mode for outputs) with SMR D1 = 0, D0 = 0.

# **Additional Timing Table**

|    | T <sub>A</sub> = -40 °C to +105 °C |                    |                 |      |      |       |            |         |

|----|------------------------------------|--------------------|-----------------|------|------|-------|------------|---------|

|    |                                    |                    |                 | 16 N | ИHz  |       |            |         |

|    |                                    |                    | V <sub>CC</sub> |      |      |       |            |         |

| No | Symbol                             | Parameter          | Note [6]        | Min  | Max  | Units | Conditions | Notes   |

| 1  | ТрС                                | Input Clock Period | 3.5V            | 62.5 | DC   | ns    |            | 1,7,8   |

|    |                                    |                    | 5.5V            | 62.5 | DC   | ns    |            | 1,7,8   |

| 2  | TrC,TfC                            | Clock Input Rise & | 3.5V            |      | 15   | ns    |            | 1,7,8   |

|    |                                    | Fall Times         | 5.5V            |      | 15   | ns    |            | 1,7,8   |

| 3  | TwC                                | Input Clock Width  | 3.5V            | 31   |      | ns    |            | 1,7,8   |

|    |                                    |                    | 5.5V            | 31   |      | ns    |            | 1,7,8   |

| 4  | TwTinL                             | Timer Input Low    | 3.5V            | 70   |      | ns    |            | 1,7,8   |

|    |                                    | Width              | 5.5V            | 70   |      | ns    |            | 1,7,8   |

| 5  | TwTinH                             | Timer Input High   | 3.5V            | 5TpC |      |       |            | 1,7,8   |

|    |                                    | Width              | 5.5V            | 5TpC |      |       |            | 1,7,8   |

| 6  | TpTin                              | Timer Input Period | 3.5V            | 8TpC |      |       |            | 1,7,8   |

|    | -                                  | •                  | 5.5V            | 8TpC |      |       |            | 1,7,8   |

| 7  | TrTin, TfTir                       | n Timer Input Rise | 3.5V            |      | 100  | ns    |            | 1,7,8   |

|    |                                    | & Fall Timer       | 5.5V            |      | 100  | ns    |            | 1,7,8   |

| 8A | TwIL                               | Int. Request Low   | 3.5V            | 70   |      | ns    |            | 1,2,7,8 |

|    |                                    | Time               | 5.5V            | 70   |      | ns    |            | 1,2,7,8 |

| 8B | TwIL                               | Int. Request Low   | 3.5V            | 5TpC |      |       |            | 1,3,7,8 |

|    |                                    | Time               | 5.5V            | 5TpC |      |       |            | 1,3,7,8 |

| 9  | TwIH                               | Int. Request Input | 3.5V            | 5TpC |      |       |            | 1,2,7,8 |

|    |                                    | High Time          | 5.5V            | ·    |      |       |            |         |

| 10 | Twsm                               | STOP Mode          | 3.5V            | 12   |      | ns    |            | 4,8     |

|    |                                    | Recovery Width     | 5.5V            | 12   |      | ns    |            | 4,8     |

|    |                                    | Spec               |                 |      |      |       |            |         |

| 11 | Tost                               | Oscillator Startup | 3.5V            |      | 5TpC |       |            | 4,8     |

|    |                                    | Time               | 5.5V            |      | 5TpC |       |            | 4,8     |

| 12 | Twdt                               | Watch-Dog Timer    | 3.5V            | 10   |      | ms    | D0 = 0     | 5,11    |

|    |                                    | Delay Time         | 5.5V            | 5    |      | ms    | D1 = 0     | 5,11    |

|    |                                    | Before Timeout     | 3.5V            | 20   |      | ms    | D0 = 1     | 5,11    |

|    |                                    |                    | 5.5V            | 10   |      | ms    | D1 = 0     | 5,11    |

|    |                                    | _                  | 3.5V            | 40   |      | ms    | D0 = 0     | 5,11    |

|    |                                    |                    | 5.5V            | 20   |      | ms    | D1 = 1     | 5,11    |

|    |                                    | _                  | 3.5V            | 160  |      | ms    | D0 = 1     | 5,11    |

|    |                                    |                    | 5.5V            | 80   |      | ms    | D1 = 1     | 5,11    |

|    |                                    |                    |                 |      |      |       |            |         |

#### Notes:

- 1. Timing Reference uses 0.7  $V_{CC}$  for a logic 1 and 0.2  $V_{CC}$  for a logic 0.

- 2. Interrupt request via Port 3 (P31-P33)

- 3. Interrupt request via Port 3 (P30)

- 4. SMR-D5 = 1, POR STOP Mode Delay is on

- 5. Reg. WDTMR

- 6. The  $V_{CC}$  voltage spec. of 5.5V guarantees 5.0V  $\pm$  0.5V.

- 7. SMR D1 = 0

- 8. Maximum frequency for internal system clock is 4 MHz when using XTAL divide-by-one mode.

- 9. For RC and LC oscillator, and for oscillator driven by clock driver.

- 10. Standard Mode (not Low EMI output ports)

- 11. Using internal RC

#### **PIN FUNCTIONS** (Continued)

Port 3 (P37-P30). Port 3 is an 8-bit, CMOS-compatible port with four fixed inputs (P33-P30) and four fixed outputs (P37-P34). These eight lines can be configured by software for interrupt and handshake control functions. Port 3, Pin 0 is Schmitt- triggered. P31, P32, and P33 are standard CMOS inputs with single trip point (no Auto Latches) and P34, P35, P36, and P37 are push-pull output lines. Low EMI output buffers can be globally programmed by the software. Two on-board comparators can process analog signals on P31 and P32 with reference to the voltage on P33. The analog function is enabled by setting the D1 of Port 3 Mode Register (P3M). The comparator output can be outputted from P34 and P37, respectively, by setting PCON register Bit D0 to 1 state. For the interrupt function, P30 and P33 are falling edge triggered interrupt inputs. P31 and P32 can be programmed as falling, rising or both edges triggered interrupt inputs (Figure 21). Access to Counter/Timer 1 is made through P31 (T<sub>IN</sub>) and P36 (TOUT). Handshake lines for Port 0, Port 1, and Port 2 are also available on Port 3 (Table 9).

**Note**: When enabling/ or disabling analog mode, the following is recommended:

- Allow two NOP delays before reading this comparator output.

- 2. Disable global interrupts, switch to analog mode, clear interrupts, and then re-enable interrupts.

- 3. IRQ register bits 3 to 0 must be cleared after enabling analog mode.

**Note:** P33–P30 differs from the Z86C30/C31/C40 in that there is no clamping diode to  $V_{CC}$  due to the EPROM high-voltage circuits. Exceeding the  $V_{IH}$  maximum specification during standard operating mode may cause the device to enter EPROM mode.

## **FUNCTIONAL DESCRIPTION** (Continued)

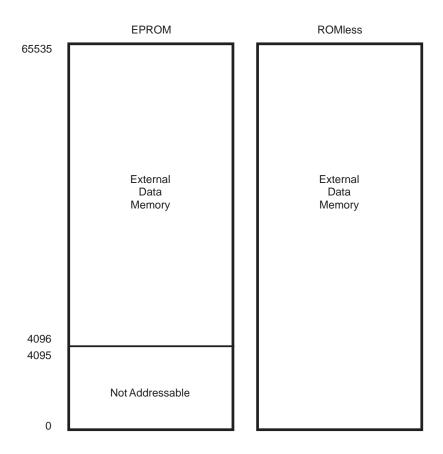

**Data Memory** ( $\overline{\text{DM}}$ ). In EPROM Mode, the Z86E40 can address up to 60 KB of external data memory beginning at location 4096. In ROMless mode, the Z86E40 can address up to 64 KB of data memory. External data memory may be included with, or separated from, the external program memory space.  $\overline{\text{DM}}$ , an optional I/O function that can be

programmed to appear on pin P34, is used to distinguish between data and program memory space (Figure 23). The state of the  $\overline{DM}$  signal is controlled by the type of instruction being executed. An LDC opcode references PROGRAM ( $\overline{DM}$  inactive) memory, and an LDE instruction references data ( $\overline{DM}$  active Low) memory.

Figure 23. Data Memory Map

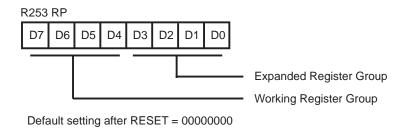

Register File. The register file consists of three I/O port registers, 236/125 general-purpose registers, 15 control and status registers, and three system configuration registers in the expanded register group. The instructions can access registers directly or indirectly through an 8-bit address field. This allows a short 4-bit register address using the Register Pointer (Figure 24). In the 4-bit mode, the register file is divided into 16 working register groups, each

occupying 16 continuous locations. The Register Pointer addresses the starting location of the active working-register group.

**Note:** Register Bank E0–EF can only be accessed through working register and indirect addressing modes. (This bank is available in Z86E30/E40 only.)

Figure 24. Register Pointer Register

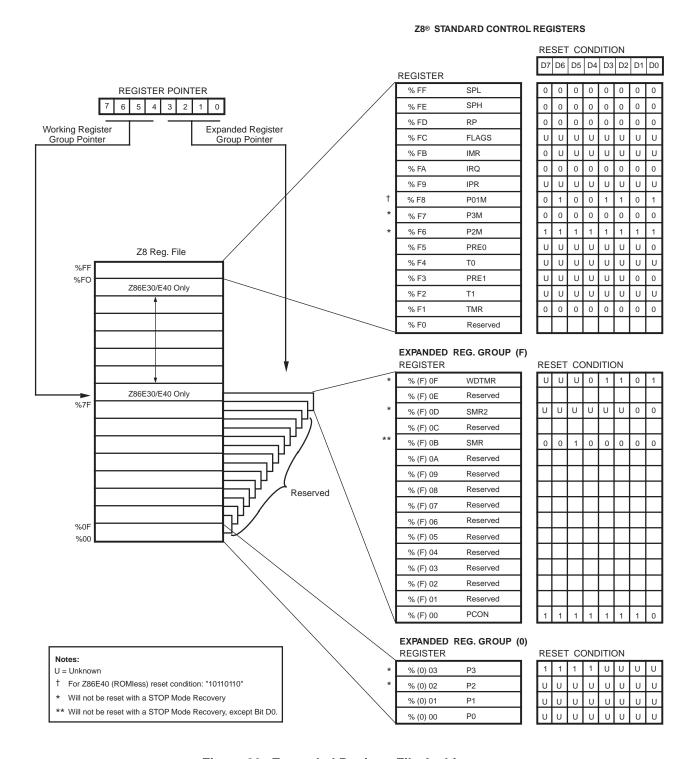

**Expanded Register File** (ERF). The register file has been expanded to allow for additional system control registers, mapping of additional peripheral devices and input/output ports into the register address area. The Z8 register address space R0 through R15 is implemented as 16 groups of 16 registers per group (Figure 26). These register groups are known as the Expanded Register File (ERF).

The low nibble (D3–D0) of the Register Pointer (RP) select the active ERF group, and the high nibble (D7–D4) of register RP select the working register group. Three system configuration registers reside in the Expanded Register File at bank FH: PCON, SMR, and WDTMR. The rest of the Expanded Register is not physically implemented and is reserved for future expansion.

Figure 26. Expanded Register File Architecture

## **FUNCTIONAL DESCRIPTION** (Continued)

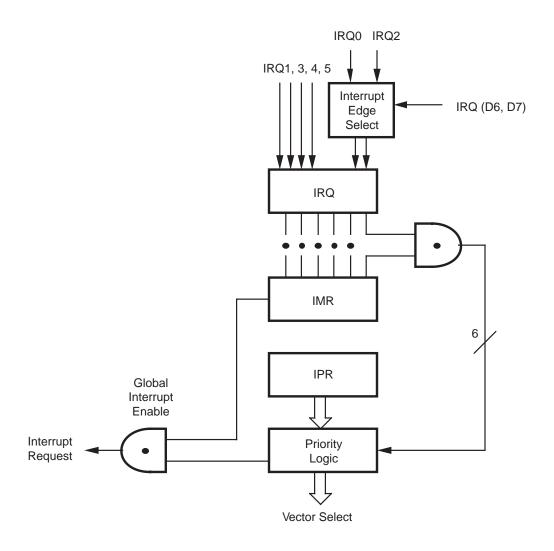

**Interrupts.** The MCU has six different interrupts from six different sources. The interrupts are maskable and prioritized (Figure 28). The six sources are divided as follows: four sources are claimed by Port 3 lines P33–P30) and two

in counter/timers. The Interrupt Mask Register globally or individually enables or disables the six interrupt requests (Table 10).

Figure 28. Interrupt Block Diagram

Table 10. Interrupt Types, Sources, and Vectors

| Name | Source                      | <b>Vector Location</b> | Comments                                      |

|------|-----------------------------|------------------------|-----------------------------------------------|

| IRQ0 | DAVO, IRQ0                  | 0, 1                   | External (P32), Rising/Falling Edge Triggered |

| IRQ1 | IRQ1                        | 2, 3                   | External (P33), Falling Edge Triggered        |

| IRQ2 | DAV2, IRQ2, T <sub>IN</sub> | 4, 5                   | External (P31), Rising/Falling Edge Triggered |

| IRQ3 | IRQ3                        | 6, 7                   | External (P30), Falling Edge Triggered        |

| IRQ4 | T0                          | 8, 9                   | Internal                                      |

| IRQ5 | TI                          | 10, 11                 | Internal                                      |

**Comparator Output Port 3** (D0). Bit 0 controls the comparator output in Port 3. A "1" in this location brings the comparator outputs to P34 and P37, and a "0" releases the Port to its standard I/O configuration. The default value is 0.

**Port 1 Open-Drain** (D1). Port 1 can be configured as an open-drain by resetting this bit (D1=0) or configured as push-pull active by setting this bit (D1=1). The default value is 1.

**Port 0 Open-Drain** (D2). Port 0 can be configured as an open-drain by resetting this bit (D2=0) or configured as push-pull active by setting this bit (D2=1). The default value is 1.

**Low EMI Port 0** (D3). Port 0 can be configured as a Low EMI Port by resetting this bit (D3=0) or configured as a Standard Port by setting this bit (D3=1). The default value is 1.

**Low EMI Port 1** (D4). Port 1 can be configured as a Low EMI Port by resetting this bit (D4=0) or configured as a Standard Port by setting this bit (D4=1). The default value is 1. **Note:** The emulator does not support Port 1 low EMI mode and must be set D4 = 1.

**Low EMI Port 2** (D5). Port 2 can be configured as a Low EMI Port by resetting this bit (D5=0) or configured as a Standard Port by setting this bit (D5=1). The default value is 1.

**Low EMI Port 3** (D6). Port 3 can be configured as a Low EMI Port by resetting this bit (D6=0) or configured as a Standard Port by setting this bit (D6=1). The default value is 1.

**Low EMI OSC** (D7). This bit of the PCON Register controls the low EMI noise oscillator. A "1" in this location configures the oscillator with standard drive. While a "0" configures the oscillator with low noise drive, however, it does not affect the relationship of SCLK and XTAL. The low EMI mode will reduce the drive of the oscillator (OSC). The default value is 1. **Note:** 4 MHz is the maximum external clock frequency when running in the low EMI oscillator mode.

**Stop-Mode Recovery Register** (SMR). This register selects the clock divide value and determines the mode of Stop-Mode Recovery (Figure 31). All bits are Write Only except bit 7 which is a Read Only. Bit 7 is a flag bit that is hardware set on the condition of STOP Recovery and reset by a power-on cycle. Bit 6 controls whether a low or high level is required from the recovery source. Bit 5 controls the reset delay after recovery. Bits 2, 3, and 4 of the SMR register specify the Stop-Mode Recovery Source. The SMR is located in Bank F of the Expanded Register Group at address 0BH.

# **FUNCTIONAL DESCRIPTION** (Continued)

Figure 31. STOP-Mode Recovery Register (Write-Only Except Bit D7, Which is Read-Only)

<sup>\*\*</sup> Default setting after RESET and STOP-Mode Recovery.

#### **FUNCTIONAL DESCRIPTION** (Continued)

Table 12. Stop-Mode Recovery Source

| D4 | D3 | D2 | SMR Source selection                |

|----|----|----|-------------------------------------|

| 0  | 0  | 0  | POR recovery only                   |

| 0  | 0  | 1  | P30 transition                      |

| 0  | 1  | 0  | P31 transition (Not in analog mode) |

| 0  | 1  | 1  | P32 transition (Not in analog mode) |

| 1  | 0  | 0  | P33 transition (Not in analog mode) |

| 1  | 0  | 1  | P27 transition                      |

| 1  | 1  | 0  | Logical NOR of Port 2 bits 0-3      |

| 1  | 1  | 1  | Logical NOR of Port 2 bits 0-7      |

|    |    |    |                                     |

**Stop-Mode Recovery Delay Select** (D5). The 5 ms RE-SET delay after Stop-Mode Recovery is disabled by programming this bit to a zero. A "1" in this bit will cause a 5 ms RESET delay after Stop-Mode Recovery. The default condition of this bit is 1. If the fast wake up mode is selected, the Stop-Mode Recovery source needs to be kept active for at least 5TpC.

**Stop-Mode Recovery Level Select** (D6). A "1" in this bit defines that a high level on any one of the recovery sources wakes the MCU from STOP Mode. A 0 defines low level recovery. The default value is 0.

**Cold or Warm Start** (D7). This bit is set by the device upon entering STOP Mode. A "0" in this bit indicates that the device has been reset by POR (cold). A "1" in this bit indicates the device was awakened by a SMR source (warm).

**Stop-Mode Recovery Register 2 (SMR2)**. This register contains additional Stop-Mode Recovery sources. When the Stop-Mode Recovery sources are selected in this register then SMR Register. Bits D2, D3, and D4 must be 0.

| SMR:10 |                       | Operation                          |  |  |

|--------|-----------------------|------------------------------------|--|--|

| D1     | Description of Action |                                    |  |  |

| 0      | 0                     | POR and/or external reset recovery |  |  |

| 0      | 1                     | Logical AND of P20 through P23     |  |  |

| 1      | 0                     | Logical AND of P20 through P27     |  |  |

Watch-Dog Timer Mode Register (WDTMR). The WDT is a retriggerable one-shot timer that resets the Z8 if it reaches its terminal count. The WDT is disabled after Power-On Reset and initially enabled by executing the WDT instruction and refreshed on subsequent executions of the WDT instruction. The WDT is driven either by an on-board RC oscillator or an external oscillator from XTAL1 pin. The

POR clock source is selected with bit 4 of the WDT register.

**Note:** Execution of the WDT instruction affects the Z (Zero), S (Sign), and V (Overflow) flags.

**WDT Time-Out Period** (D0 and D1). Bits 0 and 1 control a tap circuit that determines the time-out periods that can be obtained (Table 13). The default value of D0 and D1 are 1 and 0, respectively.

Table 13. Time-out Period of WDT

| D1 | D0 | Time-out of<br>the Internal<br>RC OSC | Time-out of<br>the System<br>Clock |

|----|----|---------------------------------------|------------------------------------|

| 0  | 0  | 5 ms                                  | 128 SCLK                           |

| 0  | 1  | 10 ms*                                | 256 SCLK*                          |

| 1  | 0  | 20 ms                                 | 512 SCLK                           |

| 1  | 1  | 80 ms                                 | 2048 SCLK                          |

#### Notes:

\*The default setting is 10 ms.

WDT During HALT Mode (D2). This bit determines whether or not the WDT is active during HALT Mode. A "1" indicates that the WDT is active during HALT. A "0" disables the WDT in HALT Mode. The default value is "1".

**WDT During STOP Mode** (D3). This bit determines whether or not the WDT is active during STOP mode. A "1" indicates active during STOP. A "0" disables the WDT during STOP Mode. This is applicable only when the WDT clock source is the internal RC oscillator.

Clock Source For WDT (D4). This bit determines which oscillator source is used to clock the internal POR and WDT counter chain. If the bit is a 1, the internal RC oscillator is bypassed and the POR and WDT clock source is driven from the external pin, XTAL1, and the WDT is stopped in STOP Mode. The default configuration of this bit is 0, which selects the RC oscillator.

**Permanent WDT.** When this feature is enabled, the WDT is enabled after reset and will operate in Run and Halt Mode. The control bits in the WDTMR do not affect the WDT operation. If the clock source of the WDT is the internal RC oscillator, then the WDT will run in STOP mode. If the clock source of the WDT is the XTAL1 pin, then the WDT will not run in STOP mode.

Note: WDT time-out in STOP Mode will not reset SMR,SMR2,PCON, WDTMR, P2M, P3M, Ports 2 & 3 Data Registers.

WDTMR Register Accessibility. The WDTMR register is accessible only during the first 60 internal system clock

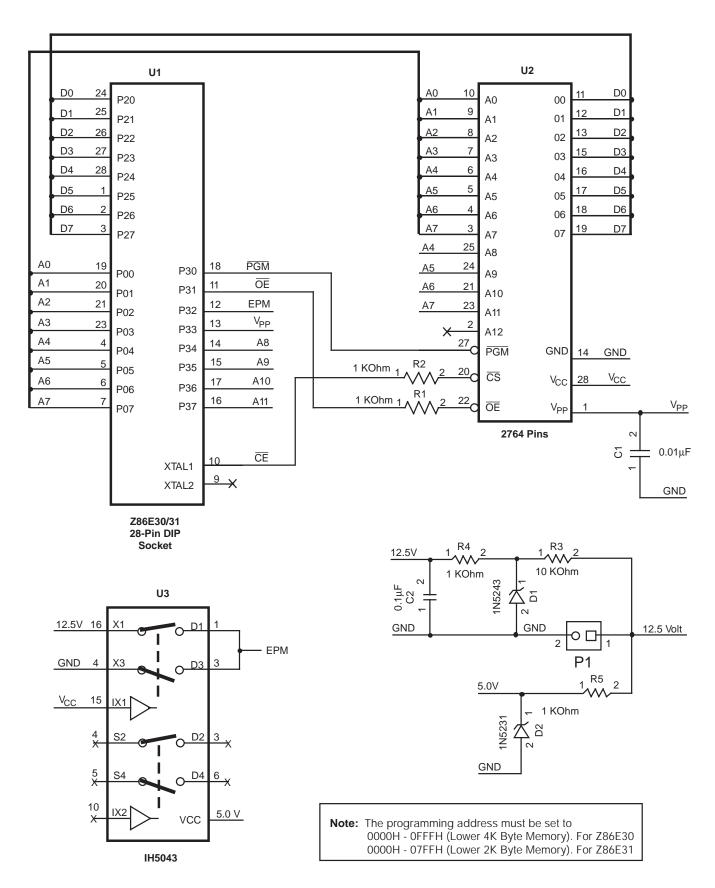

Figure 39. Z86E30/E31 Programming Adapter Circuitry

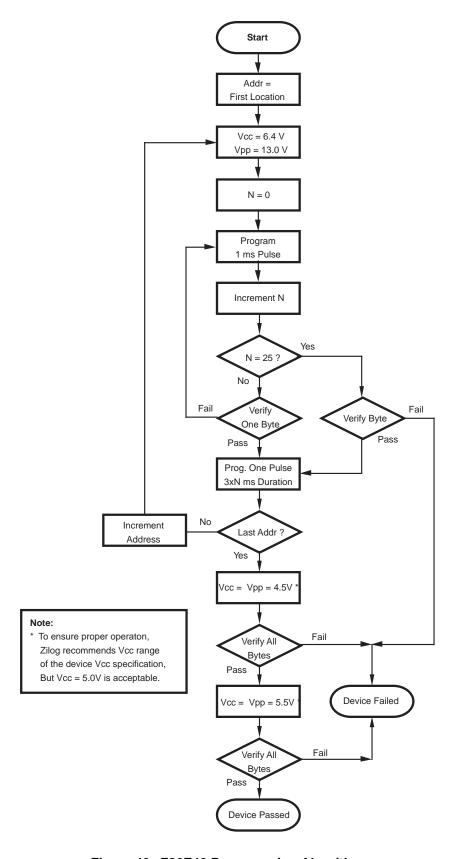

Figure 40. Z86E40 Programming Algorithm

# **PACKAGE INFORMATION (Continued)**

## **PACKAGE INFORMATION**

Figure 61. 40-Pin DIP Package Diagram

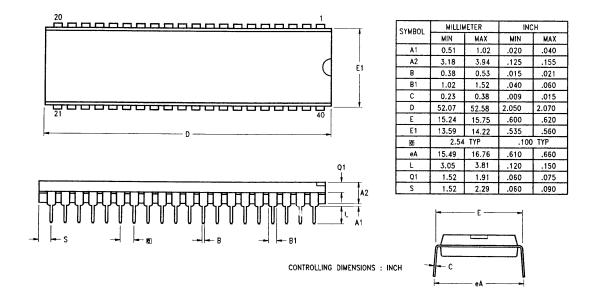

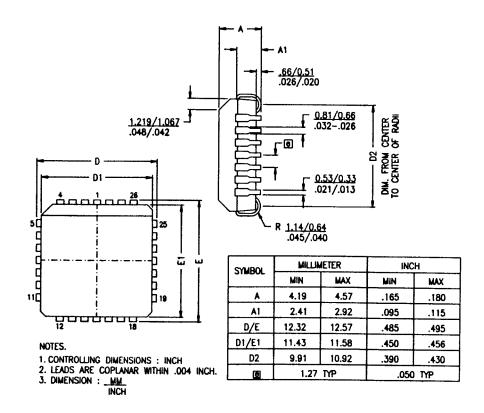

Figure 66. 28-Pin PLCC Package Diagram