Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                            |

|----------------------------|------------------------------------------------------------|

| Product Status             | Obsolete                                                   |

| Core Processor             | Z8                                                         |

| Core Size                  | 8-Bit                                                      |

| Speed                      | 16MHz                                                      |

| Connectivity               | -                                                          |

| Peripherals                | POR, WDT                                                   |

| Number of I/O              | 24                                                         |

| Program Memory Size        | 2KB (2K x 8)                                               |

| Program Memory Type        | ОТР                                                        |

| EEPROM Size                | -                                                          |

| RAM Size                   | 125 x 8                                                    |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 5.5V                                                |

| Data Converters            | -                                                          |

| Oscillator Type            | Internal                                                   |

| Operating Temperature      | -40°C ~ 105°C (TA)                                         |

| Mounting Type              | Surface Mount                                              |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                             |

| Supplier Device Package    | -                                                          |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z86e3116sec00tr |

Power connections follow conventional descriptions below:

| Connection | Circuit         | Device          |

|------------|-----------------|-----------------|

| Power      | V <sub>CC</sub> | $V_{DD}$        |

| Ground     | GND             | V <sub>SS</sub> |

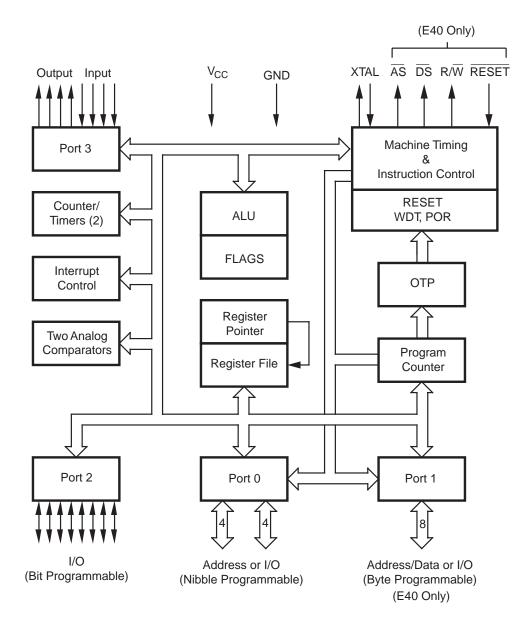

Figure 1. Z86E30/E31/E40 Functional Block Diagram

### **PIN IDENTIFICATION** (Continued)

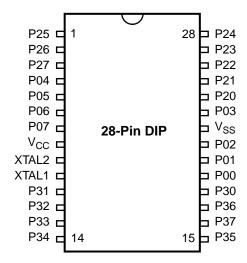

Figure 9. Standard Mode 28-Pin DIP/SOIC Pin Configuration

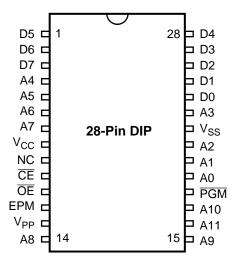

Figure 10. EPROM Programming Mode 28-Pin DIP/SOIC Pin Configuration

| Pin#  | Symbol          | Function                  | Direction |

|-------|-----------------|---------------------------|-----------|

| 1–3   | P25-P27         | Port 2, Pins 5,6,         | In/Output |

| 4–7   | P04-P07         | Port 0, Pins 4,5,6,7      | In/Output |

| 8     | V <sub>CC</sub> | Power Supply              |           |

| 9     | XTAL2           | Crystal Oscillator        | Output    |

| 10    | XTAL1           | Crystal Oscillator        | Input     |

| 11–13 | P31-P33         | Port 3, Pins 1,2,3        | Input     |

| 14–15 | P34-P35         | Port 3, Pins 4,5          | Output    |

| 16    | P37             | Port 3, Pin 7             | Output    |

| 17    | P36             | Port 3, Pin 6             | Output    |

| 18    | P30             | Port 3, Pin 0             | Input     |

| 19–21 | P00-P02         | Port 0, Pins 0,1,2        | In/Output |

| 22    | V <sub>SS</sub> | Ground                    |           |

| 23    | P03             | Port 0, Pin 3             | In/Output |

| 24–28 | P20-P24         | Port 2, Pins<br>0,1,2,3,4 | In/Output |

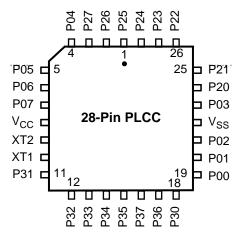

Figure 11. Standard Mode 28-Pin PLCC Pin Configuration

## **CAPACITANCE**

$T_A$  = 25°C,  $V_{CC}$  = GND = 0V, f = 1.0 MHz; unmeasured pins returned to GND.

| Parameter          | Min | Max   |

|--------------------|-----|-------|

| Input capacitance  | 0   | 12 pF |

| Output capacitance | 0   | 12 pF |

| I/O capacitance    | 0   | 12 pF |

### DC ELECTRICAL CHARACTERISTICS

| $T_A = 0  ^{\circ}C$ to +70 $^{\circ}C$ |                          |          |                               |                       |         |       |                             |       |

|-----------------------------------------|--------------------------|----------|-------------------------------|-----------------------|---------|-------|-----------------------------|-------|

|                                         |                          | $v_{cc}$ |                               |                       | Typical |       |                             |       |

| Sym                                     | Parameter                | Note [3] | Min                           | Max                   | @ 25°C  | Units | Conditions                  | Notes |

| $\overline{V_{CH}}$                     | Clock Input High Voltage | 3.5V     | 0.7 V <sub>CC</sub>           | V <sub>CC</sub> +0.3  | 1.8     | V     | Driven by External          |       |

|                                         |                          | 5.5V     | $0.7\mathrm{V}_{\mathrm{CC}}$ | V <sub>CC</sub> +0.3  | 2.5     | V     | Clock Generator             |       |

| $\overline{V_{CL}}$                     | Clock Input Low Voltage  | 3.5V     | GND -0.3                      | 0.2 V <sub>CC</sub>   | 0.9     | V     | Driven by External          |       |

| 0-                                      |                          | 4.5V     | GND -0.3                      | 0.2 V <sub>CC</sub>   | 1.5     | V     | Clock Generator             |       |

| $\overline{V_IH}$                       | Input High Voltage       | 3.5V     | 0.7 V <sub>CC</sub>           | V <sub>CC</sub> +0.3  | 2.5     | V     |                             |       |

|                                         |                          | 5.5V     | 0.7 V <sub>CC</sub>           | V <sub>CC</sub> +0.3  | 2.5     | V     |                             |       |

| $\overline{V_{IL}}$                     | Input Low Voltage        | 3.5V     | GND -0.3                      | 0.2 V <sub>CC</sub>   | 1.5     | V     |                             |       |

|                                         |                          | 5.5V     | GND -0.3                      | 0.2 V <sub>CC</sub>   | 1.5     | V     |                             |       |

| $\overline{V_{OH}}$                     | Output High Voltage      | 3.5V     | V <sub>CC</sub> -0.4          |                       | 3.3     | V     | $I_{OH} = -0.5 \text{ mA}$  |       |

| <b>.</b>                                | Low EMI Mode             | 5.5V     | V <sub>CC</sub> -0.4          |                       | 4.8     | V     |                             |       |

| $V_{OH1}$                               | Output High Voltage      | 3.5V     | V <sub>CC</sub> -0.4          |                       | 3.3     | V     | I <sub>OH</sub> = -2.0 mA   |       |

| 0111                                    |                          | 5.5V     | V <sub>CC</sub> -0.4          |                       | 4.8     | V     | $I_{OH} = -2.0 \text{ mA}$  |       |

| $\overline{V_{OL}}$                     | Output Low Voltage       | 3.5V     |                               | 0.4                   | 0.2     | V     | I <sub>OL</sub> = 1.0 mA    |       |

| 0-                                      | Low EMI Mode             | 4.5V     |                               | 0.4                   | 0.2     | V     | $I_{OL} = 1.0 \text{ mA}$   |       |

| $\overline{V_{OL1}}$                    | Output Low Voltage       | 3.5V     |                               | 0.4                   | 0.1     | V     | $I_{OL} = + 4.0 \text{ mA}$ | 8     |

|                                         |                          | 4.5V     |                               | 0.4                   | 0.1     | V     | $I_{OL} = + 4.0 \text{ mA}$ | 8     |

| $\overline{V_{OL2}}$                    | Output Low Voltage       | 3.5V     |                               | 1.2                   | 0.5     | V     | I <sub>OL</sub> = + 12 mA   | 8     |

|                                         |                          | 4.5V     |                               | 1.2                   | 0.5     | V     | $I_{OL} = + 12 \text{ mA}$  | 8     |

| $\overline{V_{RH}}$                     | Reset Input High         | 3.5V     | .8 V <sub>CC</sub>            | V <sub>CC</sub>       | 1.7     | V     |                             |       |

|                                         | Voltage                  | 5.5V     | .8 V <sub>CC</sub>            | $V_{CC}$              | 2.1     | V     |                             |       |

| $\overline{V_{RL}}$                     | Reset Input Low Voltage  | 3.5V     | GND -0.3                      | 0.2 V <sub>CC</sub>   | 1.3     | V     |                             | 13    |

|                                         |                          | 5.5V     | GND -0.3                      | 0.2 V <sub>CC</sub>   | 1.7     | V     |                             |       |

| $\overline{V_{OLR}}$                    | Reset Output Low         | 3.5V     |                               | 0.6                   | 0.3     | V     | I <sub>OL</sub> = 1.0 mA    |       |

|                                         | Voltage                  | 5.5V     |                               | 0.6                   | 0.2     | V     | $I_{OL} = 1.0 \text{ mA}$   |       |

| $\overline{V_{OFFSET}}$                 | Comparator Input         | 3.5V     |                               | 25                    | 10      | mV    |                             |       |

|                                         | Offset Voltage           | 4.5V     |                               | 25                    | 10      | mV    |                             |       |

| $V_{ICR}$                               | Input Common Mode        | 3.5V     | 0                             | V <sub>CC</sub> -1.0V |         | V     |                             | 10    |

|                                         | Voltage Range            | 5.5V     | 0                             | V <sub>CC</sub> -1.0V |         | V     |                             | 10    |

| I <sub>IL</sub>                         | Input Leakage            | 3.5V     | -1                            | 2                     | 0.032   | μΑ    | $V_{IN} = 0V, V_{CC}$       |       |

|                                         |                          | 4.5V     | -1                            | 2                     | 0.032   | μΑ    | $V_{IN} = 0V, V_{CC}$       |       |

| I <sub>OL</sub>                         | Output Leakage           | 3.5V     | -1                            | 2                     | 0.032   | μΑ    | $V_{IN} = 0V, V_{CC}$       |       |

|                                         |                          | 4.5V     | -1                            | 2                     | 0.032   | μΑ    | $V_{IN} = 0V, V_{CC}$       |       |

| $\overline{I_{IR}}$                     | Reset Input Current      | 3.5V     | -20                           | -130                  | -65     | μΑ    |                             |       |

|                                         |                          | 4.5V     | -20                           | -180                  | -112    | μΑ    |                             |       |

| T <sub>A</sub> =-40 °C to +105 °C |                              |                             |                               |                             |                   |                |                                                   |         |

|-----------------------------------|------------------------------|-----------------------------|-------------------------------|-----------------------------|-------------------|----------------|---------------------------------------------------|---------|

| Sym                               | Parameter                    | V <sub>CC</sub><br>Note [3] | Min                           | Max                         | Typical<br>@ 25°C | Units          | Conditions                                        | Notes   |

| V <sub>CH</sub>                   | Clock Input High             | 4.5V                        | 0.7 V <sub>CC</sub>           | V <sub>CC</sub> +0.3        | 2.5               | V              | Driven by External                                |         |

|                                   | Voltage                      | 5.5V                        | 0.7 V <sub>CC</sub>           | V <sub>CC</sub> +0.3        | 2.5               | V              | Clock Generator                                   |         |

| V <sub>CL</sub>                   | Clock Input Low              | 4.5V                        | GND-0.3                       | 0.2 V <sub>CC</sub>         | 1.5               | V              | Driven by External                                |         |

|                                   | Voltage                      | 5.5V                        | GND-0.3                       | $0.2\mathrm{V}_\mathrm{CC}$ | 1.5               | V              | Clock Generator                                   |         |

| V <sub>IH</sub>                   | Input High Voltage           | 4.5V                        | 0.7 V <sub>CC</sub>           | V <sub>CC</sub> +0.3        | 2.5               | V              |                                                   |         |

|                                   |                              | 5.5V                        | $0.7\mathrm{V}_{\mathrm{CC}}$ | V <sub>CC</sub> +0.3        | 2.5               | V              |                                                   |         |

| V <sub>IL</sub>                   | Input Low Voltage            | 4.5V                        | GND-0.3                       | 0.2 V <sub>CC</sub>         | 1.5               | V              |                                                   |         |

|                                   |                              | 5.5V                        | GND-0.3                       | $0.2\mathrm{V}_\mathrm{CC}$ | 1.5               | V              |                                                   |         |

| V <sub>OH</sub>                   | Output High                  | 4.5V                        | V <sub>CC</sub> -0.4          |                             | 4.8               | V              | $I_{OH} = -0.5 \text{ mA}$                        | 8       |

|                                   | Voltage Low EMI<br>Mode      | 5.5V                        | V <sub>CC</sub> -0.4          |                             | 4.8               | V              | $I_{OH} = -0.5 \text{ mA}$                        | 8       |

| V <sub>OH1</sub>                  | Output High Voltage          | 4.5V                        | V <sub>CC</sub> -0.4          |                             | 4.8               | V              | I <sub>OH</sub> = -2.0 mA                         | 8       |

|                                   |                              | 4.5V                        | V <sub>CC</sub> -0.4          |                             | 4.8               | V              | $I_{OH} = -2.0 \text{ mA}$                        | 8       |

| V <sub>OL</sub>                   | Output Low Voltage           | 4.5V                        |                               | 0.4                         | 0.2               | V              | I <sub>OL</sub> = 1.0 mA                          |         |

|                                   | Low EMI Mode                 | 5.5V                        |                               | 0.4                         | 0.2               | V              | $I_{OL} = 1.0 \text{ mA}$                         |         |

| V <sub>OL1</sub>                  | Output Low Voltage           | 4.5V                        |                               | 0.4                         | 0.1               | V              | $I_{OL} = + 4.0 \text{ mA}$                       | 8       |

|                                   |                              | 5.5V                        |                               | 0.4                         | 0.1               | V              | $I_{OL}$ = +4.0 mA                                | 8       |

| $V_{OL2}$                         | Output Low Voltage           | 4.5V                        |                               | 1.2                         | 0.5               | V              | I <sub>OL</sub> = + 12 mA                         | 8       |

|                                   |                              | 5.5V                        |                               | 1.2                         | 0.5               | V              | $I_{OL}$ = + 12 mA                                | 8       |

| $V_{RH}$                          | Reset Input High             | 3.5V                        | .8 V <sub>CC</sub>            | V <sub>CC</sub>             | 1.7               | V              |                                                   | 13      |

|                                   | Voltage                      | 5.5V                        | .8 V <sub>CC</sub>            | $V_{CC}$                    | 2.1               | V              |                                                   | 13      |

| V <sub>OLR</sub>                  | Reset Output Low             | 3.5V                        |                               | 0.6                         | 0.3               | V              | I <sub>OL</sub> = 1.0 mA                          | 13      |

|                                   | Voltage                      | 5.5V                        |                               | 0.6                         | 0.2               | V              | $I_{OL} = 1.0 \text{ mA}$                         | 13      |

| V <sub>OFFSET</sub>               | - Comparator Input           | 4.5V                        |                               | 25                          | 10                | mV             |                                                   |         |

|                                   | Offset Voltage               | 5.5V                        |                               | 25                          | 10                | mV             |                                                   |         |

| $V_{ICR}$                         | Input Common                 | 4.5V                        | 0                             | V <sub>CC</sub> -1.5V       |                   | V              |                                                   | 10      |

|                                   | Mode Voltage<br>Range        | 5.5V                        | 0                             | V <sub>CC</sub> -1.5V       |                   | V              |                                                   | 10      |

| I <sub>IL</sub>                   | Input Leakage                | 4.5V                        | -1<br>1                       | 2                           | <1<br>-1          | μA<br>^        | $V_{IN} = 0V, V_{CC}$                             |         |

| <u> </u>                          | Output Leakage               | 5.5V<br>4.5V                | -1<br>-1                      | 2                           | <1<br><1          | μA<br>         | $V_{IN} = 0V, V_{CC}$                             |         |

| l <sub>OL</sub>                   | Output Leakage               | 4.5 V<br>5.5 V              | - 1<br>-1                     | 2                           | <1<br><1          | μΑ<br>μΑ       | $V_{IN} = 0V, V_{CC}$<br>$V_{IN} = 0V, V_{CC}$    |         |

| <u> </u>                          | Reset Input Current          | 4.5V                        | -18                           | -180                        | -112              |                | vIN = ov, vCC                                     |         |

| I <sub>IR</sub>                   | Reset input Current          | 4.5 V<br>5.5 V              | -10<br>-18                    | -180                        | -112<br>-112      | μΑ<br>μΑ       |                                                   |         |

| I <sub>CC</sub>                   | Supply Current               | 4.5V                        |                               | 25                          | 20                | mA             | @ 16 MHz                                          | 4,5     |

| CC                                |                              | 5.5V                        |                               | 25                          | 20                | mA             | @ 16 MHz                                          | 4,5     |

| I <sub>CC1</sub>                  | Standby Current<br>Halt Mode | 4.5V                        |                               | 8                           | 3.7               | mA             | V <sub>IN</sub> = 0V, V <sub>CC</sub><br>@ 16 MHz | 4,5     |

|                                   |                              | 5.5V                        |                               | 8                           | 3.7               | mA             | V <sub>IN</sub> = 0V, V <sub>CC</sub><br>@ 16 MHz | 4,5     |

| I <sub>CC2</sub>                  | Standby Current              | 4.5V                        |                               | 10                          | 2                 | μΑ             | $V_{IN} = 0V, V_{CC}$                             | 6,11,14 |

| 002                               | (Stop Mode)                  | 5.5V                        |                               | 10                          | 3                 | μΑ             | $V_{IN} = 0V, V_{CC}$                             | 6,11,14 |

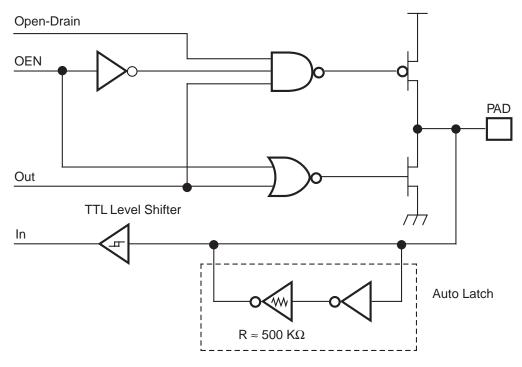

| I <sub>ALL</sub>                  | Auto Latch Low               | 4.5V                        | 1.4                           | 20                          | 4.7               | <u>.</u><br>μΑ | 0V < V <sub>IN</sub> < V <sub>CC</sub>            | 9       |

| ALL                               | Current                      | 5.5V                        | 1.4                           | 20                          | 4.7               | μΑ             | $0V < V_{IN} < V_{CC}$                            | 9       |

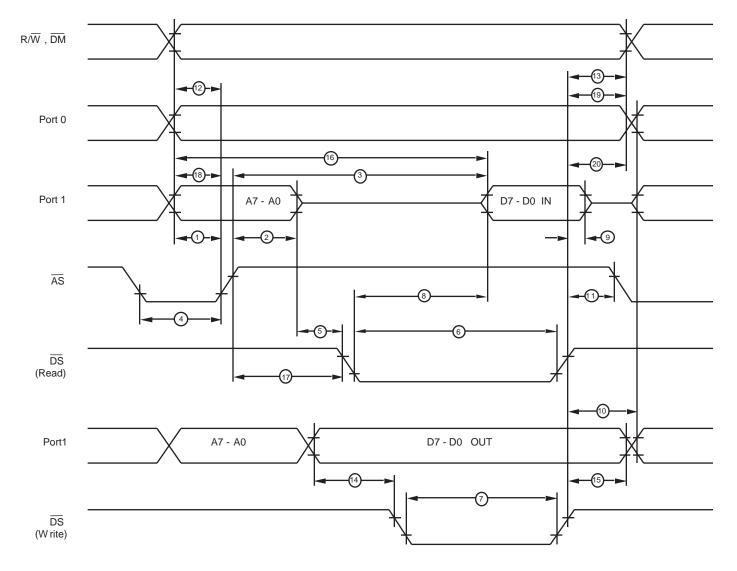

Figure 14. External I/O or Memory Read/Write Timing Z86E40 Only

# DC ELECTRICAL CHARACTERISTICS (Continued)

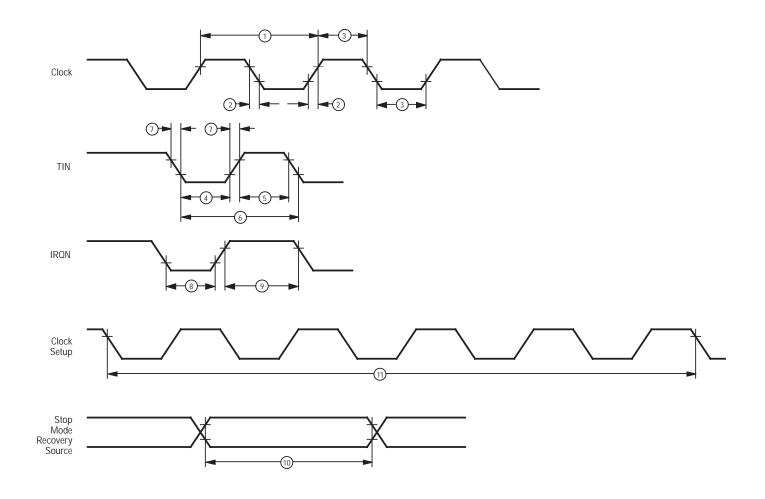

Figure 15. Additional Timing Diagram

## DC ELECTRICAL CHARACTERISTICS (Continued)

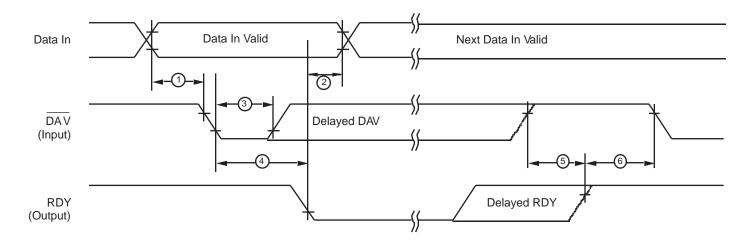

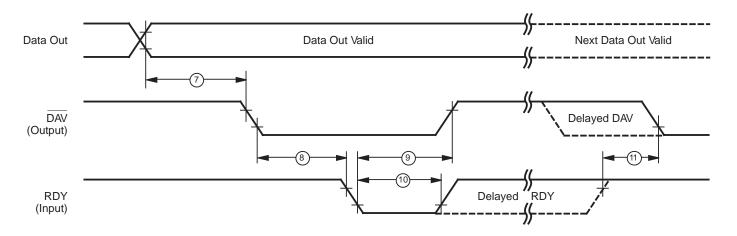

# **Handshake Timing Diagrams**

Figure 16. Input Handshake Timing

Figure 17. Output Handshake Timing

### **PIN FUNCTIONS**

### **EPROM Programming Mode**

**D7–D0** Data Bus. The data can be read from or written to external memory through the data bus.

**A11–A0** Address Bus. During programming, the EPROM address is written to the address bus.

**V<sub>CC</sub>** Power Supply. This pin must supply 5V during the EPROM read mode and 6V during other modes.

**CE** Chip Enable (active Low). This pin is active during EPROM Read Mode, Program Mode, and Program Verify Mode.

**OE** Output Enable (active Low). This pin drives the direction of the Data Bus. When this pin is Low, the Data Bus is output, when High, the Data Bus is input.

**EPM** EPROM Program Mode. This pin controls the different EPROM Program Mode by applying different voltages.

$\mathbf{V_{PP}}$  Program Voltage. This pin supplies the program voltage.

**PGM** Program Mode (active Low). When this pin is Low, the data is programmed to the EPROM through the Data Bus.

## **Application Precaution**

The production test-mode environment may be enabled accidentally during normal operation if excessive noise surges above V<sub>CC</sub> occur on pins XTAL1 and RESET.

In addition, processor operation of Z8 OTP devices may be affected by excessive noise surges on the  $V_{PP}$ ,  $\overline{CE}$ ,  $\overline{EPM}$ ,  $\overline{OE}$  pins while the microcontroller is in Standard Mode.

Recommendations for dampening voltage surges in both test and OTP mode include the following:

- Using a clamping diode to V<sub>CC</sub>

- Adding a capacitor to the affected pin

#### Standard Mode

**XTAL** Crystal 1 (time-based input). This pin connects a parallel-resonant crystal, ceramic resonator, LC, RC network, or external single-phase clock to the on-chip oscillator input.

**XTAL2** Crystal 2 (time-based output). This pin connects a parallel-resonant crystal, ceramic resonator, LC, or RC network to the on-chip oscillator output.

$R/\overline{W}$  Read/Write (output, write Low). The  $R/\overline{W}$  signal is Low when the CCP is writing to the external program or data memory (Z86E40 only).

**RESET** Reset (input, active Low). Reset will initialize the MCU. Reset is accomplished either through Power-On, Watch-Dog Timer reset, STOP-Mode Recovery, or external reset. During Power-On Reset and Watch-Dog Timer Reset, the internally generated reset drives the reset pin low for the POR time. Any devices driving the reset line must be open-drain in order to avoid damage from a possible conflict during reset conditions. Pull-up is provided internally. After the POR time, RESET is a Schmitt-triggered input.

To avoid asynchronous and noisy reset problems, the Z86E40 is equipped with a reset filter of four external clocks (4TpC). If the external reset signal is less than 4TpC in duration, no reset occurs. On the fifth clock after the reset is detected, an internal RST signal is latched and held for an internal register count of 18 external clocks, or for the duration of the external reset, whichever is longer. During the reset cycle,  $\overline{DS}$  is held active Low while  $\overline{AS}$  cycles at a rate of TpC/2. Program execution begins at location 000CH, 5–10 TpC cycles after  $\overline{RESET}$  is released. For Power-On Reset, the reset output time is 5 ms. The Z86E40 does not reset WDTMR, SMR, P2M, and P3M registers on a STOP-Mode Recovery operation.

**ROMIess** (input, active Low). This pin, when connected to GND, disables the internal ROM and forces the device to function as a Z86C90/C89 ROMIess Z8. (Note that, when left unconnected or pulled High to  $V_{CC}$ , the device functions normally as a Z8 ROM version).

**Note:** When using in ROM Mode in High EMI (noisy) environment, the ROMless pins should be connected directly to  $V_{CC}$ .

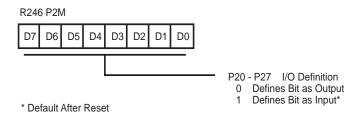

**Port 2** (P27–P20). Port 2 is an 8-bit, bidirectional, CMOS-compatible I/O port. These eight I/O lines can be configured under software control as an input or output, independently. All input buffers are Schmitt-triggered. Bits programmed as outputs can be globally programmed as either push-pull or open-drain. Low EMI output buffers can

be globally programmed by the software. When used as an I/O port, Port 2 can be placed under handshake control.

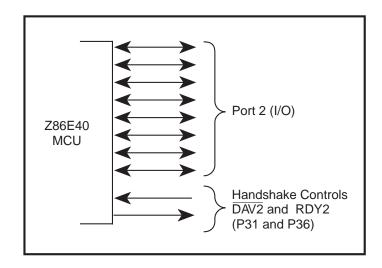

In Handshake Mode, Port 3 lines P31 and P36 are used as handshake control lines. The handshake direction is determined by the configuration (input or output) assigned to bit 7 of Port 2 (Figure 20).

Figure 20. Port 2 Configuration

### **PIN FUNCTIONS** (Continued)

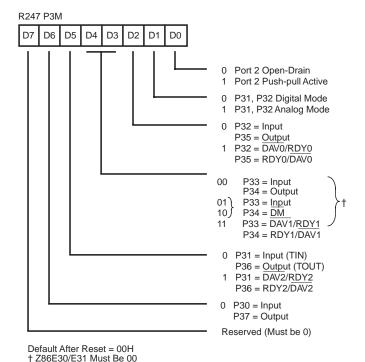

Port 3 (P37-P30). Port 3 is an 8-bit, CMOS-compatible port with four fixed inputs (P33-P30) and four fixed outputs (P37-P34). These eight lines can be configured by software for interrupt and handshake control functions. Port 3, Pin 0 is Schmitt- triggered. P31, P32, and P33 are standard CMOS inputs with single trip point (no Auto Latches) and P34, P35, P36, and P37 are push-pull output lines. Low EMI output buffers can be globally programmed by the software. Two on-board comparators can process analog signals on P31 and P32 with reference to the voltage on P33. The analog function is enabled by setting the D1 of Port 3 Mode Register (P3M). The comparator output can be outputted from P34 and P37, respectively, by setting PCON register Bit D0 to 1 state. For the interrupt function, P30 and P33 are falling edge triggered interrupt inputs. P31 and P32 can be programmed as falling, rising or both edges triggered interrupt inputs (Figure 21). Access to Counter/Timer 1 is made through P31 (T<sub>IN</sub>) and P36 (TOUT). Handshake lines for Port 0, Port 1, and Port 2 are also available on Port 3 (Table 9).

**Note**: When enabling/ or disabling analog mode, the following is recommended:

- Allow two NOP delays before reading this comparator output.

- 2. Disable global interrupts, switch to analog mode, clear interrupts, and then re-enable interrupts.

- 3. IRQ register bits 3 to 0 must be cleared after enabling analog mode.

**Note:** P33–P30 differs from the Z86C30/C31/C40 in that there is no clamping diode to  $V_{CC}$  due to the EPROM high-voltage circuits. Exceeding the  $V_{IH}$  maximum specification during standard operating mode may cause the device to enter EPROM mode.

### **FUNCTIONAL DESCRIPTION** (Continued)

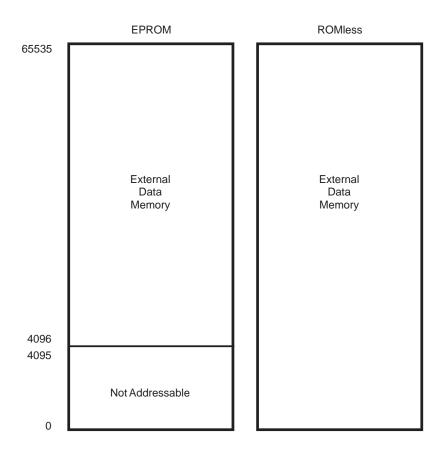

**Data Memory** ( $\overline{\text{DM}}$ ). In EPROM Mode, the Z86E40 can address up to 60 KB of external data memory beginning at location 4096. In ROMless mode, the Z86E40 can address up to 64 KB of data memory. External data memory may be included with, or separated from, the external program memory space.  $\overline{\text{DM}}$ , an optional I/O function that can be

programmed to appear on pin P34, is used to distinguish between data and program memory space (Figure 23). The state of the  $\overline{DM}$  signal is controlled by the type of instruction being executed. An LDC opcode references PROGRAM ( $\overline{DM}$  inactive) memory, and an LDE instruction references data ( $\overline{DM}$  active Low) memory.

Figure 23. Data Memory Map

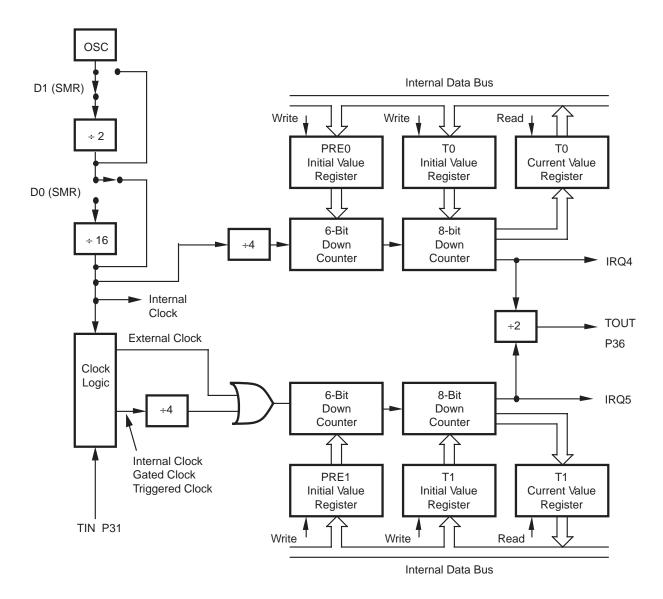

Figure 27. Counter/Timer Block Diagram

## **FUNCTIONAL DESCRIPTION** (Continued)

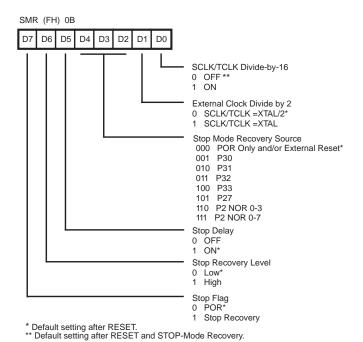

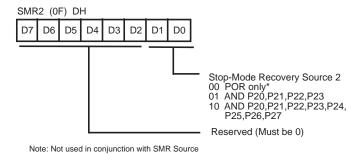

Figure 31. STOP-Mode Recovery Register (Write-Only Except Bit D7, Which is Read-Only)

<sup>\*\*</sup> Default setting after RESET and STOP-Mode Recovery.

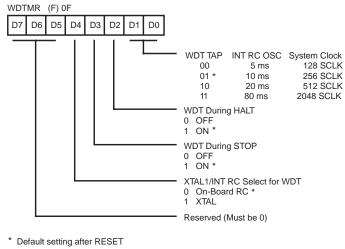

cycles from the execution of the first instruction after Power-On Reset, Watch-Dog reset or a STOP-Mode Recovery (Figures 33 and 34). After this point, the register cannot be modified by any means, intentional or otherwise. The WDTMR cannot be read and is located in Bank F of the Expanded Register Group at address location 0FH.

<sup>\*</sup> Default setting after RESET

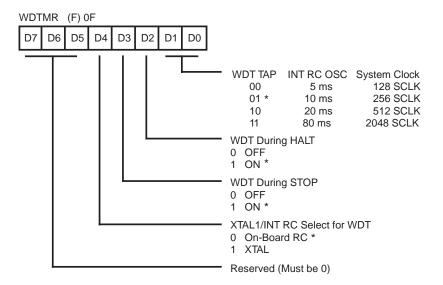

Figure 33. Watch-Dog Timer Mode Register Write Only

### **FUNCTIONAL DESCRIPTION** (Continued)

### **EPROM MODE**

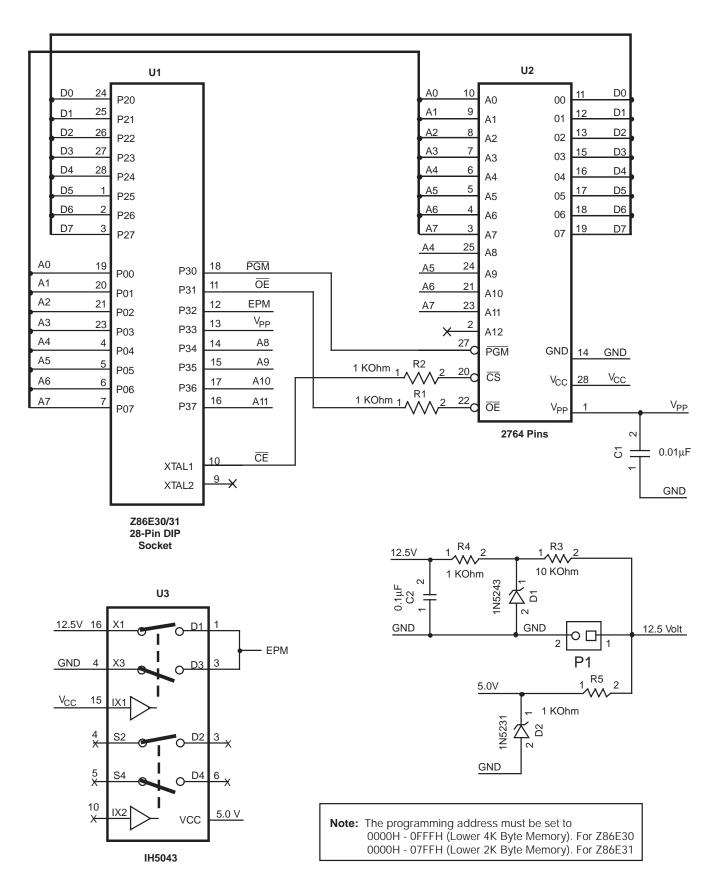

Table 14 shows the programming voltages of each programming mode. Table 15, and figures that follow show the programming timing of each programming mode. Figure 38 shows the circuit diagram of a Z86E40 programming adapter, which adapts from 2764A to Z86E40 and Figure 39 shows the Z86E30/E31 Programming Adapter Circuitry. Figure 40 shows the flowchart of an Intelligent Programming Algorithm, which is compatible with 2764A EPROM (Z86E40 is 4K EPROM, 2764A is 8K EPROM). Since the EPROM size of Z86E30/E31/E40 differs from 2764A, the programming address range has to be set from 0000H to 0FFFH for the Z86E30/E40 and 0000H to 07FFH for Z86E31. Otherwise, the upper portion of EPROM data will overwrite the lower portion of EPROM data. Figure 39 shows the adaptation from the 2764A to Z86E30/E31.

**Note:** EPROM Protect feature allows the LDC, LDCI, LDE, and LDEI instructions from internal program memory. A ROM lookup table can be used with this feature.

During programming, the  $V_{PP}$  input pin supplies the programming voltage and current to the EPROM. This pin is also used to latch which EPROM mode is to be used (R/W EPROM or R/W Option bits). The mode is set by placing the correct mode number on the least significant bits of the address and raising the EPM pin above V. After a setup time, the  $V_{PP}$  pin can then be raised or lowered. The latched EPROM mode will remain until the EPM pin is reduced below  $V_{H}$ .

| Mode Name      | Mode # | LSB Addr |

|----------------|--------|----------|

| EPROM R/W      | 0      | 0000     |

| Option Bit R/W | 3      | 0011     |

EPROM R/W mode allows the programming of the user mode program ROM.

Option Bit R/W allows the programming of the Z8 option bits. When the device is latched into Option Bit R/W mode, the address must then be changed to 63 decimals (000000111111 Binary). The Options are mapped into this address as follows:

| Bit | Option               |  |

|-----|----------------------|--|

| 7   | Unused               |  |

| 6   | Unused               |  |

| 5   | 32 KHz XTAL Option   |  |

| 4   | Permanent WDT        |  |

| 3   | Auto Latch Disable   |  |

| 2   | RC Oscillator Option |  |

| 1   | RAM Protect          |  |

| 0   | ROM Protect          |  |

Table 14 gives the proper conditions for EPROM R/W operations, once the mode is latched.

Figure 39. Z86E30/E31 Programming Adapter Circuitry

## **EXPANDED REGISTER FILE CONTROL REGISTERS**

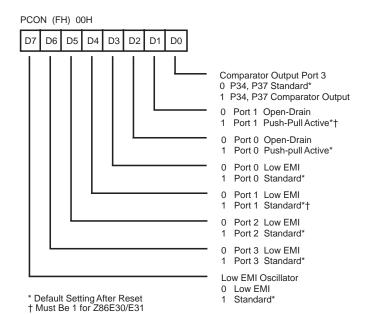

Figure 41. Port Configuration Register Write Only

Figure 42. STOP-Mode Recovery Register Write Only Except Bit D7, Which is Read Only

Figure 43. Watch-Dog Timer Mode Register Write Only

Figure 44. STOP-Mode Recovery Register 2

Write Only

### **Z8 CONTROL REGISTER DIAGRAMS** (Continued)

Figure 51. Port 2 Mode Register F6H: Write Only

Figure 52. Port 3 Mode Register F7H: Write Only

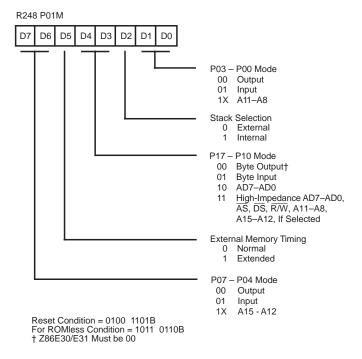

Figure 53. Port 0 and 1 Mode Register F8H: Write Only Z86E30/E31 Only

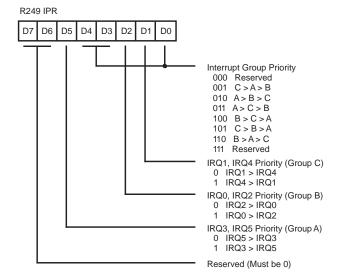

Figure 54. Interrupt Priority Register F9H: Write Only

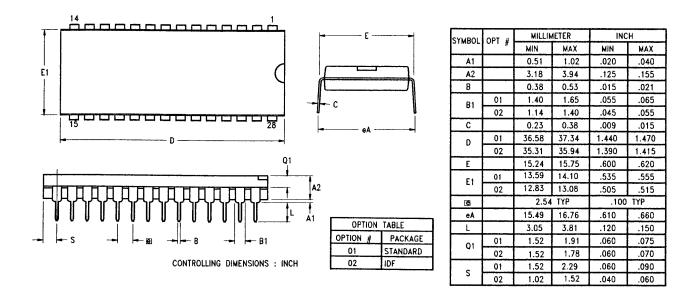

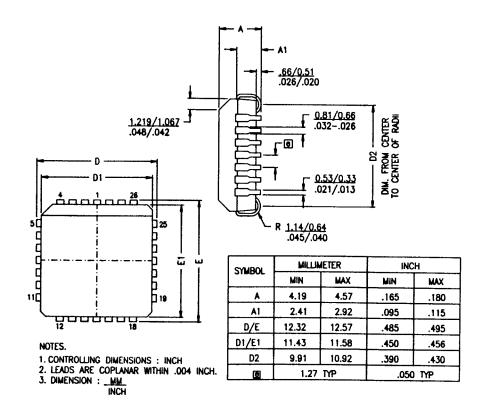

Figure 64. 28-Pin DIP Package Diagram

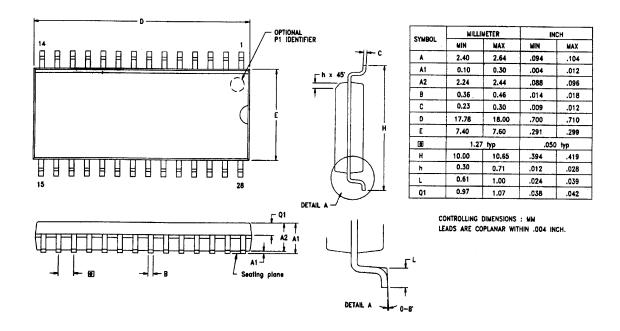

Figure 65. 28-Pin SOIC Package Diagram

Figure 66. 28-Pin PLCC Package Diagram