### Zilog - Z86E4016ASG Datasheet

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                 |

|----------------------------|--------------------------------------------------------|

| Core Processor             | Z8                                                     |

| Core Size                  | 8-Bit                                                  |

| Speed                      | 16MHz                                                  |

| Connectivity               | -                                                      |

| Peripherals                | POR, WDT                                               |

| Number of I/O              | 32                                                     |

| Program Memory Size        | 4KB (4K x 8)                                           |

| Program Memory Type        | OTP                                                    |

| EEPROM Size                | -                                                      |

| RAM Size                   | 236 x 8                                                |

| Voltage - Supply (Vcc/Vdd) | 3.5V ~ 5.5V                                            |

| Data Converters            | -                                                      |

| Oscillator Type            | Internal                                               |

| Operating Temperature      | 0°C ~ 70°C (TA)                                        |

| Mounting Type              | Surface Mount                                          |

| Package / Case             | 44-LQFP                                                |

| Supplier Device Package    | 44-LQFP (10x10)                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z86e4016asg |

|                            |                                                        |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

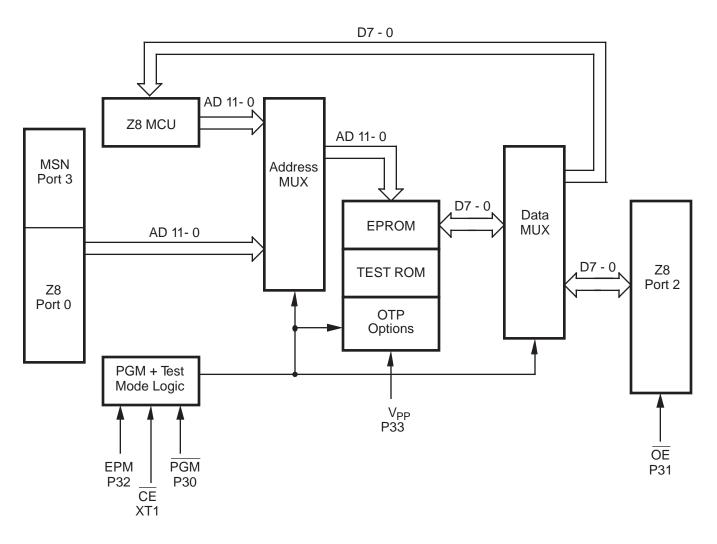

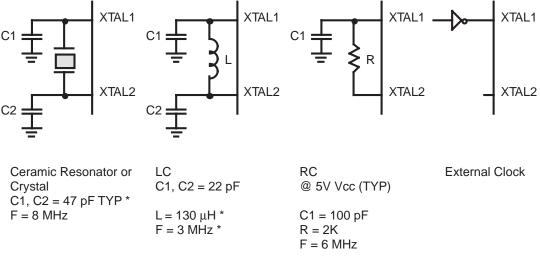

Figure 2. EPROM Programming Block Diagram

# CAPACITANCE

$T_A$  = 25°C,  $V_{CC}$  = GND = 0V, f = 1.0 MHz; unmeasured pins returned to GND.

| Parameter          | Min | Мах   |

|--------------------|-----|-------|

| Input capacitance  | 0   | 12 pF |

| Output capacitance | 0   | 12 pF |

| I/O capacitance    | 0   | 12 pF |

|                    |     |       |

### DC ELECTRICAL CHARACTERISTICS

|                     |                          |                             | T <sub>A</sub> = 0 °C                      | to +70 °C                                    |                   |       |                            |        |

|---------------------|--------------------------|-----------------------------|--------------------------------------------|----------------------------------------------|-------------------|-------|----------------------------|--------|

| Sym                 | Parameter                | V <sub>CC</sub><br>Note [3] | Min                                        | Мах                                          | Typical<br>@ 25°C | Units | Conditions                 | Notes  |

|                     | Clock Input High Voltage | 3.5V                        | 0.7 V <sub>CC</sub>                        | V <sub>CC</sub> +0.3                         | 1.8               | V     | Driven by External         |        |

| V <sub>CH</sub>     | Clock input high voltage | 5.5V<br>5.5V                | 0.7 V <sub>CC</sub><br>0.7 V <sub>CC</sub> | V <sub>CC</sub> +0.3<br>V <sub>CC</sub> +0.3 | 2.5               | V     | Clock Generator            |        |

|                     | Clock Input Low Voltage  | 3.5V                        | GND -0.3                                   |                                              | 0.9               | V     | Driven by External         |        |

| V <sub>CL</sub>     | Clock input Low voltage  | 3.5V<br>4.5V                | GND -0.3<br>GND -0.3                       | 0.2 V <sub>CC</sub>                          | 0.9<br>1.5        | V     | Clock Generator            |        |

|                     |                          |                             |                                            | 0.2 V <sub>CC</sub>                          |                   |       |                            |        |

| VIH                 | Input High Voltage       | 3.5V                        | 0.7 V <sub>CC</sub>                        | V <sub>CC</sub> +0.3                         | 2.5               | V     |                            |        |

|                     |                          | 5.5V                        | 0.7 V <sub>CC</sub>                        | V <sub>CC</sub> +0.3                         | 2.5               | V     |                            |        |

| V <sub>IL</sub>     | Input Low Voltage        | 3.5V                        | GND -0.3                                   | 0.2 V <sub>CC</sub>                          | 1.5               | V     |                            |        |

|                     |                          | 5.5V                        | GND -0.3                                   | 0.2 V <sub>CC</sub>                          | 1.5               | V     |                            |        |

| V <sub>OH</sub>     | Output High Voltage      | 3.5V                        | V <sub>CC</sub> -0.4                       |                                              | 3.3               | V     | I <sub>OH</sub> = – 0.5 mA |        |

|                     | Low EMI Mode             | 5.5V                        | V <sub>CC</sub> -0.4                       |                                              | 4.8               | V     |                            |        |

| V <sub>OH1</sub>    | Output High Voltage      | 3.5V                        | V <sub>CC</sub> -0.4                       |                                              | 3.3               | V     | I <sub>OH</sub> = -2.0 mA  |        |

| OIII                |                          | 5.5V                        | V <sub>CC</sub> -0.4                       |                                              | 4.8               | V     | I <sub>OH</sub> = -2.0 mA  |        |

| V <sub>OL</sub>     | Output Low Voltage       | 3.5V                        | 00                                         | 0.4                                          | 0.2               | V     | I <sub>OL</sub> = 1.0 mA   |        |

| VOL                 | Low EMI Mode             | 4.5V                        |                                            | 0.4                                          | 0.2               | v     | $I_{OL} = 1.0 \text{ mA}$  |        |

|                     |                          | 3.5V                        |                                            | 0.4                                          | 0.1               | V     | $I_{OL} = +4.0 \text{ mA}$ | 8      |

| V <sub>OL1</sub>    | Output Low Voltage       | 3.5V<br>4.5V                |                                            | 0.4                                          | 0.1               | V     |                            | о<br>8 |

|                     |                          |                             |                                            |                                              |                   |       | $I_{OL} = +4.0 \text{ mA}$ |        |

| V <sub>OL2</sub>    | Output Low Voltage       | 3.5V                        |                                            | 1.2                                          | 0.5               | V     | I <sub>OL</sub> = + 12 mA  | 8      |

|                     |                          | 4.5V                        |                                            | 1.2                                          | 0.5               | V     | I <sub>OL</sub> = + 12 mA  | 8      |

| V <sub>RH</sub>     | Reset Input High         | 3.5V                        | .8 V <sub>CC</sub>                         | V <sub>CC</sub>                              | 1.7               | V     |                            |        |

|                     | Voltage                  | 5.5V                        | .8 V <sub>CC</sub>                         | V <sub>CC</sub>                              | 2.1               | V     |                            |        |

| V <sub>RL</sub>     | Reset Input Low Voltage  | 3.5V                        | GND -0.3                                   | 0.2 V <sub>CC</sub>                          | 1.3               | V     |                            | 13     |

|                     |                          | 5.5V                        | GND -0.3                                   | 0.2 V <sub>CC</sub>                          | 1.7               | V     |                            |        |

| V <sub>OLR</sub>    | Reset Output Low         | 3.5V                        |                                            | 0.6                                          | 0.3               | V     | I <sub>OL</sub> = 1.0 mA   |        |

| OER                 | Voltage                  | 5.5V                        |                                            | 0.6                                          | 0.2               | V     | I <sub>OL</sub> = 1.0 mA   |        |

| V <sub>OFFSET</sub> | Comparator Input         | 3.5V                        |                                            | 25                                           | 10                | mV    | 02                         |        |

| OFFSEI              | Offset Voltage           | 4.5V                        |                                            | 25                                           | 10                | mV    |                            |        |

| V <sub>ICR</sub>    | Input Common Mode        | 3.5V                        | 0                                          | V <sub>CC</sub> -1.0V                        |                   | V     |                            | 10     |

| ICIX                | Voltage Range            | 5.5V                        | 0                                          | V <sub>CC</sub> -1.0V                        |                   | V     |                            | 10     |

| IIL                 | Input Leakage            | 3.5V                        | -1                                         | 2                                            | 0.032             | μA    | $V_{IN} = 0V, V_{CC}$      |        |

| ٦L                  | input Loundyo            | 4.5V                        | -1                                         | 2                                            | 0.032             | μA    | $V_{IN} = 0V, V_{CC}$      |        |

|                     | Output Lookaga           | 3.5V                        | -1                                         | 2                                            | 0.032             |       |                            |        |

| I <sub>OL</sub>     | Output Leakage           | 3.5V<br>4.5V                | -1<br>-1                                   | 2                                            | 0.032             | μA    | $V_{IN} = 0V, V_{CC}$      |        |

|                     |                          |                             |                                            |                                              |                   | μA    | $V_{IN} = 0V, V_{CC}$      |        |

| I <sub>IR</sub>     | Reset Input Current      | 3.5V                        | -20                                        | -130                                         | -65               | μA    |                            |        |

|                     |                          | 4.5V                        | -20                                        | -180                                         | -112              | μA    |                            |        |

## DC ELECTRICAL CHARACTERISTICS (Continued)

|    |           |                             | Note [3]        |     |     |       |       |

|----|-----------|-----------------------------|-----------------|-----|-----|-------|-------|

| No | Symbol    | Parameter                   | V <sub>CC</sub> | Min | Max | Units | Notes |

| 1  | TdA(AS)   | Address Valid to AS Rise    | 3.5V            | 25  |     | ns    | 2     |

|    | <b>、</b>  | Delay                       | 5.5V            | 25  |     | ns    |       |

| 2  | TdAS(A)   | AS Rise to Address Float    | 3.5V            | 35  |     | ns    | 2     |

|    |           | Delay                       | 5.5V            | 35  |     | ns    |       |

| 3  | TdAS(DR)  | AS Rise to Read Data Req'd  | 3.5V            |     | 180 | ns    | 1,2   |

|    |           | Valid                       | 5.5V            |     | 180 | ns    |       |

| 4  | TwAS      | AS Low Width                | 3.5V            | 40  |     | ns    | 2     |

|    |           |                             | 5.5V            | 40  |     | ns    |       |

| 5  | TdAS(DS)  | Address Float to DS Fall    | 3.5V            | 0   |     | ns    |       |

|    |           |                             | 5.5V            | 0   |     | ns    |       |

| 6  | TwDSR     | DS (Read) Low Width         | 3.5V            | 135 |     | ns    | 1,2   |

|    |           |                             | 5.5V            | 135 |     | ns    |       |

| 7  | TwDSW     | DS (Write) Low Width        | 3.5V            | 80  |     | ns    | 1,2   |

|    |           |                             | 5.5V            | 80  |     | ns    |       |

| 8  | TdDSR(DR) | DS Fall to Read Data Req'd  | 3.5V            |     | 75  | ns    | 1,2   |

|    |           | Valid                       | 5.5V            |     | 75  | ns    |       |

| 9  | ThDR(DS)  | Read Data to DS Rise Hold   | 3.5V            | 0   |     | ns    | 2     |

|    |           | Time                        | 5.5V            | 0   |     | ns    |       |

| 10 | TdDS(A)   | DS Rise to Address Active   | 3.5V            | 50  |     | ns    | 2     |

|    |           | Delay                       | 5.5V            | 50  |     | ns    |       |

| 11 | TdDS(AS)  | DS Rise to AS Fall Delay    | 3.5V            | 35  |     | ns    | 2     |

|    |           |                             | 5.5V            | 35  |     | ns    |       |

| 12 | TdR/W(AS) | R/W Valid to AS Rise Delay  | 3.5V            | 25  |     | ns    | 2     |

|    |           |                             | 5.5V            | 25  |     | ns    |       |

| 13 | TdDS(R/W) | DS Rise to R/W Not Valid    | 3.5V            | 35  |     | ns    | 2     |

|    |           |                             | 5.5V            | 35  |     | ns    |       |

| 14 | TdDW(DSW) | Write Data Valid to DS Fall | 3.5V            | 55  | 25  | ns    | 2     |

|    |           | (Write) Delay               | 5.5V            | 55  | 25  | ns    |       |

| 15 | TdDS(DW)  | DS Rise to Write Data Not   | 3.5V            | 35  |     | ns    | 2     |

|    |           | Valid Delay                 | 5.5V            | 35  |     | ns    |       |

| 16 | TdA(DR)   | Address Valid to Read Data  | 3.5V            |     | 230 | ns    | 1,2   |

|    |           | Req'd Valid                 | 5.5V            |     | 230 | ns    |       |

| 17 | TdAS(DS)  | AS Rise to DS Fall Delay    | 3.5V            | 45  |     | ns    | 2     |

|    |           | -                           | 5.5V            | 45  |     | ns    |       |

| 18 | TdDM(AS)  | DM Valid to AS Fall Delay   | 3.5V            | 30  |     | ns    | 2     |

|    |           |                             | 5.5V            | 30  |     | ns    |       |

| 20 | ThDS(AS)  | DS Valid to Address Valid   | 3.5V            | 35  |     | ns    |       |

|    |           | Hold Time                   | 5.5V            | 35  |     | ns    |       |

### Notes:

1. When using extended memory timing, add 2 TpC.

2. Timing numbers given are for minimum TpC.

3. The V<sub>CC</sub> voltage specification of 5.5V guarantees 5.0V  $\pm$ 0.5V and the V<sub>CC</sub> voltage specification of 3.5V guarantees only 3.5V

### Standard Test Load

All timing references use 0.7 V<sub>CC</sub> for a logic 1 and 0.2 V<sub>CC</sub> for a logic 0. For Standard Mode (not Low-EMI Mode for outputs) with SMR D1 = 0, D0 = 0. Zilog

|    |                                       | T <sub>A</sub> = -40°C to 105°C<br>16 MHz            |                 |          |            |          |       |  |  |

|----|---------------------------------------|------------------------------------------------------|-----------------|----------|------------|----------|-------|--|--|

|    |                                       |                                                      | Note [3]        |          |            |          |       |  |  |

| No | Symbol                                | Parameter                                            | V <sub>CC</sub> | Min      | Max        | Units    | Notes |  |  |

| 1  | TdA(AS)                               | Address Valid to AS Rise                             | 4.5V            | 25       |            | ns       | 2     |  |  |

|    |                                       | Delay                                                | 5.5V            | 25       |            | ns       |       |  |  |

| 2  | TdAS(A)                               | ASAS Rise to Address Float<br>Delay                  | 4.5V<br>5.5V    | 35<br>35 |            | ns<br>ns | 2     |  |  |

| 3  |                                       | -                                                    |                 |          | 400        |          | 10    |  |  |

| 3  | TdAS(DR)                              | AS Rise to Read Data Req'd<br>Valid                  | 4.5V<br>5.5V    |          | 180<br>180 | ns<br>ns | 1,2   |  |  |

| 4  | TwAS                                  | AS Low Width                                         | 4.5V            | 40       |            | ns       | 2     |  |  |

|    | -                                     |                                                      | 5.5V            | 40       |            | ns       |       |  |  |

| 5  | TdAS(DS)                              | Address Float to DS Fall                             | 4.5V            | 0        |            | ns       |       |  |  |

|    | ( - )                                 |                                                      | 5.5V            | 0        |            | ns       |       |  |  |

| 6  | TwDSR                                 | DS (Read) Low Width                                  | 4.5V            | 135      |            | ns       | 1,2   |  |  |

| -  | -                                     |                                                      | 5.5V            | 135      |            | ns       | ,     |  |  |

| 7  | TwDSW                                 | DS (Write) Low Width                                 | 4.5V            | 80       |            | ns       | 1,2   |  |  |

|    |                                       |                                                      | 5.5V            | 80       |            | ns       | ,     |  |  |

| 8  | TdDSR(DR)                             | DS Fall to Read Data Req'd                           | 4.5V            |          | 75         | ns       | 1,2   |  |  |

|    | ( )                                   | Valid                                                | 5.5V            |          | 75         | ns       | ,     |  |  |

| 9  | ThDR(DS)                              | Read Data to DS Rise Hold                            | 4.5V            | 0        |            | ns       | 2     |  |  |

|    | ( - )                                 | Time                                                 | 5.5V            | 0        |            | ns       |       |  |  |

| 10 | TdDS(A)                               | DS Rise to Address Active                            | 4.5V            | 50       |            | ns       | 2     |  |  |

|    |                                       | Delay                                                | 5.5V            | 50       |            | ns       |       |  |  |

| 11 | TdDS(AS)                              | DS Rise to AS Fall Delay                             | 4.5V            | 35       |            | ns       | 2     |  |  |

|    |                                       |                                                      | 5.5V            | 35       |            | ns       |       |  |  |

| 12 | TdR/W(AS)                             | $R/\overline{W}$ Valid to $\overline{AS}$ Rise Delay | 4.5V            | 25       |            | ns       | 2     |  |  |

|    |                                       |                                                      | 5.5V            | 25       |            | ns       |       |  |  |

| 13 | TdDS(R/W)                             | DS Rise to R/W Not Valid                             | 4.5V            | 35       |            | ns       | 2     |  |  |

|    |                                       |                                                      | 5.5V            | 35       |            | ns       |       |  |  |

| 14 | TdDW(DSW)                             | Write Data Valid to DS Fall                          | 4.5V            | 55       | 25         | ns       | 2     |  |  |

|    | , , , , , , , , , , , , , , , , , , , | (Write) Delay                                        | 5.5V            | 55       | 25         | ns       |       |  |  |

| 15 | TdDS(DW)                              | DS Rise to Write Data Not                            | 4.5V            | 35       |            | ns       | 2     |  |  |

|    |                                       | Valid Delay                                          | 5.5V            | 35       |            | ns       |       |  |  |

| 16 | TdA(DR)                               | Address Valid to Read Data                           | 4.5V            |          | 230        | ns       | 1,2   |  |  |

|    | . ,                                   | Req'd Valid                                          | 5.5V            |          | 230        | ns       |       |  |  |

| 17 | TdAS(DS)                              | AS Rise to DS Fall Delay                             | 4.5V            | 45       |            | ns       | 2     |  |  |

|    |                                       | -                                                    | 5.5V            | 45       |            | ns       |       |  |  |

| 18 | TdDM(AS)                              | /DM Valid to AS Fall Delay                           | 4.5V            | 30       |            | ns       | 2     |  |  |

|    |                                       |                                                      | 5.5V            | 30       |            | ns       |       |  |  |

| 20 | ThDS(AS)                              | DS Valid to Address Valid                            | 4.5V            | 35       |            | ns       |       |  |  |

|    | . ,                                   | Hold Time                                            | 5.5V            | 35       |            | ns       |       |  |  |

### Notes:

1. When using extended memory timing, add 2 TpC.

2. Timing numbers given are for minimum TpC.

3. The V<sub>CC</sub> voltage specification of 5.5V guarantees 5.0V  $\pm$ 0.5V and the V<sub>CC</sub> voltage specification of 3.5V guarantees only 3.5V

#### Standard Test Load

All timing references use 0.7  $V_{CC}$  for a logic 1 and 0.2  $V_{CC}$  for a logic 0.

For Standard Mode (not Low-EMI Mode for outputs) with SMR, D1 = 0, D0 = 0.

### DC ELECTRICAL CHARACTERISTICS (Continued)

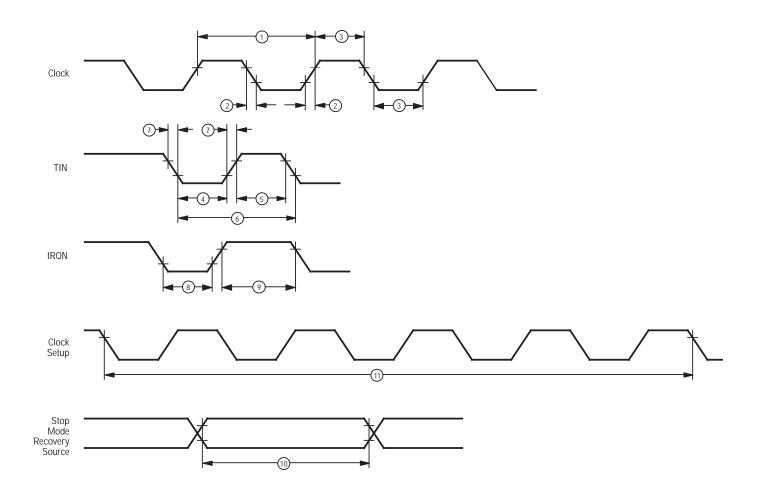

Figure 15. Additional Timing Diagram

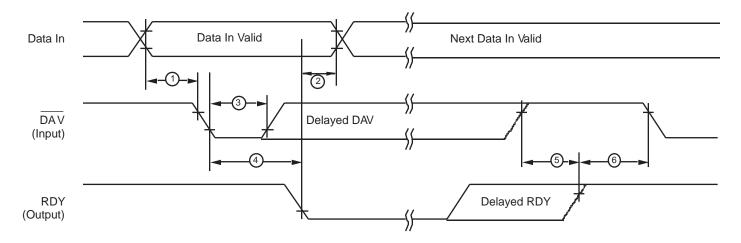

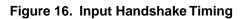

# Handshake Timing Diagrams

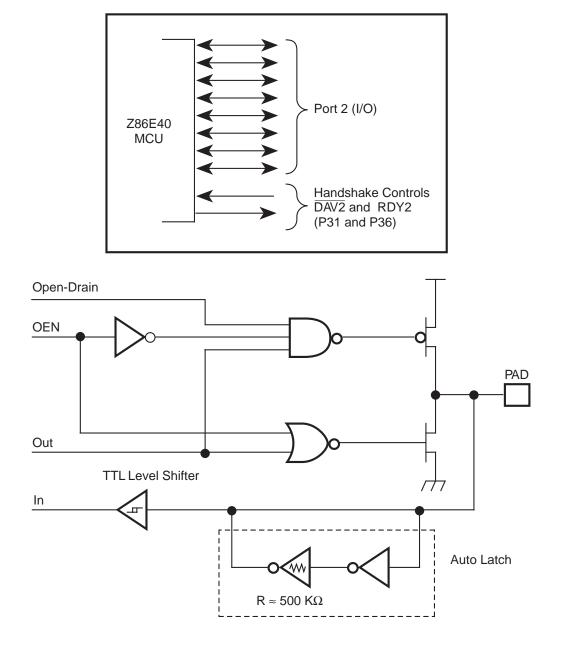

Figure 17. Output Handshake Timing

### **Additional Timing Table**

|       | T <sub>A</sub> = -40 °C to +105 °C<br>16 MHz |                    |                 |       |       |       |            |           |  |  |

|-------|----------------------------------------------|--------------------|-----------------|-------|-------|-------|------------|-----------|--|--|

|       |                                              |                    | V <sub>CC</sub> |       | 11 12 |       |            |           |  |  |

| No Sy | Symbol                                       | Parameter          | Note [6]        | Min   | Max   | Units | Conditions | Notes     |  |  |

| 1     | ТрС                                          | Input Clock Period | 3.5V            | 62.5  | DC    | ns    |            | 1,7,8     |  |  |

|       |                                              |                    | 5.5V            | 62.5  | DC    | ns    |            | 1,7,8     |  |  |

| 2     | TrC,TfC                                      | Clock Input Rise & | 3.5V            |       | 15    | ns    |            | 1,7,8     |  |  |

|       |                                              | Fall Times         | 5.5V            |       | 15    | ns    |            | 1,7,8     |  |  |

| 3     | TwC                                          | Input Clock Width  | 3.5V            | 31    |       | ns    |            | 1,7,8     |  |  |

|       |                                              |                    | 5.5V            | 31    |       | ns    |            | 1,7,8     |  |  |

| 4     | TwTinL                                       | Timer Input Low    | 3.5V            | 70    |       | ns    |            | 1,7,8     |  |  |

|       |                                              | Width              | 5.5V            | 70    |       | ns    |            | 1,7,8     |  |  |

| 5     | TwTinH                                       | Timer Input High   | 3.5V            | 5TpC  |       |       |            | 1,7,8     |  |  |

|       |                                              | Width              | 5.5V            | 5TpC  |       |       |            | 1,7,8     |  |  |

| 6     | TpTin                                        | Timer Input Period | 3.5V            | 8TpC  |       |       |            | 1,7,8     |  |  |

|       | ·                                            | I                  | 5.5V            | 8TpC  |       |       |            | 1,7,8     |  |  |

| 7     | TrTin, TfTir                                 | n Timer Input Rise | 3.5V            |       | 100   | ns    |            | 1,7,8     |  |  |

|       | ,                                            | & Fall Timer       | 5.5V            |       | 100   | ns    |            | 1,7,8     |  |  |

| 8A    | TwIL                                         | Int. Request Low   | 3.5V            | 70    |       | ns    |            | 1,2,7,8   |  |  |

|       |                                              | Time               | 5.5V            | 70    |       | ns    |            | 1,2,7,8   |  |  |

| 8B    | TwIL                                         | Int. Request Low   | 3.5V            | 5TpC  |       |       |            | 1,3,7,8   |  |  |

|       |                                              | Time               | 5.5V            | 5TpC  |       |       |            | 1,3,7,8   |  |  |

| 9     | TwIH                                         | Int. Request Input | 3.5V            | 5TpC  |       |       |            | 1,2,7,8   |  |  |

|       |                                              | High Time          | 5.5V            | - 1 - |       |       |            | , , , , - |  |  |

| 10    | Twsm                                         | STOP Mode          | 3.5V            | 12    |       | ns    |            | 4,8       |  |  |

| -     | -                                            | Recovery Width     | 5.5V            | 12    |       | ns    |            | 4,8       |  |  |

|       |                                              | Spec               |                 |       |       |       |            |           |  |  |

| 11    | Tost                                         | Oscillator Startup | 3.5V            |       | 5TpC  |       |            | 4,8       |  |  |

|       |                                              | Time               | 5.5V            |       | 5TpC  |       |            | 4,8       |  |  |

| 12    | Twdt                                         | Watch-Dog Timer    | 3.5V            | 10    |       | ms    | D0 = 0     | 5,11      |  |  |

|       |                                              | Delay Time         | 5.5V            | 5     |       | ms    | D1 = 0     | 5,11      |  |  |

|       |                                              | Before Timeout     | 3.5V            | 20    |       | ms    | D0 = 1     | 5,11      |  |  |

|       |                                              |                    | 5.5V            | 10    |       | ms    | D1 = 0     | 5,11      |  |  |

|       |                                              | -                  | 3.5V            | 40    |       | ms    | D0 = 0     | 5,11      |  |  |

|       |                                              |                    | 5.5V            | 20    |       | ms    | D1 = 1     | 5,11      |  |  |

|       |                                              | -                  | 3.5V            | 160   |       | ms    | D0 = 1     | 5,11      |  |  |

|       |                                              |                    | 5.5V            | 80    |       | ms    | D1 = 1     | 5,11      |  |  |

#### Notes:

- 1. Timing Reference uses 0.7  $V_{CC}$  for a logic 1 and 0.2  $V_{CC}$  for a logic 0.

- 2. Interrupt request via Port 3 (P31–P33)

- 3. Interrupt request via Port 3 (P30)

- 4. SMR-D5 = 1, POR STOP Mode Delay is on

- 5. Reg. WDTMR

- 6. The  $V_{CC}$  voltage spec. of 5.5V guarantees 5.0V  $\pm$  0.5V.

- 7. SMR D1 = 0

- 8. Maximum frequency for internal system clock is 4 MHz when using XTAL divide-by-one mode.

- 9. For RC and LC oscillator, and for oscillator driven by clock driver.

- 10. Standard Mode (not Low EMI output ports)

- 11. Using internal RC

### PIN FUNCTIONS (Continued)

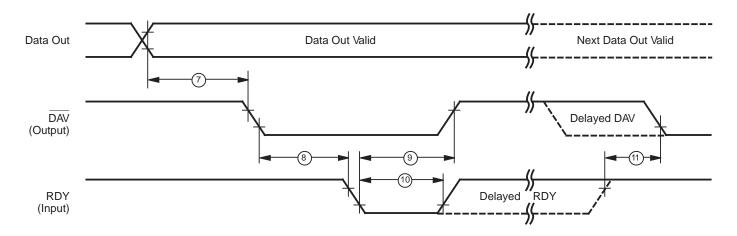

**Port 1** (P17–P10). Port 1 is an 8-bit, bidirectional, CMOScompatible port with multiplexed Address (A7–A0) and Data (D7–D0) ports. These eight I/O lines can be programmed as inputs or outputs or can be configured under software control as an Address/Data port for interfacing external memory. The input buffers are Schmitt-triggered and the output buffers can be globally programmed as either push-pull or open-drain. Low EMI output buffers can be globally programmed by the software. Port 1 can be placed under handshake control. In this configuration, Port 3, lines P33 and P34 are used as the handshake controls RDY1 and /DAV1 (Ready and Data Available). To interface external memory, Port 1 must be programmed for the multiplexed Address/Data mode. If more than 256 external locations are required, Port 0 outputs the additional lines (Figure 19).

Port 1 can be placed in the high-impedance state along with Port 0,  $\overline{AS}$ ,  $\overline{DS}$ , and  $R/\overline{W}$ , allowing the Z86E40 to share common resources in multiprocessor and DMA applications.

Figure 19. Port 1 Configuration (Z86E40 Only)

Zilog

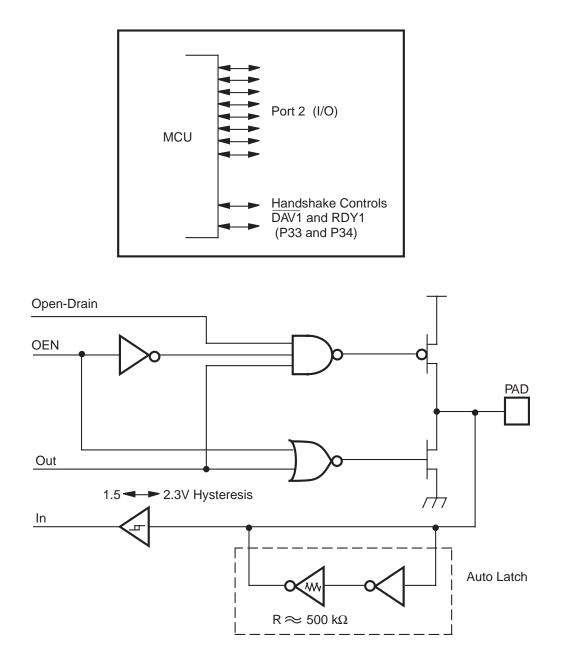

**Port 2** (P27–P20). Port 2 is an 8-bit, bidirectional, CMOScompatible I/O port. These eight I/O lines can be configured under software control as an input or output, independently. All input buffers are Schmitt-triggered. Bits programmed as outputs can be globally programmed as either push-pull or open-drain. Low EMI output buffers can be globally programmed by the software. When used as an I/O port, Port 2 can be placed under handshake control.

In Handshake Mode, Port 3 lines P31 and P36 are used as handshake control lines. The handshake direction is determined by the configuration (input or output) assigned to bit 7 of Port 2 (Figure 20).

Figure 20. Port 2 Configuration

# FUNCTIONAL DESCRIPTION

The MCU incorporates the following special functions to enhance the standard Z8 architecture to provide the user with increased design flexibility.

**RESET.** The device is reset in one of three ways:

- 1. Power-On Reset

- 2. Watch-Dog Timer

- 3. STOP-Mode Recovery Source

**Note:** Having the Auto Power-On Reset circuitry built-in, the MCU does not need to be connected to an external power-on reset circuit. The reset time is 5 ms (typical). The MCU does not reinitialize WDTMR, SMR, P2M, and P3M registers to their reset values on a STOP-Mode Recovery operation.

**Note:** The device  $V_{CC}$  must rise up to the operating  $V_{CC}$  specification before the TPOR expires.

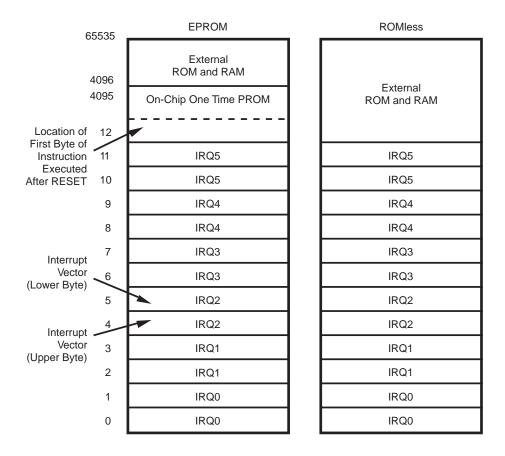

**Program Memory.** The MCU can address up to 4 KB of Internal Program Memory (Figure 22). The first 12 bytes of program memory are reserved for the interrupt vectors. These locations contain six 16-bit vectors that correspond to the six available interrupts. For EPROM mode, byte 12 (000CH) to address 4095 (0FFFH) consists of programmable EPROM. After reset, the program counter points at the address 000CH, which is the starting address of the user program.

In ROMless mode, the Z86E40 can address up to 64 KB of External Program Memory. The ROM/ROMless option is only available on the 44-pin devices.

### Figure 22. Program Memory Map (ROMIess Z86E40 Only)

**EPROM Protect.** When in ROM Protect Mode, and executing out of External Program Memory, instructions LDC, LDCI, LDE, and LDEI cannot read Internal Program Memory.

When in ROM Protect Mode and executing out of Internal Program Memory, instructions LDC, LDCI, LDE, and LDEI can read Internal Program Memory.

### FUNCTIONAL DESCRIPTION (Continued)

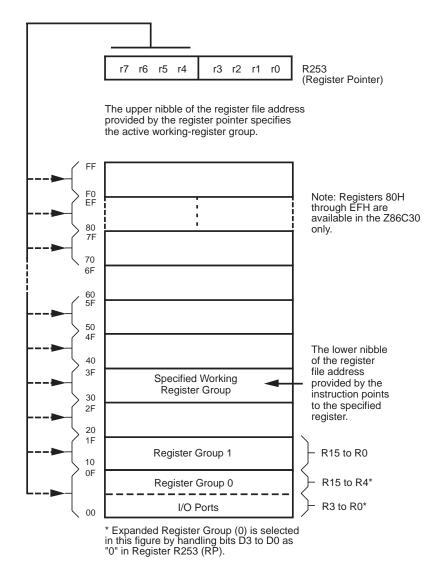

Figure 25. Register Pointer

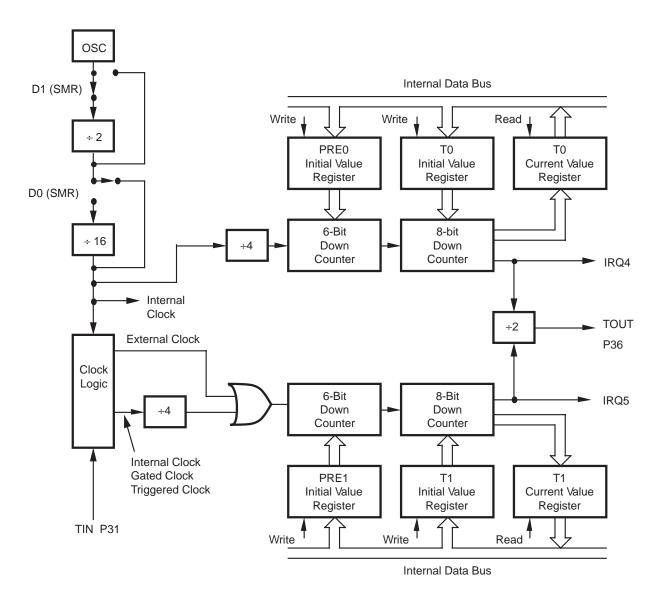

Figure 27. Counter/Timer Block Diagram

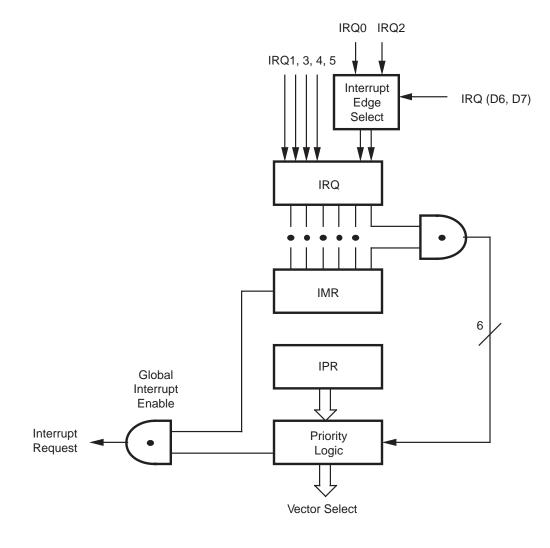

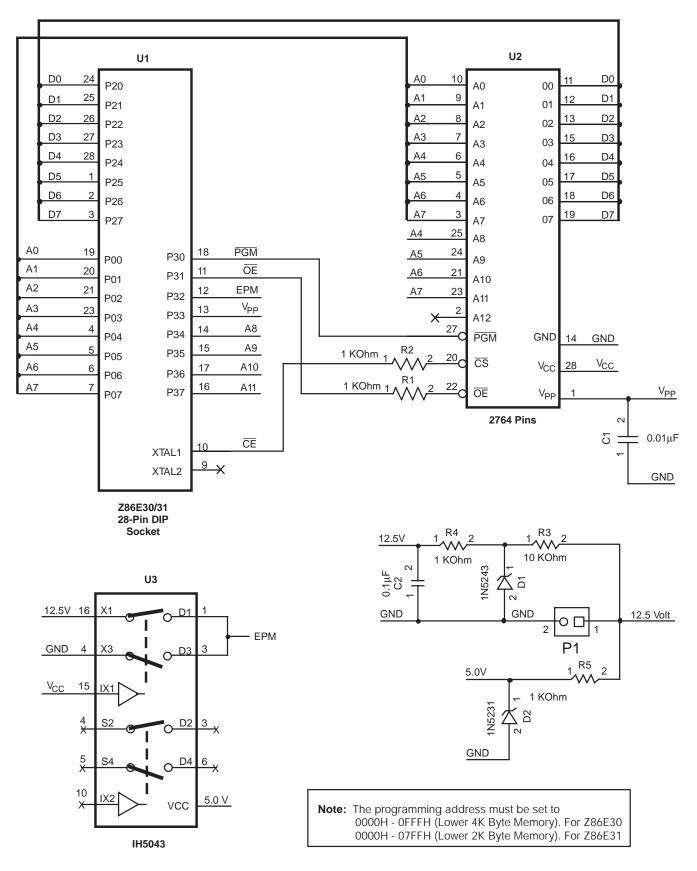

**Interrupts.** The MCU has six different interrupts from six different sources. The interrupts are maskable and prioritized (Figure 28). The six sources are divided as follows: four sources are claimed by Port 3 lines P33–P30) and two

in counter/timers. The Interrupt Mask Register globally or individually enables or disables the six interrupt requests (Table 10).

| Table 10. | Interrupt Types, | Sources, | and Vectors |

|-----------|------------------|----------|-------------|

|-----------|------------------|----------|-------------|

| Name | Source                      | Vector Location | Comments                                      |

|------|-----------------------------|-----------------|-----------------------------------------------|

| IRQ0 | DAV0, IRQ0                  | 0, 1            | External (P32), Rising/Falling Edge Triggered |

| IRQ1 | IRQ1                        | 2, 3            | External (P33), Falling Edge Triggered        |

| IRQ2 | DAV2, IRQ2, T <sub>IN</sub> | 4, 5            | External (P31), Rising/Falling Edge Triggered |

| IRQ3 | IRQ3                        | 6, 7            | External (P30), Falling Edge Triggered        |

| IRQ4 | Т0                          | 8, 9            | Internal                                      |

| IRQ5 | TI                          | 10, 11          | Internal                                      |

When more than one interrupt is pending, priorities are resolved by a programmable priority encoder that is controlled by the Interrupt Priority Register (IPR). An interrupt machine cycle is activated when an interrupt request is granted. Thus, disabling all subsequent interrupts, saves the Program Counter and Status Flags, and then branches to the program memory vector location reserved for that interrupt. All interrupts are vectored through locations in the program memory. This memory location and the next byte contain the 16-bit starting address of the interrupt service routine for that particular interrupt request.

To accommodate polled interrupt systems, interrupt inputs are masked and the interrupt request register is polled to determine which of the interrupt requests need service.

An interrupt resulting from AN1 is mapped into IRQ2, and an interrupt from AN2 is mapped into IRQ0. Interrupts IRQ2 and IRQ0 may be rising, falling or both edge triggered, and are programmable by the user. The software may poll to identify the state of the pin.

Programming bits for the Interrupt Edge Select are located in bits D7 and D6 of the IRQ Register (R250). The configuration is shown in Table 11. Table 11. IRQ Register Configuration

| D7 | D6 | P31 | P32 |

|----|----|-----|-----|

| 0  | 0  | F   | F   |

| 0  | 1  | F   | R   |

| 1  | 0  | R   | F   |

| 1  | 1  | R/F | R/F |

R = Rising Edge

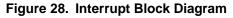

**Clock.** The on-chip oscillator has a high-gain, parallel-resonant amplifier for connection to a crystal, RC, ceramic resonator, or any suitable external clock source (XTAL1 = Input, XTAL2 = Output). The crystal should be AT cut, 10 KHz to 16 MHz max, with a series resistance (RS) less than or equal to 100 Ohms.

The crystal should be connected across XTAL1 and XTAL2 using the vendor's recommended capacitor values from each pin directly to device pin Ground. The RC oscillator option can be selected in the programming mode. The RC oscillator configuration must be an external resistor connected from XTAL1 to XTAL2, with a frequency-setting capacitor from XTAL1 to Ground (Figure 29).

\* Typical value including pin parasitics

Figure 29. Oscillator Configuration

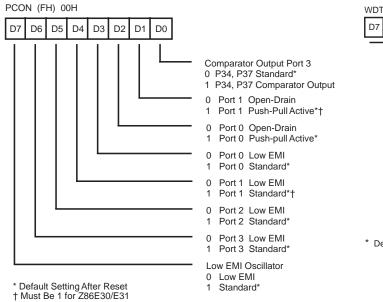

**Comparator Output Port 3** (D0). Bit 0 controls the comparator output in Port 3. A "1" in this location brings the comparator outputs to P34 and P37, and a "0" releases the Port to its standard I/O configuration. The default value is 0.

**Port 1 Open-Drain** (D1). Port 1 can be configured as an open-drain by resetting this bit (D1=0) or configured as push-pull active by setting this bit (D1=1). The default value is 1.

**Port 0 Open-Drain** (D2). Port 0 can be configured as an open-drain by resetting this bit (D2=0) or configured as push-pull active by setting this bit (D2=1). The default value is 1.

**Low EMI Port 0** (D3). Port 0 can be configured as a Low EMI Port by resetting this bit (D3=0) or configured as a Standard Port by setting this bit (D3=1). The default value is 1.

**Low EMI Port 1** (D4). Port 1 can be configured as a Low EMI Port by resetting this bit (D4=0) or configured as a Standard Port by setting this bit (D4=1). The default value is 1. **Note:** The emulator does not support Port 1 low EMI mode and must be set D4 = 1.

**Low EMI Port 2** (D5). Port 2 can be configured as a Low EMI Port by resetting this bit (D5=0) or configured as a Standard Port by setting this bit (D5=1). The default value is 1.

**Low EMI Port 3** (D6). Port 3 can be configured as a Low EMI Port by resetting this bit (D6=0) or configured as a Standard Port by setting this bit (D6=1). The default value is 1.

**Low EMI OSC** (D7). This bit of the PCON Register controls the low EMI noise oscillator. A "1" in this location configures the oscillator with standard drive. While a "0" configures the oscillator with low noise drive, however, it does not affect the relationship of SCLK and XTAL. The low EMI mode will reduce the drive of the oscillator (OSC). The default value is 1. **Note:** 4 MHz is the maximum external clock frequency when running in the low EMI oscillator mode.

**Stop-Mode Recovery Register** (SMR). This register selects the clock divide value and determines the mode of Stop-Mode Recovery (Figure 31). All bits are Write Only except bit 7 which is a Read Only. Bit 7 is a flag bit that is hardware set on the condition of STOP Recovery and reset by a power-on cycle. Bit 6 controls whether a low or high level is required from the recovery source. Bit 5 controls the reset delay after recovery. Bits 2, 3, and 4 of the SMR register specify the Stop-Mode Recovery Source. The SMR is located in Bank F of the Expanded Register Group at address 0BH.

### Table 14. EPROM Programming Table

| Programming<br>Modes | V <sub>PP</sub> | EPM            | CE              | ŌĒ              | PGM             | ADDR | DATA | V <sub>CC</sub> * |

|----------------------|-----------------|----------------|-----------------|-----------------|-----------------|------|------|-------------------|

| EPROM READ1          | Х               | V <sub>H</sub> | V <sub>IL</sub> | V <sub>IL</sub> | V <sub>IH</sub> | ADDR | Out  | 4.5V†             |

| EPROM READ2          | Х               | V <sub>H</sub> | V <sub>IL</sub> | V <sub>IL</sub> | V <sub>IH</sub> | ADDR | Out  | 5.5V†             |

| PROGRAM              | V <sub>H</sub>  | V <sub>H</sub> | $V_{IL}$        | $V_{IH}$        | $V_{IL}$        | ADDR | In   | 6.4V              |

| PROGRAM<br>VERIFY    | V <sub>H</sub>  | V <sub>H</sub> | V <sub>IL</sub> | V <sub>IL</sub> | V <sub>IH</sub> | ADDR | Out  | 6.0V              |

| OPTION BIT PGM       | V <sub>H</sub>  | V <sub>H</sub> | $V_{IL}$        | V <sub>IH</sub> | V <sub>IL</sub> | 63   | IN   | 6.4V              |

| OPTION BIT READ      | Х               | V <sub>H</sub> | $V_{IL}$        | V <sub>IL</sub> | $V_{\text{IH}}$ | 63   | OUT  | 6.0V              |

#### Notes:

$V_{H} = 13.0 \text{ V} \pm 0.1 \text{ V}$

$V_{\mbox{\scriptsize IH}}$  = As per specific Z8 DC specification

VIL= As per specific Z8 DC specification

X=Not used, but must be set to  $V_H$ ,  $V_{IH}$ , or  $V_{IL}$  level.

NU = Not used, but must be set to either  $V_{IH}$  or  $V_{IL}$  level.

$I_{PP}$  during programming = 40 mA maximum.

$I_{CC}$  during programming, verify, or read = 40 mA maximum.

$^{*}V_{CC}$  has a tolerance of  $\pm 0.25V$ .

† Zilog recommends an EPROM read at V<sub>CC</sub> = 4.5 V and 5.5 V to

ensure proper device operations during the  $V_{\mbox{CC}}$  after programming,

but  $V_{CC} = 5.0$  V is acceptable.

| Parameters | Name                                                     | Min  | Max  | Units |

|------------|----------------------------------------------------------|------|------|-------|

| 1          | Address Setup Time                                       | 2    |      | μs    |

| 2          | Data Setup Time                                          | 2    |      | μs    |

| 3          | V <sub>PP</sub> Setup                                    | 2    |      | μs    |

| 4          | V <sub>CC</sub> Setup Time                               | 2    |      | μs    |

| 5          | Chip Enable Setup Time                                   | 2    |      | μs    |

| 6          | Program Pulse Width                                      | 0.95 | 1.05 | ms    |

| 7          | Data Hold Time                                           | 2    |      | μs    |

| 8          | OE Setup Time                                            | 2    |      | μs    |

| 9          | Data Access Time                                         | 200  |      | ns    |

| 10         | Data Output Float Time                                   |      | 100  | ns    |

| 11         | Overprogram Pulse<br>Width/Option Program<br>Pulse Width | 2.85 |      | ms    |

| 12         | EPM Setup Time                                           | 2    |      | μs    |

| 13         | PGM Setup Time                                           | 2    |      | μs    |

| 14         | Address to OE Setup Time                                 | 2    |      | μs    |

| 15         | OE Width                                                 | 250  |      | ns    |

| 16         | Address to OE Low                                        | 125  |      | ns    |

### Table 15. EPROM Programming Timing

# **EXPANDED REGISTER FILE CONTROL REGISTERS**

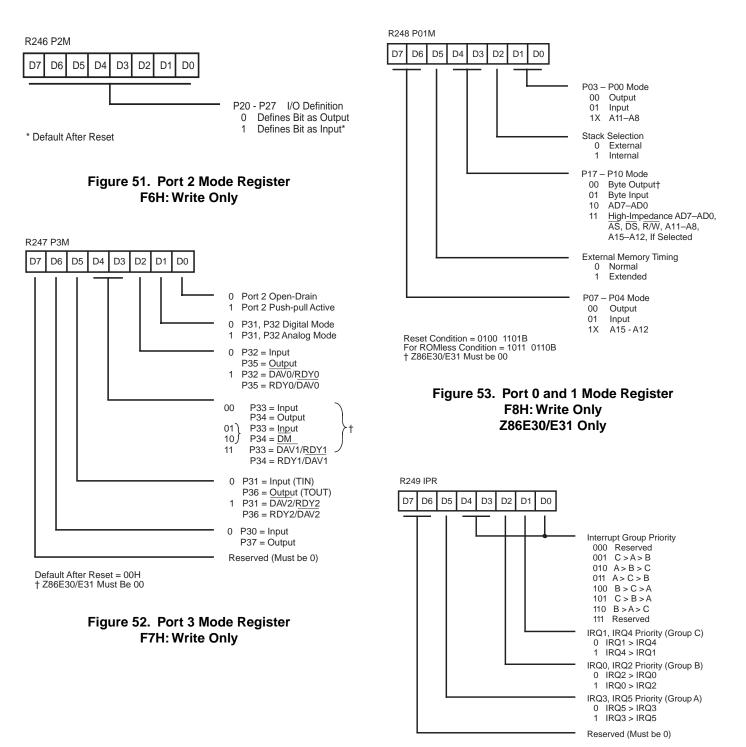

Figure 41. Port Configuration Register

Write Only

\* Default setting after RESET

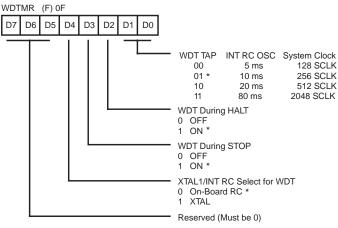

### Figure 43. Watch-Dog Timer Mode Register Write Only

Note: Not used in conjunction with SMR Source

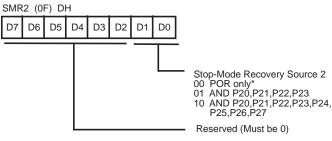

### Figure 44. STOP-Mode Recovery Register 2 Write Only

D6 D5 D4 D3 D2 D1 D0 SCLK/TCLK Divide-by-16 0 OFF \* 1 ON External Clock Divide by 2 SCLK/TCLK =XTAL/2\* 0 1 SCLK/TCLK =XTAL Stop Mode Recovery Source 000 POR Only and/or External Reset\* 001 P30 010 P31 011 P32 100 P33 101 P27 110 P2 NOR 0-3 111 P2 NOR 0-7 Stop Delay 0 OFF 1 ON\* Stop Recovery Level 0 Low\* 1 High Stop Flag POR\* 0 1 Stop Recovery

\* Default setting after RESET. \*\* Default setting after RESET and STOP-Mode Recovery.

### Figure 42. STOP-Mode Recovery Register Write Only Except Bit D7, Which is Read Only

SMR (FH) 0B

D7

# **Z8 CONTROL REGISTER DIAGRAMS** (Continued)

Figure 54. Interrupt Priority Register F9H: Write Only

# **Customer Support**

For answers to technical questions about the product, documentation, or any other issues with Zilog's offerings, please visit Zilog's Knowledge Base at <u>http://www.zilog.com/kb</u>.

For any comments, detail technical questions, or reporting problems, please visit Zilog's Technical Support at <u>http://support.zilog.com</u>.