### Zilog - Z86E4016FSG Datasheet

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

| Product Status             | Obsolete                                               |

|----------------------------|--------------------------------------------------------|

| Core Processor             | Z8                                                     |

| Core Size                  | 8-Bit                                                  |

| Speed                      | 16MHz                                                  |

| Connectivity               | -                                                      |

| Peripherals                | POR, WDT                                               |

| Number of I/O              | 32                                                     |

| Program Memory Size        | 4KB (4K x 8)                                           |

| Program Memory Type        | OTP                                                    |

| EEPROM Size                | -                                                      |

| RAM Size                   | 236 x 8                                                |

| Voltage - Supply (Vcc/Vdd) | 3.5V ~ 5.5V                                            |

| Data Converters            | -                                                      |

| Oscillator Type            | Internal                                               |

| Operating Temperature      | 0°C ~ 70°C (TA)                                        |

| Mounting Type              | Surface Mount                                          |

| Package / Case             | 44-LQFP                                                |

| Supplier Device Package    | 44-LQFP (10x10)                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z86e4016fsg |

|                            |                                                        |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

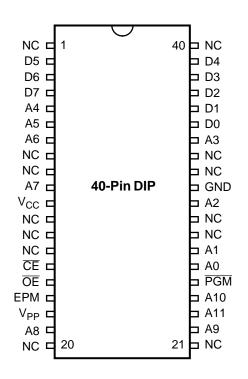

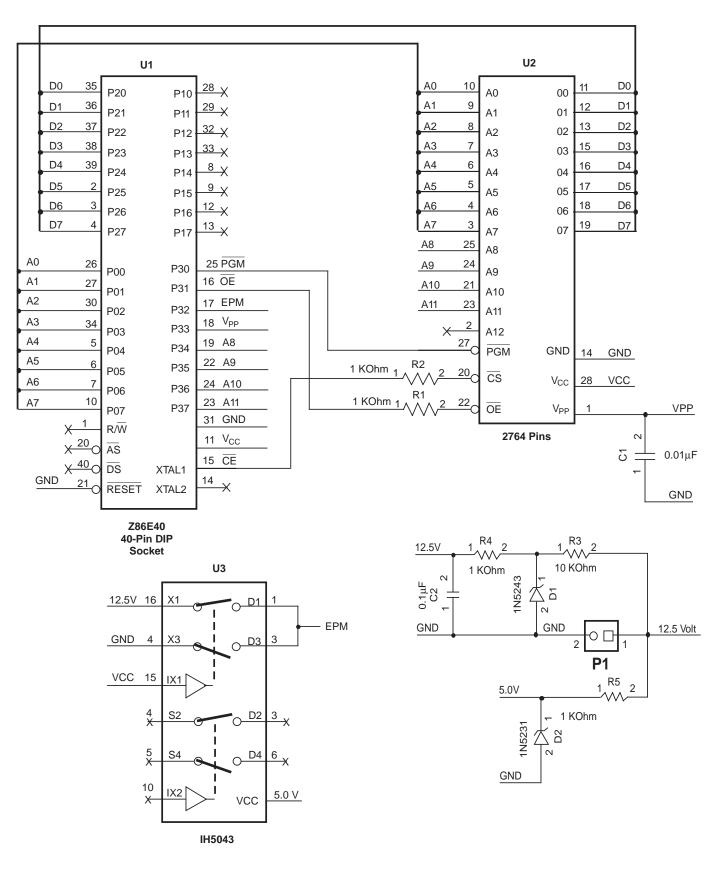

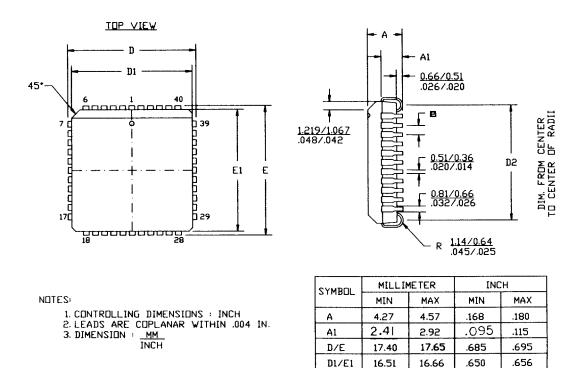

### Figure 6. 40-Pin DIP Pin Configuration EPROM Mode

# Table 4. 40-Pin DIP Package Pin IdentificationEPROM Mode

| Pin # | Symbol          | Function         | Direction |

|-------|-----------------|------------------|-----------|

| 1     | NC              | No Connection    |           |

| 2–4   | D5–D7           | Data 5,6,7       | In/Output |

| 5–7   | A4–A6           | Address 4,5,6    | Input     |

| 8–9   | NC              | No Connection    |           |

| 10    | A7              | Address 7        | Input     |

| 11    | V <sub>CC</sub> | Power Supply     |           |

| 12–14 | NC              | No Connection    |           |

| 15    | CE              | Chip Select      | Input     |

| 16    | ŌĒ              | Output Enable    | Input     |

| 17    | EPM             | EPROM Prog. Mode | Input     |

| 18    | V <sub>PP</sub> | Prog. Voltage    | Input     |

| 19    | A8              | Address 8        | Input     |

| 20–21 | NC              | No Connection    |           |

| 22    | A9              | Address 9        | Input     |

| 23    | A11             | Address 11       | Input     |

| 24    | A10             | Address 10       | Input     |

| 25    | PGM             | Prog. Mode       | Input     |

| 26–27 | A0–A1           | Address 0,1      | Input     |

| 28–29 | NC              | No Connection    |           |

| 30    | A2              | Address 2        | Input     |

| 31    | GND             | Ground           |           |

| 32–33 | NC              | No Connection    |           |

| 34    | A3              | Address 3        | Input     |

| 35–39 | D0–D4           | Data 0,1,2,3,4   | In/Output |

| 40    | NC              | No Connection    |           |

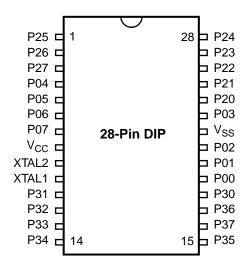

Figure 9. Standard Mode 28-Pin DIP/SOIC Pin Configuration

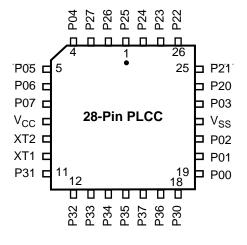

### Table 7. 28-Pin DIP/SOIC/PLCC Pin Identification\*

| Pin # | Symbol          | Function                  | Direction   |

|-------|-----------------|---------------------------|-------------|

| 1–3   | P25–P27         | Port 2, Pins 5,6,         | In/Output   |

| 4–7   | P04–P07         | Port 0, Pins 4,5,6,7      | 7 In/Output |

| 8     | V <sub>CC</sub> | Power Supply              |             |

| 9     | XTAL2           | Crystal Oscillator        | Output      |

| 10    | XTAL1           | Crystal Oscillator        | Input       |

| 11–13 | P31–P33         | Port 3, Pins 1,2,3        | Input       |

| 14–15 | P34–P35         | Port 3, Pins 4,5          | Output      |

| 16    | P37             | Port 3, Pin 7             | Output      |

| 17    | P36             | Port 3, Pin 6             | Output      |

| 18    | P30             | Port 3, Pin 0             | Input       |

| 19–21 | P00-P02         | Port 0, Pins 0,1,2        | In/Output   |

| 22    | V <sub>SS</sub> | Ground                    |             |

| 23    | P03             | Port 0, Pin 3             | In/Output   |

| 24–28 | P20–P24         | Port 2, Pins<br>0,1,2,3,4 | In/Output   |

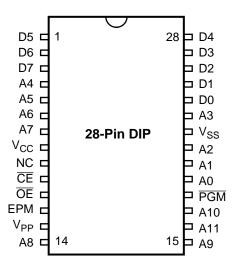

# Figure 10. EPROM Programming Mode 28-Pin DIP/SOIC Pin Configuration

Figure 11. Standard Mode 28-Pin PLCC Pin Configuration

|                  |                    |                 | T <sub>A</sub> = 0 °C | to +70 °C |         |       |                                       |        |

|------------------|--------------------|-----------------|-----------------------|-----------|---------|-------|---------------------------------------|--------|

|                  |                    | V <sub>CC</sub> | ~                     |           | Typical |       |                                       |        |

| Sym              | Parameter          | Note [3]        | Min                   | Мах       | @ 25°C  | Units | Conditions                            | Notes  |

| I <sub>CC</sub>  | Supply Current     | 3.5V            |                       | 20        | 7       | mA    | @ 16 MHz                              | 4,5    |

|                  |                    | 5.5V            |                       | 25        | 20      | mA    | @ 16 MHz                              | 4,5    |

| I <sub>CC1</sub> | Standby Current    | 3.5V            |                       | 8         | 3.7     | mA    | $V_{IN} = 0V, V_{CC}$                 | 4,5    |

|                  | Halt Mode          | 5.5V            |                       | 8         | 3.7     | mA    | @ 16 MHz                              | 4,5    |

|                  |                    | 3.5V            |                       | 7.0       | 2.9     | mA    | Clock Divide by                       | 4,5    |

|                  |                    | 5.5V            |                       | 7.0       | 2.9     | mA    | 16 @ 16 MHz                           | 4,5    |

| I <sub>CC2</sub> | Standby Current    | 3.5V            |                       | 10        | 2       | μΑ    | $V_{IN} = 0V, V_{CC}$                 | 6,11   |

| 001              | Stop Mode          | 5.5V            |                       | 10        | 3       | μA    | $V_{IN} = 0V, V_{CC}$                 | 6,11   |

|                  |                    | 3.5V            |                       | 800       | 600     | μΑ    | $V_{IN} = 0V, V_{CC}$                 | 6,11,1 |

|                  |                    | 5.5V            |                       | 800       | 600     | μA    | $V_{IN} = 0V, V_{CC}$                 | 4      |

|                  |                    |                 |                       |           |         |       | $v_{\rm IN} = 0v, v_{\rm CC}$         | 6,11,1 |

|                  |                    |                 |                       |           |         |       |                                       | 4      |

| I <sub>ALL</sub> | Auto Latch         | 3.5V            | 0.7                   | 8         | 2.4     | μΑ    | 0V <v<sub>IN<v<sub>CC</v<sub></v<sub> | 9      |

|                  | Low Current        | 5.5V            | 1.4                   | 15        | 4.7     | μA    | 0V <v<sub>IN<v<sub>CC</v<sub></v<sub> | 9      |

| I <sub>ALH</sub> | Auto Latch         | 3.5V            | -0.6                  | -5        | -1.8    | μA    | 0V <v<sub>IN<v<sub>CC</v<sub></v<sub> | 9      |

| , <u> </u>       | High Current       | 5.5V            | -1                    | -8        | -3.8    | μA    | 0V <v<sub>IN<v<sub>CC</v<sub></v<sub> | 9      |

| T <sub>POR</sub> | Power On Reset     | 3.5V            | 3.0                   | 24        | 7       | ms    |                                       |        |

|                  |                    | 5.5V            | 2.0                   | 13        | 4       | ms    |                                       |        |

| VLV              | Auto Reset Voltage |                 | 2.3                   | 3.1       | 2.9     | V     |                                       | 1,7    |

### Notes:

- 1. Device does function down to the Auto Reset voltage.

- 2. GND=0V

- 3. The V<sub>CC</sub> voltage specification of 5.5V guarantees 5.0V  $\pm$  0.5V and the V<sub>CC</sub> voltage specification of 3.5V guarantees only 3.5V.

- 4. All outputs unloaded, I/O pins floating, inputs at rail.

- 5. CL1= CL2 = 22 pF

- 6. Same as note [4] except inputs at  $V_{\mbox{CC}.}$

- 7. Max. temperature is 70°C.

- 8. STD Mode (not Low EMI Mode)

- 9. Auto Latch (mask option) selected

- 10. For analog comparator inputs when analog comparators are enabled.

- 11. Clock must be forced Low, when XTAL1 is clock driven and XTAL2 is floating.

- 12. Typicals are at  $V_{CC}$  = 5.0V and  $V_{CC}$  = 3.5V

- 13. Z86E40 only

- 14. WDT running

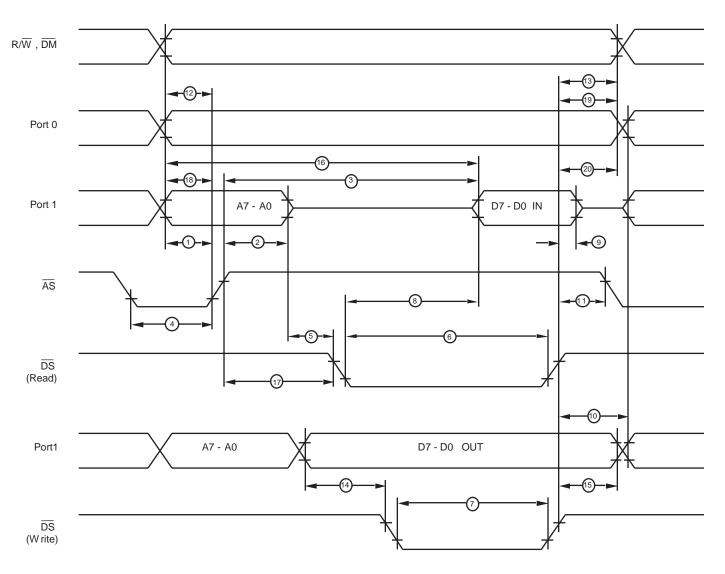

Figure 14. External I/O or Memory Read/Write Timing Z86E40 Only

# DC ELECTRICAL CHARACTERISTICS (Continued)

|    |           |                                                      | Note [3]        | ~   | T <sub>A</sub> = 0°C to 70°C<br>16 MHz |       |       |

|----|-----------|------------------------------------------------------|-----------------|-----|----------------------------------------|-------|-------|

| No | Symbol    | Parameter                                            | V <sub>CC</sub> | Min | Max                                    | Units | Notes |

| 1  | TdA(AS)   | Address Valid to AS Rise                             | 3.5V            | 25  |                                        | ns    | 2     |

|    | <b>、</b>  | Delay                                                | 5.5V            | 25  |                                        | ns    |       |

| 2  | TdAS(A)   | AS Rise to Address Float                             | 3.5V            | 35  |                                        | ns    | 2     |

|    |           | Delay                                                | 5.5V            | 35  |                                        | ns    |       |

| 3  | TdAS(DR)  | AS Rise to Read Data Req'd                           | 3.5V            |     | 180                                    | ns    | 1,2   |

|    |           | Valid                                                | 5.5V            |     | 180                                    | ns    |       |

| 4  | TwAS      | AS Low Width                                         | 3.5V            | 40  |                                        | ns    | 2     |

|    |           |                                                      | 5.5V            | 40  |                                        | ns    |       |

| 5  | TdAS(DS)  | Address Float to DS Fall                             | 3.5V            | 0   |                                        | ns    |       |

|    |           |                                                      | 5.5V            | 0   |                                        | ns    |       |

| 6  | TwDSR     | DS (Read) Low Width                                  | 3.5V            | 135 |                                        | ns    | 1,2   |

|    |           |                                                      | 5.5V            | 135 |                                        | ns    |       |

| 7  | TwDSW     | DS (Write) Low Width                                 | 3.5V            | 80  |                                        | ns    | 1,2   |

|    |           |                                                      | 5.5V            | 80  |                                        | ns    |       |

| 8  | TdDSR(DR) | DS Fall to Read Data Req'd                           | 3.5V            |     | 75                                     | ns    | 1,2   |

|    |           | Valid                                                | 5.5V            |     | 75                                     | ns    |       |

| 9  | ThDR(DS)  | Read Data to DS Rise Hold                            | 3.5V            | 0   |                                        | ns    | 2     |

|    |           | Time                                                 | 5.5V            | 0   |                                        | ns    |       |

| 10 | TdDS(A)   | DS Rise to Address Active                            | 3.5V            | 50  |                                        | ns    | 2     |

|    |           | Delay                                                | 5.5V            | 50  |                                        | ns    |       |

| 11 | TdDS(AS)  | DS Rise to AS Fall Delay                             | 3.5V            | 35  |                                        | ns    | 2     |

|    |           |                                                      | 5.5V            | 35  |                                        | ns    |       |

| 12 | TdR/W(AS) | $R/\overline{W}$ Valid to $\overline{AS}$ Rise Delay | 3.5V            | 25  |                                        | ns    | 2     |

|    |           |                                                      | 5.5V            | 25  |                                        | ns    |       |

| 13 | TdDS(R/W) | DS Rise to R/W Not Valid                             | 3.5V            | 35  |                                        | ns    | 2     |

|    |           |                                                      | 5.5V            | 35  |                                        | ns    |       |

| 14 | TdDW(DSW) | Write Data Valid to DS Fall                          | 3.5V            | 55  | 25                                     | ns    | 2     |

|    |           | (Write) Delay                                        | 5.5V            | 55  | 25                                     | ns    |       |

| 15 | TdDS(DW)  | DS Rise to Write Data Not                            | 3.5V            | 35  |                                        | ns    | 2     |

|    |           | Valid Delay                                          | 5.5V            | 35  |                                        | ns    |       |

| 16 | TdA(DR)   | Address Valid to Read Data                           | 3.5V            |     | 230                                    | ns    | 1,2   |

|    |           | Req'd Valid                                          | 5.5V            |     | 230                                    | ns    |       |

| 17 | TdAS(DS)  | AS Rise to DS Fall Delay                             | 3.5V            | 45  |                                        | ns    | 2     |

|    |           |                                                      | 5.5V            | 45  |                                        | ns    |       |

| 18 | TdDM(AS)  | DM Valid to AS Fall Delay                            | 3.5V            | 30  |                                        | ns    | 2     |

|    |           |                                                      | 5.5V            | 30  |                                        | ns    |       |

| 20 | ThDS(AS)  | DS Valid to Address Valid                            | 3.5V            | 35  |                                        | ns    |       |

|    |           | Hold Time                                            | 5.5V            | 35  |                                        | ns    |       |

### Notes:

1. When using extended memory timing, add 2 TpC.

2. Timing numbers given are for minimum TpC.

3. The V<sub>CC</sub> voltage specification of 5.5V guarantees 5.0V  $\pm$ 0.5V and the V<sub>CC</sub> voltage specification of 3.5V guarantees only 3.5V

### Standard Test Load

All timing references use 0.7 V<sub>CC</sub> for a logic 1 and 0.2 V<sub>CC</sub> for a logic 0. For Standard Mode (not Low-EMI Mode for outputs) with SMR D1 = 0, D0 = 0. Zilog

Zilog

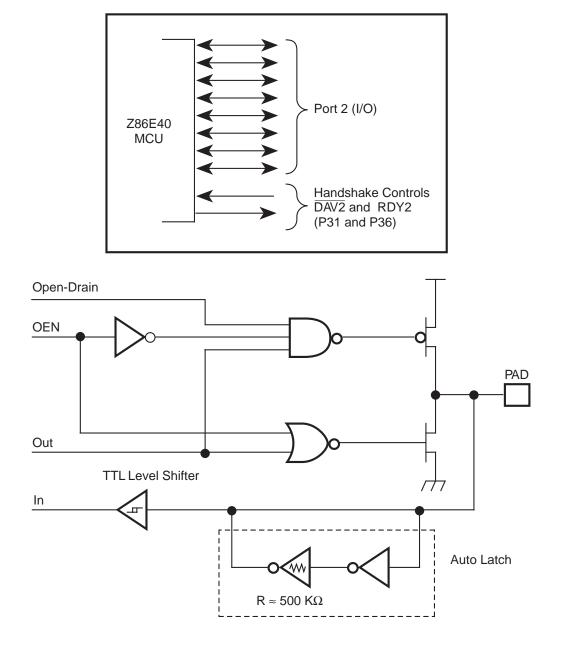

**Port 2** (P27–P20). Port 2 is an 8-bit, bidirectional, CMOScompatible I/O port. These eight I/O lines can be configured under software control as an input or output, independently. All input buffers are Schmitt-triggered. Bits programmed as outputs can be globally programmed as either push-pull or open-drain. Low EMI output buffers can be globally programmed by the software. When used as an I/O port, Port 2 can be placed under handshake control.

In Handshake Mode, Port 3 lines P31 and P36 are used as handshake control lines. The handshake direction is determined by the configuration (input or output) assigned to bit 7 of Port 2 (Figure 20).

Figure 20. Port 2 Configuration

# FUNCTIONAL DESCRIPTION

The MCU incorporates the following special functions to enhance the standard Z8 architecture to provide the user with increased design flexibility.

**RESET.** The device is reset in one of three ways:

- 1. Power-On Reset

- 2. Watch-Dog Timer

- 3. STOP-Mode Recovery Source

**Note:** Having the Auto Power-On Reset circuitry built-in, the MCU does not need to be connected to an external power-on reset circuit. The reset time is 5 ms (typical). The MCU does not reinitialize WDTMR, SMR, P2M, and P3M registers to their reset values on a STOP-Mode Recovery operation.

**Note:** The device  $V_{CC}$  must rise up to the operating  $V_{CC}$  specification before the TPOR expires.

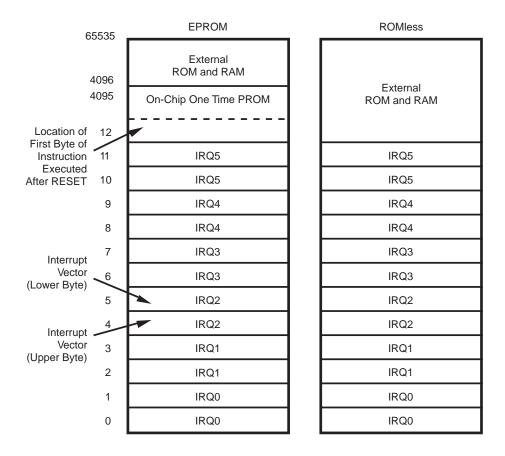

**Program Memory.** The MCU can address up to 4 KB of Internal Program Memory (Figure 22). The first 12 bytes of program memory are reserved for the interrupt vectors. These locations contain six 16-bit vectors that correspond to the six available interrupts. For EPROM mode, byte 12 (000CH) to address 4095 (0FFFH) consists of programmable EPROM. After reset, the program counter points at the address 000CH, which is the starting address of the user program.

In ROMless mode, the Z86E40 can address up to 64 KB of External Program Memory. The ROM/ROMless option is only available on the 44-pin devices.

### Figure 22. Program Memory Map (ROMIess Z86E40 Only)

**EPROM Protect.** When in ROM Protect Mode, and executing out of External Program Memory, instructions LDC, LDCI, LDE, and LDEI cannot read Internal Program Memory.

When in ROM Protect Mode and executing out of Internal Program Memory, instructions LDC, LDCI, LDE, and LDEI can read Internal Program Memory.

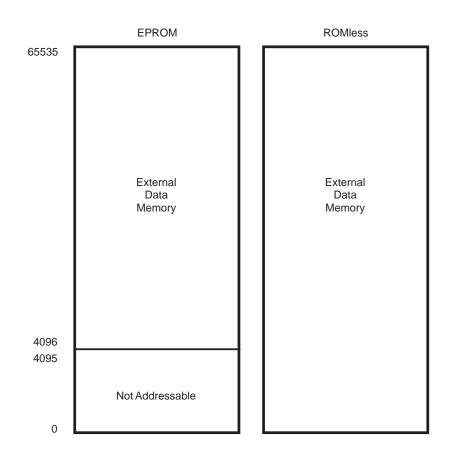

**Data Memory** (DM). In EPROM Mode, the Z86E40 can address up to 60 KB of external data memory beginning at location 4096. In ROMIess mode, the Z86E40 can address up to 64 KB of data memory. External data memory may be included with, or separated from, the external program memory space. DM, an optional I/O function that can be

programmed to appear on pin P34, is used to distinguish between data and program memory space (Figure 23). The state of the  $\overline{\text{DM}}$  signal is controlled by the type of instruction being executed. An LDC opcode references PROGRAM ( $\overline{\text{DM}}$  inactive) memory, and an LDE instruction references data ( $\overline{\text{DM}}$  active Low) memory.

Figure 23. Data Memory Map

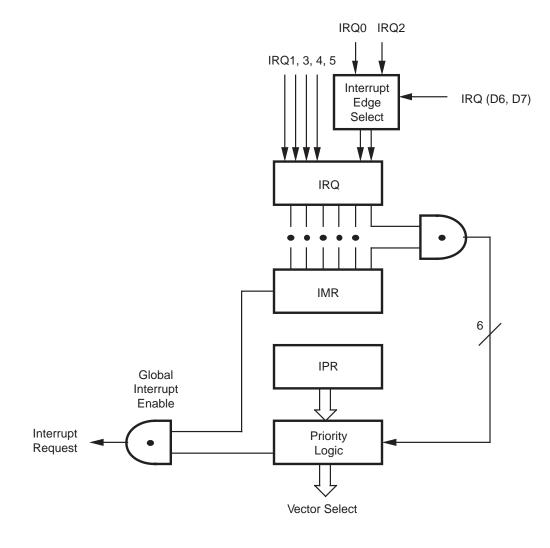

**Interrupts.** The MCU has six different interrupts from six different sources. The interrupts are maskable and prioritized (Figure 28). The six sources are divided as follows: four sources are claimed by Port 3 lines P33–P30) and two

in counter/timers. The Interrupt Mask Register globally or individually enables or disables the six interrupt requests (Table 10).

| Table 10. | Interrupt Types, | Sources, | and Vectors |

|-----------|------------------|----------|-------------|

|-----------|------------------|----------|-------------|

| Name | Source                      | Vector Location | Comments                                      |

|------|-----------------------------|-----------------|-----------------------------------------------|

| IRQ0 | DAV0, IRQ0                  | 0, 1            | External (P32), Rising/Falling Edge Triggered |

| IRQ1 | IRQ1                        | 2, 3            | External (P33), Falling Edge Triggered        |

| IRQ2 | DAV2, IRQ2, T <sub>IN</sub> | 4, 5            | External (P31), Rising/Falling Edge Triggered |

| IRQ3 | IRQ3                        | 6, 7            | External (P30), Falling Edge Triggered        |

| IRQ4 | Т0                          | 8, 9            | Internal                                      |

| IRQ5 | TI                          | 10, 11          | Internal                                      |

**Power-On Reset (POR).** A timer circuit clocked by a dedicated on-board RC oscillator is used for the Power-On Reset (POR) timer function. The POR timer allows  $V_{CC}$  and the oscillator circuit to stabilize before instruction execution begins.

The POR timer circuit is a one-shot timer triggered by one of three conditions:

- 1. Power fail to Power OK status

- 2. Stop-Mode Recovery (if D5 of SMR=0)

- 3. WDT time-out

The POR time is a nominal 5 ms. Bit 5 of the STOP mode Register (SMR) determines whether the POR timer is bypassed after STOP-Mode Recovery (typical for an external clock and RC/LC oscillators with fast start up times).

**HALT.** Turns off the internal CPU clock, but not the XTAL oscillation. The counter/timers and external interrupt IRQ0, IRQ1, and IRQ2 remain active. The device is recovered by interrupts, either externally or internally generated. An interrupt request must be executed (enabled) to exit HALT Mode. After the interrupt service routine, the program continues from the instruction after the HALT.

In order to enter STOP or HALT Mode, it is necessary to first flush the instruction pipeline to avoid suspending execution in mid-instruction. To do this, the user must execute a NOP (Opcode=FFH) immediately before the appropriate sleep instruction, that is:

| FF | NOP  | ; clear the pipeline |

|----|------|----------------------|

| 6F | STOP | ; enter STOP Mode    |

|    | or   |                      |

| FF | NOP  | ; clear the pipeline |

| 7F | HALT | ; enter HALT Mode    |

**STOP.** This instruction turns off the internal clock and external crystal oscillation and reduces the standby current to 10 microamperes or less. STOP Mode is terminated by one of the following resets: either by WDT time-out, POR, a Stop-Mode Recovery Source, which is defined by the SMR register or external reset. This causes the processor to restart the application program at address 000CH.

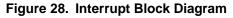

**Port Configuration Register (PCON).** The PCON register configures the ports individually; comparator output on Port 3, open-drain on Port 0 and Port 1, low EMI on Ports 0, 1, 2 and 3, and low EMI oscillator. The PCON register is located in the expanded register file at Bank F, location 00 (Figure 30).

**Comparator Output Port 3** (D0). Bit 0 controls the comparator output in Port 3. A "1" in this location brings the comparator outputs to P34 and P37, and a "0" releases the Port to its standard I/O configuration. The default value is 0.

**Port 1 Open-Drain** (D1). Port 1 can be configured as an open-drain by resetting this bit (D1=0) or configured as push-pull active by setting this bit (D1=1). The default value is 1.

**Port 0 Open-Drain** (D2). Port 0 can be configured as an open-drain by resetting this bit (D2=0) or configured as push-pull active by setting this bit (D2=1). The default value is 1.

**Low EMI Port 0** (D3). Port 0 can be configured as a Low EMI Port by resetting this bit (D3=0) or configured as a Standard Port by setting this bit (D3=1). The default value is 1.

**Low EMI Port 1** (D4). Port 1 can be configured as a Low EMI Port by resetting this bit (D4=0) or configured as a Standard Port by setting this bit (D4=1). The default value is 1. **Note:** The emulator does not support Port 1 low EMI mode and must be set D4 = 1.

**Low EMI Port 2** (D5). Port 2 can be configured as a Low EMI Port by resetting this bit (D5=0) or configured as a Standard Port by setting this bit (D5=1). The default value is 1.

**Low EMI Port 3** (D6). Port 3 can be configured as a Low EMI Port by resetting this bit (D6=0) or configured as a Standard Port by setting this bit (D6=1). The default value is 1.

**Low EMI OSC** (D7). This bit of the PCON Register controls the low EMI noise oscillator. A "1" in this location configures the oscillator with standard drive. While a "0" configures the oscillator with low noise drive, however, it does not affect the relationship of SCLK and XTAL. The low EMI mode will reduce the drive of the oscillator (OSC). The default value is 1. **Note:** 4 MHz is the maximum external clock frequency when running in the low EMI oscillator mode.

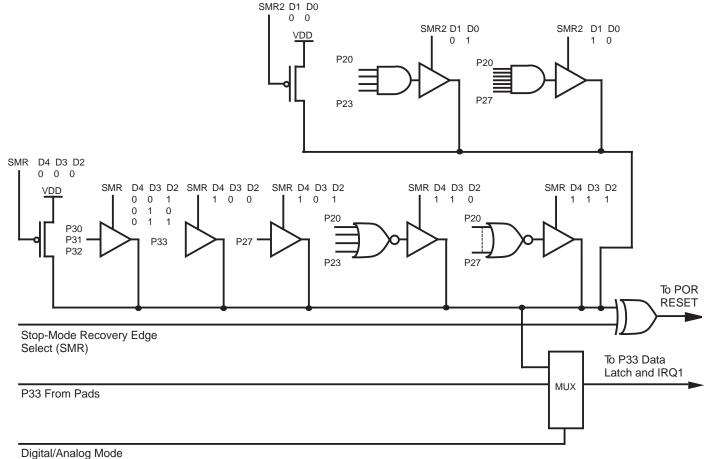

**Stop-Mode Recovery Register** (SMR). This register selects the clock divide value and determines the mode of Stop-Mode Recovery (Figure 31). All bits are Write Only except bit 7 which is a Read Only. Bit 7 is a flag bit that is hardware set on the condition of STOP Recovery and reset by a power-on cycle. Bit 6 controls whether a low or high level is required from the recovery source. Bit 5 controls the reset delay after recovery. Bits 2, 3, and 4 of the SMR register specify the Stop-Mode Recovery Source. The SMR is located in Bank F of the Expanded Register Group at address 0BH.

**SCLK/TCLK Divide-by-16 Select** (D0). This bit of the SMR controls a divide-by-16 prescaler of SCLK/TCLK. The purpose of this control is to selectively reduce device power consumption during normal processor execution (SCLK control) and/or HALT mode (where TCLK sources counter/timers and interrupt logic).

**External Clock Divide-by-Two** (D1). This bit can eliminate the oscillator divide-by-two circuitry. When this bit is 0, the System Clock (SCLK) and Timer Clock (TCLK) are equal to the external clock frequency divided by two. The SCLK/TCLK is equal to the external clock frequency when this bit is set (D1=1). Using this bit together with D7 of

PCON further helps lower EMI (i.e., D7 (PCON) = 0, D1 (SMR) = 1). The default setting is zero.

**STOP-Mode Recovery Source** (D2, D3, and D4). These three bits of the SMR register specify the wake up source of the STOP-Mode Recovery (Figure 32). Table 12 shows the SMR source selected with the setting of D2 to D4. P33–P31 cannot be used to wake up from STOP mode when programmed as analog inputs. When the STOP-Mode Recovery sources are selected in this register then SMR2 register bits D0, D1 must be set to zero.

**Note:** If the Port2 pin is configured as an output, this output level will be read by the SMR circuitry.

Select (P3M)

Figure 32. Stop-Mode Recovery Source

|    |    | -  | -                                   |

|----|----|----|-------------------------------------|

| D4 | D3 | D2 | SMR Source selection                |

| 0  | 0  | 0  | POR recovery only                   |

| 0  | 0  | 1  | P30 transition                      |

| 0  | 1  | 0  | P31 transition (Not in analog mode) |

| 0  | 1  | 1  | P32 transition (Not in analog mode) |

| 1  | 0  | 0  | P33 transition (Not in analog mode) |

| 1  | 0  | 1  | P27 transition                      |

| 1  | 1  | 0  | Logical NOR of Port 2 bits 0-3      |

| 1  | 1  | 1  | Logical NOR of Port 2 bits 0-7      |

|    |    |    |                                     |

Table 12. Stop-Mode Recovery Source

**Stop-Mode Recovery Delay Select** (D5). The 5 ms RE-SET delay after Stop-Mode Recovery is disabled by programming this bit to a zero. A "1" in this bit will cause a 5 ms RESET delay after Stop-Mode Recovery. The default condition of this bit is 1. If the fast wake up mode is selected, the Stop-Mode Recovery source needs to be kept active for at least 5TpC.

**Stop-Mode Recovery Level Select** (D6). A "1" in this bit defines that a high level on any one of the recovery sources wakes the MCU from STOP Mode. A 0 defines low level recovery. The default value is 0.

**Cold or Warm Start** (D7). This bit is set by the device upon entering STOP Mode. A "0" in this bit indicates that the device has been reset by POR (cold). A "1" in this bit indicates the device was awakened by a SMR source (warm).

**Stop-Mode Recovery Register 2 (SMR2)**. This register contains additional Stop-Mode Recovery sources. When the Stop-Mode Recovery sources are selected in this register then SMR Register. Bits D2, D3, and D4 must be 0.

| SMR:10 |    | Operation                          |

|--------|----|------------------------------------|

| D1     | D0 | Description of Action              |

| 0      | 0  | POR and/or external reset recovery |

| 0      | 1  | Logical AND of P20 through P23     |

| 1      | 0  | Logical AND of P20 through P27     |

**Watch-Dog Timer Mode Register** (WDTMR). The WDT is a retriggerable one-shot timer that resets the Z8 if it reaches its terminal count. The WDT is disabled after Power-On Reset and initially enabled by executing the WDT instruction and refreshed on subsequent executions of the WDT instruction. The WDT is driven either by an on-board RC oscillator or an external oscillator from XTAL1 pin. The

POR clock source is selected with bit 4 of the WDT register.

**Note:** Execution of the WDT instruction affects the Z (Zero), S (Sign), and V (Overflow) flags.

**WDT Time-Out Period** (D0 and D1). Bits 0 and 1 control a tap circuit that determines the time-out periods that can be obtained (Table 13). The default value of D0 and D1 are 1 and 0, respectively.

| Table 13. Time-out Period of WD | Table 13. | Time-out | Period | of WD1 |

|---------------------------------|-----------|----------|--------|--------|

|---------------------------------|-----------|----------|--------|--------|

| D1 | D0 | Time-out of<br>the Internal<br>RC OSC | Time-out of<br>the System<br>Clock |

|----|----|---------------------------------------|------------------------------------|

| 0  | 0  | 5 ms                                  | 128 SCLK                           |

| 0  | 1  | 10 ms*                                | 256 SCLK*                          |

| 1  | 0  | 20 ms                                 | 512 SCLK                           |

| 1  | 1  | 80 ms                                 | 2048 SCLK                          |

Notes:

\*The default setting is 10 ms.

**WDT During HALT Mode** (D2). This bit determines whether or not the WDT is active during HALT Mode. A "1" indicates that the WDT is active during HALT. A "0" disables the WDT in HALT Mode. The default value is "1".

**WDT During STOP Mode** (D3). This bit determines whether or not the WDT is active during STOP mode. A "1" indicates active during STOP. A "0" disables the WDT during STOP Mode. This is applicable only when the WDT clock source is the internal RC oscillator.

**Clock Source For WDT** (D4). This bit determines which oscillator source is used to clock the internal POR and WDT counter chain. If the bit is a 1, the internal RC oscillator is bypassed and the POR and WDT clock source is driven from the external pin, XTAL1, and the WDT is stopped in STOP Mode. The default configuration of this bit is 0, which selects the RC oscillator.

**Permanent WDT.** When this feature is enabled, the WDT is enabled after reset and will operate in Run and Halt Mode. The control bits in the WDTMR do not affect the WDT operation. If the clock source of the WDT is the internal RC oscillator, then the WDT will run in STOP mode. If the clock source of the WDT is the XTAL1 pin, then the WDT will not run in STOP mode.

Note: WDT time-out in STOP Mode will not reset SMR,SMR2,PCON, WDTMR, P2M, P3M, Ports 2 & 3 Data Registers.

WDTMR Register Accessibility. The WDTMR register is accessible only during the first 60 internal system clock

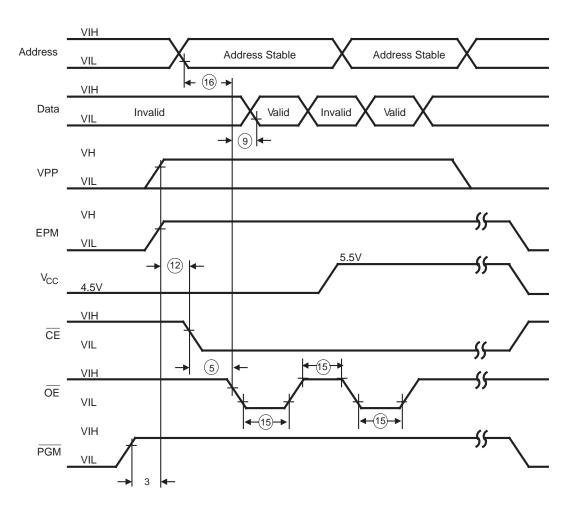

### Table 14. EPROM Programming Table

| Programming<br>Modes | V <sub>PP</sub> | EPM            | CE              | ŌĒ              | PGM             | ADDR | DATA | V <sub>CC</sub> * |

|----------------------|-----------------|----------------|-----------------|-----------------|-----------------|------|------|-------------------|

| EPROM READ1          | Х               | V <sub>H</sub> | V <sub>IL</sub> | V <sub>IL</sub> | V <sub>IH</sub> | ADDR | Out  | 4.5V†             |

| EPROM READ2          | Х               | V <sub>H</sub> | V <sub>IL</sub> | V <sub>IL</sub> | V <sub>IH</sub> | ADDR | Out  | 5.5V†             |

| PROGRAM              | V <sub>H</sub>  | V <sub>H</sub> | V <sub>IL</sub> | $V_{IH}$        | V <sub>IL</sub> | ADDR | In   | 6.4V              |

| PROGRAM<br>VERIFY    | V <sub>H</sub>  | V <sub>H</sub> | V <sub>IL</sub> | V <sub>IL</sub> | V <sub>IH</sub> | ADDR | Out  | 6.0V              |

| OPTION BIT PGM       | V <sub>H</sub>  | V <sub>H</sub> | V <sub>IL</sub> | V <sub>IH</sub> | V <sub>IL</sub> | 63   | IN   | 6.4V              |

| OPTION BIT READ      | Х               | V <sub>H</sub> | V <sub>IL</sub> | V <sub>IL</sub> | V <sub>IH</sub> | 63   | OUT  | 6.0V              |

### Notes:

$V_{H} = 13.0 \text{ V} \pm 0.1 \text{ V}$

$V_{\mbox{\scriptsize IH}}$  = As per specific Z8 DC specification

VIL= As per specific Z8 DC specification

X=Not used, but must be set to  $V_H$ ,  $V_{IH}$ , or  $V_{IL}$  level.

NU = Not used, but must be set to either  $V_{IH}$  or  $V_{IL}$  level.

$I_{PP}$  during programming = 40 mA maximum.

$I_{CC}$  during programming, verify, or read = 40 mA maximum.

$^{*}V_{CC}$  has a tolerance of  $\pm 0.25V$ .

† Zilog recommends an EPROM read at V<sub>CC</sub> = 4.5 V and 5.5 V to

ensure proper device operations during the  $V_{\mbox{CC}}$  after programming,

but  $V_{CC} = 5.0$  V is acceptable.

| Parameters | Name                                                     | Min  | Max  | Units |

|------------|----------------------------------------------------------|------|------|-------|

| 1          | Address Setup Time                                       | 2    |      | μs    |

| 2          | Data Setup Time                                          | 2    |      | μs    |

| 3          | V <sub>PP</sub> Setup                                    | 2    |      | μs    |

| 4          | V <sub>CC</sub> Setup Time                               | 2    |      | μs    |

| 5          | Chip Enable Setup Time                                   | 2    |      | μs    |

| 6          | Program Pulse Width                                      | 0.95 | 1.05 | ms    |

| 7          | Data Hold Time                                           | 2    |      | μs    |

| 8          | OE Setup Time                                            | 2    |      | μs    |

| 9          | Data Access Time                                         | 200  |      | ns    |

| 10         | Data Output Float Time                                   |      | 100  | ns    |

| 11         | Overprogram Pulse<br>Width/Option Program<br>Pulse Width | 2.85 |      | ms    |

| 12         | EPM Setup Time                                           | 2    |      | μs    |

| 13         | PGM Setup Time                                           | 2    |      | μs    |

| 14         | Address to OE Setup Time                                 | 2    |      | μs    |

| 15         | OE Width                                                 | 250  |      | ns    |

| 16         | Address to OE Low                                        | 125  |      | ns    |

### Table 15. EPROM Programming Timing

Figure 36. EPROM Read Mode Timing Diagram

## Z86E40 TIMING DIAGRAMS (Continued)

Figure 38. Z86E40 Z8 OTP Programming Adapter For use with Standard EPROM Programmers

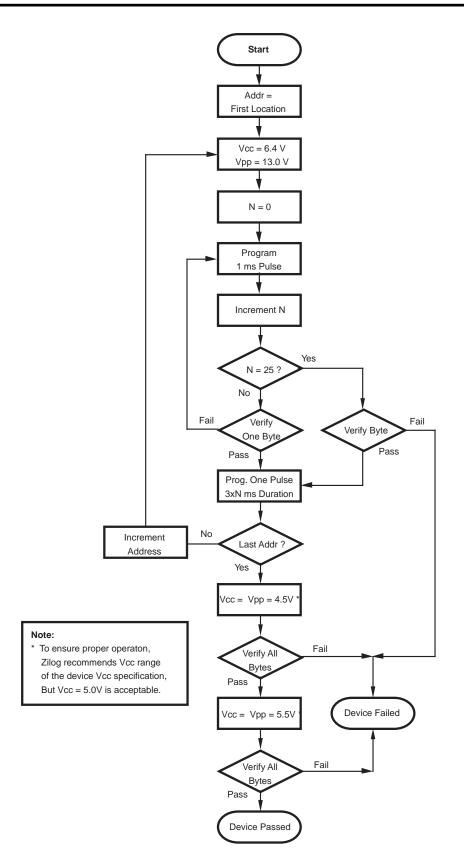

Figure 40. Z86E40 Programming Algorithm

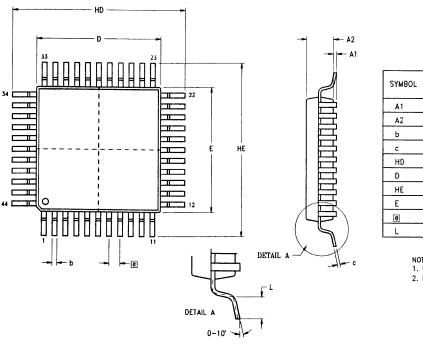

Figure 62. 44-Pin PLCC Package Diagram

D2

e

15.24

1.27 TYP

16.00

.600

| SYMBOL | MILLI    | METER | INCH      |      |  |

|--------|----------|-------|-----------|------|--|

| STMDOL | MIN      | МАХ   | MIN       | MAX  |  |

| A1     | 0.05     | 0.25  | .002      | .010 |  |

| A2     | 2.00     | 2.25  | .078      | .089 |  |

| b      | 0.25     | 0.45  | .010      | .018 |  |

| с      | 0.13     | 0.20  | .005      | .008 |  |

| HD     | 13.70    | 14.15 | .539      | .557 |  |

| D      | 9.90     | 10.10 | .390      | .398 |  |

| HE     | 13.70    | 14.15 | .539      | .557 |  |

| E      | 9.90     | 10.10 | .390      | .398 |  |

| θ      | 0.80 TYP |       | .0315 TYP |      |  |

| L      | 0.60     | 1.20  | .024      | .047 |  |

.630

.050 TYP

Figure 63. 44-Pin LQFP Package Diagram

NOTES: 1. CONTROLLING DIMENSIONS : MILLIMETER 2. LEAD COPLANARITY : MAX .10 .004"

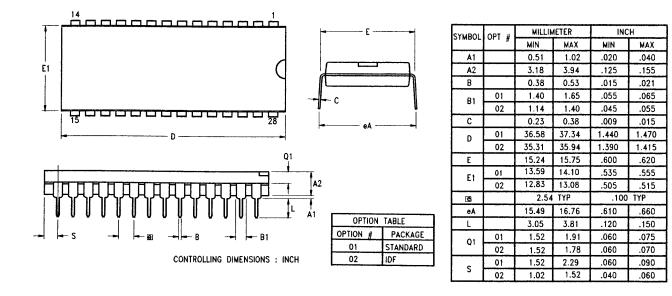

Figure 64. 28-Pin DIP Package Diagram

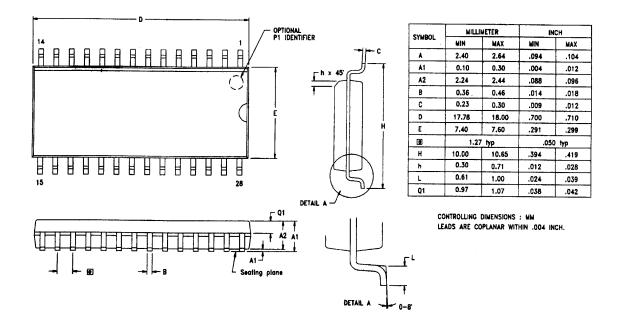

Figure 65. 28-Pin SOIC Package Diagram

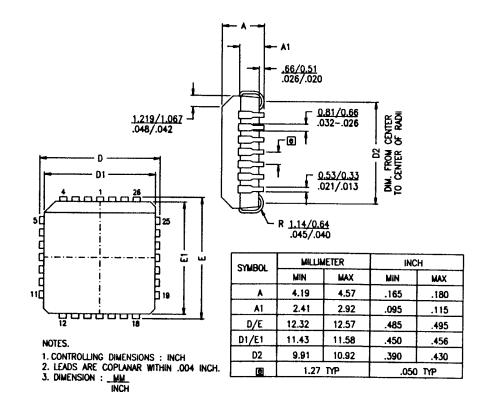

Figure 66. 28-Pin PLCC Package Diagram