Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                               |

|----------------------------|-------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                      |

| Core Processor             | F <sup>2</sup> MC-8FX                                                         |

| Core Size                  | 8-Bit                                                                         |

| Speed                      | 16MHz                                                                         |

| Connectivity               | LINbus, LPC, SIO, UART/USART                                                  |

| Peripherals                | LVD, POR, PWM, WDT                                                            |

| Number of I/O              | 17                                                                            |

| Program Memory Size        | 8KB (8K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                         |

| EEPROM Size                | -                                                                             |

| RAM Size                   | 496 x 8                                                                       |

| Voltage - Supply (Vcc/Vdd) | 2.4V ~ 5.5V                                                                   |

| Data Converters            | A/D 6x8/10b                                                                   |

| Oscillator Type            | External                                                                      |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                             |

| Mounting Type              | Surface Mount                                                                 |

| Package / Case             | 20-SOIC (0.295", 7.50mm Width)                                                |

| Supplier Device Package    | 20-SOP                                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/mb95f203kpf-g-sne2 |

| Part number Parameter | MB95<br>F204H                                   | MB95<br>F203H                                                                                                                                                                                                                                                                                                                                                                       | MB95<br>F202H | MB95<br>F204K | MB95<br>F203K | MB95<br>F202K | MB95<br>F214H | MB95<br>F213H | MB95<br>F212H | MB95<br>F214K | MB95<br>F213K | MB95<br>F212K |

|-----------------------|-------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|---------------|---------------|---------------|---------------|---------------|---------------|---------------|---------------|---------------|

| Watch prescaler       | Eight diff                                      | ight different time intervals can be selected.                                                                                                                                                                                                                                                                                                                                      |               |               |               |               |               |               |               |               |               |               |

| Flash memory          | write/era It has a f Number Data rete For write | It supports automatic programming, Embedded Algorithm, write/erase/erase-suspend/erase-resume commands.  It has a flag indicating the completion of the operation of Embedded Algorithm. Number of write/erase cycles: 100000 Data retention time: 20 years For write/erase, external Vpp(+10 V) input is required. Flash Security Feature for protecting the contents of the flash |               |               |               |               |               |               |               |               |               |               |

| Standby mode          | Sleep me                                        | ode, stop                                                                                                                                                                                                                                                                                                                                                                           | mode, wa      | atch mode     | e, timebas    | se timer m    | node          |               |               |               |               |               |

| Package               |                                                 | SDIP-24 DIP-8 SOP-20 SOP-8                                                                                                                                                                                                                                                                                                                                                          |               |               |               |               |               |               |               |               |               |               |

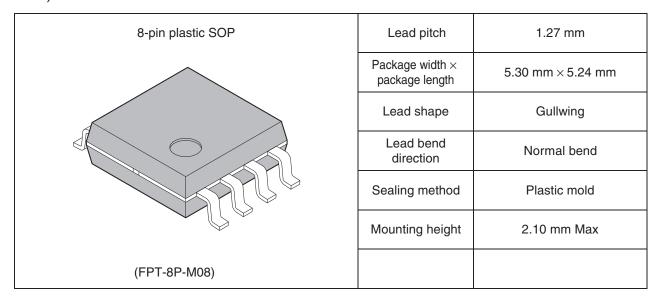

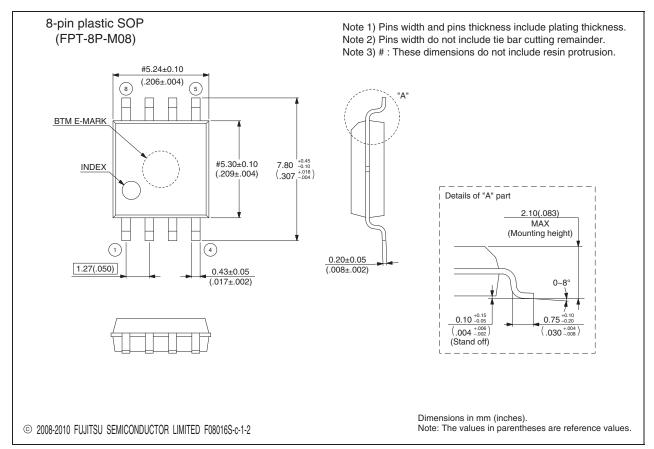

# 2. Packages and Corresponding Products

| Part number Package    | MB95<br>F204H | MB95<br>F203H | MB95<br>F202H | MB95<br>F204K | MB95<br>F203K | MB95<br>F202K | MB95<br>F214H | MB95<br>F213H | MB95<br>F212H | MB95<br>F214K | MB95<br>F213K | MB95<br>F212K |

|------------------------|---------------|---------------|---------------|---------------|---------------|---------------|---------------|---------------|---------------|---------------|---------------|---------------|

| 24-pin plastic<br>SDIP | 0             | 0             | 0             | 0             | 0             | 0             | Х             | X             | X             | Х             | Х             | Х             |

| 20-pin plastic<br>SOP  | 0             | 0             | 0             | 0             | 0             | 0             | Х             | Х             | Х             | Х             | Х             | Х             |

| 8-pin plastic DIP      | Х             | Х             | Х             | Х             | Х             | Х             | 0             | 0             | 0             | 0             | 0             | 0             |

| 8-pin plastic SOP      | Х             | Х             | Х             | Х             | Х             | Х             | 0             | 0             | 0             | 0             | 0             | 0             |

O: Available X: Unavailable

## 3. Differences Among Products And Notes On Product Selection

#### **Current consumption**

When using the on-chip debug function, take account of the current consumption of flash erase/program.

For details of current consumption, see "18. Electrical Characteristics".

#### **Package**

For details of information on each package, see "2.Packages and Corresponding Products" and "22.Package Dimensions".

#### Operating voltage

The operating voltage varies, depending on whether the on-chip debug function is used or not.

For details of the operating voltage, see "18. Electrical Characteristics".

## On-chip debug function

The on-chip debug function requires that  $V_{CC}$ ,  $V_{SS}$  and 1 serial-wire be connected to an evaluation tool. In addition, if the flash memory data has to be updated, the RSTX/PF2 pin must also be connected to the same evaluation tool.

# 6. Pin Description (MB95200H Series 20 pins)

| Pin no. | Pin name                         | I/O circuit<br>type* | Function                                                                                                                                                                                                                                                                                                               |

|---------|----------------------------------|----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | PF0/X0                           | В                    | General-purpose I/O port This pin is also used as the main clock input oscillation pin.                                                                                                                                                                                                                                |

| 2       | PF1/X1                           | В                    | General-purpose I/O port This pin is also used as the main clock input/output oscillation pin.                                                                                                                                                                                                                         |

| 3       | V <sub>SS</sub>                  | _                    | Power supply pin (GND)                                                                                                                                                                                                                                                                                                 |

| 4       | PG2/X1A                          | С                    | General-purpose I/O port This pin is also used as the subclock input/output oscillation pin.                                                                                                                                                                                                                           |

| 5       | PG1/X0A                          | С                    | General-purpose I/O port This pin is also used as the subclock input oscillation pin.                                                                                                                                                                                                                                  |

| 6       | V <sub>CC</sub>                  | _                    | Power supply pin                                                                                                                                                                                                                                                                                                       |

| 7       | С                                | _                    | Capacitor connection pin                                                                                                                                                                                                                                                                                               |

| 8       | PF2/RSTX                         | Α                    | General-purpose I/O port This pin is also used as a reset pin. This pin is a dedicated reset pin in MB95F204H/F203H/F202H.                                                                                                                                                                                             |

| 9       | P62/TO10                         | D                    | General-purpose I/O port High-current port This pin is also used as the 8/16-bit composite timer ch. 1 output.                                                                                                                                                                                                         |

| 10      | P63/TO11                         | D                    | General-purpose I/O port<br>High-current port<br>This pin is also used as the 8/16-bit composite timer ch. 1 output.                                                                                                                                                                                                   |

| 11      | P64/EC1                          | D                    | General-purpose I/O port This pin is also used as the 8/16-bit composite timer ch. 1 clock input.                                                                                                                                                                                                                      |

| 12      | P00/AN00                         | E                    | General-purpose I/O port This pin is also used as the A/D converter analog input.                                                                                                                                                                                                                                      |

| 13      | P01/AN01                         | E                    | General-purpose I/O port This pin is also used as the A/D converter analog input.                                                                                                                                                                                                                                      |

| 14      | P02/INT02/AN02/SCK               | E                    | General-purpose I/O port This pin is also used as the external interrupt input. This pin is also used as the A/D converter analog input. This pin is also used as the LIN-UART clock I/O.                                                                                                                              |

| 15      | P03/INT03/AN03/SOT               | E                    | General-purpose I/O port This pin is also used as the external interrupt input. This pin is also used as the A/D converter analog input. This pin is also used as the LIN-UART data output.                                                                                                                            |

| 16      | P04/INT04/AN04/SIN<br>/HCLK1/EC0 | F                    | General-purpose I/O port This pin is also used as the external interrupt input. This pin is also used as the A/D converter analog input. This pin is also used as the LIN-UART data input. This pin is also used as the external clock input. This pin is also used as the 8/16-bit composite timer ch. 0 clock input. |

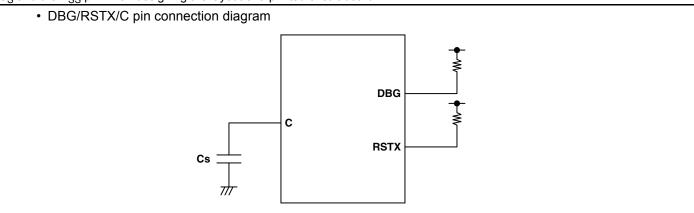

### C pin

Use a ceramic capacitor or a capacitor with equivalent frequency characteristics. The bypass capacitor for the  $V_{CC}$  pin must have a capacitance larger than  $C_S$ . For the connection to a smoothing capacitor  $C_S$ , see the diagram below. To prevent the device from unintentionally entering an unknown mode due to noise, minimize the distance between the C pin and  $C_S$  and the distance between  $C_S$  and the  $V_{SS}$  pin when designing the layout of a printed circuit board.

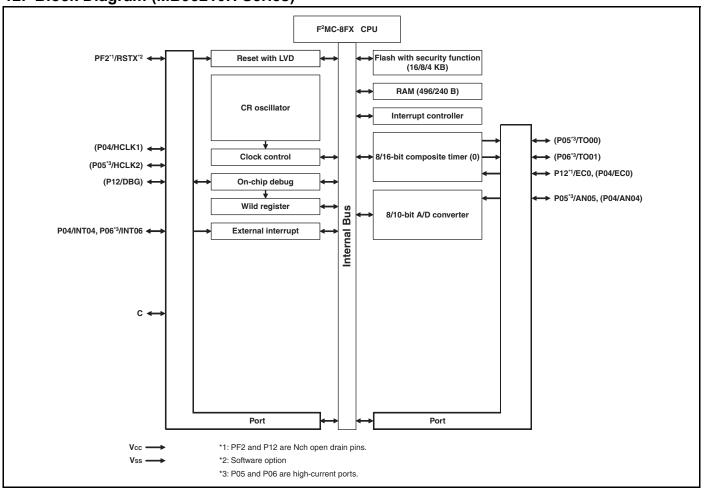

## 12. Block Diagram (MB95210H Series)

# 14. I/O Map (MB95200H Series)

| Address                                   | Register abbreviation | Register name                                               | R/W | Initial value         |

|-------------------------------------------|-----------------------|-------------------------------------------------------------|-----|-----------------------|

| 0000 <sub>H</sub>                         | PDR0                  | Port 0 data register                                        | R/W | 00000000 <sub>B</sub> |

| 0001 <sub>H</sub>                         | DDR0                  | Port 0 direction register                                   |     | 00000000 <sub>B</sub> |

| 0002 <sub>H</sub>                         | PDR1                  | Port 1 data register                                        | R/W | 00000000 <sub>B</sub> |

| 0003 <sub>H</sub>                         | DDR1                  | Port 1 direction register                                   | R/W | 00000000 <sub>B</sub> |

| 0004 <sub>H</sub>                         | _                     | (Disabled)                                                  | _   | _                     |

| 0005 <sub>H</sub>                         | WATR                  | Oscillation stabilization wait time setting register        | R/W | 11111111 <sub>B</sub> |

| 0006 <sub>H</sub>                         | _                     | (Disabled)                                                  | _   | _                     |

| 0007 <sub>H</sub>                         | SYCC                  | System clock control register                               | R/W | XXXXXX11 <sub>B</sub> |

| 0008 <sub>H</sub>                         | STBC                  | Standby control register                                    | R/W | 00000XXX <sub>B</sub> |

| 0009 <sub>H</sub>                         | RSRR                  | Reset source register                                       | R   | XXXXXXXX              |

| 000A <sub>H</sub>                         | TBTC                  | Timebase timer control register                             | R/W | 00000000 <sub>B</sub> |

| 000B <sub>H</sub>                         | WPCR                  | Watch prescaler control register                            | R/W | 00000000 <sub>B</sub> |

| 000C <sub>H</sub>                         | WDTC                  | Watchdog timer control register                             | R/W | 00000000 <sub>B</sub> |

| 000D <sub>H</sub>                         | SYCC2                 | System clock control register 2                             |     | XX100011 <sub>B</sub> |

| 000E <sub>H</sub> to<br>0015 <sub>H</sub> | _                     | (Disabled)                                                  |     | _                     |

| 0016 <sub>H</sub>                         | PDR6                  | Port 6 data register                                        |     | 00000000 <sub>B</sub> |

| 0017 <sub>H</sub>                         | DDR6                  | Port 6 direction register                                   | R/W | 00000000 <sub>B</sub> |

| 0018 <sub>H</sub> to<br>0027 <sub>H</sub> |                       | (Disabled)                                                  | _   |                       |

| 0028 <sub>H</sub>                         | PDRF                  | Port F data register                                        | R/W | 00000000 <sub>B</sub> |

| 0029 <sub>H</sub>                         | DDRF                  | Port F direction register                                   | R/W | 00000000 <sub>B</sub> |

| 002A <sub>H</sub>                         | PDRG                  | Port G data register                                        | R/W | 00000000 <sub>B</sub> |

| 002B <sub>H</sub>                         | DDRG                  | Port G direction register                                   | R/W | 00000000 <sub>B</sub> |

| 002C <sub>H</sub>                         | PUL0                  | Port 0 pull-up register                                     | R/W | 00000000 <sub>B</sub> |

| 002D <sub>H</sub> to<br>0034 <sub>H</sub> | _                     | (Disabled)                                                  | _   |                       |

| 0035 <sub>H</sub>                         | PULG                  | Port G pull-up register                                     | R/W | 00000000 <sub>B</sub> |

| 0036 <sub>H</sub>                         | T01CR1                | 8/16-bit composite timer 01 status control register 1 ch. 0 | R/W | 00000000 <sub>B</sub> |

| 0037 <sub>H</sub>                         | T00CR1                | 8/16-bit composite timer 00 status control register 1 ch. 0 | R/W | 00000000 <sub>B</sub> |

| 0038 <sub>H</sub>                         | T11CR1                | 8/16-bit composite timer 11 status control register 1 ch. 1 | R/W | 00000000 <sub>B</sub> |

| 0039 <sub>H</sub>                         | T10CR1                | 8/16-bit composite timer 10 status control register 1 ch. 1 | R/W | 00000000 <sub>B</sub> |

| 003A <sub>H</sub> to<br>0048 <sub>H</sub> | _                     | (Disabled)                                                  | _   | _                     |

| 0049 <sub>H</sub>                         | EIC10                 | External interrupt circuit control register ch. 2/ch. 3     | R/W | 00000000 <sub>B</sub> |

# 15. I/O Map (MB95210H Series)

| Address                                   | Register abbreviation | Register name                                               | R/W | Initial value         |

|-------------------------------------------|-----------------------|-------------------------------------------------------------|-----|-----------------------|

| 0000 <sub>H</sub>                         | PDR0                  | Port 0 data register                                        | R/W | 00000000 <sub>B</sub> |

| 0001 <sub>H</sub>                         | DDR0                  | Port 0 direction register                                   | R/W | 00000000 <sub>B</sub> |

| 0002 <sub>H</sub>                         | PDR1                  | Port 1 data register                                        | R/W | 00000000 <sub>B</sub> |

| 0003 <sub>H</sub>                         | DDR1                  | Port 1 direction register                                   | R/W | 00000000 <sub>B</sub> |

| 0004 <sub>H</sub>                         | _                     | (Disabled)                                                  |     | _                     |

| 0005 <sub>H</sub>                         | WATR                  | Oscillation stabilization wait time setting register        | R/W | 11111111 <sub>B</sub> |

| 0006 <sub>H</sub>                         | _                     | (Disabled)                                                  |     | _                     |

| 0007 <sub>H</sub>                         | SYCC                  | System clock control register                               | R/W | XXXXXX11 <sub>B</sub> |

| 0008 <sub>H</sub>                         | STBC                  | Standby control register                                    | R/W | 00000XXX <sub>B</sub> |

| 0009 <sub>H</sub>                         | RSRR                  | Reset source register                                       | R   | XXXXXXXX <sub>B</sub> |

| 000A <sub>H</sub>                         | TBTC                  | Timebase timer control register                             | R/W | 00000000 <sub>B</sub> |

| 000B <sub>H</sub>                         | WPCR                  | Watch prescaler control register                            | R/W | 00000000 <sub>B</sub> |

| 000C <sub>H</sub>                         | WDTC                  | Watchdog timer control register                             | R/W | 00000000 <sub>B</sub> |

| 000D <sub>H</sub>                         | SYCC2                 | System clock control register 2                             | R/W | XX100011 <sub>B</sub> |

| 000E <sub>H</sub> to<br>0015 <sub>H</sub> | _                     | (Disabled)                                                  | _   | 1                     |

| 0016 <sub>H</sub>                         | _                     | (Disabled)                                                  | _   |                       |

| 0017 <sub>H</sub>                         | _                     | (Disabled)                                                  | _   | _                     |

| 0018 <sub>H</sub> to<br>0027 <sub>H</sub> | _                     | (Disabled)                                                  | _   | _                     |

| 0028 <sub>H</sub>                         | PDRF                  | Port F data register                                        | R/W | 00000000 <sub>B</sub> |

| 0029 <sub>H</sub>                         | DDRF                  | Port F direction register                                   | R/W | 00000000 <sub>B</sub> |

| 002A <sub>H</sub>                         | _                     | (Disabled)                                                  | _   | _                     |

| 002B <sub>H</sub>                         | _                     | (Disabled)                                                  | _   |                       |

| 002C <sub>H</sub>                         | PUL0                  | Port 0 pull-up register                                     | R/W | 00000000 <sub>B</sub> |

| 002D <sub>H</sub> to<br>0034 <sub>H</sub> | _                     | (Disabled)                                                  | _   |                       |

| 0035 <sub>H</sub>                         | _                     | (Disabled)                                                  |     | _                     |

| 0036 <sub>H</sub>                         | T01CR1                | 8/16-bit composite timer 01 status control register 1 ch. 0 | R/W | 00000000 <sub>B</sub> |

| 0037 <sub>H</sub>                         | T00CR1                | 8/16-bit composite timer 00 status control register 1 ch. 0 | R/W | 00000000 <sub>B</sub> |

| 0038 <sub>H</sub>                         | _                     | (Disabled)                                                  | _   |                       |

| 0039 <sub>H</sub>                         | _                     | (Disabled)                                                  |     | _                     |

| 003A <sub>H</sub> to<br>0048 <sub>H</sub> | _                     | (Disabled)                                                  |     | _                     |

| 0049 <sub>H</sub>                         | _                     | (Disabled)                                                  |     | _                     |

# 17. Interrupt Source Table (MB95210H Series)

|                                        | 1.4                            | Vector tab        | le address        | Dit                                                | Priority order of in-                                                 |  |

|----------------------------------------|--------------------------------|-------------------|-------------------|----------------------------------------------------|-----------------------------------------------------------------------|--|

| Interrupt source                       | Interrupt<br>request<br>number | Upper             | Lower             | Bit name of<br>interrupt level<br>setting register | terrupt sources of<br>the same level<br>(occurring<br>simultaneously) |  |

| External interrupt ch. 4               | IRQ0                           | FFFA <sub>H</sub> | FFFB <sub>H</sub> | L00 [1:0]                                          | High                                                                  |  |

| _                                      | IRQ1                           | FFF8 <sub>H</sub> | FFF9 <sub>H</sub> | L01 [1:0]                                          |                                                                       |  |

|                                        | IRQ2                           | FFF6 <sub>H</sub> | FFF7 <sub>H</sub> | L02 [1:0]                                          | <b>↑</b>                                                              |  |

| External interrupt ch. 6  — —          | - IRQ3                         | FFF4 <sub>H</sub> | FFF5 <sub>H</sub> | L03 [1:0]                                          | -                                                                     |  |

| _                                      | IRQ4                           | FFF2 <sub>H</sub> | FFF3 <sub>H</sub> | L04 [1:0]                                          | ]                                                                     |  |

| 8/16-bit composite timer ch. 0 (Lower) | IRQ5                           | FFF0 <sub>H</sub> | FFF1 <sub>H</sub> | L05 [1:0]                                          | ]                                                                     |  |

| 8/16-bit composite timer ch. 0 (Upper) | IRQ6                           | FFEE <sub>H</sub> | FFEF <sub>H</sub> | L06 [1:0]                                          | ]                                                                     |  |

| _                                      | IRQ7                           | FFEC <sub>H</sub> | FFED <sub>H</sub> | L07 [1:0]                                          | ]                                                                     |  |

| _                                      | IRQ8                           | FFEA <sub>H</sub> | FFEB <sub>H</sub> | L08 [1:0]                                          | ]                                                                     |  |

| _                                      | IRQ9                           | FFE8 <sub>H</sub> | FFE9 <sub>H</sub> | L09 [1:0]                                          | ]                                                                     |  |

| _                                      | IRQ10                          | FFE6 <sub>H</sub> | FFE7 <sub>H</sub> | L10 [1:0]                                          |                                                                       |  |

| _                                      | IRQ11                          | FFE4 <sub>H</sub> | FFE5 <sub>H</sub> | L11 [1:0]                                          |                                                                       |  |

| _                                      | IRQ12                          | FFE2 <sub>H</sub> | FFE3 <sub>H</sub> | L12 [1:0]                                          |                                                                       |  |

| _                                      | IRQ13                          | FFE0 <sub>H</sub> | FFE1 <sub>H</sub> | L13 [1:0]                                          |                                                                       |  |

| _                                      | IRQ14                          | FFDE <sub>H</sub> | FFDF <sub>H</sub> | L14 [1:0]                                          |                                                                       |  |

| _                                      | IRQ15                          | FFDC <sub>H</sub> | FFDD <sub>H</sub> | L15 [1:0]                                          |                                                                       |  |

| _                                      | IRQ16                          | FFDA <sub>H</sub> | FFDB <sub>H</sub> | L16 [1:0]                                          |                                                                       |  |

| _                                      | IRQ17                          | FFD8 <sub>H</sub> | FFD9 <sub>H</sub> | L17 [1:0]                                          |                                                                       |  |

| 8/10-bit A/D converter                 | IRQ18                          | FFD6 <sub>H</sub> | FFD7 <sub>H</sub> | L18 [1:0]                                          |                                                                       |  |

| Timebase timer                         | IRQ19                          | FFD4 <sub>H</sub> | FFD5 <sub>H</sub> | L19 [1:0]                                          | ]                                                                     |  |

| Watch prescaler                        | IRQ20                          | FFD2 <sub>H</sub> | FFD3 <sub>H</sub> | L20 [1:0]                                          | ]                                                                     |  |

| _                                      | IRQ21                          | FFD0 <sub>H</sub> | FFD1 <sub>H</sub> | L21 [1:0]                                          | ]                                                                     |  |

| _                                      | IRQ22                          | FFCE <sub>H</sub> | FFCF <sub>H</sub> | L22 [1:0]                                          | ▼                                                                     |  |

| Flash memory                           | IRQ23                          | FFCC <sub>H</sub> | FFCD <sub>H</sub> | L23 [1:0]                                          | Low                                                                   |  |

$(V_{CC} = 5.0 \text{ V} \pm 10\%, V_{SS} = 0.0 \text{ V}, T_A = -40^{\circ}\text{C to } +85^{\circ}\text{C})$

| Doromotor              | Cumbal            | Din nama                         | Condition                                                                                                          |     | Value | <b>!</b> | Unit | Domouko                                           |

|------------------------|-------------------|----------------------------------|--------------------------------------------------------------------------------------------------------------------|-----|-------|----------|------|---------------------------------------------------|

| Parameter              | Symbol            | Pin name                         | Condition                                                                                                          | Min | Тур   | Max      | Unit | Remarks                                           |

| Input capacitance      | C <sub>IN</sub>   | Other than $V_{CC}$ and $V_{SS}$ | f = 1 MHz                                                                                                          | _   | 5     | 15       | pF   |                                                   |

|                        |                   |                                  | V <sub>CC</sub> = 5.5 V<br>F <sub>CH</sub> = 32 MHz                                                                | _   | 13    | 17       | mA   | Flash memory product (except writing and erasing) |

|                        | I <sub>CC</sub>   |                                  | F <sub>MP</sub> = 16 MHz<br>Main clock mode<br>(divided by 2)                                                      | _   | 33.5  | 39.5     | mA   | Flash memory product (at writing and erasing)     |

|                        |                   |                                  |                                                                                                                    | _   | 15    | 21       | mA   | At A/D conversion                                 |

|                        | I <sub>CCS</sub>  |                                  | $V_{CC}$ = 5.5 V<br>$F_{CH}$ = 32 MHz<br>$F_{MP}$ = 16 MHz<br>Main sleep mode<br>(divided by 2)                    | _   | 5.5   | 9        | mA   |                                                   |

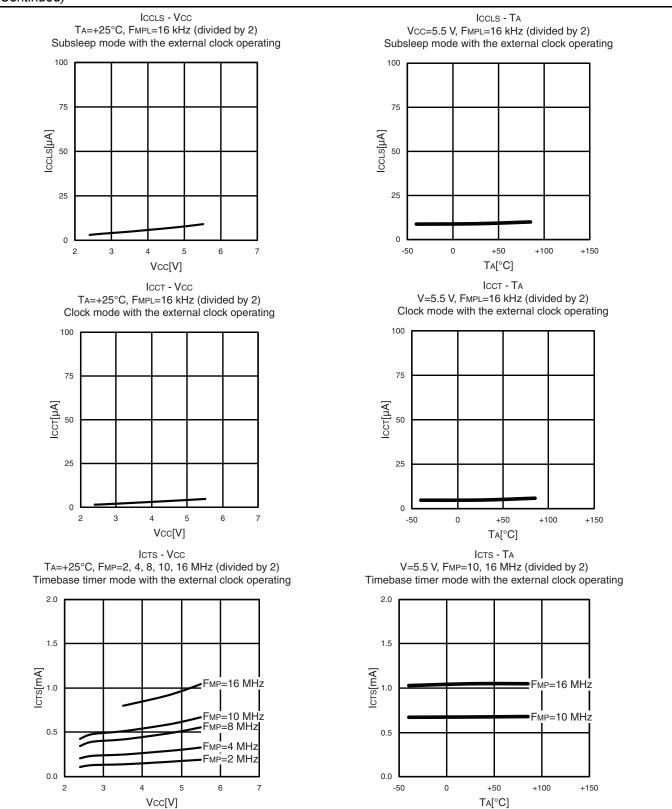

| Power supply current*4 | I <sub>CCL</sub>  |                                  | $V_{CC}$ = 5.5 V<br>$F_{CL}$ = 32 kHz<br>$F_{MPL}$ = 16 kHz<br>Subclock mode<br>(divided by 2)<br>$T_A$ = +25 °C   | _   | 65    | 153      | μA   |                                                   |

|                        | I <sub>CCLS</sub> |                                  | $V_{CC}$ = 5.5 V<br>$F_{CL}$ = 32 kHz<br>$F_{MPL}$ = 16 kHz<br>Subsleep mode<br>(divided by 2)<br>$T_{A}$ = +25 °C | _   | 10    | 84       | μА   |                                                   |

|                        | Ісст              |                                  | $V_{CC}$ = 5.5 V<br>$F_{CL}$ = 32 kHz<br>Watch mode<br>Main stop mode<br>$T_A$ = +25°C                             | _   | 5     | 30       | μА   |                                                   |

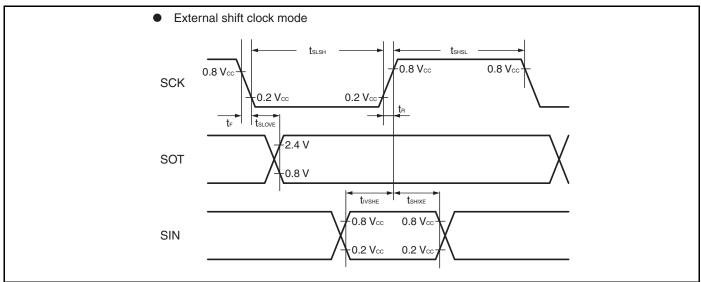

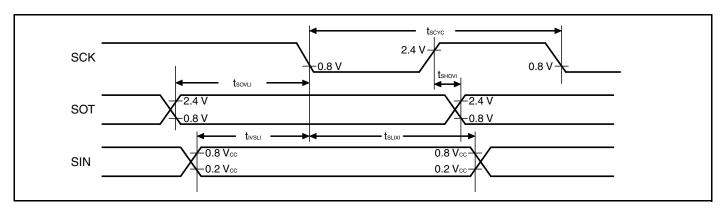

Sampling is executed at the rising edge of the sampling  $clock^{*1}$ , and serial clock delay is enabled  $clock^{*2}$ . (ESCR register: SCES bit = 0, ECCR register: SCDE bit = 1)

$(V_{CC} = 5.0 \text{ V} \pm 10\%, V_{SS} = 0.0 \text{ V}, T_A = -40^{\circ}\text{C to } +85^{\circ}\text{C})$

| Parameter                                        | Symbol             | Pin name     | Condition                             | Va                       | Unit                   |       |

|--------------------------------------------------|--------------------|--------------|---------------------------------------|--------------------------|------------------------|-------|

| Farameter                                        | Symbol             | Fill liaille | Condition                             | Min                      | Max                    | Ollit |

| Serial clock cycle time                          | t <sub>SCYC</sub>  | SCK          |                                       | 5 t <sub>MCLK</sub> *3   | _                      | ns    |

| SCK ↑→ SOT delay time                            | t <sub>SHOVI</sub> | SCK, SOT     | Internal clock                        | -95                      | +95                    | ns    |

| $Valid\;SIN\toSCK\;\!\!\downarrow$               | t <sub>IVSLI</sub> | SCK, SIN     | operation output pin:                 | t <sub>MCLK</sub> *3+190 | _                      | ns    |

| SCK $\downarrow \rightarrow$ valid SIN hold time | t <sub>SLIXI</sub> | SCK, SIN     | $C_L = 80 \text{ pF} + 1 \text{ TTL}$ | 0                        | _                      | ns    |

| $SOT \rightarrow SCK \downarrow delay time$      | t <sub>SOVLI</sub> | SCK, SOT     |                                       | _                        | 4 t <sub>MCLK</sub> *3 | ns    |

<sup>\*1:</sup> There is a function used to choose whether the sampling of reception data is performed at a rising edge or a falling edge of the serial clock.

<sup>\*3:</sup> See "18.4.2. Source Clock/Machine Clock" for t<sub>MCLK</sub>.

<sup>\*2:</sup> The serial clock delay function is a function that delays the output signal of the serial clock for half clock.

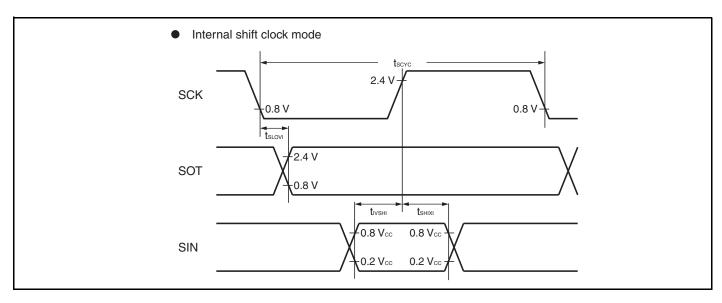

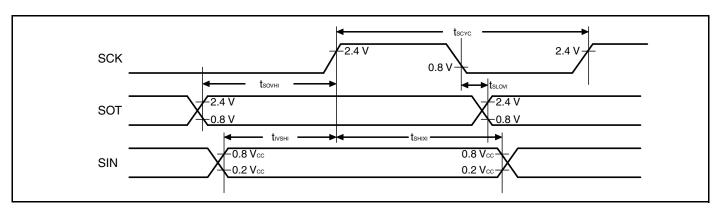

Sampling is executed at the falling edge of the sampling  $clock^{*1}$ , and serial clock delay is enabled\*<sup>2</sup>. (ESCR register: SCES bit = 1, ECCR register: SCDE bit = 1)

$(V_{CC} = 5.0 \text{ V} \pm 10\%, V_{SS} = 0.0 \text{ V}, T_A = -40^{\circ}\text{C to } +85^{\circ}\text{C})$

| Parameter                                   | Symbol             | Pin name     | Condition                             | Val                      | Unit                   |       |

|---------------------------------------------|--------------------|--------------|---------------------------------------|--------------------------|------------------------|-------|

| raidilletei                                 | Syllibol           | Fill lialile | Condition                             | Min                      | Max                    | Oilit |

| Serial clock cycle time                     | t <sub>SCYC</sub>  | SCK          |                                       | 5 t <sub>MCLK</sub> *3   | _                      | ns    |

| $SCK \downarrow \rightarrow SOT$ delay time | t <sub>SLOVI</sub> | SCK, SOT     | Internal clock operation              | -95                      | +95                    | ns    |

| Valid SIN → SCK ↑                           | t <sub>IVSHI</sub> | SCK, SIN     | output pin:                           | t <sub>MCLK</sub> *3+190 | _                      | ns    |

| SCK ↑→ valid SIN hold time                  | t <sub>SHIXI</sub> | SCK, SIN     | $C_L = 80 \text{ pF} + 1 \text{ TTL}$ | 0                        | _                      | ns    |

| $SOT \rightarrow SCK \uparrow delay time$   | t <sub>SOVHI</sub> | SCK, SOT     |                                       | _                        | 4 t <sub>MCLK</sub> *3 | ns    |

<sup>\*1:</sup> There is a function used to choose whether the sampling of reception data is performed at a rising edge or a falling edge of the serial clock.

<sup>\*3:</sup> See "18.4.2.Source Clock/Machine Clock" for t<sub>MCLK</sub>.

<sup>\*2:</sup> The serial clock delay function is a function that delays the output signal of the serial clock for half clock.

### 18.4.7 Low-voltage Detection

$(V_{SS} = 0.0 \text{ V}, T_A = -40^{\circ}\text{C to } +85^{\circ}\text{C})$

| Davamatav                   | Cumbal           |      | Value |      | Unit | Domestics.                                                                                          |

|-----------------------------|------------------|------|-------|------|------|-----------------------------------------------------------------------------------------------------|

| Parameter                   | Symbol           | Min  | Тур   | Max  | Unit | Remarks                                                                                             |

| Release voltage             | $V_{DL+}$        | 2.52 | 2.7   | 2.88 | V    | At power supply rise                                                                                |

| Detection voltage           | V <sub>DL</sub>  | 2.42 | 2.6   | 2.78 | V    | At power supply fall                                                                                |

| Hysteresis width            | V <sub>HYS</sub> | 70   | 100   | _    | mV   |                                                                                                     |

| Power supply start voltage  | V <sub>off</sub> | _    | _     | 2.3  | V    |                                                                                                     |

| Power supply end voltage    | V <sub>on</sub>  | 4.9  | _     | _    | V    |                                                                                                     |

| Power supply voltage change | +                | 1    | _     | _    | μs   | Slope of power supply that the reset release signal generates                                       |

| time (at power supply rise) | t <sub>r</sub>   | _    | 3000  | _    | μs   | Slope of power supply that the reset release signal generates within the rating (V <sub>DL+</sub> ) |

| Power supply voltage change |                  | 300  | _     | _    | μs   | Slope of power supply that the reset detection signal generates                                     |

| time (at power supply fall) | t <sub>f</sub>   | _    | 300   | _    | μs   | Slope of power supply that the reset detection signal generates within the rating $(V_{DL-})$       |

| Reset release delay time    | t <sub>d1</sub>  | _    | _     | 300  | μs   |                                                                                                     |

| Reset detection delay time  | t <sub>d2</sub>  | _    | _     | 20   | μs   |                                                                                                     |

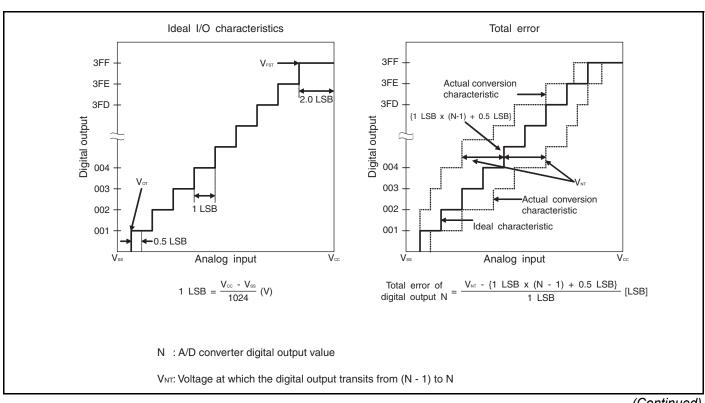

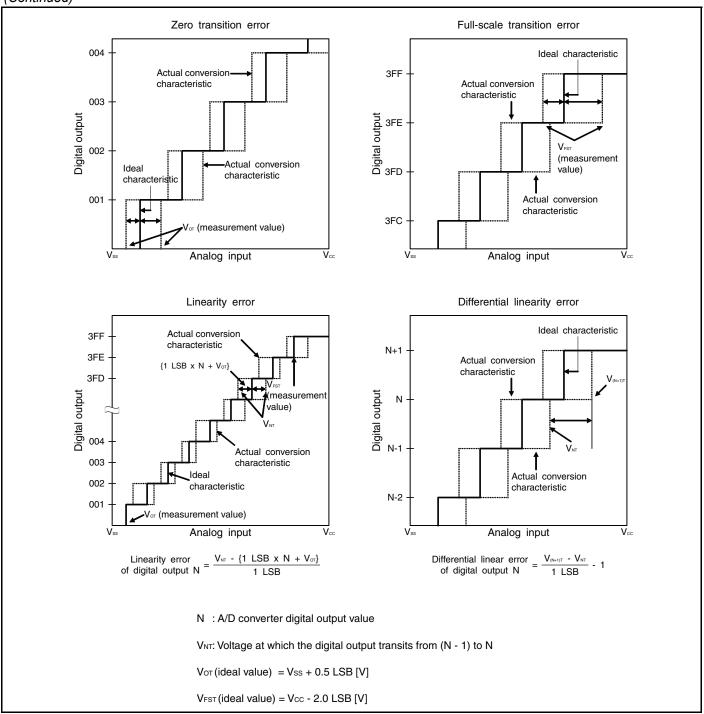

#### 18.5.3 Definitions of A/D Converter Terms

#### ■ Resolution

It indicates the level of analog variation that can be distinguished by the A/D converter. When the number of bits is 10, analog voltage can be divided into  $2^{10}$  = 1024.

#### ■ Linearity error (unit: LSB)

It indicates how much an actual conversion value deviates from the straight line connecting the zero transition point ("00 0000 0000"  $\leftarrow$  "00 0000 0001") of a device to the full-scale transition point ("11 1111 1111"  $\leftarrow$  "11 1111 1110") of the same device.

## ■ Differential linear error (unit: LSB)

It indicates how much the input voltage required to change the output code by 1 LSB deviates from an ideal value.

#### ■ Total error (unit: LSB)

It indicates the difference between an actual value and a theoretical value. The error can be caused by a zero transition error, a full-scale transition errors, a linearity error, a quantum error, or noise.

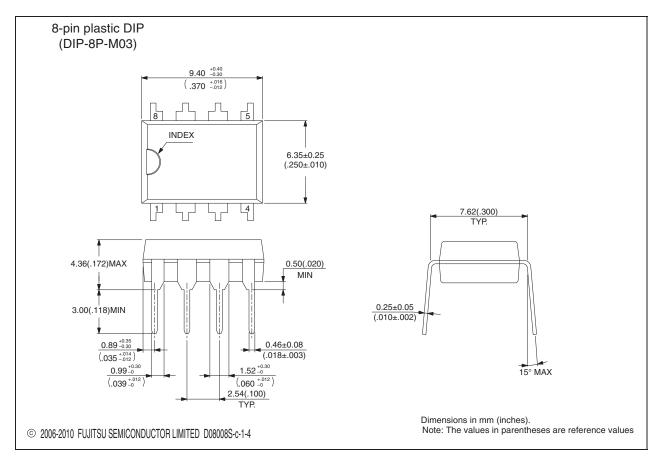

| 8-pin plastic DIP | Lead pitch     | 2.54 mm      |

|-------------------|----------------|--------------|

|                   | Sealing method | Plastic mold |

|                   |                |              |

|                   |                |              |

|                   |                |              |

|                   |                |              |

| (DIP-8P-M03)      |                |              |

Page 65 of 66

## 23. Major Changes

Spansion Publication Number: DS07-12623-5E

| Page | Section                                                                                                                                                 | Change results                                                                                         |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|

| 30   | Electrical Characteristics 1. Absolute Maximum Ratings                                                                                                  | Changed the characteristics of Input voltage.                                                          |

| 33   |                                                                                                                                                         | Corrected the maximum value of "H" level input voltage for PF2 pin. $V_{CC} + 0.3 \rightarrow 10.5$    |

|      | 3. DC Characteristics                                                                                                                                   | Corrected the maximum value of Open-drain output application voltage. 0.2Vcc $\rightarrow$ Vss $+$ 5.5 |

| 36   | ]                                                                                                                                                       | Added the footnote *5.                                                                                 |

| 39   | 4. AC Characteristics (1) Clock Timing  Added a figure of HCLK1/HCLK2.                                                                                  |                                                                                                        |

| 42   | (2) Source Clock/Machine Clock  Corrected the graph of Operating voltage - Operating frequency (with the on-chip debug function). (Corrected the pitch) |                                                                                                        |

| 43   | (3) External Reset Added "and power on" to the remarks column.                                                                                          |                                                                                                        |

| 58   | 6. Flash Memory Program/Erase<br>Characteristics                                                                                                        | Added the row of "Current drawn on PF2".                                                               |

|      |                                                                                                                                                         | Corrected the minimum value of Power supply voltage at erase/program. 4.5 $\rightarrow$ 3.0            |

Note: Please see "Document History" about later revised information.

# **Document History**

| Document Title: MB95200H/210H Series F <sup>2</sup> MC-8FX 8-bit Microcontroller Document Number: 002-07463 |         |                    |                    |                                                                                                       |

|-------------------------------------------------------------------------------------------------------------|---------|--------------------|--------------------|-------------------------------------------------------------------------------------------------------|

| Revision                                                                                                    | ECN     | Orig. of<br>Change | Submission<br>Date | Description of Change                                                                                 |

| **                                                                                                          | _       | AKIH               | 07/16/2010         | Migrated to Cypress and assigned document number 002-07463. No change to document contents or format. |

| *A                                                                                                          | 5177811 | AKIH               | 03/18/2016         | Updated to Cypress format.                                                                            |

Document Number: 002-07463 Rev. \*A