Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                        |

|----------------------------|---------------------------------------------------------------|

| Core Processor             | XCore                                                         |

| Core Size                  | 32-Bit 16-Core                                                |

| Speed                      | 2000MIPS                                                      |

| Connectivity               | -                                                             |

| Peripherals                | <u> </u>                                                      |

| Number of I/O              | 88                                                            |

| Program Memory Size        | -                                                             |

| Program Memory Type        | ROMIess                                                       |

| EEPROM Size                | <u> </u>                                                      |

| RAM Size                   | 512K x 8                                                      |

| Voltage - Supply (Vcc/Vdd) | 0.95V ~ 3.6V                                                  |

| Data Converters            | -                                                             |

| Oscillator Type            | External                                                      |

| Operating Temperature      | 0°C ~ 70°C (TA)                                               |

| Mounting Type              | Surface Mount                                                 |

| Package / Case             | 128-TQFP Exposed Pad                                          |

| Supplier Device Package    | 128-TQFP (14x14)                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/xmos/xl216-512-tq128-c20 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

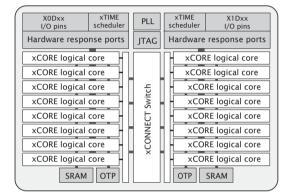

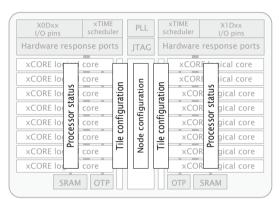

# 1 xCORE Multicore Microcontrollers

The xCORE-200 Series is a comprehensive range of 32-bit multicore microcontrollers that brings the low latency and timing determinism of the xCORE architecture to mainstream embedded applications. Unlike conventional microcontrollers, xCORE multicore microcontrollers execute multiple real-time tasks simultaneously and communicate between tasks using a high speed network. Because xCORE multicore microcontrollers are completely deterministic, you can write software to implement functions that traditionally require dedicated hardware.

Figure 1: XL216-512-TQ128 block diagram

Key features of the XL216-512-TQ128 include:

- **Tiles**: Devices consist of one or more xCORE tiles. Each tile contains between five and eight 32-bit xCOREs with highly integrated I/O and on-chip memory.

- Logical cores Each logical core can execute tasks such as computational code, DSP code, control software (including logic decisions and executing a state machine) or software that handles I/O. Section 6.1

- ▶ **xTIME scheduler** The xTIME scheduler performs functions similar to an RTOS, in hardware. It services and synchronizes events in a core, so there is no requirement for interrupt handler routines. The xTIME scheduler triggers cores on events generated by hardware resources such as the I/O pins, communication channels and timers. Once triggered, a core runs independently and concurrently to other cores, until it pauses to wait for more events. Section 6.2

- Channels and channel ends Tasks running on logical cores communicate using channels formed between two channel ends. Data can be passed synchronously or asynchronously between the channel ends assigned to the communicating tasks. Section 6.5

- xCONNECT Switch and Links Between tiles, channel communications are implemented over a high performance network of xCONNECT Links and routed through a hardware xCONNECT Switch. Section 6.6

-XM()S

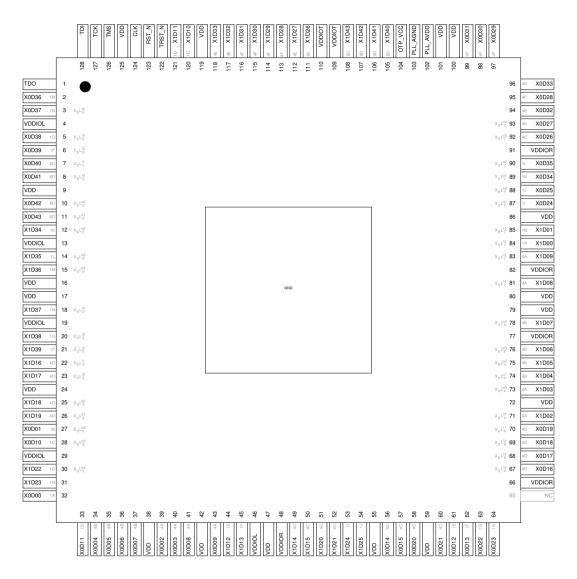

# 3 Pin Configuration

XL216-512-TQ128 Datasheet

E

(continued)

| Signal | Function                                      |                  |                 |                 |                   |                   | Туре | Properties  |

|--------|-----------------------------------------------|------------------|-----------------|-----------------|-------------------|-------------------|------|-------------|

| X0D41  | $X_0L0_{in}^0$                                |                  |                 | 8D <sup>5</sup> | 16B <sup>13</sup> |                   | I/O  | IOL, PD     |

| X0D42  | $X_0L0_{out}^0$                               |                  |                 | 8D <sup>6</sup> | 16B <sup>14</sup> |                   | I/O  | IOL, PD     |

| X0D43  | $X_0L0_{out}^1$                               |                  |                 | 8D <sup>7</sup> | 16B <sup>15</sup> |                   | I/O  | IOL, PD     |

| X1D00  | $X_0L7_{in}^2$                                | 1A <sup>0</sup>  |                 |                 |                   |                   | I/O  | IOR, PD     |

| X1D01  | X <sub>0</sub> L7 <sup>1</sup>                | 1 B <sup>0</sup> |                 |                 |                   |                   | I/O  | IOR, PD     |

| X1D02  | X <sub>0</sub> L4 <sup>0</sup>                |                  | 4A <sup>0</sup> | 8A <sup>0</sup> | 16A <sup>0</sup>  | 32A <sup>20</sup> | I/O  | IOR, PD     |

| X1D03  | X <sub>0</sub> L4 <sup>0</sup> <sub>out</sub> |                  | 4A <sup>1</sup> | 8A <sup>1</sup> | 16A <sup>1</sup>  | 32A <sup>21</sup> | I/O  | IOR, PD     |

| X1D04  | X <sub>0</sub> L4 <sup>1</sup> <sub>out</sub> |                  | 4B <sup>0</sup> | 8A <sup>2</sup> | 16A <sup>2</sup>  | 32A <sup>22</sup> | I/0  | IOR, PD     |

| X1D05  | $X_0L4_{out}^2$                               |                  | 4B <sup>1</sup> | 8A <sup>3</sup> | 16A <sup>3</sup>  | 32A <sup>23</sup> | I/O  | IOR, PD     |

| X1D06  | X <sub>0</sub> L4 <sup>3</sup> <sub>out</sub> |                  | 4B <sup>2</sup> | 8A <sup>4</sup> | 16A <sup>4</sup>  | 32A <sup>24</sup> | I/0  | IOR, PD     |

| X1D07  | X <sub>0</sub> L4 <sup>4</sup> <sub>out</sub> |                  | 4B <sup>3</sup> | 8A <sup>5</sup> | 16A <sup>5</sup>  | 32A <sup>25</sup> | I/O  | IOR, PD     |

| X1D08  | X <sub>0</sub> L7 <sup>4</sup>                |                  | 4A <sup>2</sup> | 8A <sup>6</sup> | 16A <sup>6</sup>  | 32A <sup>26</sup> | I/O  | IOR, PD     |

| X1D09  | X <sub>0</sub> L7 <sup>3</sup>                |                  | 4A <sup>3</sup> | 8A <sup>7</sup> | 16A <sup>7</sup>  | 32A <sup>27</sup> | I/O  | IOR, PD     |

| X1D10  |                                               | 1C <sup>0</sup>  |                 |                 |                   |                   | I/O  | IOT, PD     |

| X1D11  |                                               | 1D <sup>0</sup>  |                 |                 |                   |                   | I/O  | IOT, PD     |

| X1D12  |                                               | 1E <sup>0</sup>  |                 |                 |                   |                   | I/O  | IOL, PD     |

| X1D13  |                                               | 1F <sup>0</sup>  |                 |                 |                   |                   | I/0  | IOL, PD     |

| X1D14  |                                               |                  | 4C <sup>0</sup> | 8B <sup>0</sup> | 16A <sup>8</sup>  | 32A <sup>28</sup> | I/O  | IOR, PD     |

| X1D15  |                                               |                  | 4C <sup>1</sup> | 8B1             | 16A <sup>9</sup>  | 32A <sup>29</sup> | I/O  | IOR, PD     |

| X1D16  | X <sub>0</sub> L3 <sup>1</sup>                |                  | 4D <sup>0</sup> | 8B <sup>2</sup> | 16A <sup>10</sup> |                   | I/0  | IOL, PD     |

| X1D17  | X <sub>0</sub> L3 <sup>0</sup> <sub>in</sub>  |                  | 4D <sup>1</sup> | 8B <sup>3</sup> | 16A <sup>11</sup> |                   | I/O  | IOL, PD     |

| X1D18  | X <sub>0</sub> L3 <sup>0</sup> <sub>out</sub> |                  | 4D <sup>2</sup> | 8B <sup>4</sup> | 16A <sup>12</sup> |                   | I/O  | IOL, PD     |

| X1D19  | X <sub>0</sub> L3 <sup>1</sup> <sub>out</sub> |                  | 4D <sup>3</sup> | 8B <sup>5</sup> | 16A <sup>13</sup> |                   | I/O  | IOL, PD     |

| X1D20  |                                               |                  | 4C <sup>2</sup> | 8B <sup>6</sup> | 16A <sup>14</sup> | 32A <sup>30</sup> | I/O  | IOR, PD     |

| X1D21  |                                               |                  | 4C <sup>3</sup> | 8B <sup>7</sup> | 16A <sup>15</sup> | 32A <sup>31</sup> | I/O  | IOR, PD     |

| X1D22  | X <sub>0</sub> L3 <sup>4</sup>                | 1G <sup>0</sup>  |                 |                 |                   |                   | I/O  | IOL, PD     |

| X1D23  |                                               | 1H <sup>0</sup>  |                 |                 |                   |                   | I/O  | IOL, PD     |

| X1D24  |                                               | 110              |                 |                 |                   |                   | I/O  | IOR, PD     |

| X1D25  |                                               | 1J <sup>0</sup>  |                 |                 |                   |                   | I/0  | IOR, PD     |

| X1D26  |                                               |                  | 4E <sup>0</sup> | 8C <sup>0</sup> | 16B <sup>0</sup>  |                   | I/O  | IOT, PD     |

| X1D27  |                                               |                  | 4E <sup>1</sup> | 8C <sup>1</sup> | 16B <sup>1</sup>  |                   | I/0  | IOT, PD     |

| X1D28  |                                               |                  | 4F <sup>0</sup> | 8C <sup>2</sup> | 16B <sup>2</sup>  |                   | I/O  | IOT, PD     |

| X1D29  |                                               |                  | 4F <sup>1</sup> | 8C <sup>3</sup> | 16B <sup>3</sup>  |                   | I/O  | IOT, PD     |

| X1D30  |                                               |                  | 4F <sup>2</sup> | 8C <sup>4</sup> | 16B <sup>4</sup>  |                   | I/O  | IOT, PD     |

| X1D31  |                                               |                  | 4F <sup>3</sup> | 8C <sup>5</sup> | 16B <sup>5</sup>  |                   | 1/0  | IOT, PD     |

| X1D32  |                                               |                  | 4E <sup>2</sup> | 8C <sup>6</sup> | 16B <sup>6</sup>  |                   | I/O  | IOT, PD     |

| X1D33  |                                               |                  | 4E <sup>3</sup> | 8C <sup>7</sup> | 16B <sup>7</sup>  |                   | I/O  | IOT, PD     |

| X1D34  | X <sub>0</sub> L0 <sup>2</sup> <sub>out</sub> | 1K <sup>0</sup>  |                 |                 |                   |                   | I/O  | IOL, PD     |

| X1D35  | X <sub>0</sub> L0 <sup>3</sup> <sub>out</sub> | 1L <sup>0</sup>  |                 |                 |                   |                   | 1/0  | IOL, PD     |

| X1D36  | X <sub>0</sub> L0 <sup>4</sup> <sub>out</sub> | 1M <sup>0</sup>  |                 | 8D <sup>0</sup> | 16B <sup>8</sup>  |                   | I/O  | IOL, PD     |

| X1D37  | X <sub>0</sub> L3 <sup>4</sup> <sub>in</sub>  | 1 N <sup>0</sup> |                 | 8D <sup>1</sup> | 16B <sup>9</sup>  |                   | 1/0  | IOL, PD     |

| X1D38  | $X_0L3_{in}^3$                                | 100              |                 | 8D <sup>2</sup> | 16B <sup>10</sup> |                   | 1/0  | IOL, PD     |

| X1D39  | X <sub>0</sub> L3 <sup>2</sup> <sub>in</sub>  | 1P <sup>0</sup>  |                 | 8D <sup>3</sup> | 16B <sup>11</sup> |                   | 1/0  | IOL, PD     |

| L      | v 111                                         |                  |                 |                 |                   |                   | 1    | (continued) |

The pins used for SPI boot are hardcoded in the boot ROM and cannot be changed. If required, an SPI boot program can be burned into OTP that uses different pins.

#### 8.3 Boot from SPI slave

If set to boot from SPI slave, the processor enables the three pins specified in Figure 12 and expects a boot image to be clocked in. The supported clock polarity and phase are 0/0 and 1/1.

Figure 12: SPI slave pins

| Pin   | Signal | Description                |

|-------|--------|----------------------------|

| X0D00 | SS     | Slave Select               |

| X0D10 | SCLK   | Clock                      |

| X0D11 | MOSI   | Master Out Slave In (Data) |

The xCORE Tile expects each byte to be transferred with the *least-significant bit first*. The pins used for SPI boot are hardcoded in the boot ROM and cannot be changed. If required, an SPI boot program can be burned into OTP that uses different pins.

#### 8.4 Boot from xConnect Link

If set to boot from an xConnect Link, the processor enables its link(s) around 2 us after the boot process starts. Enabling the Link switches off the pull-down resistors on the link, drives all the TX wires low (the initial state for the Link), and monitors the RX pins for boot-traffic; they must be low at this stage. If the internal pull-down is too weak to drain any residual charge, external pull-downs of 10K may be required on those pins.

The boot-rom on the core will then:

- 1. Allocate channel-end 0.

- 2. Input a word on channel-end 0. It will use this word as a channel to acknowledge the boot. Provide the null-channel-end 0x0000FF02 if no acknowledgment is required.

- 3. Input the boot image specified above, including the CRC.

- 4. Input an END control token.

- 5. Output an END control token to the channel-end received in step 2.

- 6. Free channel-end 0.

- 7. Jump to the loaded code.

#### 8.5 Boot from OTP

If an xCORE tile is set to use secure boot (see Figure 8), the boot image is read from address 0 of the OTP memory in the tile's security module.

# 12.3 ESD Stress Voltage

Figure 20 ESD stress voltage

| 20:  | Symbol | Parameter            | MIN   | ТҮР | MAX  | UNITS | Notes |

|------|--------|----------------------|-------|-----|------|-------|-------|

| ress | HBM    | Human body model     | -2.00 |     | 2.00 | KV    |       |

| age  | CDM    | Charged Device Model | -500  |     | 500  | V     |       |

#### 12.4 Reset Timing

|                                                                   | Symbol  | Parameters          | MIN | TYP | MAX | UNITS | Notes |

|-------------------------------------------------------------------|---------|---------------------|-----|-----|-----|-------|-------|

| Figure 21:                                                        | T(RST)  | Reset pulse width   | 5   |     |     | μs    |       |

| Reset timing                                                      | T(INIT) | Initialization time |     |     | 150 | μs    | А     |

| A Shows the time taken to start besting ofter DST N has gone high |         |                     |     |     |     |       |       |

A Shows the time taken to start booting after RST\_N has gone high.

# 12.5 Power Consumption

|            | Symbol    | Parameter              | MIN | TYP | MAX | UNITS   | Notes      |

|------------|-----------|------------------------|-----|-----|-----|---------|------------|

|            | I(DDCQ)   | Quiescent VDD current  |     | 45  |     | mA      | A, B, C    |

| Figure 22: | PD        | Tile power dissipation |     | 325 |     | µW/MIPS | A, D, E, F |

| xCORE Tile | IDD       | Active VDD current     |     | 570 | 700 | mA      | A, G       |

| currents   | I(ADDPLL) | PLL_AVDD current       |     | 5   | 7   | mA      | Н          |

A Use for budgetary purposes only.

B Assumes typical tile and I/O voltages with no switching activity.

- C Includes PLL current.

- D Assumes typical tile and I/O voltages with nominal switching activity.

- E Assumes 1 MHz = 1 MIPS.

- F PD(TYP) value is the usage power consumption under typical operating conditions.

- G Measurement conditions: VDD = 1.0 V, VDDIO = 3.3 V, 25 °C, 500 MHz, average device resource usage.

- H PLL\_AVDD = 1.0 V

The tile power consumption of the device is highly application dependent and should be used for budgetary purposes only.

The asynchronous nature of links means that the relative phasing of CLK clocks is not important in a multi-clock system, providing each meets the required stability criteria.

| Symbol   | Parameter                     | MIN | TYP | MAX | UNITS | Notes |

|----------|-------------------------------|-----|-----|-----|-------|-------|

| f(TCK_D) | TCK frequency (debug)         |     |     | 18  | MHz   |       |

| f(TCK_B) | TCK frequency (boundary scan) |     |     | 10  | MHz   |       |

| T(SETUP) | TDO to TCK setup time         | 5   |     |     | ns    | А     |

| T(HOLD)  | TDO to TCK hold time          | 5   |     |     | ns    | А     |

| T(DELAY) | TCK to output delay           |     |     | 15  | ns    | В     |

# 12.9 JTAG Timing

Figure 26: JTAG timing

A Timing applies to TMS and TDI inputs.

B Timing applies to TDO output from negative edge of TCK.

All JTAG operations are synchronous to TCK apart from the global asynchronous reset TRST\_N.

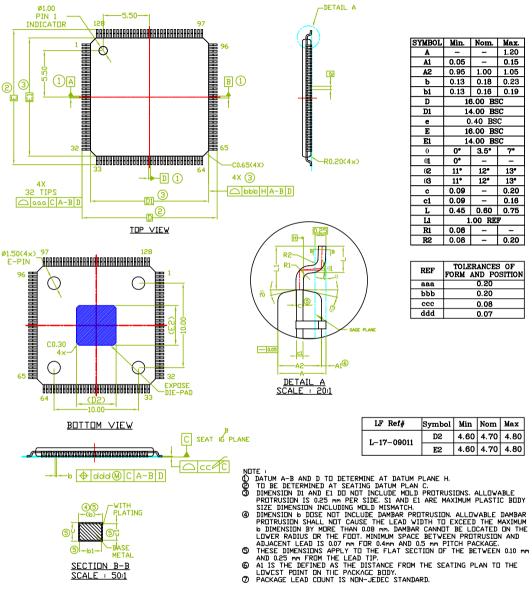

#### **Package Information** 13

| SYMBOL    | Min.      | Nom.    | Max. |  |  |

|-----------|-----------|---------|------|--|--|

| A         | -         | -       | 1.20 |  |  |

| A1        | 0.05      | -       | 0.15 |  |  |

| A2        | 0.95      | 1.00    | 1.05 |  |  |

| Ρ         | 0.13      | 0.18    | 0.23 |  |  |

| b1        | 0.13      | 0.16    | 0.19 |  |  |

| D         | 16        | 3.00 BS | SC   |  |  |

| D1        | 14        | 1.00 BS | SC   |  |  |

| e         | 0.40 BSC  |         |      |  |  |

| Е         | 16.00 BSC |         |      |  |  |

| E1        | 14.00 BSC |         |      |  |  |

| θ         | 0°        | 3.5°    | 7°   |  |  |

| <b>01</b> | 0*        | -       | -    |  |  |

| <b>62</b> | 11*       | 12*     | 13*  |  |  |

| <b>63</b> | 11*       | 12*     | 13*  |  |  |

| c         | 0.09      | -       | 0.20 |  |  |

| c1        | 0.09      | -       | 0.16 |  |  |

| L         | 0.45      | 0.60    | 0.75 |  |  |

| LI        | 1.00 REF  |         |      |  |  |

| R1        | 0.08      | -       | -    |  |  |

| R2        | 0.08      | -       | 0.20 |  |  |

| REF | TOLERANCES OF<br>FORM AND POSITION |

|-----|------------------------------------|

| aaa | 0.20                               |

| bbb | 0.20                               |

| ccc | 0.08                               |

| ddd | 0.07                               |

| LF Ref#    | Symbol | Min  | Nom  | Max  |

|------------|--------|------|------|------|

| L-17-09011 | D2     | 4.60 | 4.70 | 4.80 |

| L-17-09011 | E2     | 4.60 | 4.70 | 4.80 |

XS2-L16A-512-TQ128

-XMOS

# Appendices

# A Configuration of the XL216-512-TQ128

The device is configured through banks of registers, as shown in Figure 29.

Figure 29: Registers

The following communication sequences specify how to access those registers. Any messages transmitted contain the most significant 24 bits of the channel-end to which a response is to be sent. This comprises the node-identifier and the channel number within the node. if no response is required on a write operation, supply 24-bits with the last 8-bits set, which suppresses the reply message. Any multi-byte data is sent most significant byte first.

# A.1 Accessing a processor status register

The processor status registers are accessed directly from the processor instruction set. The instructions GETPS and SETPS read and write a word. The register number should be translated into a processor-status resource identifier by shifting the register number left 8 places, and ORing it with 0x0B. Alternatively, the functions getps(reg) and setps(reg,value) can be used from XC.

# A.2 Accessing an xCORE Tile configuration register

xCORE Tile configuration registers can be accessed through the interconnect using the functions write\_tile\_config\_reg(tileref, ...) and read\_tile\_config\_reg(tile  $\rightarrow$  ref, ...), where tileref is the name of the xCORE Tile, e.g. tile[1]. These functions implement the protocols described below.

Instead of using the functions above, a channel-end can be allocated to communicate with the xCORE tile configuration registers. The destination of the channel-end should be set to 0xnnnnC20C where nnnnnn is the tile-identifier.

A write message comprises the following:

| control-token | 24-bit response        | 16-bit          | 32-bit | control-token |

|---------------|------------------------|-----------------|--------|---------------|

| 192           | channel-end identifier | register number | data   | 1             |

The response to a write message comprises either control tokens 3 and 1 (for success), or control tokens 4 and 1 (for failure).

A read message comprises the following:

| control-token | 24-bit response        | 16-bit          | control-token |

|---------------|------------------------|-----------------|---------------|

| 193           | channel-end identifier | register number | 1             |

The response to the read message comprises either control token 3, 32-bit of data, and control-token 1 (for success), or control tokens 4 and 1 (for failure).

#### A.3 Accessing node configuration

Node configuration registers can be accessed through the interconnect using the functions write\_node\_config\_reg(device, ...) and read\_node\_config\_reg(device,  $\rightarrow$  ...), where device is the name of the node. These functions implement the protocols described below.

Instead of using the functions above, a channel-end can be allocated to communicate with the node configuration registers. The destination of the channel-end should be set to 0xnnnnC30C where nnnn is the node-identifier.

A write message comprises the following:

control-token

24-bit response

16-bit

32-bit

control-token

192

channel-end identifier

register number

data

1

The response to a write message comprises either control tokens 3 and 1 (for success), or control tokens 4 and 1 (for failure).

A read message comprises the following:

| control-token | 24-bit response        | 16-bit          | control-token |

|---------------|------------------------|-----------------|---------------|

| 193           | channel-end identifier | register number | 1             |

The response to a read message comprises either control token 3, 32-bit of data, and control-token 1 (for success), or control tokens 4 and 1 (for failure).

| 0x09:<br>Ring       | Bits  | Perm | Init | Description                   |

|---------------------|-------|------|------|-------------------------------|

| Oscillator          | 31:16 | RO   | -    | Reserved                      |

| Oscillator<br>Value | 15:0  | RO   | 0    | Ring oscillator Counter data. |

### B.10 Ring Oscillator Value: 0x0A

This register contains the current count of the Peripheral Wire ring oscillator. This value is not reset on a system reset.

**0x0A** Ring Oscillator Value

-

| ( <b>0A:</b><br>Ling | Bits  | Perm | Init | Description                   |

|----------------------|-------|------|------|-------------------------------|

| ator                 | 31:16 | RO   | -    | Reserved                      |

| lue                  | 15:0  | RO   | 0    | Ring oscillator Counter data. |

#### B.11 RAM size: 0x0C

The size of the RAM in bytes

**0x0C:** RAM size

|   | Bits | Perm | Init | Description                                |

|---|------|------|------|--------------------------------------------|

|   | 31:2 | RO   |      | Most significant 16 bits of all addresses. |

| 2 | 1:0  | RO   | -    | Reserved                                   |

#### B.12 Debug SSR: 0x10

This register contains the value of the SSR register when the debugger was called.

### B.22 Instruction breakpoint control: 0x40 .. 0x43

This register controls which logical cores may take an instruction breakpoint, and under which condition.

| Bits  | Perm | Init | Description                                                                                              |  |

|-------|------|------|----------------------------------------------------------------------------------------------------------|--|

| 31:24 | RO   | -    | Reserved                                                                                                 |  |

| 23:16 | DRW  | 0    | A bit for each thread in the machine allowing the breakpoint to be enabled individually for each thread. |  |

| 15:2  | RO   | -    | Reserved                                                                                                 |  |

| 1     | DRW  | 0    | When 0 break when PC == IBREAK_ADDR. When 1 = break when PC != IBREAK_ADDR.                              |  |

| 0     | DRW  | 0    | When 1 the instruction breakpoint is enabled.                                                            |  |

0x40 .. 0x43: Instruction breakpoint control

### B.23 Data watchpoint address 1: 0x50 .. 0x53

This set of registers contains the first address for the four data watchpoints.

**0x50 .. 0x53:** Data watchpoint address 1

| Data<br>hpoint | Bits | Perm | Init | Description |

|----------------|------|------|------|-------------|

| ress 1         | 31:0 | DRW  |      | Value.      |

#### B.24 Data watchpoint address 2: 0x60 .. 0x63

This set of registers contains the second address for the four data watchpoints.

0x60 .. 0x63: Data watchpoint address 2

| Data<br>Chpoint | Bits | Perm | Init | Description |

|-----------------|------|------|------|-------------|

| dress 2         | 31:0 | DRW  |      | Value.      |

# B.25 Data breakpoint control register: 0x70 .. 0x73

This set of registers controls each of the four data watchpoints.

-XMOS

XS2-L16A-512-TQ128

|                                    | Bits  | Perm | Init | Description                                                                                              |

|------------------------------------|-------|------|------|----------------------------------------------------------------------------------------------------------|

|                                    | 31:24 | RO   | -    | Reserved                                                                                                 |

|                                    | 23:16 | DRW  | 0    | A bit for each thread in the machine allowing the breakpoint to be enabled individually for each thread. |

| 0x9C 0x9F:<br>Resources            | 15:2  | RO   | -    | Reserved                                                                                                 |

| Resources<br>breakpoint<br>control | 1     | DRW  | 0    | When 0 break when condition A is met. When 1 = break when condition B is met.                            |

| register                           | 0     | DRW  | 0    | When 1 the instruction breakpoint is enabled.                                                            |

41

# C Tile Configuration

The xCORE Tile control registers can be accessed using configuration reads and writes (use write\_tile\_config\_reg(tileref, ...) and read\_tile\_config\_reg(tileref,  $\rightarrow$  ...) for reads and writes).

| Number    | Perm | Description                                    |

|-----------|------|------------------------------------------------|

| 0x00      | CRO  | Device identification                          |

| 0x01      | CRO  | xCORE Tile description 1                       |

| 0x02      | CRO  | xCORE Tile description 2                       |

| 0x04      | CRW  | Control PSwitch permissions to debug registers |

| 0x05      | CRW  | Cause debug interrupts                         |

| 0x06      | CRW  | xCORE Tile clock divider                       |

| 0x07      | CRO  | Security configuration                         |

| 0x20 0x27 | CRW  | Debug scratch                                  |

| 0x40      | CRO  | PC of logical core 0                           |

| 0x41      | CRO  | PC of logical core 1                           |

| 0x42      | CRO  | PC of logical core 2                           |

| 0x43      | CRO  | PC of logical core 3                           |

| 0x44      | CRO  | PC of logical core 4                           |

| 0x45      | CRO  | PC of logical core 5                           |

| 0x46      | CRO  | PC of logical core 6                           |

| 0x47      | CRO  | PC of logical core 7                           |

| 0x60      | CRO  | SR of logical core 0                           |

| 0x61      | CRO  | SR of logical core 1                           |

| 0x62      | CRO  | SR of logical core 2                           |

| 0x63      | CRO  | SR of logical core 3                           |

| 0x64      | CRO  | SR of logical core 4                           |

| 0x65      | CRO  | SR of logical core 5                           |

| 0x66      | CRO  | SR of logical core 6                           |

| 0x67      | CRO  | SR of logical core 7                           |

Figure 31: Summary

# C.1 Device identification: 0x00

This register identifies the xCORE Tile

-XMOS°

0x04: Control PSwitch permissions to debug registers

| Bits | Perm | Init | Description                                                                                                     |

|------|------|------|-----------------------------------------------------------------------------------------------------------------|

| 31   | CRW  | 0    | When 1 the PSwitch is restricted to RO access to all CRW registers from SSwitch, XCore(PS_DBG_Scratch) and JTAG |

| 30:1 | RO   | -    | Reserved                                                                                                        |

| 0    | CRW  | 0    | When 1 the PSwitch is restricted to RO access to all CRW registers from SSwitch                                 |

# C.5 Cause debug interrupts: 0x05

This register can be used to raise a debug interrupt in this xCORE tile.

**0x05:** Cause debug interrupts

| Bits | Perm | Init | Description                                 |

|------|------|------|---------------------------------------------|

| 31:2 | RO   | -    | Reserved                                    |

| 1    | CRW  | 0    | 1 when the processor is in debug mode.      |

| 0    | CRW  | 0    | Request a debug interrupt on the processor. |

# C.6 xCORE Tile clock divider: 0x06

This register contains the value used to divide the PLL clock to create the xCORE tile clock. The divider is enabled under control of the tile control register

0x06: xCORE Tile clock divider

| Bits  | Perm | Init | Description                                                   |  |

|-------|------|------|---------------------------------------------------------------|--|

| 31    | CRW  | 0    | Clock disable. Writing '1' will remove the clock to the tile. |  |

| 30:16 | RO   | -    | Reserved                                                      |  |

| 15:0  | CRW  | 0    | Clock divider.                                                |  |

# C.7 Security configuration: 0x07

Copy of the security register as read from OTP.

|    | Bits  | Perm | Init | Description                                                 |

|----|-------|------|------|-------------------------------------------------------------|

|    | 31    | CRO  |      | Disables write permission on this register                  |

|    | 30:15 | RO   | -    | Reserved                                                    |

|    | 14    | CRO  |      | Disable access to XCore's global debug                      |

|    | 13    | RO   | -    | Reserved                                                    |

|    | 12    | CRO  |      | lock all OTP sectors                                        |

|    | 11:8  | CRO  |      | lock bit for each OTP sector                                |

|    | 7     | CRO  |      | Enable OTP reduanacy                                        |

|    | 6     | RO   | -    | Reserved                                                    |

|    | 5     | CRO  |      | Override boot mode and read boot image from OTP             |

| 7: | 4     | CRO  |      | Disable JTAG access to the PLL/BOOT configuration registers |

| y. | 3:1   | RO   | -    | Reserved                                                    |

| n  | 0     | CRO  |      | Disable access to XCore's JTAG debug TAP                    |

0x07 Security configuration

# C.8 Debug scratch: 0x20 .. 0x27

A set of registers used by the debug ROM to communicate with an external debugger, for example over the switch. This is the same set of registers as the Debug Scratch registers in the processor status.

0x20 .. 0x27: Debug scratch

| <b>0x27:</b><br>Debug | Bits | Perm | Init | Description |

|-----------------------|------|------|------|-------------|

| cratch                | 31:0 | CRW  |      | Value.      |

# C.9 PC of logical core 0: 0x40

Value of the PC of logical core 0.

0x40 PC of logical core 0

| 9 <b>x40:</b><br>gical | Bits | Perm | Init | Description |

|------------------------|------|------|------|-------------|

| ore 0                  | 31:0 | CRO  |      | Value.      |

-XMOS

# C.10 PC of logical core 1: 0x41

Value of the PC of logical core 1.

# C.24 SR of logical core 7: 0x67

Value of the SR of logical core 7

| 0x67:         |      |      |      |             |

|---------------|------|------|------|-------------|

| SR of logical | Bits | Perm | Init | Description |

| core 7        | 31:0 | CRO  |      | Value.      |

### D.8 System JTAG device ID register: 0x09

**0x09**: System JTAG device ID register

|         | Bits  | Perm | Init | Description |

|---------|-------|------|------|-------------|

| -       | 31:28 | RO   |      |             |

| 9:<br>G | 27:12 | RO   |      |             |

| D       | 11:1  | RO   |      |             |

| er      | 0     | RO   |      |             |

### D.9 System USERCODE register: 0x0A

**0x0A** System USERCODE register

| A:<br>n | Bits  | Perm | Init | Description                                |

|---------|-------|------|------|--------------------------------------------|

| E       | 31:18 | RO   |      | JTAG USERCODE value programmed into OTP SR |

| er      | 17:0  | RO   |      | metal fixable ID code                      |

### D.10 Directions 0-7: 0x0C

This register contains eight directions, for packets with a mismatch in bits 7..0 of the node-identifier. The direction in which a packet will be routed is goverened by the most significant mismatching bit.

| Bits  | Perm | Init | Description                                     |  |

|-------|------|------|-------------------------------------------------|--|

| 31:28 | RW   | 0    | The direction for packets whose dimension is 7. |  |

| 27:24 | RW   | 0    | The direction for packets whose dimension is 6. |  |

| 23:20 | RW   | 0    | The direction for packets whose dimension is 5. |  |

| 19:16 | RW   | 0    | The direction for packets whose dimension is 4. |  |

| 15:12 | RW   | 0    | The direction for packets whose dimension is 3. |  |

| 11:8  | RW   | 0    | The direction for packets whose dimension is 2. |  |

| 7:4   | RW   | 0    | The direction for packets whose dimension is 1. |  |

| 3:0   | RW   | 0    | The direction for packets whose dimension is 0. |  |

0x0C: Directions 0-7

#### D.11 Directions 8-15: 0x0D

This register contains eight directions, for packets with a mismatch in bits 15..8 of the node-identifier. The direction in which a packet will be routed is goverened by the most significant mismatching bit.

-XMOS-

# F Schematics Design Check List

✓ This section is a checklist for use by schematics designers using the XL216-512-TQ128. Each of the following sections contains items to check for each design.

### F.1 Power supplies

- □ VDDIO and OTP\_VCC supply is within specification before the VDD (core) supply is turned on. Specifically, the VDDIO and OTP\_VCC supply is within specification before VDD (core) reaches 0.4V (Section 11).

- The VDD (core) supply ramps monotonically (rises constantly) from 0V to its final value (0.95V 1.05V) within 10ms (Section 11).

- The VDD (core) supply is capable of supplying 700 mA (Section 11 and Figure 18).

- PLL\_AVDD is filtered with a low pass filter, for example an RC filter, see Section 11

#### F.2 Power supply decoupling

- The design has multiple decoupling capacitors per supply, for example at least four0402 or 0603 size surface mount capacitors of 100nF in value, per supply (Section 11).

- A bulk decoupling capacitor of at least 10uF is placed on each supply (Section 11).

#### F.3 Power on reset

□ The RST\_N and TRST\_N pins are asserted (low) during or after power up. The device is not used until these resets have taken place.

#### F.4 Clock

- The CLK input pin is supplied with a clock with monotonic rising edges and low jitter.

- You have chosen an input clock frequency that is supported by the device (Section 7).

#### F.5 Boot

- □ The device is connected to a QSPI flash for booting, connected to X0D01, X0D04..X0D07, and X0D10 (Section 8). If not, you must boot the device through OTP or JTAG, or set it to boot from SPI and connect a SPI flash.

- ☐ The Flash that you have chosen is supported by **xflash**, or you have created a specification file for it.

#### F.6 JTAG, XScope, and debugging

- $\Box$  You have decided as to whether you need an XSYS header or not (Section E)

- □ If you have not included an XSYS header, you have devised a method to program the SPI-flash or OTP (Section E).

#### F.7 GPIO

- □ You have not mapped both inputs and outputs to the same multi-bit port.

- Pins X0D04, X0D05, X0D06, and X0D07 are output only and are, during and after reset, pulled high and low appropriately (Section 8)

#### F.8 Multi device designs

Skip this section if your design only includes a single XMOS device.

$\Box$  One device is connected to a QSPI or SPI flash for booting.

-XMOS

Devices that boot from link have, for example, X0D06 pulled high and have link XL0 connected to a device to boot from (Section 8).

# H Associated Design Documentation

| Document Title                                 | Information                               | Document Number |

|------------------------------------------------|-------------------------------------------|-----------------|

| Estimating Power Consumption For XS1-L Devices | Power consumption                         | X4271           |

| Programming XC on XMOS Devices                 | Timers, ports, clocks, cores and channels | X9577           |

| xTIMEcomposer User Guide                       | Compilers, assembler and linker/mapper    | X3766           |

|                                                | Timing analyzer, xScope, debugger         |                 |

|                                                | Flash and OTP programming utilities       |                 |

# I Related Documentation

| Document Title                                  | Information                         | Document Number |

|-------------------------------------------------|-------------------------------------|-----------------|

| The XMOS XS1 Architecture                       | ISA manual                          | X7879           |

| XS1 Port I/O Timing                             | Port timings                        | X5821           |

| xCONNECT Architecture                           | Link, switch and system information | X4249           |

| XS1-L Link Performance and Design<br>Guidelines | Link timings                        | X2999           |

| XS1-L Clock Frequency Control                   | Advanced clock control              | X1433           |

| XS1-L Active Power Conservation                 | Low-power mode during idle          | X7411           |

-XMOS<sup>®</sup>-

63