Welcome to **E-XFL.COM**

**Understanding Embedded - CPLDs (Complex Programmable Logic Devices)**

Embedded - CPLDs, or Complex Programmable Logic Devices, are highly versatile digital logic devices used in electronic systems. These programmable components are designed to perform complex logical operations and can be customized for specific applications. Unlike fixed-function ICs, CPLDs offer the flexibility to reprogram their configuration, making them an ideal choice for various embedded systems. They consist of a set of logic gates and programmable interconnects, allowing designers to implement complex logic circuits without needing custom hardware.

#### **Applications of Embedded - CPLDs**

| Details                         |                                                           |

|---------------------------------|-----------------------------------------------------------|

| Product Status                  | Active                                                    |

| Programmable Type               | In System Programmable                                    |

| Delay Time tpd(1) Max           | 6.2 ns                                                    |

| Voltage Supply - Internal       | 1.71V ~ 1.89V                                             |

| Number of Logic Elements/Blocks | 1270                                                      |

| Number of Macrocells            | 980                                                       |

| Number of Gates                 | -                                                         |

| Number of I/O                   | 271                                                       |

| Operating Temperature           | 0°C ~ 85°C (TJ)                                           |

| Mounting Type                   | Surface Mount                                             |

| Package / Case                  | 324-LBGA                                                  |

| Supplier Device Package         | 324-FBGA (19x19)                                          |

| Purchase URL                    | https://www.e-xfl.com/product-detail/intel/5m1270zf324c5n |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## Programming/Erasure Specifications

Table 3 3 lists the programming/erasure specifications for the MAX V device family.

Table 3 3. Programming/Erasure Specifications for MAX V Devices

| Parameter                 | Block                           | Minimum | ı Typica | al Maxin | num Ur | nit |

|---------------------------|---------------------------------|---------|----------|----------|--------|-----|

| Erase and reprogram cycle | UFM                             |         | _        | 1000(1)  | Cycles |     |

| Liase and reprogram cycle | Configuration flash memory (CFN | M) —    | _        | 100      | Cycle  | es  |

Note thable 3 3

### DC Electrical Characteristics

Table 3 4 lists DC electrical characteristics for the MAX V device family.

Table 3 4. DC Electrical Characteristics for MAX V D(Notes) (Part 1 of 2)

| Symbol                   | Parameter                                             | Conditions                                                        | Minin  | num Typ | ical Max | kimum |

|--------------------------|-------------------------------------------------------|-------------------------------------------------------------------|--------|---------|----------|-------|

| I <sub>I</sub>           |                                                       | nt <sub>I</sub> ¥V <sub>CCIO</sub> max to 0 V(2)                  | -10    | _       | 10       | μΑ    |

| l <sub>oz</sub>          | Tri-stated I/O pin leakag                             | $V_{\rm O} = V_{\rm CCIO}$ max to 0 V(2)                          | -10    | _       | 10       | μА    |

|                          |                                                       | 5M40Z, 5M80Z, 5M160Z, an<br>5M240Z (Commercial grade)<br>(4) (5)  |        | 25      | 90       | μА    |

|                          |                                                       | 5M240Z (Commercial grade)<br>(6)                                  | _      | 27      | 96       | μA    |

| I <sub>CCSTANDBY</sub>   | V <sub>CCINT</sub> supply current (standby) (3)       | 5M40Z, 5M80Z, 5M160Z, an<br>5M240Z (Industrial grade)<br>(5), (7) | d<br>— | 25      | 139      | μА    |

|                          |                                                       | 5M240Z (Industrial grade(6)                                       | _      | 27      | 152      | μA    |

|                          |                                                       | 5M570Z (Commercial grade)<br>(4)                                  | _      | 27      | 96       | μA    |

|                          |                                                       | 5M570Z (Industrial grade()7)                                      | _      | 27      | 152      | μA    |

|                          |                                                       | 5M1270Z and 5M2210Z                                               | _      | 2       | _        | mA    |

| )/ (O)                   | Hysteresis for Schmitt                                | V <sub>CCIO</sub> = 3.3 V                                         | _      | 400     | _        | mV    |

| V <sub>SCHMITT</sub> (8) | trigger input(9)                                      | V <sub>CCIO</sub> = 2.5 V                                         | _      | 190     | _        | mV    |

| I <sub>CCPOWERUP</sub>   | V <sub>CCINT</sub> supply current during power-up(10) | MAX V devices                                                     | _      | _       | 40       | mA    |

|                          |                                                       | V <sub>CCIO</sub> = 3.3 V (11)                                    | 5      | _       | 25       | k:    |

|                          | Value of I/O pin pull-up                              | V <sub>CCIO</sub> = 2.5 V (11)                                    | 10     | _       | 40       | k:    |

| R <sub>PULLUP</sub>      | resistor during user                                  | V <sub>CCIO</sub> = 1.8 V (11)                                    | 25     | _       | 60       | k:    |

|                          | mode and ISP                                          | V <sub>CCIO</sub> = 1.5 V (11)                                    | 45     | _       | 95       | k:    |

|                          |                                                       | V <sub>CCIO</sub> = 1.2 V (11)                                    | 80     | _       | 130      | k:    |

<sup>(1)</sup> This value applies to the commercial grade devices. For the industrial grade devices, the value is 100 cycles.

Table 3 4. DC Electrical Characteristics for MAX V D(eNotes 1) (Part 2 of 2)

| Symbol              | Parameter                                                       | Conditions | Minir | num Typ | ical Max | kimum | Unit |

|---------------------|-----------------------------------------------------------------|------------|-------|---------|----------|-------|------|

| I <sub>PULLUP</sub> | I/O pin pull-up resistor<br>current when I/O is<br>unprogrammed | _          | _     | _       | 300      | μА    |      |

| Go                  | Input capacitance for user I/O pin                              | _          | _     | _       | 8        | pF    | -    |

| C <sub>GCLK</sub>   | Input capacitance for dual-purpose GCLK/us I/O pin              | er —       | _     | _       | 8        | pF    |      |

Notes table 3 4

- (1) Typical values are for  $\mp$  25°C,  $\forall_{CINT}$ = 1.8 V and  $\forall_{CIO}$ = 1.2, 1.5, 1.8, 2.5, or 3.3 V.

- (2) This value is specified for normal device operation. The value may vary during power-up. This applies totally (3.3, 2.5, 1.8, 1.5, and 1.2 V).

- (3)  $V_i$  = ground, no load, and no toggling inputs.

- (4) Commercial temperature ranges from 0°C to 85°C with the maximum current at 85°C.

- (5) Not applicable to the T144 package of the 5M240Z device.

- (6) Only applicable to the T144 package of the 5M240Z device.

- (7) Industrial temperature ranges from -40°C to 100°C with the maximum current at 100°C.

- (8) This value applies to commercial and industrial range devices. For extended temperature range devices also mV for V<sub>CCIO</sub>= 3.3 V and 120 mV for V<sub>CCIO</sub>= 2.5 V.

- (9) TheTCK input is susceptible to high pulse glitches when the input signal fall time is greater than 200 ns for all I/O standards.

- (10) This is a peak current value with a maximum duration of time.

- (11) Pin pull-up resistance values will lower if an external source drives the pin higher iban V

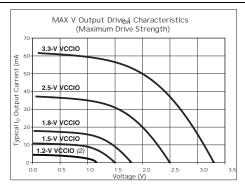

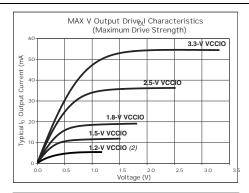

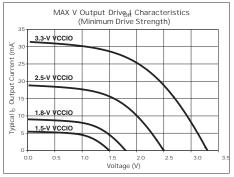

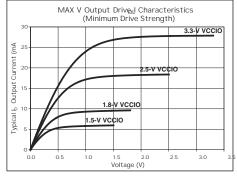

## **Output Drive Characteristics**

Figure 3 1 shows the typical drive strength characteristics of MAX V devices.

Figure 3 1. Output Drive Characteristics of MAX V (Naviee's)

Notes tbigure 3 1

- (1) The DC output current per pin is subject to the absolute maximum ratiobted -1 on page 3-1

- (2) 1.2-V \( \frac{1}{2} \) conly applicable to the maximum drive strength.

# I/O Standard Specifications

Table 3 5 through Table 3 13 on page 3 Best the I/O standard specifications for the MAX V device family.

Table 3 5. 3.3-V LVTTL Specifications for MAX V Devices

| Symbol            | Parameter                 | Conditions     | Minimur | n Maximu | m | Unit |

|-------------------|---------------------------|----------------|---------|----------|---|------|

| V <sub>CCIO</sub> | I/O supply voltage        | _              | 3.0     | 3.6      | V |      |

| V <sub>IH</sub>   | High-level input voltage  | _              | 1.7     | 4.0      | V |      |

| V <sub>IL</sub>   | Low-level input voltage   | _              | -0.5    | 0.8      | V |      |

| V <sub>OH</sub>   | High-level output voltage | IOH = -4 m/1A  | 2.4     | _        | V |      |

| V <sub>OL</sub>   | Low-level output voltage  | IOL = 4  r(1A) | _       | 0.45     | V |      |

Note toable 3 5

<sup>(1)</sup> This specification is supported across all the programmable drive strength settings available for this I/O standarid, thus show MAX V Device Architecthumpter.

| Table 3 6. 3.3-V LVCMOS Specifications for | MAX V | Devices |

|--------------------------------------------|-------|---------|

|--------------------------------------------|-------|---------|

| Symbol            | Parameter                 | Conditions                                  | Minimur                 | n Maximi                  | ım | Unit |

|-------------------|---------------------------|---------------------------------------------|-------------------------|---------------------------|----|------|

| V <sub>CCIO</sub> | I/O supply voltage        | _                                           | 3.0                     | 3.6                       | V  |      |

| V <sub>IH</sub>   | High-level input voltage  | _                                           | 1.7                     | 4.0                       | V  |      |

| V <sub>IL</sub>   | Low-level input voltage   | _                                           | -0.5                    | 0.8                       | V  |      |

| V <sub>OH</sub>   | High-level output voltage | $V_{CCIO} = 3.0,$<br>IOH = -0.1 mA(1)       | V <sub>CCIO</sub> - 0.2 | V <sub>CCIO</sub> - 0.2 — |    |      |

| V <sub>OL</sub>   | Low-level output voltage  | $V_{CCIO} = 3.0,$ $IOL = 0.1 \text{ mA}(1)$ | _                       | 0.2                       | V  |      |

Note toable 3 6

Table 3 7. 2.5-V I/O Specifications for MAX V Devices

| Symbol            | Parameter                 | Conditions        | Minimur | n Maxim      | ım l |

|-------------------|---------------------------|-------------------|---------|--------------|------|

| V <sub>CCIO</sub> | I/O supply voltage        | _                 | 2.375   | 2.625        | V    |

| V <sub>IH</sub>   | High-level input voltage  | _                 | 1.7     | 4.0          | V    |

| V <sub>IL</sub>   | Low-level input voltage   | _                 | -0.5    | 0.7          | V    |

|                   |                           | IOH = -0.1  mA(1) | 2.1     | <del>_</del> | V    |

| $V_{OH}$          | High-level output voltage | IOH = -1  mA(1)   | 2.0     | _            | V    |

|                   |                           | IOH = -2  mA(1)   | 1.7     | _            | V    |

|                   |                           | IOL = 0.1  mA(1)  | _       | 0.2          | V    |

| V <sub>OL</sub>   | Low-level output voltage  | IOL = 1 mA(1)     | _       | 0.4          | V    |

|                   |                           | IOL = 2 mA(1)     | _       | 0.7          | V    |

Note to able 3 7

Table 3 8. 1.8-V I/O Specifications for MAX V Devices

| Symbol            | Parameter                 | Conditions     | Minimun                  | n Maximu | ım | Unit |

|-------------------|---------------------------|----------------|--------------------------|----------|----|------|

| V <sub>CCIO</sub> | I/O supply voltage        | _              | 1.71                     | 1.89     | V  |      |

| V <sub>IH</sub>   | High-level input voltage  | _              | 0.65 ₺८₺                 | 2.25 (2) | V  |      |

| V <sub>IL</sub>   | Low-level input voltage   | _              | -0.3                     | 0.35ക€⊮  | V  |      |

| V <sub>OH</sub>   | High-level output voltage | IOH = -2 r(nA) | V <sub>CCIO</sub> - 0.45 | _        | V  |      |

| V <sub>OL</sub>   | Low-level output voltage  | IOL = 2 n(1A)  | _                        | 0.45     | V  |      |

Notes toable 3 8

- (1) This specification is supported across all the programmable drive strength settings available for this I/O standarid, thus show MAX V Device Architecthumpter.

- (2) This maximum Mreflects the JEDEC specification. The MAX V input buffer can tolerate xinvum of 4.0, as specified by the Arameter in Table 3–2 on page 3–2

<sup>(1)</sup> This specification is supported across all the programmable drive strength settings available for this I/O standariod, those show MAX V Device Architecthoarpeter.

<sup>(1)</sup> This specification is supported across all the programmable drive strength settings available for this I/O standarid, this show MAX V Device Architecthoapeter.

Table 3 9. 1.5-V I/O Specifications for MAX V Devices

| Symbol            | Parameter                 | Conditions      | Minimun                 | n Maximu                    | ım | Unit |

|-------------------|---------------------------|-----------------|-------------------------|-----------------------------|----|------|

| V <sub>CCIO</sub> | I/O supply voltage        | _               | 1.425                   | 1.575                       | V  |      |

| V <sub>IH</sub>   | High-level input voltage  | _               | 0.65 &c\⁄               | V <sub>CCIO</sub> + 0.3 (2) | V  |      |

| V <sub>IL</sub>   | Low-level input voltage   | _               | -0.3                    | 0.35 ക∈%                    | V  |      |

| V <sub>OH</sub>   | High-level output voltage | IOH = -2 r(1A). | 0.75 × √ <sub>CIO</sub> | _                           | V  |      |

| V <sub>OL</sub>   | Low-level output voltage  | IOL = 2 r(1A)   | _                       | 0.25 × ₹ <sub>CIO</sub>     | V  |      |

Notes table 3 9

- (1) This specification is supported across all the programmable drive strength settings available for this I/O standarid, thus show MAX V Device Architecthumpter.

- (2) This maximum | reflects the JEDEC specification. The MAX V input buffer can tole rate xin from of 4.0, as specified by the Arameter in Table 3–2 on page 3–2

Table 3 10. 1.2-V I/O Specifications for MAX V Devices

| Symbol            | Parameter                 | Conditions      | Minimun                        | n Maximu                       | ım | Unit |

|-------------------|---------------------------|-----------------|--------------------------------|--------------------------------|----|------|

| V <sub>CCIO</sub> | I/O supply voltage        | _               | 1.14                           | 1.26                           | V  |      |

| V <sub>IH</sub>   | High-level input voltage  | _               | 0.8 <b>%</b> %                 | V <sub>CCIO</sub> + 0.3        | V  |      |

| V <sub>IL</sub>   | Low-level input voltage   | _               | -0.3                           | 0.25 & №                       | V  |      |

| V <sub>OH</sub>   | High-level output voltage | IOH = -2 r(1A). | 0.75 <b>×</b> √ <sub>CIO</sub> | _                              | V  |      |

| V <sub>OL</sub>   | Low-level output voltage  | IOL = 2 r(1A)   | _                              | 0.25 <b>×</b> √ <sub>CIO</sub> | V  |      |

Note toable 3 10

Table 3 11. 3.3-V PCI Specifications for MAX V De(Motes1)

| Symbol            | Parameter                 | Conditions    | Minim                 | um Typ | ical Max                | imum | Unit |

|-------------------|---------------------------|---------------|-----------------------|--------|-------------------------|------|------|

| V <sub>CCIO</sub> | I/O supply voltage        | _             | 3.0                   | 3.3    | 3.6                     | V    |      |

| V <sub>IH</sub>   | High-level input voltage  | _             | 0.5 &c\6              | _      | V <sub>CCIO</sub> + 0.5 | V    |      |

| V <sub>IL</sub>   | Low-level input voltage   | _             | -0.5                  | _      | 0.3 ⊗c1⁄6               | V    |      |

| V <sub>OH</sub>   | High-level output voltage | IOH = -500 μ/ | A 0.8 <sub>0</sub> %√ | _      | _                       | V    |      |

| V <sub>OL</sub>   | Low-level output voltage  | IOL = 1.5 mA  | _                     | _      | 0.2 <sub>80</sub> V     | V    |      |

Note to able 3 11

Table 3 12. LVDS Specifications for MAX V De(Nices 1)

| Symbol            | Parameter                         | Conditions | Minim | um Typi | ical Max | imum | Unit |

|-------------------|-----------------------------------|------------|-------|---------|----------|------|------|

| V <sub>CCIO</sub> | I/O supply voltage                | _          | 2.375 | 2.5     | 2.625    | V    |      |

| V <sub>OD</sub>   | Differential output voltage swing | _          | 247   | _       | 600      | m    | V    |

| Vos               | Output offset voltage             | _          | 1.125 | 1.25    | 1.375    | V    |      |

Note toable 3 12

<sup>(1)</sup> This specification is supported across all the programmable drive strength settings available for this I/O standariod, those show MAX V Device Architecthoapeter.

<sup>(1) 3.3-</sup>V PCI I/O standard is only supported in Bank 3 of the 5M1270Z and 5M2210Z devices.

<sup>(1)</sup> Supports emulated LVDS output using a three-resistor network (LVDS\_E\_3R).

## **Power Consumption**

You can use the AlteraPowerPlay Early Power Estimator and PowerPlay Power Analyzer to estimate the device power.

For more information about these power analysis tools, referPtowtenPlay Early Power Estimator for Altera CPLDs Usera6ditheePowerPlay Power Analyshapter in volume 3 of th@uartus II Handbook.

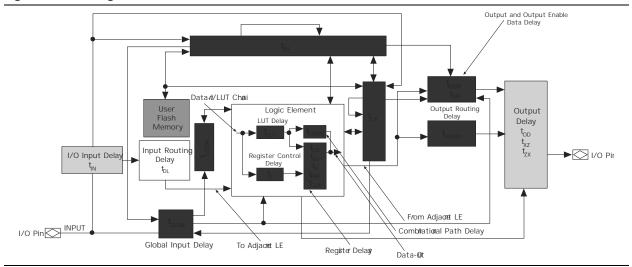

# Timing Model and Specifications

MAX V devices timing can be analyzed with the Altera Quaft tusoftware, a variety of industry-standard EDA simulators and timing analyzers, or with the timing model shown in Figure 3 2

MAX V devices have predictable internal delays that allow you to determine the worst-case timing of any design. The software provides timing simulation, point-to-point delay prediction, and detailed timing analysis for device-wide performance evaluation.

Figure 3 2. Timing Model for MAX V Devices

You can derive the timing characteristics of any signal path from the timing model and parameters of a particular device. You can calculate external timing parameters, which represent pin-to-pin timing delays, as the sum of the internal parameters.

f For more information, refer AN629: Understanding Timing in Altera CPLDs

|                  |                          |                 |         |               |                   | Performance            |                 |            |            |    |  |

|------------------|--------------------------|-----------------|---------|---------------|-------------------|------------------------|-----------------|------------|------------|----|--|

| Resource<br>Used | Design Size and Function |                 | sources | Used          | 5M40Z/ 5<br>5M240 | M80Z/ 5M<br>DZ/ 5M570Z | 160Z/<br>5W1270 | )Z/ 5M2210 | )Z<br>Unit |    |  |

|                  |                          | Mode            | LEs     | UFM<br>Blocks | C4                | C5, I5                 | C4              | C5, I5     |            |    |  |

|                  | 512 × 16                 | None            | 3       | 1             | 10.0              | 10.0                   | 10.0            | 10.0       | M          | Hz |  |

|                  | 512 × 16                 | SPI(2)          | 37      | 1             | 9.7               | 9.7                    | 8.0             | 8.0        | MH         | Ż  |  |

| UFM              | 512 × 8                  | Parallel<br>(3) | 73      | 1             | (4)               | (4)                    | (4)             | (4)        | MHz        |    |  |

|                  | 512 × 16                 | <b>₹C</b> (3)   | 142     | 1             | 100(5)            | 100 (5)                | 100 (5)         | 100 (5)    | kHz        |    |  |

Table 3 17. Device Performance for MAX V Devices (Part 2 of 2)

Notes table 3 17

- (1) This design is a binary loadable up counter.

- (2) This design is configured for read-only operation in Extended mode. Read and write ability increases the numbereoutsoduEsellesed.

- (3) This design is configured for read-only operation. Read and write ability increases the number of LEs used.

- (4) This design is asynchronous.

- (5) The \*C megafunction is verified in hardware up to 100-kHz serial clock line rate.

## Internal Timing Parameters

Internal timing parameters are specified on a speed grade basis independent of device density. Table 3 18 through Table 3 25 on page 3 118 t the MAX V device internal timing microparameters for LEs, input/output elements (IOEs), UFM blocks, and MultiTrack interconnects.

f For more information about each internal timing microparameters symbol, refer to AN629: Understanding Timing in Altera CPLDs

Table 3 18. LE Internal Timing Microparameters for MAX V Devices (Part 1 of 2)

|                   |                                           | 51   | M40Z/ 5<br>5M240 | M80Z/ 5<br>Z/ 5M5 |       | /    | 5M1270 | )Z/ 5M2 | 210Z   |      | Ì        |

|-------------------|-------------------------------------------|------|------------------|-------------------|-------|------|--------|---------|--------|------|----------|

| Symbol            | Parameter                                 | С    | :4               | C.                | 5, 15 |      | C4     |         | C5, I5 | Unit | i        |

|                   |                                           | Min  | Max              | Min               | Max   | Min  | Ma     | х М     | in M   | lax  | i        |

| t <sub>LUT</sub>  | LE combinational look-u table (LUT) delay | p _  | 1,215            |                   | 2,247 |      | 742    | _       | 914    | ps   | <b>;</b> |

| t <sub>COMB</sub> | Combinational path dela                   | ay — | 243              | -                 | 30    | 9 –  | - 19   | 2 -     | _ 2:   | 36   | ps       |

| t <sub>CLR</sub>  | LE register clear delay                   | 401  | _                | 54                | 5 –   | - 30 | 9 –    | - 38    | 1 -    | -    | ps       |

| t <sub>PRE</sub>  | LE register preset delay                  | 401  | _                | 54                | 5 –   | - 30 | 9 –    | - 38    | 31 -   | _    | ps       |

| t <sub>SU</sub>   | LE register setup time before clock       | 260  | _                | 321               |       | 271  |        | 333     | _      | ps   |          |

| t <sub>H</sub>    | LE register hold time after clock         | 0    | _                | 0                 | _     | 0    | _      | 0       | _      | ps   |          |

| t <sub>CO</sub>   | LE register clock-to-output delay         | _    | 380              | _                 | 494   |      | 305    |         | 376    | ps   |          |

Table 3 18. LE Internal Timing Microparameters for MAX V Devices (Part 2 of 2)

|                    |                                | 51  | M40Z/ 5<br>5M24C | M80Z/ !<br>)Z/ 5M5 |       | /   | 5M1270 | )Z/ 5M2 | 210Z   |      |    |

|--------------------|--------------------------------|-----|------------------|--------------------|-------|-----|--------|---------|--------|------|----|

| Symbol             | Parameter                      | С   | :4               | C!                 | 5, 15 |     | C4     |         | C5, I5 | Unit |    |

|                    |                                | Min | Max              | Min                | Max   | Min | Ma     | х М     | in M   | ах   |    |

| t <sub>CLKHL</sub> | Minimum clock high or low time | 253 |                  | 339                | _     | 216 | _      | 266     | _      | ps   | 3  |

| t <sub>C</sub>     | Register control delay         | _   | 1,350            | 6 –                | 1,74  | 1 — | 1,1    | 14 -    | 1,3    | 72   | ps |

Table 3 19. IOE Internal Timing Microparameters for MAX V Devices

|                       |                                                                | 5N  | 140Z/ 5M<br>5M240Z/ |     |       | 51  | M1270Z/ | 5M221 | OZ      |      |

|-----------------------|----------------------------------------------------------------|-----|---------------------|-----|-------|-----|---------|-------|---------|------|

| Symbol                | Parameter                                                      | C   | 4                   | C5, | , 15  | С   | 4       | C5    | 5, I5 L | Jnit |

|                       |                                                                | Min | Max                 | Min | Max   | Min | Max     | Min   | Max     |      |

| t <sub>FASTIO</sub>   | Data output delay from adjacent LE to I/O block                | _   | 170                 | _   | 428   | _   | 207     | _     | 254     | ps   |

| t <sub>IN</sub>       | I/O input pad and buffer delay                                 | _   | 907                 | _   | 986   | _   | 920     | _     | 1,132   | ps   |

| t <sub>GLOB</sub> (1) | I/O input pad and buffer<br>delay used as global<br>signal pin | _   | 2,261               | _   | 3,322 | _   | 1,974   | _     | 2,430   | ps   |

| t <sub>IOE</sub>      | Internally generated output enable delay                       | _   | 530                 | _   | 1,410 | _   | 374     | _     | 460     | ps   |

| $t_{DL}$              | Input routing delay                                            | _   | 318                 |     | 509   | _   | 291     |       | 358     | ps   |

| t <sub>OD</sub> (2)   | Output delay buffer and pad delay                              | _   | 1,319               | _   | 1,543 | _   | 1,383   | _     | 1,702   | ps   |

| t <sub>XZ</sub> (3)   | Output buffer disable delay                                    | _   | 1,045               | _   | 1,276 | _   | 982     | _     | 1,209   | ps   |

| t <sub>ZX</sub> (4)   | Output buffer enable delay                                     | _   | 1,160               | _   | 1,353 | _   | 1,303   | _     | 1,604   | ps   |

Notes table 3 19

MiMice d0.86.6(t)9.7( del.0291 Tw m0 7)]TJ54 T4,82

$- \mathsf{TwL} \ \ \mathsf{Tw(o)} - 5.8 (212 \ \mathsf{TDa} \ 5 \mathsf{M}) \\ 3.4 (240) \\ 20.5 (\mathsf{Z} \ 7) \\ ] \\ 2 \ \mathsf{T64}, \\ \mathsf{buffy} \ \mathsf{n8} \ 0 \ \mathsf{t} \ (\mathsf{D}) \\ 26.5 (\mathsf{m} \ \mathsf{Tt}) \\ 17.0 \ 0 \ 0 \ \mathsf{t33} \\ ] \\ \mathsf{Tr} \\ \mathsf{T$

<sup>(1)</sup> Delay numbers foetoediffer for each device density and speed grade. The delay numbers foetoe in Table 3–19 are based on a 5M240Z device target.

Table 3-18. LE Internal Timing Microparameters for MAX V Devices (Part 2 of 2)

|                    |                                | 51  | 5M40Z/ 5M80Z/ 5M160Z/<br>5M240Z/ 5M570Z 5M1270Z/ 5M2210Z |     |       |     |       |     | ½/ 5M2210Z |      |  |

|--------------------|--------------------------------|-----|----------------------------------------------------------|-----|-------|-----|-------|-----|------------|------|--|

| Symbol             | Parameter                      | C   | 4                                                        | C5  | , I5  | C   | 4     | C5  | , I5       | Unit |  |

|                    |                                | Min | Max                                                      | Min | Max   | Min | Max   | Min | Max        |      |  |

| t <sub>CLKHL</sub> | Minimum clock high or low time | 253 | _                                                        | 339 | _     | 216 | _     | 266 | _          | ps   |  |

| t <sub>C</sub>     | Register control delay         | _   | 1,356                                                    | _   | 1,741 | _   | 1,114 |     | 1,372      | ps   |  |

Table 3–19. IOE Internal Timing Microparameters for MAX V Devices

|                       |                                                                | 5M40Z/ 5M80Z/ 5M160Z/<br>5M240Z/ 5M570Z |       |        |       | 5M1270Z/ 5M2210Z |       |        |       |      |

|-----------------------|----------------------------------------------------------------|-----------------------------------------|-------|--------|-------|------------------|-------|--------|-------|------|

| Symbol                | Parameter                                                      | C4                                      |       | C5, I5 |       | C4               |       | C5, I5 |       | Unit |

|                       |                                                                | Min                                     | Max   | Min    | Max   | Min              | Max   | Min    | Max   |      |

| t <sub>FASTIO</sub>   | Data output delay from adjacent LE to I/O block                | _                                       | 170   |        | 428   | _                | 207   | _      | 254   | ps   |

| t <sub>IN</sub>       | I/O input pad and buffer delay                                 | _                                       | 907   | _      | 986   | _                | 920   | _      | 1,132 | ps   |

| t <sub>GLOB</sub> (1) | I/O input pad and buffer<br>delay used as global<br>signal pin | _                                       | 2,261 | _      | 3,322 | _                | 1,974 | _      | 2,430 | ps   |

| t <sub>IOE</sub>      | Internally generated output enable delay                       | _                                       | 530   | _      | 1,410 | _                | 374   | _      | 460   | ps   |

| t <sub>DL</sub>       | Input routing delay                                            | _                                       | 318   | _      | 509   | _                | 291   | _      | 358   | ps   |

| t <sub>oD</sub> (2)   | Output delay buffer and pad delay                              | _                                       | 1,319 | _      | 1,543 | _                | 1,383 | _      | 1,702 | ps   |

| t <sub>XZ</sub> (3)   | Output buffer disable delay                                    | _                                       | 1,045 | _      | 1,276 | _                | 982   | _      | 1,209 | ps   |

| t <sub>ZX</sub> (4)   | Output buffer enable delay                                     | _                                       | 1,160 | _      | 1,353 | _                | 1,303 | _      | 1,604 | ps   |

#### Notes to Table 3–19:

- (1) Delay numbers for t<sub>GLOB</sub> differ for each device density and speed grade. The delay numbers for t<sub>GLOB</sub>, shown in Table 3–19, are based on a 5M240Z device target.

- (2) For more information about delay adders associated with different I/O standards, drive strengths, and slew rates, refer to Table 3–34 on page 3–24 and Table 3–35 on page 3–25.

- (3) For more information about  $t_{\chi Z}$  delay adders associated with different I/O standards, drive strengths, and slew rates, refer to Table 3–22 on page 3–15 and Table 3–23 on page 3–15.

- (4) For more information about  $t_{ZX}$  delay adders associated with different I/O standards, drive strengths, and slew rates, refer to Table 3–20 on page 3–14 and Table 3–21 on page 3–14.