Welcome to **E-XFL.COM**

**Understanding Embedded - CPLDs (Complex Programmable Logic Devices)**

Embedded - CPLDs, or Complex Programmable Logic Devices, are highly versatile digital logic devices used in electronic systems. These programmable components are designed to perform complex logical operations and can be customized for specific applications. Unlike fixed-function ICs, CPLDs offer the flexibility to reprogram their configuration, making them an ideal choice for various embedded systems. They consist of a set of logic gates and programmable interconnects, allowing designers to implement complex logic circuits without needing custom hardware.

#### **Applications of Embedded - CPLDs**

| Details                         |                                                           |

|---------------------------------|-----------------------------------------------------------|

| Product Status                  | Active                                                    |

| Programmable Type               | In System Programmable                                    |

| Delay Time tpd(1) Max           | 7 ns                                                      |

| Voltage Supply - Internal       | 1.71V ~ 1.89V                                             |

| Number of Logic Elements/Blocks | 2210                                                      |

| Number of Macrocells            | 1700                                                      |

| Number of Gates                 | -                                                         |

| Number of I/O                   | 203                                                       |

| Operating Temperature           | 0°C ~ 85°C (TJ)                                           |

| Mounting Type                   | Surface Mount                                             |

| Package / Case                  | 256-LBGA                                                  |

| Supplier Device Package         | 256-FBGA (17x17)                                          |

| Purchase URL                    | https://www.e-xfl.com/product-detail/intel/5m2210zf256c4n |

|                                 |                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **Recommended Operating Conditions**

Table 3–2 lists recommended operating conditions for the MAX V device family.

Table 3–2. Recommended Operating Conditions for MAX V Devices

| Symbol                 | Parameter                                                               | Conditions         | Minimum | Maximum           | Unit |

|------------------------|-------------------------------------------------------------------------|--------------------|---------|-------------------|------|

| V <sub>CCINT</sub> (1) | 1.8-V supply voltage for internal logic and in-system programming (ISP) | MAX V devices      | 1.71    | 1.89              | V    |

|                        | Supply voltage for I/O buffers, 3.3-V operation                         | _                  | 3.00    | 3.60              | V    |

| V <sub>CCIO</sub> (1)  | Supply voltage for I/O buffers, 2.5-V operation                         | _                  | 2.375   | 2.625             | V    |

|                        | Supply voltage for I/O buffers, 1.8-V operation                         | _                  | 1.71    | 1.89              | V    |

|                        | Supply voltage for I/O buffers, 1.5-V operation                         | _                  | 1.425   | 1.575             | V    |

|                        | Supply voltage for I/O buffers, 1.2-V operation                         | _                  | 1.14    | 1.26              | V    |

| V <sub>I</sub>         | Input voltage                                                           | (2), (3), (4)      | -0.5    | 4.0               | V    |

| V <sub>0</sub>         | Output voltage                                                          | _                  | 0       | V <sub>CCIO</sub> | V    |

|                        |                                                                         | Commercial range   | 0       | 85                | °C   |

| $T_J$                  | Operating junction temperature                                          | Industrial range   | -40     | 100               | °C   |

|                        |                                                                         | Extended range (5) | -40     | 125               | °C   |

#### Notes to Table 3-2:

- (1) MAX V device ISP and/or user flash memory (UFM) programming using JTAG or logic array is not guaranteed outside the recommended operating conditions (for example, if brown-out occurs in the system during a potential write/program sequence to the UFM, Altera recommends that you read back the UFM contents and verify it against the intended write data).

- (2) The minimum DC input is -0.5 V. During transitions, the inputs may undershoot to -2.0 V for input currents less than 100 mA and periods shorter than 20 ns.

- (3) During transitions, the inputs may overshoot to the voltages shown below based on the input duty cycle. The DC case is equivalent to 100% duty cycle. For more information about 5.0-V tolerance, refer to the Using MAX V Devices in Multi-Voltage Systems chapter.

V<sub>IN</sub> Max. Duty Cycle

- 4.0 V 100% (DC)

- 4.1 V 90%

- 4.2 V 50%

- 4.3 V 30%

- 4.4 V 17%

- 4.5 V 10%

- (4) All pins, including the clock, I/O, and JTAG pins, may be driven before V<sub>CCINT</sub> and V<sub>CCIO</sub> are powered.

- (5) For the extended temperature range of 100 to 125°C, MAX V UFM programming (erase/write) is only supported using the JTAG interface. UFM programming using the logic array interface is not guaranteed in this range.

Table 3-4. DC Electrical Characteristics for MAX V Devices (Note 1) (Part 2 of 2)

| Symbol              | Parameter                                                       | Conditions | Minimum | Typical | Maximum | Unit |

|---------------------|-----------------------------------------------------------------|------------|---------|---------|---------|------|

| I <sub>PULLUP</sub> | I/O pin pull-up resistor<br>current when I/O is<br>unprogrammed | _          | _       | _       | 300     | μА   |

| C <sub>IO</sub>     | Input capacitance for user I/O pin                              | _          | _       | _       | 8       | pF   |

| C <sub>GCLK</sub>   | Input capacitance for dual-purpose GCLK/user I/O pin            | _          | _       | _       | 8       | pF   |

#### Notes to Table 3-4:

- (1) Typical values are for  $T_A = 25^{\circ}C$ ,  $V_{CCINT} = 1.8 \text{ V}$  and  $V_{CCIO} = 1.2$ , 1.5, 1.8, 2.5, or 3.3 V.

- (2) This value is specified for normal device operation. The value may vary during power-up. This applies to all V<sub>CCIO</sub> settings (3.3, 2.5, 1.8, 1.5, and 1.2 V).

- (3)  $V_1$  = ground, no load, and no toggling inputs.

- (4) Commercial temperature ranges from 0°C to 85°C with the maximum current at 85°C.

- (5) Not applicable to the T144 package of the 5M240Z device.

- (6) Only applicable to the T144 package of the 5M240Z device.

- (7) Industrial temperature ranges from -40°C to 100°C with the maximum current at 100°C.

- (8) This value applies to commercial and industrial range devices. For extended temperature range devices, the V<sub>SCHMITT</sub> typical value is 300 mV for V<sub>CCIO</sub> = 3.3 V and 120 mV for V<sub>CCIO</sub> = 2.5 V.

- (9) The TCK input is susceptible to high pulse glitches when the input signal fall time is greater than 200 ns for all I/O standards.

- (10) This is a peak current value with a maximum duration of t<sub>CONFIG</sub> time.

- (11) Pin pull-up resistance values will lower if an external source drives the pin higher than V<sub>CCIO</sub>.

| Table 3-6. 3.3-V LVCMOS Speci | fications for M <i>A</i> | X V Devices |

|-------------------------------|--------------------------|-------------|

|-------------------------------|--------------------------|-------------|

| Symbol            | Parameter                 | Conditions                                    | Minimum                 | Maximum | Unit |

|-------------------|---------------------------|-----------------------------------------------|-------------------------|---------|------|

| V <sub>CCIO</sub> | I/O supply voltage        | _                                             | 3.0                     | 3.6     | V    |

| V <sub>IH</sub>   | High-level input voltage  | _                                             | 1.7                     | 4.0     | V    |

| V <sub>IL</sub>   | Low-level input voltage   | _                                             | -0.5                    | 0.8     | V    |

| V <sub>OH</sub>   | High-level output voltage | $V_{CCIO} = 3.0,$<br>IOH = -0.1 mA (1)        | V <sub>CCIO</sub> - 0.2 | _       | V    |

| $V_{0L}$          | Low-level output voltage  | $V_{CCIO} = 3.0,$ $IOL = 0.1 \text{ mA } (1)$ | _                       | 0.2     | V    |

#### Note to Table 3-6:

Table 3-7. 2.5-V I/O Specifications for MAX V Devices

| Symbol            | Parameter Conditions      |                   | Minimum | Maximum | Unit |

|-------------------|---------------------------|-------------------|---------|---------|------|

| V <sub>CCIO</sub> | I/O supply voltage        | _                 | 2.375   | 2.625   | V    |

| V <sub>IH</sub>   | High-level input voltage  | _                 | 1.7     | 4.0     | V    |

| V <sub>IL</sub>   | Low-level input voltage   | _                 | -0.5    | 0.7     | V    |

| V <sub>OH</sub>   |                           | IOH = -0.1 mA (1) | 2.1     | _       | V    |

|                   | High-level output voltage | IOH = -1 mA (1)   | 2.0     | _       | V    |

|                   |                           | IOH = -2 mA (1)   | 1.7     | _       | V    |

|                   |                           | IOL = 0.1 mA (1)  | _       | 0.2     | V    |

| $V_{OL}$          | Low-level output voltage  | IOL = 1 mA (1)    | _       | 0.4     | V    |

| V <sub>OL</sub>   |                           | IOL = 2 mA (1)    | _       | 0.7     | V    |

#### Note to Table 3-7:

Table 3-8. 1.8-V I/O Specifications for MAX V Devices

| Symbol            | Parameter                 | Conditions      | Minimum                  | Maximum                  | Unit |

|-------------------|---------------------------|-----------------|--------------------------|--------------------------|------|

| V <sub>CCIO</sub> | I/O supply voltage        | _               | 1.71                     | 1.89                     | V    |

| V <sub>IH</sub>   | High-level input voltage  | _               | 0.65 × V <sub>CCIO</sub> | 2.25 (2)                 | V    |

| V <sub>IL</sub>   | Low-level input voltage   | _               | -0.3                     | 0.35 × V <sub>CCIO</sub> | V    |

| V <sub>OH</sub>   | High-level output voltage | IOH = -2 mA (1) | V <sub>CCIO</sub> - 0.45 | _                        | V    |

| V <sub>OL</sub>   | Low-level output voltage  | IOL = 2 mA (1)  | _                        | 0.45                     | V    |

#### Notes to Table 3-8:

- (1) This specification is supported across all the programmable drive strength settings available for this I/O standard, as shown in the MAX V Device Architecture chapter.

- (2) This maximum V<sub>IH</sub> reflects the JEDEC specification. The MAX V input buffer can tolerate a V<sub>IH</sub> maximum of 4.0, as specified by the V<sub>I</sub> parameter in Table 3–2 on page 3–2.

<sup>(1)</sup> This specification is supported across all the programmable drive strength settings available for this I/O standard, as shown in the MAX V Device Architecture chapter.

<sup>(1)</sup> This specification is supported across all the programmable drive strength settings available for this I/O standard, as shown in the MAX V Device Architecture chapter.

### **Power-Up Timing**

Table 3–15 lists the power-up timing characteristics for the MAX V device family.

Table 3-15. Power-Up Timing for MAX V Devices

| Symbol              | Parameter                                                  | Device             | Temperature Range         | Min | Тур | Max | Unit |

|---------------------|------------------------------------------------------------|--------------------|---------------------------|-----|-----|-----|------|

|                     |                                                            | 5M40Z              | Commercial and industrial | _   | _   | 200 | μs   |

|                     |                                                            | 3101402            | Extended                  | _   | _   | 300 | μs   |

|                     |                                                            | 5M80Z              | Commercial and industrial | _   | _   | 200 | μs   |

|                     |                                                            | JIVIOUZ            | Extended                  | _   | _   | 300 | μs   |

|                     |                                                            | 5M160Z             | Commercial and industrial | _   | _   | 200 | μs   |

|                     | The amount of time from when minimum V <sub>CCINT</sub> is |                    | Extended                  | _   | _   | 300 | μs   |

|                     |                                                            | 5M240Z <i>(2)</i>  | Commercial and industrial | _   | _   | 200 | μs   |

|                     |                                                            | JIVIZ40Z (Z)       | Extended                  | _   | _   | 300 | μs   |

| t                   |                                                            | 5M240Z <i>(3)</i>  | Commercial and industrial | _   | _   | 300 | μs   |

| t <sub>CONFIG</sub> | reached until the device                                   | 31V12402 (3)       | Extended                  | _   | _   | 400 | μs   |

|                     | enters user mode (1)                                       | 5M570Z             | Commercial and industrial | _   | _   | 300 | μs   |

|                     |                                                            | 31013702           | Extended                  | _   | _   | 400 | μs   |

|                     |                                                            | 5M1270Z <i>(4)</i> | Commercial and industrial | _   | _   | 300 | μs   |

|                     |                                                            | 3W12702 (4)        | Extended                  | _   | _   | 400 | μs   |

|                     |                                                            | 5M1270Z <i>(5)</i> | Commercial and industrial | _   | _   | 450 | μs   |

|                     |                                                            | JIVITZTUZ (3)      | Extended                  | _   | _   | 500 | μs   |

|                     |                                                            | 5M2210Z            | Commercial and industrial | _   |     | 450 | μs   |

|                     |                                                            | JIVIZZ IUZ         | Extended                  | _   | _   | 500 | μs   |

#### Notes to Table 3-15:

- (1) For more information about power-on reset (POR) trigger voltage, refer to the Hot Socketing and Power-On Reset in MAX V Devices chapter.

- (2) Not applicable to the T144 package of the 5M240Z device.

- (3) Only applicable to the T144 package of the 5M240Z device.

- (4) Not applicable to the F324 package of the 5M1270Z device.

- (5) Only applicable to the F324 package of the 5M1270Z device.

### **Power Consumption**

You can use the Altera® PowerPlay Early Power Estimator and PowerPlay Power Analyzer to estimate the device power.

For more information about these power analysis tools, refer to the *PowerPlay Early Power Estimator for Altera CPLDs User Guide* and the *PowerPlay Power Analysis* chapter in volume 3 of the *Quartus II Handbook*.

## **Timing Model and Specifications**

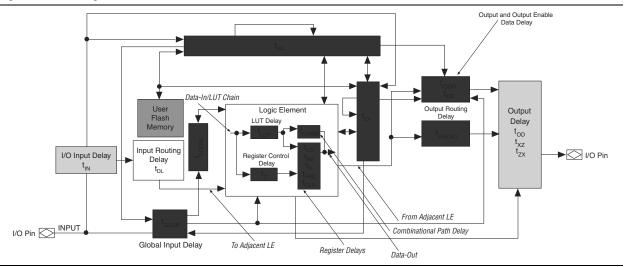

MAX V devices timing can be analyzed with the Altera Quartus® II software, a variety of industry-standard EDA simulators and timing analyzers, or with the timing model shown in Figure 3–2.

MAX V devices have predictable internal delays that allow you to determine the worst-case timing of any design. The software provides timing simulation, point-to-point delay prediction, and detailed timing analysis for device-wide performance evaluation.

Figure 3-2. Timing Model for MAX V Devices

You can derive the timing characteristics of any signal path from the timing model and parameters of a particular device. You can calculate external timing parameters, which represent pin-to-pin timing delays, as the sum of the internal parameters.

For more information, refer to AN629: Understanding Timing in Altera CPLDs.

### **Preliminary and Final Timing**

This section describes the performance, internal, external, and UFM timing specifications. All specifications are representative of the worst-case supply voltage and junction temperature conditions.

Timing models can have either preliminary or final status. The Quartus II software issues an informational message during the design compilation if the timing models are preliminary. Table 3–16 lists the status of the MAX V device timing models.

Preliminary status means the timing model is subject to change. Initially, timing numbers are created using simulation results, process data, and other known parameters. These tests are used to make the preliminary numbers as close to the actual timing parameters as possible.

Final timing numbers are based on actual device operation and testing. These numbers reflect the actual performance of the device under the worst-case voltage and junction temperature conditions.

Device

Final

5M40Z

✓

5M80Z

✓

5M160Z

✓

5M240Z

✓

5M570Z

✓

5M1270Z

✓

5M22107

✓

Table 3-16. Timing Model Status for MAX V Devices

### **Performance**

Table 3–17 lists the MAX V device performance for some common designs. All performance values were obtained with the Quartus II software compilation of megafunctions.

Table 3-17. Device Performance for MAX V Devices (Part 1 of 2)

|                  |                                         |                |     |               | Performance |                          |          |        |     |

|------------------|-----------------------------------------|----------------|-----|---------------|-------------|--------------------------|----------|--------|-----|

| Resource<br>Used | Design Size and<br>Function             | Resources Used |     |               |             | 80Z/ 5M160Z/<br>/ 5M570Z | 5M1270Z/ | Unit   |     |

|                  |                                         | Mode           | LEs | UFM<br>Blocks | C4          | C5, I5                   | C4       | C5, I5 |     |

|                  | 16-bit counter (1)                      |                | 16  | 0             | 184.1       | 118.3                    | 247.5    | 201.1  | MHz |

|                  | 64-bit counter (1)                      | _              | 64  | 0             | 83.2        | 80.5                     | 154.8    | 125.8  | MHz |

|                  | 16-to-1 multiplexer                     | _              | 11  | 0             | 17.4        | 20.4                     | 8.0      | 9.3    | ns  |

| LE               | 32-to-1 multiplexer                     | _              | 24  | 0             | 12.5        | 25.3                     | 9.0      | 11.4   | ns  |

|                  | 16-bit XOR function                     | _              | 5   | 0             | 9.0         | 16.1                     | 6.6      | 8.2    | ns  |

|                  | 16-bit decoder with single address line | _              | 5   | 0             | 9.2         | 16.1                     | 6.6      | 8.2    | ns  |

|                  | Design Size and<br>Function |                      |     |               |         | Performance           |                  |         |      |  |

|------------------|-----------------------------|----------------------|-----|---------------|---------|-----------------------|------------------|---------|------|--|

| Resource<br>Used |                             | Resources Used       |     |               | -       | OZ/ 5M16OZ/<br>5M57OZ | 5M1270Z/ 5M2210Z |         | Unit |  |

|                  |                             | Mode                 | LEs | UFM<br>Blocks | C4      | C5, I5                | C4               | C5, I5  |      |  |

|                  | 512 × 16                    | None                 | 3   | 1             | 10.0    | 10.0                  | 10.0             | 10.0    | MHz  |  |

|                  | 512 × 16                    | SPI (2)              | 37  | 1             | 9.7     | 9.7                   | 8.0              | 8.0     | MHz  |  |

| UFM              | 512 × 8                     | Parallel (3)         | 73  | 1             | (4)     | (4)                   | (4)              | (4)     | MHz  |  |

|                  | 512 × 16                    | I <sup>2</sup> C (3) | 142 | 1             | 100 (5) | 100 (5)               | 100 (5)          | 100 (5) | kHz  |  |

Table 3-17. Device Performance for MAX V Devices (Part 2 of 2)

#### Notes to Table 3-17:

- (1) This design is a binary loadable up counter.

- (2) This design is configured for read-only operation in Extended mode. Read and write ability increases the number of logic elements (LEs) used.

- (3) This design is configured for read-only operation. Read and write ability increases the number of LEs used.

- (4) This design is asynchronous.

- (5) The I<sup>2</sup>C megafunction is verified in hardware up to 100-kHz serial clock line rate.

### **Internal Timing Parameters**

Internal timing parameters are specified on a speed grade basis independent of device density. Table 3–18 through Table 3–25 on page 3–19 list the MAX V device internal timing microparameters for LEs, input/output elements (IOEs), UFM blocks, and MultiTrack interconnects.

For more information about each internal timing microparameters symbol, refer to *AN629: Understanding Timing in Altera CPLDs*.

Table 3-18. LE Internal Timing Microparameters for MAX V Devices (Part 1 of 2)

|                   |                                            | 5M40Z/ 5M80Z/ 5M160Z/<br>5M240Z/ 5M570Z |       |        |       | 5M1270Z/ 5M2210Z |     |        |     |      |

|-------------------|--------------------------------------------|-----------------------------------------|-------|--------|-------|------------------|-----|--------|-----|------|

| Symbol            | Parameter                                  | C4                                      |       | C5, I5 |       | C4               |     | C5, I5 |     | Unit |

|                   |                                            | Min                                     | Max   | Min    | Max   | Min              | Max | Min    | Max |      |

| t <sub>LUT</sub>  | LE combinational look-up table (LUT) delay | _                                       | 1,215 | _      | 2,247 | _                | 742 | _      | 914 | ps   |

| t <sub>COMB</sub> | Combinational path delay                   | _                                       | 243   | _      | 309   | _                | 192 | _      | 236 | ps   |

| t <sub>CLR</sub>  | LE register clear delay                    | 401                                     | _     | 545    | _     | 309              | _   | 381    | _   | ps   |

| t <sub>PRE</sub>  | LE register preset delay                   | 401                                     | _     | 545    | _     | 309              | _   | 381    | _   | ps   |

| t <sub>SU</sub>   | LE register setup time<br>before clock     | 260                                     | _     | 321    | _     | 271              | _   | 333    | _   | ps   |

| t <sub>H</sub>    | LE register hold time after clock          | 0                                       | _     | 0      | _     | 0                | _   | 0      | _   | ps   |

| t <sub>CO</sub>   | LE register<br>clock-to-output delay       |                                         | 380   |        | 494   |                  | 305 |        | 376 | ps   |

Table 3-18. LE Internal Timing Microparameters for MAX V Devices (Part 2 of 2)

| Symbol             | Parameter                      | 51  | //40Z/ 5M8<br>5M240Z/ |        | DZ/   | 5M1270Z/ 5M2210Z |       |        |       |      |

|--------------------|--------------------------------|-----|-----------------------|--------|-------|------------------|-------|--------|-------|------|

|                    |                                | C4  |                       | C5, I5 |       | C4               |       | C5, I5 |       | Unit |

|                    |                                | Min | Max                   | Min    | Max   | Min              | Max   | Min    | Max   |      |

| t <sub>CLKHL</sub> | Minimum clock high or low time | 253 | _                     | 339    | _     | 216              | _     | 266    | _     | ps   |

| t <sub>C</sub>     | Register control delay         | _   | 1,356                 | _      | 1,741 | _                | 1,114 |        | 1,372 | ps   |

Table 3–19. IOE Internal Timing Microparameters for MAX V Devices

|                       |                                                                | 51  | M40Z/ 5M8<br>5M240Z/ | 0Z/ 5M16<br>5M570Z | OZ/   |     |       |        |       |      |

|-----------------------|----------------------------------------------------------------|-----|----------------------|--------------------|-------|-----|-------|--------|-------|------|

| Symbol                | Parameter                                                      | C4  |                      | C5, I5             |       | C4  |       | C5, I5 |       | Unit |

|                       |                                                                | Min | Max                  | Min                | Max   | Min | Max   | Min    | Max   |      |

| t <sub>FASTIO</sub>   | Data output delay from adjacent LE to I/O block                | _   | 170                  |                    | 428   | _   | 207   | _      | 254   | ps   |

| t <sub>IN</sub>       | I/O input pad and buffer delay                                 | _   | 907                  | _                  | 986   | _   | 920   | _      | 1,132 | ps   |

| t <sub>GLOB</sub> (1) | I/O input pad and buffer<br>delay used as global<br>signal pin | _   | 2,261                | _                  | 3,322 | _   | 1,974 | _      | 2,430 | ps   |

| t <sub>IOE</sub>      | Internally generated output enable delay                       | _   | 530                  | _                  | 1,410 | _   | 374   | _      | 460   | ps   |

| t <sub>DL</sub>       | Input routing delay                                            | _   | 318                  | _                  | 509   | _   | 291   | _      | 358   | ps   |

| t <sub>oD</sub> (2)   | Output delay buffer and pad delay                              | _   | 1,319                | _                  | 1,543 | _   | 1,383 | _      | 1,702 | ps   |

| t <sub>XZ</sub> (3)   | Output buffer disable delay                                    | _   | 1,045                | _                  | 1,276 | _   | 982   | _      | 1,209 | ps   |

| t <sub>ZX</sub> (4)   | Output buffer enable delay                                     | _   | 1,160                | _                  | 1,353 | _   | 1,303 | _      | 1,604 | ps   |

#### Notes to Table 3–19:

- (1) Delay numbers for t<sub>GLOB</sub> differ for each device density and speed grade. The delay numbers for t<sub>GLOB</sub>, shown in Table 3–19, are based on a 5M240Z device target.

- (2) For more information about delay adders associated with different I/O standards, drive strengths, and slew rates, refer to Table 3–34 on page 3–24 and Table 3–35 on page 3–25.

- (3) For more information about  $t_{\chi Z}$  delay adders associated with different I/O standards, drive strengths, and slew rates, refer to Table 3–22 on page 3–15 and Table 3–23 on page 3–15.

- (4) For more information about  $t_{ZX}$  delay adders associated with different I/O standards, drive strengths, and slew rates, refer to Table 3–20 on page 3–14 and Table 3–21 on page 3–14.

The default slew rate setting for MAX V devices in the Quartus II design software is "fast".

Table 3-24. UFM Block Internal Timing Microparameters for MAX V Devices (Part 1 of 2)

|                   |                                                                                           | 51  | M40Z/ 5M8<br>5M240Z/ | OZ/ 5M16<br>5M57OZ | OZ/  |     | !   |     |      |      |

|-------------------|-------------------------------------------------------------------------------------------|-----|----------------------|--------------------|------|-----|-----|-----|------|------|

| Symbol            | Parameter                                                                                 | C   | 4                    | C5                 | , I5 | C   | 4   | C5  | , I5 | Unit |

|                   |                                                                                           | Min | Max                  | Min                | Max  | Min | Max | Min | Max  |      |

| t <sub>ACLK</sub> | Address register clock period                                                             | 100 | _                    | 100                | _    | 100 | _   | 100 | _    | ns   |

| t <sub>ASU</sub>  | Address register shift signal setup to address register clock                             | 20  | _                    | 20                 | _    | 20  | _   | 20  | _    | ns   |

| t <sub>AH</sub>   | Address register shift signal hold to address register clock                              | 20  | _                    | 20                 | _    | 20  | _   | 20  | _    | ns   |

| t <sub>ADS</sub>  | Address register data in setup to address register clock                                  | 20  | _                    | 20                 | _    | 20  | _   | 20  | _    | ns   |

| t <sub>ADH</sub>  | Address register data in hold from address register clock                                 | 20  | _                    | 20                 | _    | 20  | _   | 20  | _    | ns   |

| t <sub>DCLK</sub> | Data register clock period                                                                | 100 | _                    | 100                | _    | 100 | _   | 100 | _    | ns   |

| t <sub>DSS</sub>  | Data register shift signal setup to data register clock                                   | 60  | _                    | 60                 | _    | 60  | _   | 60  | _    | ns   |

| t <sub>DSH</sub>  | Data register shift signal<br>hold from data register<br>clock                            | 20  | _                    | 20                 | _    | 20  | _   | 20  | _    | ns   |

| t <sub>DDS</sub>  | Data register data in<br>setup to data register<br>clock                                  | 20  | _                    | 20                 | _    | 20  | _   | 20  | _    | ns   |

| t <sub>DDH</sub>  | Data register data in hold from data register clock                                       | 20  | _                    | 20                 | _    | 20  | _   | 20  | _    | ns   |

| t <sub>DP</sub>   | Program signal to data clock hold time                                                    | 0   | _                    | 0                  | _    | 0   | _   | 0   | _    | ns   |

| t <sub>PB</sub>   | Maximum delay between<br>program rising edge to<br>UFM busy signal rising<br>edge         | _   | 960                  | _                  | 960  | _   | 960 | _   | 960  | ns   |

| t <sub>BP</sub>   | Minimum delay allowed<br>from UFM busy signal<br>going low to program<br>signal going low | 20  | _                    | 20                 | _    | 20  | _   | 20  | _    | ns   |

| t <sub>PPMX</sub> | Maximum length of busy pulse during a program                                             | _   | 100                  | _                  | 100  | _   | 100 | _   | 100  | μs   |

Table 3–24. UFM Block Internal Timing Microparameters for MAX V Devices (Part 2 of 2)

|                   |                                                                                                       | 51  |     | 80Z/ 5M160<br>/ 5M570Z | DZ/  | 5M1270Z/ 5M2210Z |     |        |     |      |

|-------------------|-------------------------------------------------------------------------------------------------------|-----|-----|------------------------|------|------------------|-----|--------|-----|------|

| Symbol            | Parameter                                                                                             | C   | 4   | C5                     | , I5 | C4               |     | C5, I5 |     | Unit |

|                   |                                                                                                       | Min | Max | Min                    | Max  | Min              | Max | Min    | Max |      |

| t <sub>AE</sub>   | Minimum erase signal<br>to address clock hold<br>time                                                 | 0   | _   | 0                      | _    | 0                | _   | 0      | _   | ns   |

| t <sub>EB</sub>   | Maximum delay between<br>the erase rising edge to<br>the UFM busy signal<br>rising edge               | _   | 960 | _                      | 960  | _                | 960 | _      | 960 | ns   |

| t <sub>BE</sub>   | Minimum delay allowed<br>from the UFM busy<br>signal going low to<br>erase signal going low           | 20  | _   | 20                     | _    | 20               | _   | 20     | _   | ns   |

| t <sub>EPMX</sub> | Maximum length of busy pulse during an erase                                                          | _   | 500 | _                      | 500  | _                | 500 | _      | 500 | ms   |

| t <sub>DCO</sub>  | Delay from data register clock to data register output                                                | _   | 5   | _                      | 5    | _                | 5   | _      | 5   | ns   |

| t <sub>OE</sub>   | Delay from OSC_ENA<br>signal reaching UFM to<br>rising clock of OSC<br>leaving the UFM                | 180 | _   | 180                    | _    | 180              | _   | 180    | _   | ns   |

| t <sub>RA</sub>   | Maximum read access time                                                                              | _   | 65  | _                      | 65   | _                | 65  | _      | 65  | ns   |

| t <sub>oscs</sub> | Maximum delay between<br>the OSC_ENA rising edge<br>to the erase/program<br>signal rising edge        | 250 | _   | 250                    | _    | 250              | _   | 250    | _   | ns   |

| t <sub>oscн</sub> | Minimum delay allowed<br>from the<br>erase/program signal<br>going low to OSC_ENA<br>signal going low | 250 | _   | 250                    | _    | 250              | _   | 250    | _   | ns   |

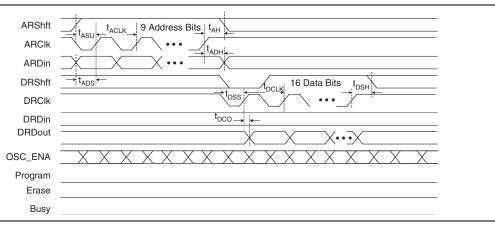

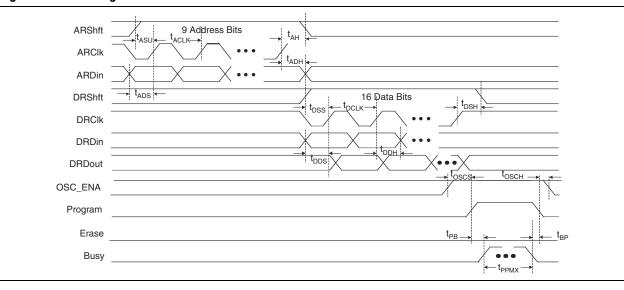

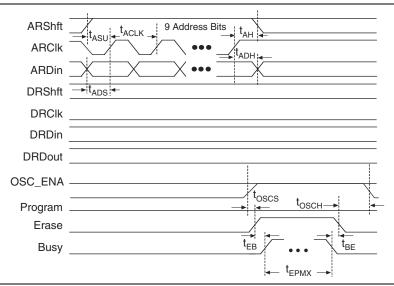

Figure 3–3 through Figure 3–5 show the read, program, and erase waveforms for UFM block timing parameters listed in Table 3–24.

Figure 3-3. UFM Read Waveform

Figure 3-4. UFM Program Waveform

Figure 3-5. UFM Erase Waveform

Table 3-25. Routing Delay Internal Timing Microparameters for MAX V Devices

| Routing            | 5   | M40Z/ 5M8<br>5M240Z/ | OZ/ 5M160<br>5M57OZ | <b>Z</b> / |     |     |     |      |    |

|--------------------|-----|----------------------|---------------------|------------|-----|-----|-----|------|----|

|                    | C   | 4                    | C5                  | , I5       | C   | 4   | C5  | Unit |    |

|                    | Min | Max                  | Min                 | Max        | Min | Max | Min | Max  |    |

| t <sub>C4</sub>    |     | 860                  | _                   | 1,973      | _   | 561 |     | 690  | ps |

| t <sub>R4</sub>    | _   | 655                  | _                   | 1,479      | _   | 445 | _   | 548  | ps |

| t <sub>LOCAL</sub> | _   | — 1,143              |                     | 2,947      | _   | 731 | _   | 899  | ps |

## **External Timing Parameters**

External timing parameters are specified by device density and speed grade. All external I/O timing parameters shown are for the 3.3-V LVTTL I/O standard with the maximum drive strength and fast slew rate. For external I/O timing using standards other than LVTTL or for different drive strengths, use the I/O standard input and output delay adders in Table 3–32 on page 3–23 through Table 3–36 on page 3–25.

For more information about each external timing parameters symbol, refer to *AN629: Understanding Timing in Altera CPLDs.*

Table 3–30 lists the external I/O timing parameters for the F324 package of the 5M1270Z device.

Table 3-30. Global Clock External I/O Timing Parameters for the 5M1270Z Device (Note 1), (2)

| Ob al            | Parameter.                                        | 0         | C   | 4     | C5  | , I5  | 11   |

|------------------|---------------------------------------------------|-----------|-----|-------|-----|-------|------|

| Symbol           | Parameter                                         | Condition | Min | Max   | Min | Max   | Unit |

| t <sub>PD1</sub> | Worst case pin-to-pin delay through one LUT       | 10 pF     | _   | 9.1   | _   | 11.2  | ns   |

| t <sub>PD2</sub> | Best case pin-to-pin delay through one LUT        | 10 pF     | _   | 4.8   | _   | 5.9   | ns   |

| t <sub>SU</sub>  | Global clock setup time                           | _         | 1.5 | _     | 1.9 | _     | ns   |

| t <sub>H</sub>   | Global clock hold time                            | _         | 0   | _     | 0   | _     | ns   |

| t <sub>CO</sub>  | Global clock to output delay                      | 10 pF     | 2.0 | 6.0   | 2.0 | 7.4   | ns   |

| t <sub>CH</sub>  | Global clock high time                            | _         | 216 | _     | 266 | _     | ps   |

| t <sub>CL</sub>  | Global clock low time                             | _         | 216 | _     | 266 | _     | ps   |

| t <sub>CNT</sub> | Minimum global clock period for 16-bit counter    | _         | 4.0 | _     | 5.0 | _     | ns   |

| f <sub>CNT</sub> | Maximum global clock frequency for 16-bit counter | _         | _   | 247.5 | _   | 201.1 | MHz  |

#### Notes to Table 3-30:

- (1) The maximum frequency is limited by the I/O standard on the clock input pin. The 16-bit counter critical delay performs faster than this global clock input pin maximum frequency.

- (2) Only applicable to the F324 package of the 5M1270Z device.

Table 3–31 lists the external I/O timing parameters for the 5M2210Z device.

Table 3-31. Global Clock External I/O Timing Parameters for the 5M2210Z Device (Note 1)

| Cumbal           | Parameter                                         | Condition | C   | 4     | C5  | , I5  | II-i-i-i |

|------------------|---------------------------------------------------|-----------|-----|-------|-----|-------|----------|

| Symbol           | Parameter                                         | Condition | Min | Max   | Min | Max   | Unit     |

| t <sub>PD1</sub> | Worst case pin-to-pin delay through one LUT       | 10 pF     | _   | 9.1   | _   | 11.2  | ns       |

| t <sub>PD2</sub> | Best case pin-to-pin delay through one LUT        | 10 pF     | _   | 4.8   | _   | 5.9   | ns       |

| t <sub>SU</sub>  | Global clock setup time                           | _         | 1.5 | _     | 1.9 | _     | ns       |

| t <sub>H</sub>   | Global clock hold time                            | _         | 0   | _     | 0   | _     | ns       |

| t <sub>co</sub>  | Global clock to output delay                      | 10 pF     | 2.0 | 6.0   | 2.0 | 7.4   | ns       |

| t <sub>CH</sub>  | Global clock high time                            | _         | 216 | _     | 266 | _     | ps       |

| t <sub>CL</sub>  | Global clock low time                             | _         | 216 | _     | 266 | _     | ps       |

| t <sub>CNT</sub> | Minimum global clock period for 16-bit counter    | _         | 4.0 | _     | 5.0 | _     | ns       |

| f <sub>CNT</sub> | Maximum global clock frequency for 16-bit counter | _         |     | 247.5 |     | 201.1 | MHz      |

#### Note to Table 3-31:

(1) The maximum frequency is limited by the I/O standard on the clock input pin. The 16-bit counter critical delay performs faster than this global clock input pin maximum frequency.

### **External Timing I/O Delay Adders**

The I/O delay timing parameters for the I/O standard input and output adders and the input delays are specified by speed grade, independent of device density.

Table 3–32 through Table 3–36 on page 3–25 list the adder delays associated with I/O pins for all packages. If you select an I/O standard other than 3.3-V LVTTL, add the input delay adder to the external  $t_{SU}$  timing parameters listed in Table 3–26 on page 3–20 through Table 3–31. If you select an I/O standard other than 3.3-V LVTTL with 16 mA drive strength and fast slew rate, add the output delay adder to the external  $t_{CO}$  and  $t_{PD}$  listed in Table 3–26 on page 3–20 through Table 3–31.

Table 3–32. External Timing Input Delay Adders for MAX V Devices

|                         |                            | 51  | M40Z/ 5M8<br>5M240Z/ | •      | DZ/   |     |       |        |       |      |

|-------------------------|----------------------------|-----|----------------------|--------|-------|-----|-------|--------|-------|------|

| I/0 St                  | tandard                    | C4  |                      | C5, I5 |       | C4  |       | C5, I5 |       | Unit |

|                         |                            | Min | Max                  | Min    | Max   | Min | Max   | Min    | Max   |      |

| 3.3-V LVTTL             | Without Schmitt<br>Trigger | _   | 0                    | _      | 0     | _   | 0     | _      | 0     | ps   |

| 3.3-V LVIIL             | With Schmitt<br>Trigger    | _   | 387                  | _      | 442   | _   | 480   | _      | 591   | ps   |

| 3.3-V LVCMOS            | Without Schmitt<br>Trigger | _   | 0                    | _      | 0     | _   | 0     | _      | 0     | ps   |

| 3.3-V LVGIVIUS          | With Schmitt<br>Trigger    | _   | 387                  | _      | 442   | _   | 480   | _      | 591   | ps   |

| 2.5-V LVTTL /           | Without Schmitt<br>Trigger | _   | 42                   | _      | 42    | _   | 246   | _      | 303   | ps   |

| LVCMOS                  | With Schmitt<br>Trigger    | _   | 429                  | _      | 483   | _   | 787   | _      | 968   | ps   |

| 1.8-V LVTTL /<br>LVCMOS | Without Schmitt<br>Trigger | _   | 378                  | _      | 368   | _   | 695   | _      | 855   | ps   |

| 1.5-V LVCMOS            | Without Schmitt<br>Trigger | _   | 681                  | _      | 658   | _   | 1,334 | _      | 1,642 | ps   |

| 1.2-V LVCMOS            | Without Schmitt<br>Trigger | _   | 1,055                | _      | 1,010 | _   | 2,324 | _      | 2,860 | ps   |

| 3.3-V PCI               | Without Schmitt<br>Trigger | _   | 0                    | _      | 0     | _   | 0     | _      | 0     | ps   |

Table 3–33. External Timing Input Delay t<sub>GLOB</sub> Adders for GCLK Pins for MAX V Devices (Part 1 of 2)

| I/O Standard |                            | 51  | //40Z/ 5M8<br>5M240Z/ |        | DZ/ |     |     |        |     |      |

|--------------|----------------------------|-----|-----------------------|--------|-----|-----|-----|--------|-----|------|

|              |                            | C4  |                       | C5, I5 |     | C4  |     | C5, I5 |     | Unit |

|              |                            | Min | Max                   | Min    | Max | Min | Max | Min    | Max |      |

| 3.3-V LVTTL  | Without Schmitt<br>Trigger | _   | 0                     | _      | 0   | _   | 0   | _      | 0   | ps   |

| 3.5-V LVIIL  | With Schmitt<br>Trigger    | _   | 387                   | _      | 442 | _   | 400 | _      | 493 | ps   |

Table 3–33. External Timing Input Delay  $t_{\text{GLOB}}$  Adders for GCLK Pins for MAX V Devices (Part 2 of 2)

|                         |                            | 51  | //40Z/ 5M8<br>5M240Z/ |        | DZ/   |     |       |        |       |      |

|-------------------------|----------------------------|-----|-----------------------|--------|-------|-----|-------|--------|-------|------|

| I/0 St                  | tandard                    | C4  |                       | C5, I5 |       | C4  |       | C5, I5 |       | Unit |

|                         |                            | Min | Max                   | Min    | Max   | Min | Max   | Min    | Max   |      |

| 3.3-V LVCMOS            | Without Schmitt<br>Trigger | _   | 0                     | _      | 0     | _   | 0     | _      | 0     | ps   |

| 3.3-V LVGIVIOS          | With Schmitt<br>Trigger    | _   | 387                   | _      | 442   | _   | 400   | _      | 493   | ps   |

| 2.5-V LVTTL /           | Without Schmitt<br>Trigger | _   | 242                   | _      | 242   | _   | 287   | _      | 353   | ps   |

| LVCMOS                  | With Schmitt<br>Trigger    | _   | 429                   | _      | 483   | _   | 550   | _      | 677   | ps   |

| 1.8-V LVTTL /<br>LVCMOS | Without Schmitt<br>Trigger |     | 378                   |        | 368   | _   | 459   | _      | 565   | ps   |

| 1.5-V LVCMOS            | Without Schmitt<br>Trigger | _   | 681                   | _      | 658   | _   | 1,111 | _      | 1,368 | ps   |

| 1.2-V LVCMOS            | Without Schmitt<br>Trigger | _   | 1,055                 | _      | 1,010 | _   | 2,067 | _      | 2,544 | ps   |

| 3.3-V PCI               | Without Schmitt<br>Trigger | _   | 0                     | _      | 0     | _   | 7     | _      | 9     | ps   |

Table 3–34. External Timing Output Delay and  $t_{\text{0D}}$  Adders for Fast Slew Rate for MAX V Devices

|                        |       | 51  | //40Z/ 5M8<br>5M240Z/ | 0Z/ 5M160<br>5M570Z | DZ/   |     | i     |        |       |      |

|------------------------|-------|-----|-----------------------|---------------------|-------|-----|-------|--------|-------|------|

| I/O Standard           |       | C   | 4                     | C5, I5              |       | C4  |       | C5, I5 |       | Unit |

|                        |       | Min | Max                   | Min                 | Max   | Min | Max   | Min    | Max   |      |

| 3.3-V LVTTL            | 16 mA | _   | 0                     | _                   | 0     | _   | 0     | _      | 0     | ps   |

| 3.3-V LVIIL            | 8 mA  | _   | 39                    | _                   | 58    | _   | 84    | _      | 104   | ps   |

| 3.3-V LVCMOS           | 8 mA  | _   | 0                     | _                   | 0     |     | 0     | _      | 0     | ps   |

| 3.3-V LVGIVIOS         | 4 mA  | _   | 39                    | _                   | 58    | _   | 84    | _      | 104   | ps   |

| 2.5-V LVTTL / LVCMOS   | 14 mA | _   | 122                   | _                   | 129   | _   | 158   | _      | 195   | ps   |

| 2.3-V LVIIL/LVGIVIOS   | 7 mA  | _   | 196                   | _                   | 188   | _   | 251   | _      | 309   | ps   |

| 1.8-V LVTTL / LVCMOS   | 6 mA  | _   | 624                   | _                   | 624   | _   | 738   | _      | 909   | ps   |

| 1.0-V LVIIL / LVGIVIOS | 3 mA  | _   | 686                   | —                   | 694   |     | 850   | —      | 1,046 | ps   |

| 1.5-V LVCMOS           | 4 mA  | _   | 1,188                 | _                   | 1,184 |     | 1,376 | _      | 1,694 | ps   |

| 1.5-V LVGIVIOS         | 2 mA  | _   | 1,279                 | _                   | 1,280 | _   | 1,517 | _      | 1,867 | ps   |

| 1.2-V LVCMOS           | 3 mA  | _   | 1,911                 | _                   | 1,883 | _   | 2,206 | _      | 2,715 | ps   |

| 3.3-V PCI              | 20 mA | _   | 39                    |                     | 58    |     | 4     |        | 5     | ps   |

| LVDS                   | _     | _   | 122                   | _                   | 129   | _   | 158   | _      | 195   | ps   |

| RSDS                   |       | _   | 122                   | _                   | 129   | _   | 158   | _      | 195   | ps   |

Table 3–35. External Timing Output Delay and  $t_{\text{0D}}$  Adders for Slow Slew Rate for MAX V Devices

|                        | I/O Standard |     | M40Z/ 5M8<br>5M240Z/ |        | OZ/    |     | !      |        |        |      |

|------------------------|--------------|-----|----------------------|--------|--------|-----|--------|--------|--------|------|

| I/O Standard           |              | C4  |                      | C5, I5 |        | C4  |        | C5, I5 |        | Unit |

|                        |              | Min | Max                  | Min    | Max    | Min | Max    | Min    | Max    |      |

| 3.3-V LVTTL            | 16 mA        | _   | 5,913                | _      | 6,043  | _   | 6,612  | _      | 6,293  | ps   |

| 3.3-V LVIIL            | 8 mA         | _   | 6,488                | _      | 6,645  | _   | 7,313  | _      | 6,994  | ps   |

| 3.3-V LVCMOS           | 8 mA         |     | 5,913                | _      | 6,043  |     | 6,612  |        | 6,293  | ps   |

| 3.3-V LVUIVIOS         | 4 mA         | _   | 6,488                | _      | 6,645  |     | 7,313  | _      | 6,994  | ps   |

| 2.5-V LVTTL / LVCMOS   | 14 mA        |     | 9,088                | _      | 9,222  |     | 10,021 |        | 9,702  | ps   |

| Z.J-V LVIIL / LVGIVIOS | 7 mA         | _   | 9,808                | _      | 9,962  | _   | 10,881 | _      | 10,562 | ps   |

| 1.8-V LVTTL / LVCMOS   | 6 mA         | _   | 21,758               | _      | 21,782 | _   | 21,134 | _      | 20,815 | ps   |

| 1.0-V LVIIL / LVGIVIOS | 3 mA         | _   | 23,028               | _      | 23,032 |     | 22,399 | _      | 22,080 | ps   |

| 1.5-V LVCMOS           | 4 mA         | _   | 39,068               | _      | 39,032 |     | 34,499 | _      | 34,180 | ps   |

| 1.0-V LVUIVIUO         | 2 mA         | _   | 40,578               | _      | 40,542 | _   | 36,281 | _      | 35,962 | ps   |

| 1.2-V LVCMOS           | 3 mA         | _   | 69,332               | _      | 70,257 | _   | 55,796 | _      | 55,477 | ps   |

| 3.3-V PCI              | 20 mA        | _   | 6,488                | _      | 6,645  | _   | 339    | _      | 418    | ps   |

Table 3-36. IOE Programmable Delays for MAX V Devices

| Parameter                                     | 51  | //40Z/ 5M8<br>5M240Z/ |     | DZ/    |     |       |     |        |    |

|-----------------------------------------------|-----|-----------------------|-----|--------|-----|-------|-----|--------|----|

|                                               | C4  |                       | C5  | C5, I5 |     | C4    |     | C5, I5 |    |

|                                               | Min | Max                   | Min | Max    | Min | Max   | Min | Max    |    |

| Input Delay from Pin to Internal<br>Cells = 1 | _   | 1,858                 | _   | 2,214  | _   | 1,592 | _   | 1,960  | ps |

| Input Delay from Pin to Internal<br>Cells = 0 | _   | 569                   | _   | 616    | _   | 115   | _   | 142    | ps |

## **Maximum Input and Output Clock Rates**

Table 3–37 and Table 3–38 list the maximum input and output clock rates for standard I/O pins in MAX V devices.

Table 3-37. Maximum Input Clock Rate for I/Os for MAX V Devices

| I/O Standard    |                         | 5M40Z/ 5M80Z/ 5M160Z/<br>5M240Z/ 5M570Z/5M1270Z/<br>5M2210Z | Unit |

|-----------------|-------------------------|-------------------------------------------------------------|------|

|                 |                         | C4, C5, I5                                                  |      |

| 3.3-V LVTTL     | Without Schmitt Trigger | 304                                                         | MHz  |

| 3.3-V LVIIL     | With Schmitt Trigger    | 304                                                         | MHz  |

| 2 2 V I V CM OS | Without Schmitt Trigger | 304                                                         | MHz  |

| 3.3-V LVCMOS    | With Schmitt Trigger    | 304                                                         | MHz  |

| 2.5-V LVTTL     | Without Schmitt Trigger | 304                                                         | MHz  |

|                 | With Schmitt Trigger    | 304                                                         | MHz  |

| 2.5-V LVCMOS    | Without Schmitt Trigger | 304                                                         | MHz  |

| 2.5-V LVGIVIOS  | With Schmitt Trigger    | 304                                                         | MHz  |

| 1.8-V LVTTL     | Without Schmitt Trigger | 200                                                         | MHz  |

| 1.8-V LVCMOS    | Without Schmitt Trigger | 200                                                         | MHz  |

| 1.5-V LVCMOS    | Without Schmitt Trigger | 150                                                         | MHz  |

| 1.2-V LVCMOS    | Without Schmitt Trigger | 120                                                         | MHz  |

| 3.3-V PCI       | Without Schmitt Trigger | 304                                                         | MHz  |

Table 3–38. Maximum Output Clock Rate for I/Os for MAX V Devices

| I/O Standard | 5M40Z/ 5M80Z/ 5M160Z/<br>5M240Z/ 5M570Z/5M1270Z/<br>5M2210Z | Unit |

|--------------|-------------------------------------------------------------|------|

|              | C4, C5, I5                                                  |      |

| 3.3-V LVTTL  | 304                                                         | MHz  |

| 3.3-V LVCMOS | 304                                                         | MHz  |

| 2.5-V LVTTL  | 304                                                         | MHz  |

| 2.5-V LVCMOS | 304                                                         | MHz  |

| 1.8-V LVTTL  | 200                                                         | MHz  |

| 1.8-V LVCMOS | 200                                                         | MHz  |

| 1.5-V LVCMOS | 150                                                         | MHz  |

| 1.2-V LVCMOS | 120                                                         | MHz  |

| 3.3-V PCI    | 304                                                         | MHz  |

| LVDS         | 304                                                         | MHz  |

| RSDS         | 200                                                         | MHz  |

Table 3–40 lists the emulated RSDS output timing specifications for MAX V devices.

Table 3-40. Emulated RSDS Output Timing Specifications for MAX V Devices

| Parameter               | Mode | 5M40Z/ 5M8<br>5M240Z/ 5M5<br>5M2 | Unit |      |

|-------------------------|------|----------------------------------|------|------|

| raiailletei             | Mode | C4, (                            | Unit |      |

|                         |      | Min                              | Max  |      |

|                         | ×10  | _                                | 200  | Mbps |

|                         | ×9   | _                                | 200  | Mbps |

|                         | ×8   | _                                | 200  | Mbps |

|                         | ×7   | _                                | 200  | Mbps |

| Data vata (1)           | ×6   | _                                | 200  | Mbps |

| Data rate (1)           | ×5   | _                                | 200  | Mbps |

|                         | ×4   | _                                | 200  | Mbps |

|                         | ×3   | _                                | 200  | Mbps |

|                         | ×2   | _                                | 200  | Mbps |

|                         | ×1   | _                                | 200  | Mbps |

| t <sub>DUTY</sub>       | _    | 45                               | 55   | %    |

| Total jitter <i>(2)</i> | _    | _                                | 0.2  | UI   |

| t <sub>RISE</sub>       | _    | _                                | 450  | ps   |

| t <sub>FALL</sub>       | _    | _                                | 450  | ps   |

#### Notes to Table 3-40:

<sup>(1)</sup> For the input clock pin to achieve 200 Mbps, use I/O standard with  $V_{\text{CCIO}}$  of 1.8 V and above.

$<sup>\</sup>begin{tabular}{ll} \end{tabular} \begin{tabular}{ll} \end{tabular} \beg$

### **JTAG Timing Specifications**

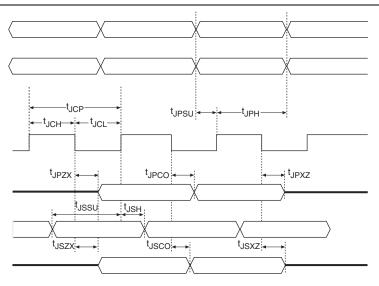

Figure 3–6 shows the timing waveform for the JTAG signals for the MAX V device family.

Figure 3–6. JTAG Timing Waveform for MAX V Devices

Table 3–41 lists the JTAG timing parameters and values for the MAX V device family.

Table 3-41. JTAG Timing Parameters for MAX V Devices (Part 1 of 2)

| Symbol                                          | Parameter                                               | Min  | Max | Unit |

|-------------------------------------------------|---------------------------------------------------------|------|-----|------|

|                                                 | TCK clock period for V <sub>CCIO1</sub> = 3.3 V         | 55.5 | _   | ns   |

| + (1)                                           | TCK clock period for $V_{CCIO1} = 2.5 \text{ V}$        | 62.5 | _   | ns   |

| t <sub>JCP</sub> (1)                            | TCK clock period for $V_{\text{CCIO1}} = 1.8 \text{ V}$ | 100  | _   | ns   |

|                                                 | TCK clock period for $V_{CCIO1} = 1.5 \text{ V}$        | 143  | _   | ns   |

| t <sub>JCH</sub>                                | TCK clock high time                                     | 20   | _   | ns   |

| t <sub>JCL</sub>                                | TCK clock low time                                      | 20   | _   | ns   |

| t <sub>JPSU</sub>                               | JTAG port setup time (2)                                | 8    | _   | ns   |

| t <sub>JPH</sub>                                | JTAG port hold time                                     | 10   | _   | ns   |

| t <sub>JPCO</sub> JTAG port clock to output (2) |                                                         | _    | 15  | ns   |

| t <sub>JPZX</sub>                               | JTAG port high impedance to valid output (2)            | _    | 15  | ns   |

| t <sub>JPXZ</sub>                               | JTAG port valid output to high impedance (2)            | _    | 15  | ns   |

| t <sub>JSSU</sub>                               | Capture register setup time                             | 8    | _   | ns   |

| t <sub>JSH</sub> Capture register hold time     |                                                         | 10   | _   | ns   |

| t <sub>JSCO</sub>                               | Update register clock to output                         |      | 25  | ns   |

| t <sub>JSZX</sub>                               | Update register high impedance to valid output          |      | 25  | ns   |

Table 3-41. JTAG Timing Parameters for MAX V Devices (Part 2 of 2)

| Symbol     | Parameter                                      | Min | Max | Unit |

|------------|------------------------------------------------|-----|-----|------|

| $t_{JSXZ}$ | Update register valid output to high impedance | _   | 25  | ns   |

#### Notes to Table 3-41:

- (1) Minimum clock period specified for 10 pF load on the TDO pin. Larger loads on TDO degrades the maximum TCK frequency.

- (2) This specification is shown for 3.3-V LVTTL/LVCMOS and 2.5-V LVTTL/LVCMOS operation of the JTAG pins. For 1.8-V LVTTL/LVCMOS and 1.5-V LVCMOS operation, the t<sub>JPSU</sub> minimum is 6 ns and t<sub>JPCO</sub>, t<sub>JPZX</sub>, and t<sub>JPXZ</sub> are maximum values at 35 ns.

## **Document Revision History**

Table 3–42 lists the revision history for this chapter.

Table 3-42. Document Revision History

| Date          | Version | Changes                                                     |

|---------------|---------|-------------------------------------------------------------|

| May 2011      | 1.2     | Updated Table 3–2, Table 3–15, Table 3–16, and Table 3–33.  |

| January 2011  | 1.1     | Updated Table 3–37, Table 3–38, Table 3–39, and Table 3–40. |

| December 2010 | 1.0     | Initial release.                                            |