Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| re Processor<br>re Size<br>eed<br>nnectivity | Active S08 8-Bit 50MHz                                                |

|----------------------------------------------|-----------------------------------------------------------------------|

| re Processor<br>re Size<br>eed<br>nnectivity | S08<br>8-Bit                                                          |

| re Size<br>eed<br>nnectivity                 | 8-Bit                                                                 |

| nnectivity                                   |                                                                       |

| nnectivity                                   | 50MHz                                                                 |

|                                              |                                                                       |

| do la consta                                 | I <sup>2</sup> C, LINbus, SCI, SPI                                    |

| ripherals                                    | LVD, PWM, WDT                                                         |

| mber of I/O                                  | 26                                                                    |

| gram Memory Size                             | 64KB (64K x 8)                                                        |

| gram Memory Type                             | FLASH                                                                 |

| PROM Size                                    | -                                                                     |

| M Size                                       | 4K x 8                                                                |

| tage - Supply (Vcc/Vdd)                      | 1.8V ~ 3.6V                                                           |

| ta Converters                                | A/D 10x12b                                                            |

| cillator Type                                | Internal                                                              |

| erating Temperature                          | -40°C ~ 85°C (TA)                                                     |

| unting Type                                  | Surface Mount                                                         |

| ckage / Case                                 | 32-LQFP                                                               |

| oplier Device Package                        | 32-LQFP (7x7)                                                         |

| chase URL                                    | https://www.e-xfl.com/product-detail/nxp-semiconductors/mc9s08qe64clc |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

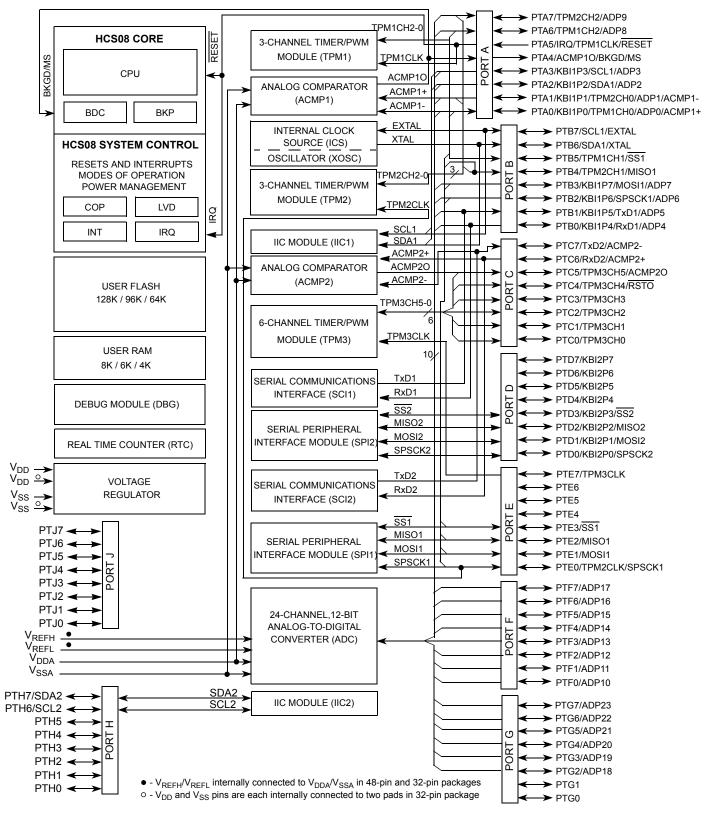

Figure 1. MC9S08QE128 Series Block Diagram

### MC9S08QE128 Series Comparison

# 1 MC9S08QE128 Series Comparison

The following table compares the various device derivatives available within the MC9S08QE128 series.

Table 1. MC9S08QE128 Series Features by MCU and Package

| Feature               | М   | C9S0        | 8QE1: | 28 | MC9S08QE96 |     |    |      | N     | MC9S08QE64 |    |    |  |

|-----------------------|-----|-------------|-------|----|------------|-----|----|------|-------|------------|----|----|--|

| Flash size (bytes)    |     | 131         | 072   |    | 98304      |     |    |      | 65536 |            |    |    |  |

| RAM size (bytes)      |     | 80          | 64    |    | 6016       |     |    | 4096 |       |            |    |    |  |

| Pin quantity          | 80  | 64          | 48    | 44 | 80         | 64  | 48 | 44   | 64    | 48         | 44 | 32 |  |

| ACMP1                 |     |             |       |    |            | ye  | es |      |       |            |    |    |  |

| ACMP2                 |     |             |       |    |            | уe  | es |      |       |            |    |    |  |

| ADC channels          | 24  | 24 22 10 10 |       |    | 24         | 22  | 10 | 10   | 22    | 10         | 10 | 10 |  |

| DBG                   |     |             |       |    |            | y€  | es |      |       |            |    |    |  |

| ICS                   |     |             |       |    |            | уe  | es |      |       |            |    |    |  |

| IIC1                  |     | yes         |       |    |            |     |    |      |       |            |    |    |  |

| IIC2                  | yes | yes         | no    | no | yes        | yes | no | no   | yes   | no         | no | no |  |

| IRQ                   |     |             |       |    |            | ye  | es |      |       |            |    |    |  |

| KBI                   | 16  | 16          | 16    | 16 | 16         | 16  | 16 | 16   | 16    | 16         | 16 | 12 |  |

| Port I/O <sup>1</sup> | 70  | 54          | 38    | 34 | 70         | 54  | 38 | 34   | 54    | 38         | 34 | 26 |  |

| RTC                   |     |             |       |    |            | уe  | es |      |       |            |    |    |  |

| SCI1                  |     |             |       |    |            | ye  | es |      |       |            |    |    |  |

| SCI2                  |     |             |       |    |            | уe  | es |      |       |            |    |    |  |

| SPI1                  |     |             |       |    |            | ye  | es |      |       |            |    |    |  |

| SPI2                  |     |             |       |    |            | ye  | es |      |       |            |    |    |  |

| TPM1 channels         |     |             |       |    |            | 3   | 3  |      |       |            |    |    |  |

| TPM2 channels         |     | 3           |       |    |            |     |    |      |       |            |    |    |  |

| TPM3 channels         |     | 6           |       |    |            |     |    |      |       |            |    |    |  |

| XOSC                  |     |             |       |    |            | уe  | es |      |       |            |    |    |  |

Port I/O count does not include the input only PTA5/IRQ/TPM1CLK/RESET or the output only PTA4/ACMP1O/BKGD/MS.

#### **Pin Assignments**

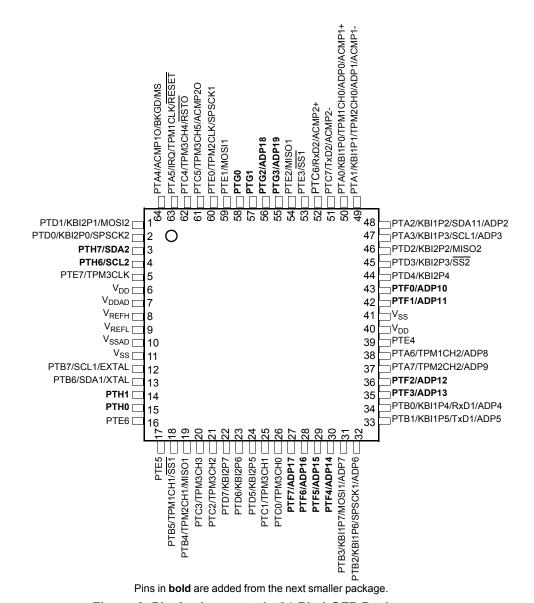

Figure 3. Pin Assignments in 64-Pin LQFP Package

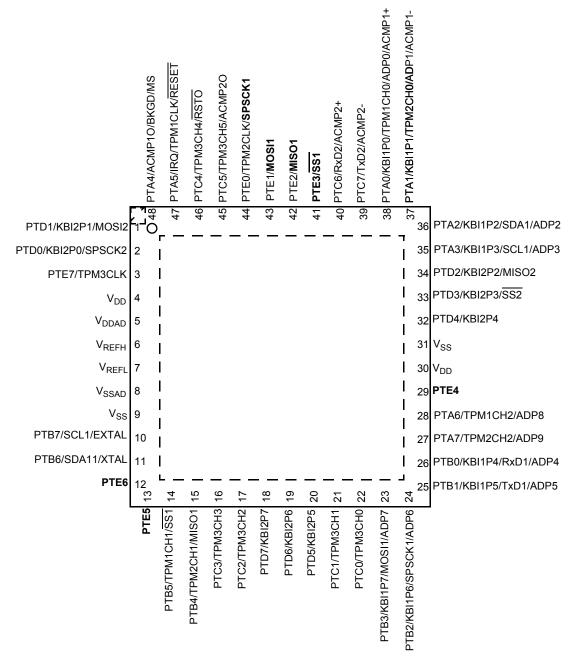

Figure 4. Pin Assignments in 48-Pin QFN Package

Power supply must maintain regulation within operating V<sub>DD</sub> range during instantaneous and operating maximum current conditions. If positive injection current (V<sub>In</sub> > V<sub>DD</sub>) is greater than I<sub>DD</sub>, the injection current may flow out of V<sub>DD</sub> and could result in external power supply going out of regulation. Ensure external V<sub>DD</sub> load will shunt current greater than maximum injection current. This will be the greatest risk when the MCU is not consuming power. Examples are: if no system clock is present, or if the clock rate is very low (which would reduce overall power consumption).

### 3.4 Thermal Characteristics

This section provides information about operating temperature range, power dissipation, and package thermal resistance. Power dissipation on I/O pins is usually small compared to the power dissipation in on-chip logic and voltage regulator circuits, and it is user-determined rather than being controlled by the MCU design. To take  $P_{I/O}$  into account in power calculations, determine the difference between actual pin voltage and  $V_{SS}$  or  $V_{DD}$  and multiply by the pin current for each I/O pin. Except in cases of unusually high pin current (heavy loads), the difference between pin voltage and  $V_{SS}$  or  $V_{DD}$  will be very small.

Rating **Symbol** Value Unit Operating temperature range (packaged) -40 to 85 °C  $T_A$ Maximum junction temperature 95 ٥С  $T_{JM}$ Thermal resistance Single-layer board 32-pin LQFP 82 °C/W 44-pin LQFP  $\theta_{\mathsf{JA}}$ 68 48-pin QFN 81 64-pin LQFP 69  $\theta_{\text{JA}}$ °C/W 80-pin LQFP 60 Thermal resistance Four-layer board 32-pin LQFP 54 44-pin LQFP °C/W 46  $\theta_{\mathsf{JA}}$ 48-pin QFN 26 64-pin LQFP 50 °C/W  $\theta_{JA}$ 47 80-pin LQFP

**Table 5. Thermal Characteristics**

The average chip-junction temperature  $(T_I)$  in °C can be obtained from:

$$T_{J} = T_{A} + (P_{D} \times \theta_{JA})$$

Eqn. 1

where:

$T_A = Ambient temperature, °C$

$\theta_{JA}$  = Package thermal resistance, junction-to-ambient, °C/W

$P_{\rm D} = P_{\rm int} + P_{\rm I/O}$

$P_{int} = I_{DD} \times V_{DD}$ , Watts — chip internal power

$P_{I/O}$  = Power dissipation on input and output pins — user determined

MC9S08QE128 Series Data Sheet, Rev. 7

For most applications,  $P_{I/O} \ll P_{int}$  and can be neglected. An approximate relationship between  $P_D$  and  $T_J$  (if  $P_{I/O}$  is neglected) is:

$$P_D = K \div (T_J + 273^{\circ}C)$$

Eqn. 2

Solving Equation 1 and Equation 2 for K gives:

$$K = P_D \times (T_\Delta + 273^{\circ}C) + \theta_{A\Delta} \times (P_D)^2$$

Eqn. 3

where K is a constant pertaining to the particular part. K can be determined from equation 3 by measuring  $P_D$  (at equilibrium) for a known  $T_A$ . Using this value of K, the values of  $P_D$  and  $T_J$  can be obtained by solving Equation 1 and Equation 2 iteratively for any value of  $T_A$ .

### 3.5 ESD Protection and Latch-Up Immunity

Although damage from electrostatic discharge (ESD) is much less common on these devices than on early CMOS circuits, normal handling precautions should be used to avoid exposure to static discharge. Qualification tests are performed to ensure that these devices can withstand exposure to reasonable levels of static without suffering any permanent damage.

All ESD testing is in conformity with AEC-Q100 Stress Test Qualification for Automotive Grade Integrated Circuits. During the device qualification ESD stresses were performed for the human body model (HBM), the machine model (MM) and the charge device model (CDM).

A device is defined as a failure if after exposure to ESD pulses the device no longer meets the device specification. Complete DC parametric and functional testing is performed per the applicable device specification at room temperature followed by hot temperature, unless specified otherwise in the device specification.

| Model         | Description                 | Symbol | Value        | Unit |

|---------------|-----------------------------|--------|--------------|------|

|               | Series resistance           | R1     | 1500         | Ω    |

| Human<br>Body | Storage capacitance         | С      | 100          | pF   |

|               | Number of pulses per pin    | _      | 3            |      |

|               | Series resistance           | R1     | 0            | Ω    |

| Machine       | Storage capacitance         | С      | 200          | pF   |

|               | Number of pulses per pin    | _      | 3            |      |

| Latch-up      | Minimum input voltage limit |        | <b>- 2.5</b> | V    |

| Lateri-up     | Maximum input voltage limit |        | 7.5          | V    |

Table 6. ESD and Latch-up Test Conditions

Table 7. ESD and Latch-Up Protection Characteristics

| No. | Rating <sup>1</sup>                       | Symbol           | Min    | Max | Unit |

|-----|-------------------------------------------|------------------|--------|-----|------|

| 1   | Human body model (HBM)                    | V <sub>HBM</sub> | ± 2000 | _   | V    |

| 2   | Machine model (MM)                        | V <sub>MM</sub>  | ± 200  | _   | V    |

| 3   | Charge device model (CDM)                 | $V_{CDM}$        | ± 500  | _   | V    |

| 4   | Latch-up current at T <sub>A</sub> = 85°C | I <sub>LAT</sub> | ± 100  | _   | mA   |

Parameter is achieved by design characterization on a small sample size from typical devices under typical conditions unless otherwise noted.

MC9S08QE128 Series Data Sheet, Rev. 7

14

Freescale Semiconductor

### 3.6 DC Characteristics

This section includes information about power supply requirements and I/O pin characteristics.

**Table 8. DC Characteristics**

| Num | С | Cha                                          | aracteristic                                       | Symbol                         | Condition                                         | Min                    | Typ <sup>1</sup> | Max                    | Unit |  |

|-----|---|----------------------------------------------|----------------------------------------------------|--------------------------------|---------------------------------------------------|------------------------|------------------|------------------------|------|--|

| 1   |   | Operating Voltage                            | )                                                  |                                |                                                   | 1.8 <sup>2</sup>       |                  | 3.6                    | V    |  |

|     | С | Output high voltage                          | All I/O pins, low-drive strength                   |                                | 1.8 V, I <sub>Load</sub> = –2 mA                  | V <sub>DD</sub> – 0.5  | _                | _                      |      |  |

| 2   | Р |                                              | All I/O pins,                                      | $V_{OH}$                       | 2.7 V, I <sub>Load</sub> = -10 mA                 | V <sub>DD</sub> – 0.5  | _                | _                      | V    |  |

|     | T |                                              | high-drive strength                                |                                | 2.3 V, I <sub>Load</sub> = -6 mA                  | V <sub>DD</sub> – 0.5  |                  | _                      |      |  |

|     | С |                                              |                                                    |                                | 1.8V, $I_{Load} = -3 \text{ mA}$                  | $V_{DD} - 0.5$         |                  | _                      |      |  |

| 3   | D | Output high current                          | Max total I <sub>OH</sub> for all ports            | I <sub>OHT</sub>               |                                                   | _                      |                  | 100                    | mA   |  |

|     | С | Output low voltage                           | All I/O pins, low-drive strength                   |                                | 1.8 V, I <sub>Load</sub> = 2 mA                   | _                      |                  | 0.5                    |      |  |

| 4   | Р |                                              | All I/O pins,                                      | $V_{OL}$                       | 2.7 V, I <sub>Load</sub> = 10 mA                  | _                      |                  | 0.5                    | V    |  |

|     | T |                                              | high-drive strength                                |                                | 2.3 V, I <sub>Load</sub> = 6 mA                   | _                      |                  | 0.5                    |      |  |

|     | С |                                              |                                                    |                                | 1.8 V, I <sub>Load</sub> = 3 mA                   |                        |                  | 0.5                    |      |  |

| 5   | D | Output low current                           | Max total I <sub>OL</sub> for all ports            | I <sub>OLT</sub>               |                                                   |                        | 1                | 100                    | mA   |  |

| 6   | Р | Input high                                   | all digital inputs                                 | V <sub>IH</sub>                | V <sub>DD</sub> > 2.7 V                           | 0.70 x V <sub>DD</sub> | _                | _                      |      |  |

|     | С | voltage                                      |                                                    | VIΗ                            | V <sub>DD</sub> > 1.8 V                           | 0.85 x V <sub>DD</sub> | _                | _                      | V    |  |

| 7   | Р | Input low voltage                            | all digital inputs                                 | V <sub>IL</sub>                | V <sub>DD</sub> > 2.7 V                           | _                      |                  | 0.35 x V <sub>DD</sub> |      |  |

| ,   | С |                                              |                                                    | ¥ IL                           | V <sub>DD</sub> >1.8 V                            |                        | l                | 0.30 x V <sub>DD</sub> |      |  |

| 8   | С | Input hysteresis                             | all digital inputs                                 | $V_{hys}$                      |                                                   | $0.06 \times V_{DD}$   |                  | _                      | mV   |  |

| 9   | Р | Input leakage current                        | all input only pins<br>(Per pin)                   | I <sub>In </sub>               | $V_{In} = V_{DD}$ or $V_{SS}$                     |                        | 1                | 1                      | μА   |  |

| 10  | Р | Hi-Z (off-state)<br>leakage current          | all input/output<br>(per pin)                      | I <sub>OZ </sub>               | $V_{In} = V_{DD}$ or $V_{SS}$                     | _                      | _                | 1                      | μА   |  |

| 11  | Р | Pull-up resistors                            | all digital inputs, when<br>enabled                | R <sub>PU</sub>                |                                                   | 17.5                   | _                | 52.5                   | kΩ   |  |

|     |   | DC injection                                 | Single pin limit                                   |                                |                                                   | -0.2                   |                  | 0.2                    | mA   |  |

| 12  | D | current <sup>3, 4, 5</sup>                   | Total MCU limit, includes sum of all stressed pins | I <sub>IC</sub>                | $V_{IN} < V_{SS}, V_{IN} > V_{DD}$                | <b>-</b> 5             | _                | 5                      | mA   |  |

| 13  | С | Input Capacitance                            | e, all pins                                        | C <sub>In</sub>                |                                                   | _                      |                  | 8                      | pF   |  |

| 14  | С | RAM retention vo                             | Itage                                              | V <sub>RAM</sub>               |                                                   | _                      | 0.6              | 1.0                    | V    |  |

| 15  | С | POR re-arm volta                             | ge <sup>6</sup>                                    | V <sub>POR</sub>               |                                                   | 0.9                    | 1.4              | 1.79                   | V    |  |

| 16  | D | POR re-arm time                              |                                                    | t <sub>POR</sub>               |                                                   | 10                     | _                | _                      | μS   |  |

| 17  | Р | Low-voltage deter<br>high range <sup>7</sup> | ction threshold —                                  | V <sub>LVDH</sub> <sup>8</sup> | V <sub>DD</sub> falling<br>V <sub>DD</sub> rising | 2.11<br>2.16           | 2.16<br>2.21     | 2.22<br>2.27           | V    |  |

### **Table 8. DC Characteristics (continued)**

| Num | С | Characteristic                                            | Symbol            | Condition                                         | Min          | Typ <sup>1</sup> | Max          | Unit |

|-----|---|-----------------------------------------------------------|-------------------|---------------------------------------------------|--------------|------------------|--------------|------|

| 18  | Р | Low-voltage detection threshold — low range <sup>7</sup>  | V <sub>LVDL</sub> | V <sub>DD</sub> falling<br>V <sub>DD</sub> rising | 1.80<br>1.86 | 1.82<br>1.90     | 1.91<br>1.99 | ٧    |

| 19  | Р | Low-voltage warning threshold — high range <sup>7</sup>   | V <sub>LVWH</sub> | V <sub>DD</sub> falling<br>V <sub>DD</sub> rising | 2.36<br>2.36 | 2.46<br>2.46     | 2.56<br>2.56 | ٧    |

| 20  | Р | Low-voltage warning threshold — low range <sup>7</sup>    | V <sub>LVWL</sub> | V <sub>DD</sub> falling<br>V <sub>DD</sub> rising | 2.11<br>2.16 | 2.16<br>2.21     | 2.22<br>2.27 | ٧    |

| 21  | С | Low-voltage inhibit reset/recover hysteresis <sup>7</sup> | V <sub>hys</sub>  |                                                   | _            | 50               | _            | mV   |

| 22  | Р | Bandgap Voltage Reference <sup>9</sup>                    | $V_{BG}$          |                                                   | 1.15         | 1.17             | 1.18         | V    |

<sup>&</sup>lt;sup>1</sup> Typical values are measured at 25°C. Characterized, not tested

<sup>&</sup>lt;sup>9</sup> Factory trimmed at  $V_{DD}$  = 3.0 V, Temp = 25°C

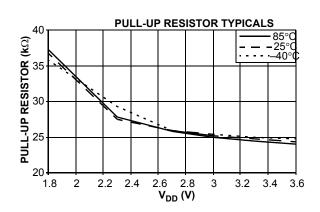

Figure 7. Pull-up and Pull-down Typical Resistor Values

<sup>&</sup>lt;sup>2</sup> As the supply voltage rises, the LVD circuit will hold the MCU in reset until the supply has risen above V<sub>LVDL</sub>.

$<sup>^3</sup>$  All functional non-supply pins are internally clamped to  $V_{SS}$  and  $V_{DD}$ .

<sup>&</sup>lt;sup>4</sup> Input must be current limited to the value specified. To determine the value of the required current-limiting resistor, calculate resistance values for positive and negative clamp voltages, then use the larger of the two values.

Power supply must maintain regulation within operating V<sub>DD</sub> range during instantaneous and operating maximum current conditions. If positive injection current (V<sub>In</sub> > V<sub>DD</sub>) is greater than I<sub>DD</sub>, the injection current may flow out of V<sub>DD</sub> and could result in external power supply going out of regulation. Ensure external V<sub>DD</sub> load will shunt current greater than maximum injection current. This will be the greatest risk when the MCU is not consuming power. Examples are: if no system clock is present, or if clock rate is very low (which would reduce overall power consumption).

<sup>&</sup>lt;sup>6</sup> Maximum is highest voltage that POR is guaranteed.

<sup>&</sup>lt;sup>7</sup> Low voltage detection and warning limits measured at 1 MHz bus frequency.

<sup>&</sup>lt;sup>8</sup> Run at 1 MHz bus frequency

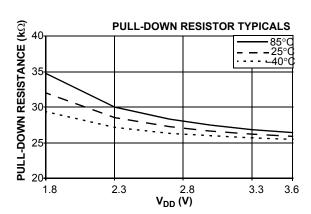

Figure 8. Typical Low-Side Driver (Sink) Characteristics — Low Drive (PTxDSn = 0)

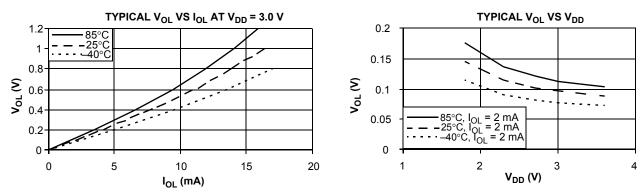

Figure 9. Typical Low-Side Driver (Sink) Characteristics — High Drive (PTxDSn = 1)

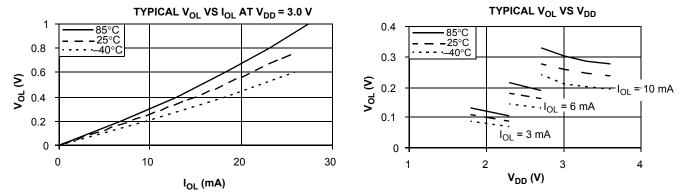

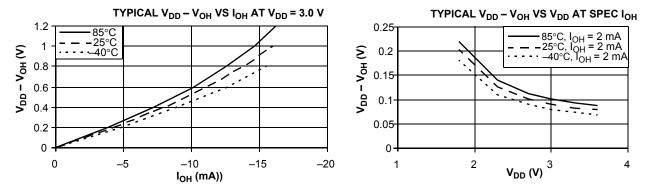

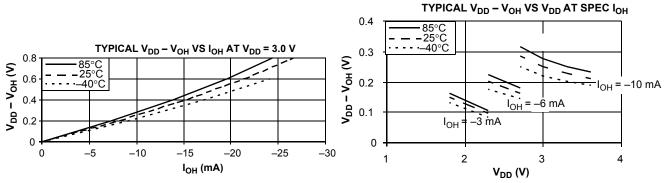

Figure 10. Typical High-Side (Source) Characteristics — Low Drive (PTxDSn = 0)

Figure 11. Typical High-Side (Source) Characteristics — High Drive (PTxDSn = 1)

# 3.7 Supply Current Characteristics

This section includes information about power supply current in various operating modes.

**Table 9. Supply Current Characteristics**

| Num | С | Parameter                                    | Symbol           | Bus<br>Freq     | V <sub>DD</sub><br>(V) | Typ <sup>1</sup> | Max  | Unit  | Temp<br>(°C) |

|-----|---|----------------------------------------------|------------------|-----------------|------------------------|------------------|------|-------|--------------|

|     | Р | Run supply current                           |                  | 25.165 MHz      |                        | 16               | 18   |       | -40 to 25    |

|     | Р | FEI mode, all modules on                     |                  | 25. 105 WII 12  |                        | 16               | 20   |       | 85           |

| 1   | Т |                                              | $RI_{DD}$        | 20 MHz          | 3                      | 14.4             | _    | mA    |              |

|     | Т |                                              |                  | 8 MHz           |                        | 6.5              | _    |       | -40 to 85    |

|     | Т |                                              |                  | 1 MHz           |                        | 1.4              | _    |       |              |

|     | С | Run supply current                           |                  | 25.165 MHz      |                        | 11.5             | 12.3 |       |              |

| 2   | Т | FEI mode, all modules off                    | RI <sub>DD</sub> | 20 MHz          | 3                      | 9.5              | _    | mA    | –40 to 85    |

| _   | Т |                                              |                  | 8 MHz           |                        | 4.6              | _    | 1117  | 40 10 00     |

|     | Т |                                              |                  | 1 MHz           |                        | 1.0              | _    |       |              |

| 3   | Т | Run supply current<br>LPS=0, all modules off | RI <sub>DD</sub> | 16 kHz<br>FBILP | 3                      | 152              | _    | μА    | –40 to 85    |

|     | Т |                                              | 14100            | 16 kHz<br>FBELP | Ü                      | 115              | _    | μΑ    | -40 to 65    |

|     | _ | Run supply current                           |                  |                 |                        | 04.0             | _    |       | 0 to 70      |

| 4   | Т | LPS=1, all modules off, running from Flash   | RI <sub>DD</sub> | 16 kHz          | 3                      | 21.9             | _    | μΑ    | -40 to 85    |

| '   | _ | Run supply current                           | טטייי            | FBELP           | Ü                      | 7                | _    | μι    | 0 to 70      |

|     | Т | LPS=1, all modules off, running from RAM     |                  |                 |                        | 7.3              |      |       | -40 to 85    |

|     | С | Wait mode supply current                     |                  | 25.165 MHz      |                        | 5.74             | 6    |       |              |

|     | Т | FEI mode, all modules off                    | $WI_{DD}$        | 20 MHz          | 3                      | 4.57             | _    | mA    | 40 to 85     |

|     | Т |                                              | טטיייי           | 8 MHz           |                        | 2                | _    | 111/5 | -40 10 03    |

|     | Т |                                              |                  | 1 MHz           |                        | 0.73             | _    |       |              |

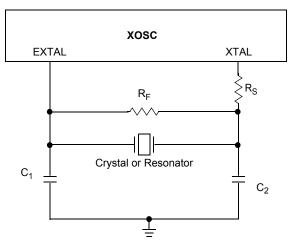

Figure 13. Typical Crystal or Resonator Circuit: High Range and Low Range/High Gain

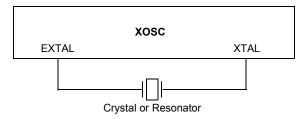

Figure 14. Typical Crystal or Resonator Circuit: Low Range/Low Gain

# 3.9 Internal Clock Source (ICS) Characteristics

Table 12. ICS Frequency Specifications (Temperature Range = -40 to 85°C Ambient)

| Num | С | Charac                                                                        | teristic                          | Symbol                   | Min    | Typ <sup>1</sup> | Max               | Unit              |

|-----|---|-------------------------------------------------------------------------------|-----------------------------------|--------------------------|--------|------------------|-------------------|-------------------|

| 1   | Р | Average internal reference frequency at V <sub>DD</sub> = 3.6 V and temperatu | f <sub>int_ft</sub>               | _                        | 32.768 | _                | kHz               |                   |

| 2   | Р | Internal reference frequency — L                                              | ser trimmed                       | f <sub>int_ut</sub>      | 31.25  | _                | 39.06             | kHz               |

| 3   | Т | Internal reference start-up time                                              |                                   | t <sub>IRST</sub>        | _      | 60               | 100               | μS                |

|     | Р | D00 t t f                                                                     | Low range (DRS=00)                |                          | 16     | _                | 20                |                   |

| 4   | Р | DCO output frequency range — trimmed <sup>2</sup>                             | Mid range (DRS=01)                | f <sub>dco_u</sub>       | 32     | _                | 40                | MHz               |

|     | P | ummod                                                                         | High range (DRS=10)               |                          | 48     | _                | 60                |                   |

|     | Р | DCO output frequency <sup>2</sup>                                             | Low range (DRS=00)                |                          | _      | 19.92            | _                 |                   |

| 5   | Р | Reference = 32768 Hz<br>and                                                   | Mid range (DRS=01)                | f <sub>dco_DMX32</sub>   | _      | 39.85            | _                 | MHz               |

|     | Р | DMX32 = 1                                                                     | High range (DRS=10)               |                          | _      | 59.77            | _                 |                   |

| 6   | С | Resolution of trimmed DCO outp temperature (using FTRIM)                      | Δf <sub>dco_res_t</sub>           | _                        | ± 0.1  | ± 0.2            | %f <sub>dco</sub> |                   |

| 7   | С | Resolution of trimmed DCO outp temperature (not using FTRIM)                  | ut frequency at fixed voltage and | $\Delta f_{dco\_res\_t}$ | _      | ± 0.2            | ± 0.4             | %f <sub>dco</sub> |

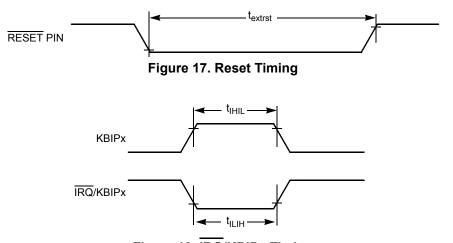

| Table 12 | Control   | Timina    | (continued) |

|----------|-----------|-----------|-------------|

| Table 13 | . Control | - i imina | (continued) |

| Num | С | Rating                                                                                                                                                          | Symbol                                | Min                           | Typ <sup>1</sup> | Max | Unit |

|-----|---|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|-------------------------------|------------------|-----|------|

| 7   | D | IRQ pulse width Asynchronous path <sup>2</sup> Synchronous path <sup>4</sup>                                                                                    | t <sub>ILIH,</sub> t <sub>IHIL</sub>  | 100<br>1.5 x t <sub>cyc</sub> | _<br>_           | _   | ns   |

| 8   | D | Keyboard interrupt pulse width Asynchronous path <sup>2</sup> Synchronous path <sup>4</sup>                                                                     | t <sub>ILIH</sub> , t <sub>IHIL</sub> | 100<br>1.5 x t <sub>cyc</sub> | _<br>_           | _   | ns   |

| 9   | С | Port rise and fall time — Low output drive (PTxDS = 0) (load = 50 pF) <sup>5</sup> Slew rate control disabled (PTxSE = 0) Slew rate control enabled (PTxSE = 1) | t <sub>Rise</sub> , t <sub>Fall</sub> |                               | 8<br>31          | -   | ns   |

| 9   |   | Port rise and fall time — High output drive (PTxDS = 1) (load = 50 pF) Slew rate control disabled (PTxSE = 0) Slew rate control enabled (PTxSE = 1)             | t <sub>Rise</sub> , t <sub>Fall</sub> |                               | 7<br>24          |     | ns   |

| 10  |   | Voltage regulator recovery time                                                                                                                                 | t <sub>VRR</sub>                      | _                             | 4                | _   | μS   |

<sup>&</sup>lt;sup>1</sup> Typical values are based on characterization data at  $V_{DD}$  = 3.0V, 25°C unless otherwise stated.

$<sup>^5</sup>$  Timing is shown with respect to 20%  $\rm V_{DD}$  and 80%  $\rm V_{DD}$  levels. Temperature range  $-40^{\circ}\rm C$  to 85°C.

Figure 18. IRQ/KBIPx Timing

<sup>&</sup>lt;sup>2</sup> This is the shortest pulse that is guaranteed to be recognized as a reset or interrupt pin request. Shorter pulses are not guaranteed to override reset requests from internal sources.

To enter BDM mode following a POR, BKGD/MS should be held low during the power-up and for a hold time of t<sub>MSH</sub> after V<sub>DD</sub> rises above V<sub>LVD</sub>.

<sup>&</sup>lt;sup>4</sup> This is the minimum pulse width that is guaranteed to pass through the pin synchronization circuitry. Shorter pulses may or may not be recognized. In stop mode, the synchronizer is bypassed so shorter pulses can be recognized in that case.

# 3.11 Analog Comparator (ACMP) Electricals

**Table 16. Analog Comparator Electrical Specifications**

| С | Characteristic                         | Symbol             | Min            | Typical | Max      | Unit |

|---|----------------------------------------|--------------------|----------------|---------|----------|------|

| D | Supply voltage                         | $V_{DD}$           | 1.80           | _       | 3.6      | V    |

| С | Supply current (active)                | I <sub>DDAC</sub>  | _              | 20      | 35       | μΑ   |

| D | Analog input voltage                   | $V_{AIN}$          | $V_{SS} - 0.3$ |         | $V_{DD}$ | V    |

| С | Analog input offset voltage            | $V_{AIO}$          |                | 20      | 40       | mV   |

| С | Analog comparator hysteresis           | $V_{H}$            | 3.0            | 9.0     | 15.0     | mV   |

| Р | Analog input leakage current           | I <sub>ALKG</sub>  | _              |         | 1.0      | μА   |

| С | Analog comparator initialization delay | t <sub>AINIT</sub> | _              | _       | 1.0      | μS   |

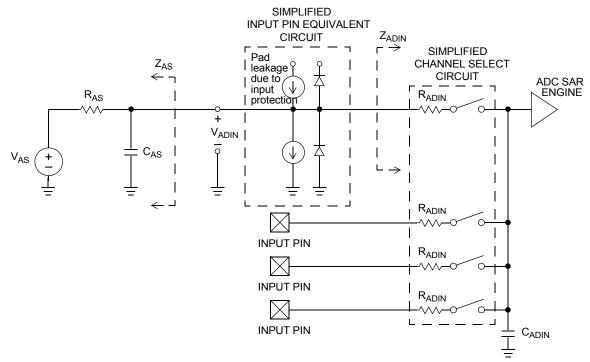

### 3.12 ADC Characteristics

**Table 17. 12-bit ADC Operating Conditions**

| С | Characteristic              | Conditions                                                                  | Symb              | Min               | Typ <sup>1</sup>  | Max               | Unit    | Comment         |

|---|-----------------------------|-----------------------------------------------------------------------------|-------------------|-------------------|-------------------|-------------------|---------|-----------------|

| D | Supply voltage              | Absolute                                                                    | $V_{DDAD}$        | 1.8               | _                 | 3.6               | V       |                 |

|   |                             | Delta to V <sub>DD</sub> (V <sub>DD</sub> -V <sub>DDAD</sub> ) <sup>2</sup> | $\Delta V_{DDAD}$ | -100              | 0                 | +100              | mV      |                 |

| D | Ground voltage              | Delta to V <sub>SS</sub> (V <sub>SS</sub> -V <sub>SSAD</sub> ) <sup>2</sup> | $\Delta V_{SSAD}$ | -100              | 0                 | +100              | mV      |                 |

| D | Ref Voltage High            |                                                                             | V <sub>REFH</sub> | 1.8               | $V_{DDAD}$        | $V_{DDAD}$        | V       |                 |

| D | Ref Voltage Low             |                                                                             | V <sub>REFL</sub> | V <sub>SSAD</sub> | V <sub>SSAD</sub> | V <sub>SSAD</sub> | V       |                 |

| D | Input Voltage               |                                                                             | V <sub>ADIN</sub> | V <sub>REFL</sub> | _                 | V <sub>REFH</sub> | V       |                 |

| С | Input<br>Capacitance        |                                                                             | C <sub>ADIN</sub> | _                 | 4.5               | 5.5               | pF      |                 |

| С | Input Resistance            |                                                                             | R <sub>ADIN</sub> | _                 | 5                 | 7                 | kΩ      |                 |

|   | Analog Source<br>Resistance | 12 bit mode<br>f <sub>ADCK</sub> > 4MHz<br>f <sub>ADCK</sub> < 4MHz         | R <sub>AS</sub>   | _                 | _                 | 2<br>5            |         | External to MCU |

| С |                             | 10 bit mode<br>f <sub>ADCK</sub> > 4MHz<br>f <sub>ADCK</sub> < 4MHz         |                   | _                 | _                 | 5<br>10           | kΩ      |                 |

|   |                             | 8 bit mode (all valid f <sub>ADCK</sub> )                                   |                   | _                 |                   | 10                |         |                 |

| D |                             | High Speed (ADLPC=0)                                                        | f <sub>ADCK</sub> | 0.4               | _                 | 8.0               | MHz     |                 |

|   | Clock Freq.                 | Low Power (ADLPC=1)                                                         |                   | 0.4               | _                 | 4.0               | IVII IZ |                 |

Typical values assume V<sub>DDAD</sub> = 3.0V, Temp = 25°C, f<sub>ADCK</sub>=1.0MHz unless otherwise stated. Typical values are for reference only and are not tested in production.

<sup>&</sup>lt;sup>2</sup> DC potential difference.

Figure 25. ADC Input Impedance Equivalency Diagram

Table 18. 12-bit ADC Characteristics ( $V_{REFH} = V_{DDAD}$ ,  $V_{REFL} = V_{SSAD}$ )

| Characteristic                                  | Conditions              | С | Symb               | Min  | Typ <sup>1</sup> | Max | Unit   | Comment                   |

|-------------------------------------------------|-------------------------|---|--------------------|------|------------------|-----|--------|---------------------------|

| Supply Current<br>ADLPC=1<br>ADLSMP=1<br>ADCO=1 |                         | Т | I <sub>DDAD</sub>  | _    | 120              | _   | μА     |                           |

| Supply Current<br>ADLPC=1<br>ADLSMP=0<br>ADCO=1 |                         | Т | I <sub>DDAD</sub>  | _    | 202              | _   | μА     |                           |

| Supply Current<br>ADLPC=0<br>ADLSMP=1<br>ADCO=1 |                         | Т | I <sub>DDAD</sub>  | _    | 288              | _   | μА     |                           |

| Supply Current<br>ADLPC=0<br>ADLSMP=0<br>ADCO=1 |                         | D | I <sub>DDAD</sub>  | _    | 0.532            | 1   | mA     |                           |

| Supply Current                                  | Stop, Reset, Module Off | Р | I <sub>DDAD</sub>  | _    | 0.007            | 0.8 | μΑ     |                           |

| ADC<br>Asynchronous<br>Clock Source             | High Speed (ADLPC=0)    | Р | f <sub>ADACK</sub> | 2    | 3.3              | 5   | NAL I— | $t_{ADACK} = 1/f_{ADACK}$ |

|                                                 | Low Power (ADLPC=1)     | Р |                    | 1.25 | 2                | 3.3 | MHz    |                           |

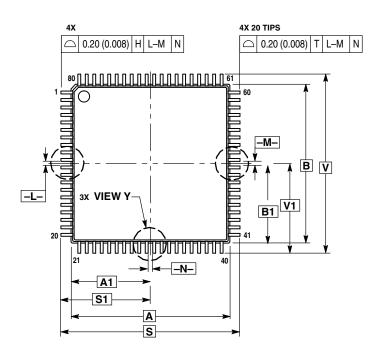

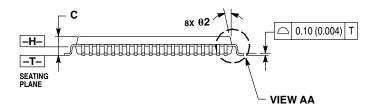

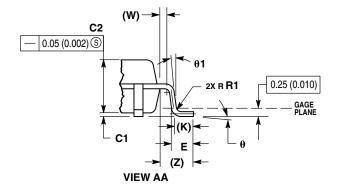

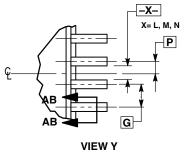

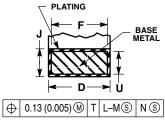

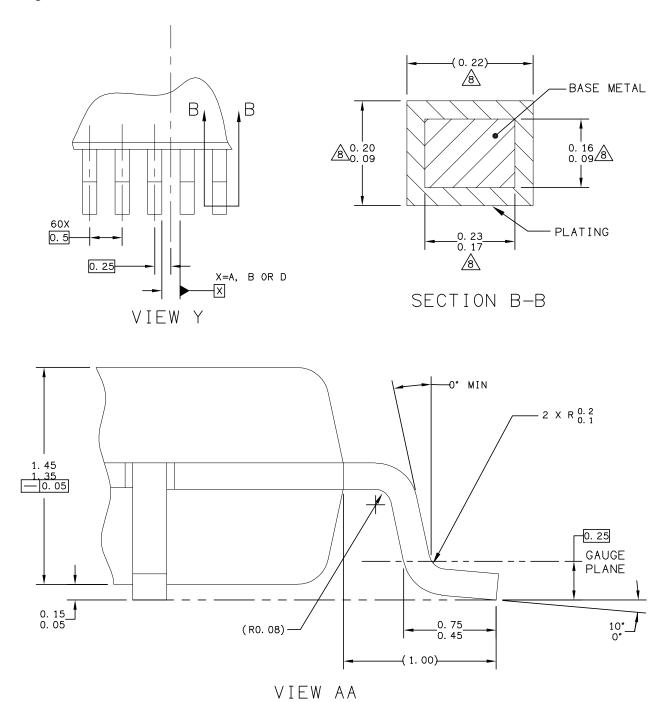

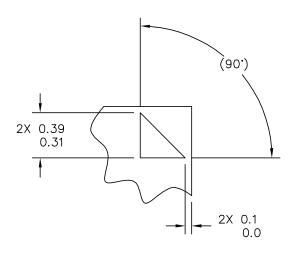

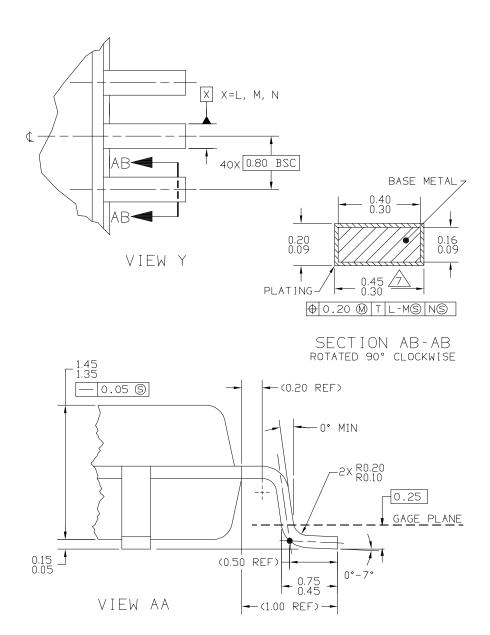

**DATE 09/21/95 CASE 917A-02 ISSUE C**

**SECTION AB-AB** ROTATED 90 ° CLOCKWISE

- NOTES:

1. DIMENSIONING AND TOLERANCING PER ANSI Y14.5M, 1982. CONTROLLING DIMENSION: MILLIMETER.

- DATUM PLANE -H- IS LOCATED AT BOTTOM OF LEAD AND IS COINCIDENT WITH THE LEAD WHERE THE LEAD EXITS THE PLASTIC BODY AT

- THE BOTTOM OF THE PARTING LINE.

DATUMS -L-, -M- AND -N- TO BE DETERMINED

AT DATUM PLANE -H-.

- DIMENSIONS S AND V TO BE DETERMINED AT SEATING PLANE -T-.

6. DIMENSIONS A AND B DO NOT INCLUDE MOLD

- PROTRUSION. ALLOWABLE PROTRUSION IS 0.250 (0.010) PER SIDE. DIMENSIONS A AND B DO INCLUDE MOLD MISMATCH AND ARE DETERMINED AT DATUM PLANE -H-.

- DIMENSION D DOES NOT INCLUDE DAMBAR

PROTRUSION. DAMBAR PROTRUSION SHALL NOT CAUSE THE LEAD WIDTH TO EXCEED 0.460 (0.018), MINIMUM SPACE BETWEEN PROTRUSION AND ADJACENT LEAD OR PROTRUSION 0.07 (0.003).

|     | MILLIN    | IETERS   | INCHES    |           |  |  |

|-----|-----------|----------|-----------|-----------|--|--|

| DIM | MIN       | MAX      | MIN       | MAX       |  |  |

| Α   | 14.00 BSC |          | 0.551 BSC |           |  |  |

| A1  | 7.00      | BSC      | 0.276 BSC |           |  |  |

| В   | 14.00     | BSC      | 0.551 BSC |           |  |  |

| B1  | 7.00      | BSC      | 0.276     | BSC       |  |  |

| С   |           | 1.60     |           | 0.063     |  |  |

| C1  | 0.04      | 0.24     | 0.002     | 0.009     |  |  |

| C2  | 1.30      | 1.50     | 0.051     | 0.059     |  |  |

| D   | 0.22      | 0.38     | 0.009     | 0.015     |  |  |

| Е   | 0.40      | 0.75     | 0.016     | 0.030     |  |  |

| F   | 0.17      | 0.33     | 0.007     | 0.013     |  |  |

| G   | 0.65      | BSC      | 0.026 BSC |           |  |  |

| J   | 0.09      | 0.27     | 0.004     | 0.011     |  |  |

| K   | 0.50      | REF      | 0.020     | REF       |  |  |

| Р   | 0.325     | BSC      | 0.013 REF |           |  |  |

| R1  | 0.10      | 0.20     | 0.004     | 0.008     |  |  |

| S   | 16.00     | BSC      | 0.630 BSC |           |  |  |

| S1  | 8.00      | BSC      | 0.315     | BSC       |  |  |

| U   | 0.09      | 0.16     | 0.004     | 0.006     |  |  |

| ٧   | 16.00     | BSC      | 0.630 BSC |           |  |  |

| V1  | 8.00      | 8.00 BSC |           | 0.315 BSC |  |  |

| W   | 0.20      | 0.20 REF |           | 0.008 REF |  |  |

| Z   |           | REF      |           | REF       |  |  |

| 0   | 0 °       | 10°      | 0 °       | 10°       |  |  |

| 01  | 0°        |          | 0 °       |           |  |  |

| 02  | 9°        | 14°      | 9°        | 14°       |  |  |

Figure 26. 80-pin LQFP Package Drawing (Case 917A, Doc #98ASS23237W)

| © FREESCALE SEMICONDUCTOR, INC. ALL RIGHTS RESERVED. | MECHANICA   | L OUTLINE      | PRINT VERSION NO | OT TO SCALE |

|------------------------------------------------------|-------------|----------------|------------------|-------------|

| TITLE: 64LD LQFP,                                    | DOCUMENT NO | ): 98ASS23234W | REV: D           |             |

| 10 X 10 X 1.4 P                                      | CASE NUMBER | R: 840F-02     | 06 APR 2005      |             |

| 0.5 PITCH, CASE OU                                   | ITLINE      | STANDARD: JE   | DEC MS-026 BCD   |             |

Figure 28. 64-pin LQFP Package Drawing (Case 840F, Doc #98ASS23234W), Sheet 2 of 3

MC9S08QE128 Series Data Sheet, Rev. 7

DETAIL N

PREFERRED CORNER CONFIGURATION

DETAIL M

PREFERED PIN 1 BACKSIDE IDENTIFIER

| © FREESCALE SEMICONDUCTOR, INC. ALL RIGHTS RESERVED. | MECHANICA                        | L OUTLINE    | PRINT VERSION NO  | T TO SCALE |

|------------------------------------------------------|----------------------------------|--------------|-------------------|------------|

| TITLE: THERMALLY ENHANCED                            | QUAD                             | DOCUMENT NO  | ): 98ARH99048A    | REV: F     |

| FLAT NON-LEADED PACKA                                | CASE NUMBER: 1314-05 05 DEC 2005 |              |                   |            |

| 48 TERMINAL, 0.5 PITCH (7                            | ′ X / X 1)                       | STANDARD: JE | DEC-MO-220 VKKD-2 | 2          |

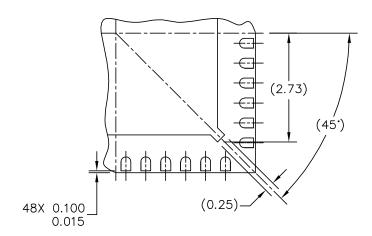

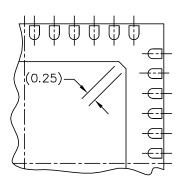

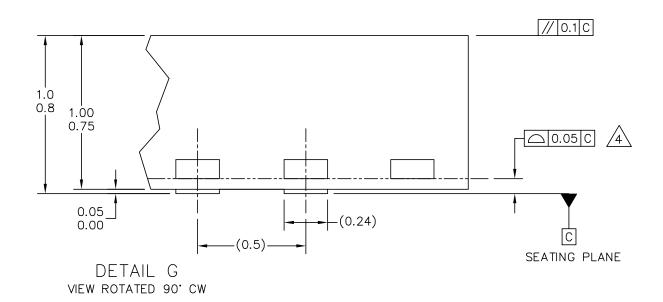

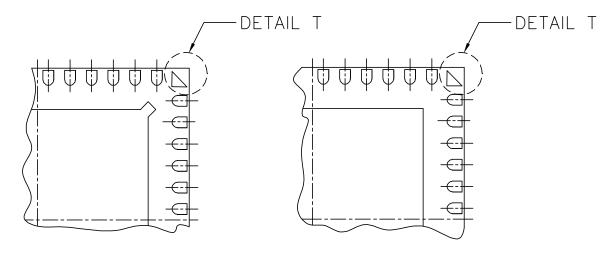

Figure 31. 48-pin QFN Package Drawing (Case 1314, Doc #98ARH99048A), Sheet 2 of 3

MC9S08QE128 Series Data Sheet, Rev. 7

DETAIL M

PIN 1 BACKSIDE IDENTIFIER OPTION

DETAIL M

PIN 1 BACKSIDE IDENTIFIER OPTION

DETAIL T

NOTES:

- 1. DIMENSIONS ARE IN MILLIMETERS.

- 2. INTERPRET DIMENSIONS AND TOLERANCES PER ASME Y14.5M-1994.

- 3. THE COMPLETE JEDEC DESIGNATOR FOR THIS PACKAGE IS: HF-PQFN.

4. COPLANARITY APPLIES TO LEADS, CORNER LEADS, AND DIE ATTACH PAD.

5. MIN METAL GAP SHOULD BE 0.2MM.

| © FREESCALE SEMICONDUCTOR, INC. ALL RIGHTS RESERVED. | MECHANICA                       | L OUTLINE      | PRINT VERSION NO  | T TO SCALE |

|------------------------------------------------------|---------------------------------|----------------|-------------------|------------|

| TITLE: THERMALLY ENHANCED                            | DOCUMENT NO                     | ): 98ARH99048A | REV: F            |            |

| FLAT NON-LEADED PACKA                                | CASE NUMBER: 1314-05 05 DEC 200 |                |                   |            |

| 48 TERMINAL, 0.5 PITCH (7                            | 7 X 7 X 1)                      | STANDARD: JE   | DEC-MO-220 VKKD-2 | 2          |

Figure 32. 48-pin QFN Package Drawing (Case 1314, Doc #98ARH99048A), Sheet 3 of 3

MC9S08QE128 Series Data Sheet, Rev. 7

Figure 34. 44-pin LQFP Package Drawing (Case 824D, Doc #98ASS23225W), Sheet 2 of 3

MC9S08QE128 Series Data Sheet, Rev. 7

#### How to Reach Us:

Home Page:

www.freescale.com

E-mail:

support@freescale.com

**USA/Europe or Locations Not Listed:**

Freescale Semiconductor Technical Information Center, EL516 2100 East Elliot Road Tempe, Arizona 85284 1-800-521-6274 or +1-480-768-2130 www.freescale.com/support

Europe, Middle East, and Africa: Freescale Halbleiter Deutschland GmbH Technical Information Center Schatzbogen 7 81829 Muenchen, Germany +44 1296 380 456 (English) +46 8 52200080 (English) +49 89 92103 559 (German) +33 1 69 35 48 48 (French) www.freescale.com/support

#### Japan:

Freescale Semiconductor Japan Ltd. Headquarters ARCO Tower 15F 1-8-1, Shimo-Meguro, Meguro-ku, Tokyo 153-0064 Japan 0120 191014 or +81 3 5437 9125 support.japan@freescale.com

#### Asia/Pacific:

Freescale Semiconductor China Ltd. Exchange Building 23F No. 118 Jianguo Road Chaoyang District Beijing 100022 China +86 10 5879 8000 support.asia@freescale.com

For Literature Requests Only:

Freescale Semiconductor Literature Distribution Center

P.O. Box 5405

Denver, Colorado 80217

1-800-441-2447 or +1-303-675-2140

Fax: +1-303-675-2150

LDCForFreescaleSemiconductor@hibbertgroup.com

Document Number: MC9S08QE128

Rev. 7 10/2008 Information in this document is provided solely to enable system and software implementers to use Freescale Semiconductor products. There are no express or implied copyright licenses granted hereunder to design or fabricate any integrated circuits or integrated circuits based on the information in this document.

Freescale Semiconductor reserves the right to make changes without further notice to any products herein. Freescale Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Freescale Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters that may be provided in Freescale Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals", must be validated for each customer application by customer's technical experts. Freescale Semiconductor does not convey any license under its patent rights nor the rights of others. Freescale Semiconductor products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Freescale Semiconductor product could create a situation where personal injury or death may occur. Should Buyer purchase or use Freescale Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and hold Freescale Semiconductor and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Freescale Semiconductor was negligent regarding the design or manufacture of the part.

RoHS-compliant and/or Pb-free versions of Freescale products have the functionality and electrical characteristics as their non-RoHS-compliant and/or non-Pb-free counterparts. For further information, see <a href="http://www.freescale.com">http://www.freescale.com</a> or contact your Freescale sales representative.

For information on Freescale's Environmental Products program, go to http://www.freescale.com/epp.

Freescale  $^{\text{TM}}$  and the Freescale logo are trademarks of Freescale Semiconductor, Inc. All other product or service names are the property of their respective owners.

© Freescale Semiconductor, Inc. 2008. All rights reserved.