Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                     |

|----------------------------|------------------------------------------------------------|

| Core Processor             | S08                                                        |

| Core Size                  | 8-Bit                                                      |

| Speed                      | 50MHz                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SCI, SPI                         |

| Peripherals                | LVD, PWM, WDT                                              |

| Number of I/O              | 34                                                         |

| Program Memory Size        | 96КВ (96К × 8)                                             |

| Program Memory Type        | FLASH                                                      |

| EEPROM Size                | -                                                          |

| RAM Size                   | 6K x 8                                                     |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                |

| Data Converters            | A/D 10x12b                                                 |

| Oscillator Type            | Internal                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                          |

| Mounting Type              | Surface Mount                                              |

| Package / Case             | 44-LQFP                                                    |

| Supplier Device Package    | 44-LQFP (10x10)                                            |

| Purchase URL               | https://www.e-xfl.com/pro/item?MUrl=&PartUrl=mc9s08qe96cld |

|                            |                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

\_\_\_\_\_

| Part Number   | Package Description | Original (gold wire)<br>package document number | Current (copper wire)<br>package document number |

|---------------|---------------------|-------------------------------------------------|--------------------------------------------------|

| MC68HC908JW32 | 48 QFN              | 98ARH99048A                                     | 98ASA00466D                                      |

| MC9S08AC16    |                     |                                                 |                                                  |

| MC9S908AC60   |                     |                                                 |                                                  |

| MC9S08AC128   |                     |                                                 |                                                  |

| MC9S08AW60    |                     |                                                 |                                                  |

| MC9S08GB60A   |                     |                                                 |                                                  |

| MC9S08GT16A   |                     |                                                 |                                                  |

| MC9S08JM16    |                     |                                                 |                                                  |

| MC9S08JM60    |                     |                                                 |                                                  |

| MC9S08LL16    |                     |                                                 |                                                  |

| MC9S08QE128   |                     |                                                 |                                                  |

| MC9S08QE32    |                     |                                                 |                                                  |

| MC9S08RG60    |                     |                                                 |                                                  |

| MCF51CN128    |                     |                                                 |                                                  |

| MC9RS08LA8    | 48 QFN              | 98ARL10606D                                     | 98ASA00466D                                      |

| MC9S08GT16A   | 32 QFN              | 98ARH99035A                                     | 98ASA00473D                                      |

| MC9S908QE32   | 32 QFN              | 98ARE10566D                                     | 98ASA00473D                                      |

| MC9S908QE8    | 32 QFN              | 98ASA00071D                                     | 98ASA00736D                                      |

| MC9S08JS16    | 24 QFN              | 98ARL10608D                                     | 98ASA00734D                                      |

| MC9S08QB8     |                     |                                                 |                                                  |

| MC9S08QG8     | 24 QFN              | 98ARL10605D                                     | 98ASA00474D                                      |

| MC9S08SH8     | 24 QFN              | 98ARE10714D                                     | 98ASA00474D                                      |

| MC9RS08KB12   | 24 QFN              | 98ASA00087D                                     | 98ASA00602D                                      |

| MC9S08QG8     | 16 QFN              | 98ARE10614D                                     | 98ASA00671D                                      |

| MC9RS08KB12   | 8 DFN               | 98ARL10557D                                     | 98ASA00672D                                      |

| MC9S08QG8     |                     |                                                 |                                                  |

| MC9RS08KA2    | 6 DFN               | 98ARL10602D                                     | 98ASA00735D                                      |

## Freescale Semiconductor

Data Sheet: Technical Data

An Energy Efficient Solution by Freescale

# MC9S08QE128 Series

Covers: MC9S08QE128, MC9S08QE96, MC9S08QE64

- 8-Bit HCS08 Central Processor Unit (CPU)

- Up to 50.33-MHz HCS08 CPU above 2.4V, 40-MHz CPU above 2.1V, and 20-MHz CPU above 1.8V, across temperature range

- HC08 instruction set with added BGND instruction

- Support for up to 32 interrupt/reset sources

- On-Chip Memory

- Flash read/program/erase over full operating voltage and temperature

- Random-access memory (RAM)

- Security circuitry to prevent unauthorized access to RAM and flash contents

- Power-Saving Modes

- Two low power stop modes; reduced power wait mode

- Peripheral clock enable register can disable clocks to unused modules, reducing currents; allows clocks to remain enabled to specific peripherals in stop3 mode

- Very low power external oscillator can be used in stop3 mode to provide accurate clock to active peripherals

- Very low power real time counter for use in run, wait, and stop modes with internal and external clock sources

- $6 \,\mu s$  typical wake up time from stop modes

- Clock Source Options

- Oscillator (XOSC) Loop-control Pierce oscillator; Crystal or ceramic resonator range of 31.25 kHz to 38.4 kHz or 1 MHz to 16 MHz

- Internal Clock Source (ICS) FLL controlled by internal or external reference; precision trimming of internal reference allows 0.2% resolution and 2% deviation; supports CPU freq. from 2 to 50.33 MHz

- System Protection

- Watchdog computer operating properly (COP) reset with option to run from dedicated 1-kHz internal clock source or bus clock

- Low-voltage detection with reset or interrupt; selectable trip points

- Illegal opcode detection with reset

- Flash block protection

- Development Support

- Single-wire background debug interface

- Breakpoint capability to allow single breakpoint setting during in-circuit debugging (plus two more breakpoints)

- On-chip in-circuit emulator (ICE) debug module containing two comparators and nine trigger modes.

# MC9S08QE128

Document Number: MC9S08QE128

80-LQFP Case 917A 14 mm<sup>2</sup>

48-QFN Case 1314 7 mm<sup>2</sup> 64-LQFP Case 840F 10 mm<sup>2</sup> 44-LQFP Case 824D 10 mm<sup>2</sup>

Rev. 7, 10/2008

Eight deep FIFO for storing change-of-flow addresses and event-only data. Debug module supports both tag and force breakpoints.

- ADC 24-channel, 12-bit resolution; 2.5 μs conversion time; automatic compare function; 1.7 mV/°C temperature sensor; internal bandgap reference channel; operation in stop3; fully functional from 3.6V to 1.8V

- ACMPx Two analog comparators with selectable interrupt on rising, falling, or either edge of comparator output; compare option to fixed internal bandgap reference voltage; outputs can be optionally routed to TPM module; operation in stop3

- SCIx Two SCIs with full duplex non-return to zero (NRZ); LIN master extended break generation; LIN slave extended break detection; wake up on active edge

- SPIx— Two serial peripheral interfaces with Full-duplex or single-wire bidirectional; Double-buffered transmit and receive; MSB-first or LSB-first shifting

- IICx Two IICs with; Up to 100 kbps with maximum bus loading; Multi-master operation; Programmable slave address; Interrupt driven byte-by-byte data transfer; supports broadcast mode and 10 bit addressing

- TPMx One 6-channel and two 3-channel; Selectable input capture, output compare, or buffered edge- or center-aligned PWMs on each channel

- RTC 8-bit modulus counter with binary or decimal based prescaler; External clock source for precise time base, time-of-day, calendar or task scheduling functions; Free running on-chip low power oscillator (1 kHz) for cyclic wake-up without external components

- Input/Output

- 70 GPIOs and 1 input-only and 1 output-only pin

- 16 KBI interrupts with selectable polarity

- Hysteresis and configurable pull-up device on all input pins; Configurable slew rate and drive strength on all output pins.

- SET/CLR registers on 16 pins (PTC and PTE)

Freescale reserves the right to change the detail specifications as may be required to permit improvements in the design of its products.

© Freescale Semiconductor, Inc., 2008. All rights reserved.

# **Table of Contents**

| 1 | MC98  | S08QE128 Series Comparison4                 |

|---|-------|---------------------------------------------|

| 2 | Pin A | ssignments                                  |

| 3 | Elect | rical Characteristics                       |

|   | 3.1   | Introduction                                |

|   | 3.2   | Parameter Classification                    |

|   | 3.3   | Absolute Maximum Ratings12                  |

|   | 3.4   | Thermal Characteristics                     |

|   | 3.5   | ESD Protection and Latch-Up Immunity14      |

|   | 3.6   | DC Characteristics                          |

|   | 3.7   | Supply Current Characteristics              |

|   | 3.8   | External Oscillator (XOSC) Characteristics  |

|   | 3.9   | Internal Clock Source (ICS) Characteristics |

|   | 3.10  | AC Characteristics                          |

|   |       | 3.10.1 Control Timing                   |

|---|-------|-----------------------------------------|

|   |       | 3.10.2 TPM Module Timing                |

|   |       | 3.10.3 SPI Timing 27                    |

|   | 3.11  | Analog Comparator (ACMP) Electricals 30 |

|   | 3.12  | ADC Characteristics                     |

|   | 3.13  | Flash Specifications                    |

| 4 | Order | ing Information                         |

|   | 4.1   | Device Numbering System 34              |

| 5 | Packa | age Information                         |

|   |       | Mechanical Drawings                     |

| 6 | Produ | ct Documentation 49                     |

| 7 | Revis | ion History                             |

MC9S08QE128 Series Comparison

# 1 MC9S08QE128 Series Comparison

The following table compares the various device derivatives available within the MC9S08QE128 series.

### Table 1. MC9S08QE128 Series Features by MCU and Package

| Feature               | MC9S08QE128 |     |    |    | MC9S08QE96 |     |    |       | MC9S08QE64 |      |    |    |

|-----------------------|-------------|-----|----|----|------------|-----|----|-------|------------|------|----|----|

| Flash size (bytes)    | 131072      |     |    |    | 98304      |     |    | 65536 |            |      |    |    |

| RAM size (bytes)      |             | 80  | 64 |    |            | 60  | 16 |       |            | 4096 |    |    |

| Pin quantity          | 80          | 64  | 48 | 44 | 80         | 64  | 48 | 44    | 64         | 48   | 44 | 32 |

| ACMP1                 |             |     |    | •  | •          | ye  | es | •     |            |      | •  |    |

| ACMP2                 |             |     |    |    |            | ye  | es |       |            |      |    |    |

| ADC channels          | 24          | 22  | 10 | 10 | 24         | 22  | 10 | 10    | 22         | 10   | 10 | 10 |

| DBG                   |             |     |    |    |            | ye  | es |       |            |      |    |    |

| ICS                   |             |     |    |    |            | ye  | es |       |            |      |    |    |

| IIC1                  |             | yes |    |    |            |     |    |       |            |      |    |    |

| IIC2                  | yes         | yes | no | no | yes        | yes | no | no    | yes        | no   | no | no |

| IRQ                   |             |     |    |    |            | ye  | es |       |            |      |    |    |

| КВІ                   | 16          | 16  | 16 | 16 | 16         | 16  | 16 | 16    | 16         | 16   | 16 | 12 |

| Port I/O <sup>1</sup> | 70          | 54  | 38 | 34 | 70         | 54  | 38 | 34    | 54         | 38   | 34 | 26 |

| RTC                   |             |     |    |    |            | ye  | es |       |            |      |    |    |

| SCI1                  |             |     |    |    |            | ye  | es |       |            |      |    |    |

| SCI2                  |             |     |    |    |            | ye  | es |       |            |      |    |    |

| SPI1                  |             |     |    |    |            | ye  | es |       |            |      |    |    |

| SPI2                  |             |     |    |    |            | ye  | es |       |            |      |    |    |

| TPM1 channels         |             |     |    |    |            | 3   | 3  |       |            |      |    |    |

| TPM2 channels         |             |     |    |    |            | 3   | 3  |       |            |      |    |    |

| TPM3 channels         |             |     |    |    |            | 6   | 3  |       |            |      |    |    |

| XOSC                  |             |     |    |    |            | ye  | es |       |            |      |    |    |

<sup>1</sup> Port I/O count does not include the input only PTA5/IRQ/TPM1CLK/RESET or the output only PTA4/ACMP1O/BKGD/MS.

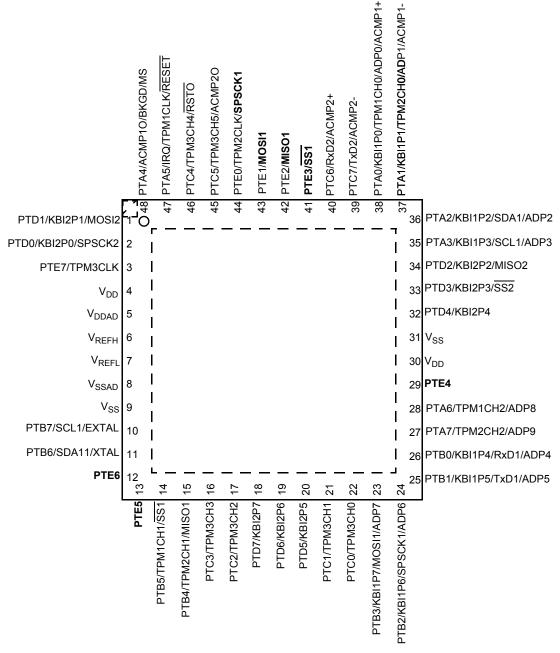

Figure 4. Pin Assignments in 48-Pin QFN Package

<sup>3</sup> Power supply must maintain regulation within operating V<sub>DD</sub> range during instantaneous and operating maximum current conditions. If positive injection current (V<sub>In</sub> > V<sub>DD</sub>) is greater than I<sub>DD</sub>, the injection current may flow out of V<sub>DD</sub> and could result in external power supply going out of regulation. Ensure external V<sub>DD</sub> load will shunt current greater than maximum injection current. This will be the greatest risk when the MCU is not consuming power. Examples are: if no system clock is present, or if the clock rate is very low (which would reduce overall power consumption).

### 3.4 Thermal Characteristics

This section provides information about operating temperature range, power dissipation, and package thermal resistance. Power dissipation on I/O pins is usually small compared to the power dissipation in on-chip logic and voltage regulator circuits, and it is user-determined rather than being controlled by the MCU design. To take  $P_{I/O}$  into account in power calculations, determine the difference between actual pin voltage and  $V_{SS}$  or  $V_{DD}$  and multiply by the pin current for each I/O pin. Except in cases of unusually high pin current (heavy loads), the difference between pin voltage and  $V_{SS}$  or  $V_{DD}$  will be very small.

|   | Rating                                  | Symbol          | Value     | Unit |

|---|-----------------------------------------|-----------------|-----------|------|

| 0 | perating temperature range (packaged)   | T <sub>A</sub>  | -40 to 85 | °C   |

| Μ | aximum junction temperature             | T <sub>JM</sub> | 95        | °C   |

| T | hermal resistance<br>Single-layer board |                 |           |      |

|   | 32-pin LQFP                             |                 | 82        |      |

|   | 44-pin LQFP                             | $\theta_{JA}$   | 68        | °C/W |

|   | 48-pin QFN                              |                 | 81        |      |

|   | 64-pin LQFP                             | 0               | 69        | °C/W |

|   | 80-pin LQFP                             | $\theta_{JA}$   | 60        | C/W  |

| T | hermal resistance<br>Four-layer board   |                 |           |      |

|   | 32-pin LQFP                             |                 | 54        |      |

|   | 44-pin LQFP                             | $\theta_{JA}$   | 46        | °C/W |

|   | 48-pin QFN                              |                 | 26        |      |

|   | 64-pin LQFP                             | Α               | 50        | °C/W |

|   | 80-pin LQFP                             | $\theta_{JA}$   | 47        | 0/11 |

The average chip-junction temperature  $(T_I)$  in °C can be obtained from:

$$T_{J} = T_{A} + (P_{D} \times \theta_{JA})$$

Eqn. 1

where:

$\begin{array}{l} T_A = \text{Ambient temperature, } ^{\circ}\text{C} \\ \theta_{JA} = \text{Package thermal resistance, junction-to-ambient, } ^{\circ}\text{C/W} \\ P_D = P_{int} + P_{I/O} \\ P_{int} = I_{DD} \times V_{DD}, \text{Watts } \text{ -- chip internal power} \\ P_{I/O} = \text{Power dissipation on input and output pins } \text{ -- user determined} \end{array}$

| Num | С | Characteristic                                               | Symbol            | Condition                                         | Min          | Typ <sup>1</sup> | Max          | Unit |

|-----|---|--------------------------------------------------------------|-------------------|---------------------------------------------------|--------------|------------------|--------------|------|

| 18  | Ρ | Low-voltage detection threshold — low range <sup>7</sup>     | V <sub>LVDL</sub> | V <sub>DD</sub> falling<br>V <sub>DD</sub> rising | 1.80<br>1.86 | 1.82<br>1.90     | 1.91<br>1.99 | V    |

| 19  | Ρ | Low-voltage warning threshold — high range <sup>7</sup>      | V <sub>LVWH</sub> | V <sub>DD</sub> falling<br>V <sub>DD</sub> rising | 2.36<br>2.36 | 2.46<br>2.46     | 2.56<br>2.56 | V    |

| 20  | Ρ | Low-voltage warning threshold — low range <sup>7</sup>       | V <sub>LVWL</sub> | V <sub>DD</sub> falling<br>V <sub>DD</sub> rising | 2.11<br>2.16 | 2.16<br>2.21     | 2.22<br>2.27 | V    |

| 21  | С | Low-voltage inhibit reset/recover<br>hysteresis <sup>7</sup> | V <sub>hys</sub>  |                                                   | _            | 50               | _            | mV   |

| 22  | Ρ | Bandgap Voltage Reference <sup>9</sup>                       | V <sub>BG</sub>   |                                                   | 1.15         | 1.17             | 1.18         | V    |

### Table 8. DC Characteristics (continued)

<sup>1</sup> Typical values are measured at 25°C. Characterized, not tested

<sup>2</sup> As the supply voltage rises, the LVD circuit will hold the MCU in reset until the supply has risen above V<sub>LVDL</sub>.

$^3$  All functional non-supply pins are internally clamped to V<sub>SS</sub> and V<sub>DD</sub>.

<sup>4</sup> Input must be current limited to the value specified. To determine the value of the required current-limiting resistor, calculate resistance values for positive and negative clamp voltages, then use the larger of the two values.

- <sup>5</sup> Power supply must maintain regulation within operating V<sub>DD</sub> range during instantaneous and operating maximum current conditions. If positive injection current (V<sub>In</sub> > V<sub>DD</sub>) is greater than I<sub>DD</sub>, the injection current may flow out of V<sub>DD</sub> and could result in external power supply going out of regulation. Ensure external V<sub>DD</sub> load will shunt current greater than maximum injection current. This will be the greatest risk when the MCU is not consuming power. Examples are: if no system clock is present, or if clock rate is very low (which would reduce overall power consumption).

- <sup>6</sup> Maximum is highest voltage that POR is guaranteed.

- <sup>7</sup> Low voltage detection and warning limits measured at 1 MHz bus frequency.

- <sup>8</sup> Run at 1 MHz bus frequency

- <sup>9</sup> Factory trimmed at  $V_{DD}$  = 3.0 V, Temp = 25°C

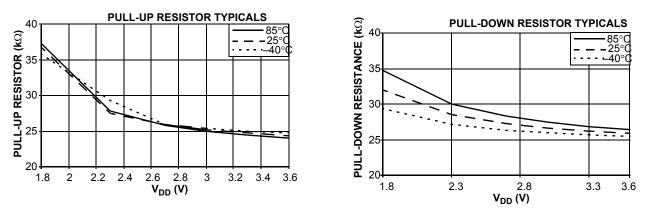

Figure 7. Pull-up and Pull-down Typical Resistor Values

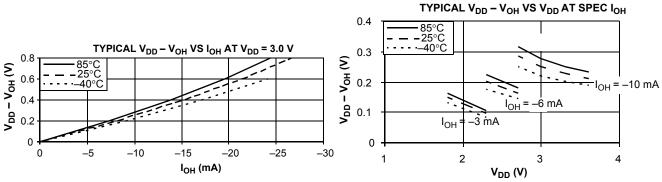

Figure 11. Typical High-Side (Source) Characteristics — High Drive (PTxDSn = 1)

### 3.7 Supply Current Characteristics

This section includes information about power supply current in various operating modes.

| Num | с | Parameter                                                  | Symbol             | Bus<br>Freq     | V <sub>DD</sub><br>(V) | Typ <sup>1</sup> | Мах  | Unit     | Temp<br>(°C) |    |           |

|-----|---|------------------------------------------------------------|--------------------|-----------------|------------------------|------------------|------|----------|--------------|----|-----------|

|     | Р | Run supply current                                         |                    | 25.165 MHz      |                        | 16               | 18   |          | -40 to 25    |    |           |

|     | Р | FEI mode, all modules on                                   |                    | 25.105 10112    |                        | 16               | 20   |          | 85           |    |           |

| 1   | Т |                                                            | RI <sub>DD</sub>   | 20 MHz          | 3                      | 14.4             | _    | mA       |              |    |           |

|     | Т |                                                            |                    | 8 MHz           |                        | 6.5              | _    |          | -40 to 85    |    |           |

|     | Т |                                                            |                    | 1 MHz           |                        | 1.4              | _    |          |              |    |           |

|     | С | Run supply current                                         |                    | 25.165 MHz      |                        | 11.5             | 12.3 |          |              |    |           |

| 2   | Т | FEI mode, all modules off                                  | RI <sub>DD</sub>   | 20 MHz          | 3                      | 9.5              | _    | mA       | –40 to 85    |    |           |

| 2   | Т |                                                            | NDD                | 8 MHz           | 3                      | 4.6              | _    |          | +0 10 00     |    |           |

|     | Т |                                                            |                    | 1 MHz           |                        | 1.0              | _    |          |              |    |           |

| 3   | т | Run supply current<br>LPS=0, all modules off               | RI <sub>DD</sub>   | 16 kHz<br>FBILP | 3                      | 152              | _    | μA       | –40 to 85    |    |           |

| 0   | т |                                                            |                    | 16 kHz<br>FBELP |                        |                  | 115  | _        | μ            |    |           |

|     | т | Run supply current                                         | - RI <sub>DD</sub> |                 |                        | 01.0             |      |          | 0 to 70      |    |           |

| 4   | I | LPS=1, all modules off, running from<br>Flash              |                    | Rlaa            | RI                     | 16 kHz           | 3    | 21.9     |              | μA | -40 to 85 |

|     | Т | Run supply current<br>LPS=1, all modules off, running from |                    | FBELP           | Ŭ                      | 7.3              |      | μαι      | 0 to 70      |    |           |

|     |   | RAM                                                        |                    |                 |                        | 7.5              | —    |          | -40 to 85    |    |           |

|     | С | Wait mode supply current                                   |                    | 25.165 MHz      |                        | 5.74             | 6    |          |              |    |           |

| 5   | Т | FEI mode, all modules off                                  | WI <sub>DD</sub>   | 20 MHz          | 3 4.57 —               |                  | mA   | 40 to 85 |              |    |           |

|     | Т |                                                            | טטייי              | 8 MHz           | U                      | 2                |      |          | 40 10 00     |    |           |

|     | Т |                                                            |                    | 1 MHz           |                        | 0.73             | _    |          |              |    |           |

### Table 9. Supply Current Characteristics

| Num | С | Rating                                                                                                                                                                   | Symbol                                | Min                           | Typ <sup>1</sup> | Мах | Unit |

|-----|---|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|-------------------------------|------------------|-----|------|

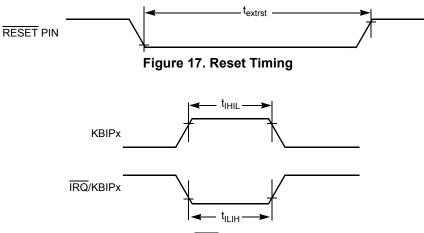

| 7   | D | IRQ pulse width<br>Asynchronous path <sup>2</sup><br>Synchronous path <sup>4</sup>                                                                                       | t <sub>ILIH,</sub> t <sub>IHIL</sub>  | 100<br>1.5 x t <sub>cyc</sub> |                  |     | ns   |

| 8   | D | Keyboard interrupt pulse width<br>Asynchronous path <sup>2</sup><br>Synchronous path <sup>4</sup>                                                                        | t <sub>ILIH,</sub> t <sub>IHIL</sub>  | 100<br>1.5 x t <sub>cyc</sub> | _                |     | ns   |

| 9   | С | Port rise and fall time —<br>Low output drive (PTxDS = 0) (load = 50 pF) <sup>5</sup><br>Slew rate control disabled (PTxSE = 0)<br>Slew rate control enabled (PTxSE = 1) | t <sub>Rise</sub> , t <sub>Fall</sub> |                               | 8<br>31          |     | ns   |

| 3   | 0 | Port rise and fall time —<br>High output drive (PTxDS = 1) (load = 50 pF)<br>Slew rate control disabled (PTxSE = 0)<br>Slew rate control enabled (PTxSE = 1)             | t <sub>Rise</sub> , t <sub>Fall</sub> |                               | 7<br>24          |     | ns   |

| 10  |   | Voltage regulator recovery time                                                                                                                                          | t <sub>VRR</sub>                      |                               | 4                | _   | μS   |

### Table 13. Control Timing (continued)

<sup>1</sup> Typical values are based on characterization data at  $V_{DD}$  = 3.0V, 25°C unless otherwise stated.

<sup>2</sup> This is the shortest pulse that is guaranteed to be recognized as a reset or interrupt pin request. Shorter pulses are not guaranteed to override reset requests from internal sources.

$^{3}$  To enter BDM mode following a POR, BKGD/MS should be held low during the power-up and for a hold time of t<sub>MSH</sub> after V<sub>DD</sub> rises above V<sub>LVD</sub>.

<sup>4</sup> This is the minimum pulse width that is guaranteed to pass through the pin synchronization circuitry. Shorter pulses may or may not be recognized. In stop mode, the synchronizer is bypassed so shorter pulses can be recognized in that case.

$^5\,$  Timing is shown with respect to 20%  $V_{DD}$  and 80%  $V_{DD}$  levels. Temperature range –40°C to 85°C.

Figure 18. IRQ/KBIPx Timing

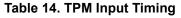

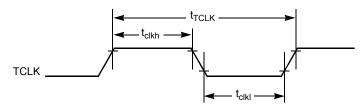

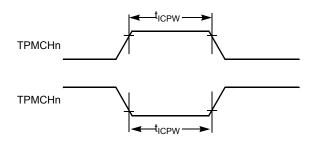

### 3.10.2 TPM Module Timing

Synchronizer circuits determine the shortest input pulses that can be recognized or the fastest clock that can be used as the optional external source to the timer counter. These synchronizers operate from the current bus rate clock.

| No. | С | Function                  | Symbol            | Min | Max                 | Unit             |

|-----|---|---------------------------|-------------------|-----|---------------------|------------------|

| 1   | D | External clock frequency  | f <sub>TCLK</sub> | 0   | f <sub>Bus</sub> /4 | Hz               |

| 2   | D | External clock period     | t <sub>TCLK</sub> | 4   | _                   | t <sub>cyc</sub> |

| 3   | D | External clock high time  | t <sub>clkh</sub> | 1.5 | —                   | t <sub>cyc</sub> |

| 4   | D | External clock low time   | t <sub>ciki</sub> | 1.5 | —                   | t <sub>cyc</sub> |

| 5   | D | Input capture pulse width | t <sub>ICPW</sub> | 1.5 | —                   | t <sub>cyc</sub> |

Figure 19. Timer External Clock

Figure 20. Timer Input Capture Pulse

### NOTES:

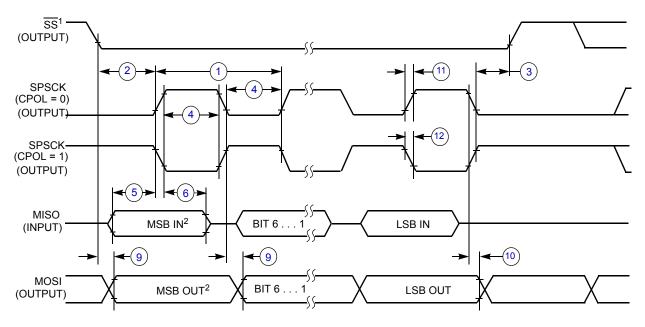

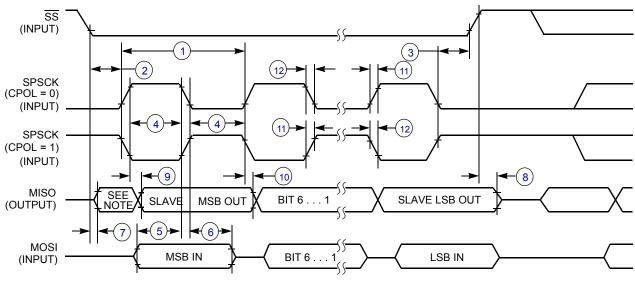

1. SS output mode (DDS7 = 1, SSOE = 1).

2. LSBF = 0. For LSBF = 1, bit order is LSB, bit 1, ..., bit 6, MSB.

### Figure 21. SPI Master Timing (CPHA = 0)

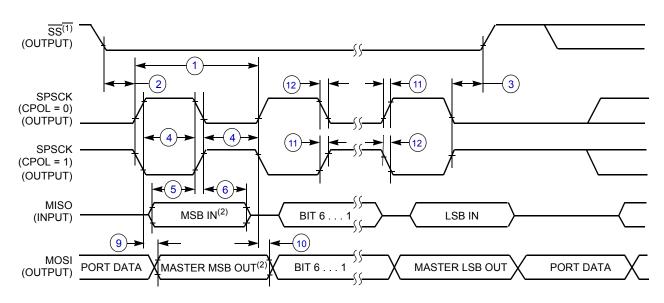

NOTES:

1.  $\overline{SS}$  output mode (DDS7 = 1, SSOE = 1).

2. LSBF = 0. For LSBF = 1, bit order is LSB, bit 1, ..., bit 6, MSB.

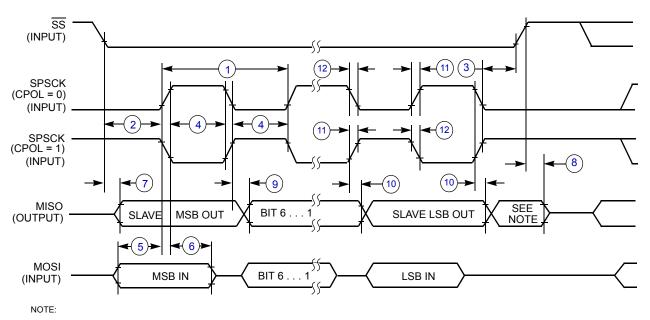

1. Not defined but normally MSB of character just received

NOTE:

1. Not defined but normally LSB of character just received

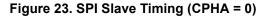

Figure 24. SPI Slave Timing (CPHA = 1)

### 3.11 Analog Comparator (ACMP) Electricals

**Table 16. Analog Comparator Electrical Specifications**

| С | Characteristic                         | Symbol             | Min                   | Typical | Max      | Unit |

|---|----------------------------------------|--------------------|-----------------------|---------|----------|------|

| D | Supply voltage                         | V <sub>DD</sub>    | 1.80                  | _       | 3.6      | V    |

| С | Supply current (active)                | I <sub>DDAC</sub>  | —                     | 20      | 35       | μA   |

| D | Analog input voltage                   | V <sub>AIN</sub>   | V <sub>SS</sub> – 0.3 | -       | $V_{DD}$ | V    |

| С | Analog input offset voltage            | V <sub>AIO</sub>   |                       | 20      | 40       | mV   |

| С | Analog comparator hysteresis           | V <sub>H</sub>     | 3.0                   | 9.0     | 15.0     | mV   |

| Р | Analog input leakage current           | I <sub>ALKG</sub>  | _                     | _       | 1.0      | μA   |

| С | Analog comparator initialization delay | t <sub>AINIT</sub> | —                     | —       | 1.0      | μS   |

### 3.12 ADC Characteristics

#### С Characteristic Conditions Symb Typ<sup>1</sup> Unit Comment Min Max Supply voltage V Absolute 1.8 3.6 V<sub>DDAD</sub> D Delta to V<sub>DD</sub> (V<sub>DD</sub>-V<sub>DDAD</sub>)<sup>2</sup> $\Delta V_{DDAD}$ -100 0 +100 mV Delta to V<sub>SS</sub> (V<sub>SS</sub>-V<sub>SSAD</sub>)<sup>2</sup> -100 0 +100 D Ground voltage $\Delta V_{SSAD}$ mV Ref Voltage High 1.8 V D $V_{REFH}$ V<sub>DDAD</sub> V<sub>DDAD</sub> V D Ref Voltage Low V<sub>REFL</sub> V<sub>SSAD</sub> V<sub>SSAD</sub> V<sub>SSAD</sub> D Input Voltage V V<sub>ADIN</sub> V<sub>REFL</sub> V<sub>REFH</sub> Input C<sub>ADIN</sub> 4.5 5.5 С pF Capacitance С Input Resistance $\mathsf{R}_{\mathsf{ADIN}}$ 5 7 kΩ External to MCU Analog Source 12 bit mode R<sub>AS</sub> Resistance $f_{ADCK} > 4MHz$ 2 $f_{ADCK} < 4MHz$ 5 \_\_\_\_ С 10 bit mode kΩ $f_{ADCK} > 4MHz$ 5 f<sub>ADCK</sub> < 4MHz 10 8 bit mode (all valid f<sub>ADCK</sub>) 10 ADC Conversion High Speed (ADLPC=0) 0.4 8.0 **f**ADCK MHz D Clock Freg. Low Power (ADLPC=1) 0.4 4.0

### Table 17. 12-bit ADC Operating Conditions

<sup>1</sup> Typical values assume V<sub>DDAD</sub> = 3.0V, Temp = 25°C, f<sub>ADCK</sub>=1.0MHz unless otherwise stated. Typical values are for reference only and are not tested in production.

<sup>2</sup> DC potential difference.

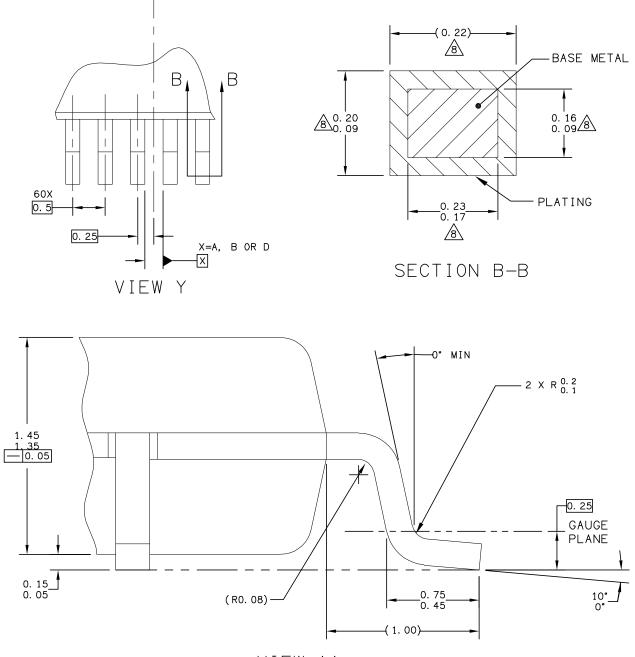

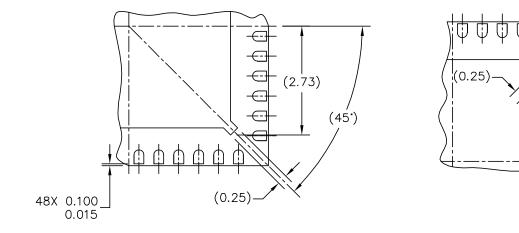

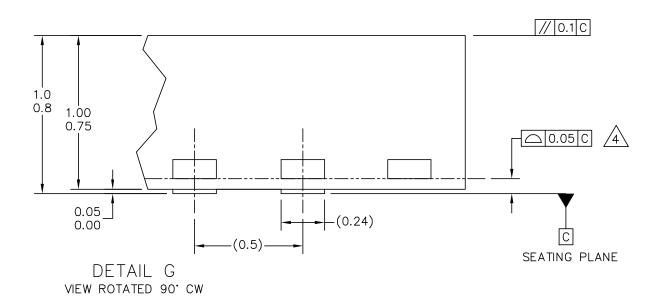

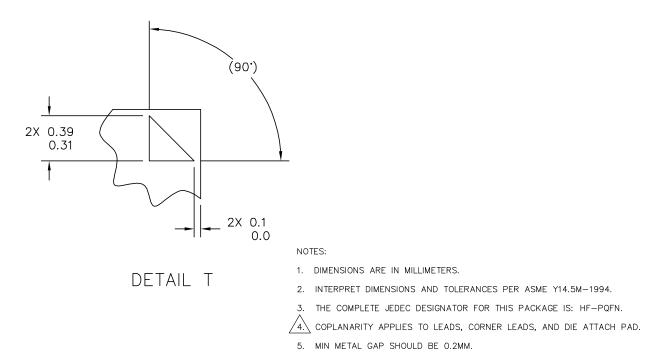

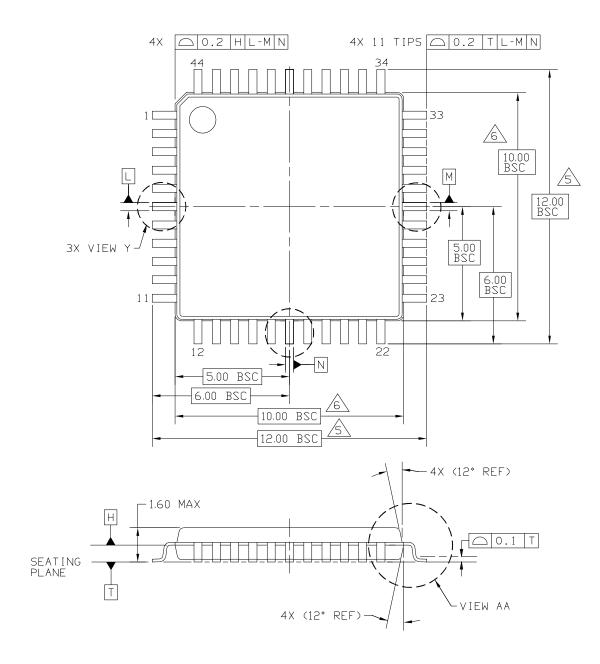

### 5.1 Mechanical Drawings

The following pages are mechanical drawings for the packages described in Table 21. For the latest available drawings please visit our web site (http://www.freescale.com) and enter the package's document number into the keyword search box.

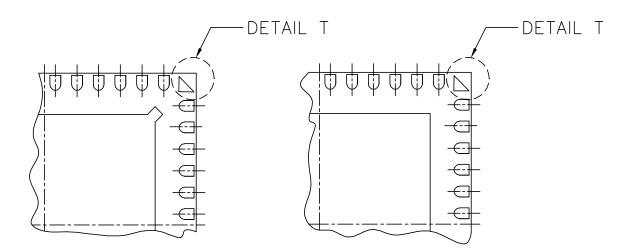

VIEW AA

| © FREESCALE SEMICONDUCTOR, INC.<br>ALL RIGHTS RESERVED.            | MECHANICAL OUTLINE |              | PRINT VERSION NO | DT TO SCALE |

|--------------------------------------------------------------------|--------------------|--------------|------------------|-------------|

| TITLE: 64LD LQFP,<br>10 X 10 X 1.4 PKG,<br>0.5 PITCH, CASE OUTLINE |                    | DOCUMENT NO  | ): 98ASS23234₩   | REV: D      |

|                                                                    |                    | CASE NUMBER  | 8:840F-02        | 06 APR 2005 |

|                                                                    |                    | STANDARD: JE | DEC MS-026 BCD   |             |

Figure 28. 64-pin LQFP Package Drawing (Case 840F, Doc #98ASS23234W), Sheet 2 of 3

NOTES:

- 1. DIMENSIONS ARE IN MILLIMETERS.

- 2. DIMENSIONING AND TOLERANCING PER ASME Y14.5M-1994.

- 3. DATUMS A, B AND D TO BE DETERMINED AT DATUM PLANE H.

- /4. DIMENSIONS TO BE DETERMINED AT SEATING PLANE C.

- 5. THIS DIMENSION DOES NOT INCLUDE DAMBAR PROTRUSION. ALLOWABLE DAMBAR PROTRUSION SHALL NOT CAUSE THE LEAD WIDTH TO EXCEED THE UPPER LIMIT BY MORE THAN 0.08 mm AT MAXIMUM MATERIAL CONDITION. DAMBAR CANNOT BE LOCATED ON THE LOWER RADIUS OR THE FOOT. MINIMUM SPACE BETWEEN PROTRUSION AND ADJACENT LEAD SHALL NOT BE LESS THAN 0.07 mm.

- ATHIS DIMENSION DOES NOT INCLUDE MOLD PROTRUSION. ALLOWABLE PROTRUSION IS 0.25 mm PER SIDE. THIS DIMENSION IS MAXIMUM PLASTIC BODY SIZE DIMENSION INCLUDING MOLD MISMATCH.

- /7. EXACT SHAPE OF EACH CORNER IS OPTIONAL.

- $\frac{8}{2}$  THESE DIMENSIONS APPLY TO THE FLAT SECTION OF THE LEAD BETWEEN 0.1 mm AND 0.25 mm FROM THE LEAD TIP.

| © FREESCALE SEMICONDUCTOR, INC.<br>ALL RIGHTS RESERVED.            | MECHANICAL OUTLINE |              | PRINT VERSION NOT TO SCAL |             |

|--------------------------------------------------------------------|--------------------|--------------|---------------------------|-------------|

| TITLE: 64LD LQFP,<br>10 X 10 X 1.4 PKG,<br>0.5 PITCH, CASE OUTLINE |                    | DOCUMENT NO  | ): 98ASS23234₩            | REV: D      |

|                                                                    |                    | CASE NUMBER  | 2: 840F-02                | 06 APR 2005 |

|                                                                    |                    | STANDARD: JE | DEC MS-026 BCD            |             |

#### Figure 29. 64-pin LQFP Package Drawing (Case 840F, Doc #98ASS23234W), Sheet 3 of 3

DETAIL N PREFERRED CORNER CONFIGURATION

DETAIL M PREFERED PIN 1 BACKSIDE IDENTIFIER

| © FREESCALE SEMICONDUCTOR, INC.<br>ALL RIGHTS RESERVED.                                               | MECHANICA | L OUTLINE                     | PRINT VERSION NO | T TO SCALE  |

|-------------------------------------------------------------------------------------------------------|-----------|-------------------------------|------------------|-------------|

| TITLE: THERMALLY ENHANCED QUAD<br>FLAT NON-LEADED PACKAGE (QFN)<br>48 TERMINAL, 0.5 PITCH (7 X 7 X 1) |           | DOCUMENT NO                   | ): 98ARH99048A   | REV: F      |

|                                                                                                       |           |                               |                  | 05 DEC 2005 |

|                                                                                                       |           | STANDARD: JEDEC-MO-220 VKKD-2 |                  |             |

Figure 31. 48-pin QFN Package Drawing (Case 1314, Doc #98ARH99048A), Sheet 2 of 3

DETAIL M PIN 1 BACKSIDE IDENTIFIER OPTION

DETAIL M PIN 1 BACKSIDE IDENTIFIER OPTION

| © FREESCALE SEMICONDUCTOR, INC.<br>ALL RIGHTS RESERVED. | MECHANICA | LOUTLINE                      | PRINT VERSION NO | T TO SCALE  |

|---------------------------------------------------------|-----------|-------------------------------|------------------|-------------|

| TITLE: THERMALLY ENHANCED                               | QUAD      | DOCUMENT NO                   | ): 98ARH99048A   | REV: F      |

| FLAT NON-LEADED PACKAGE (QFN)                           |           | CASE NUMBER: 1314-05 05 DEC 2 |                  | 05 DEC 2005 |

| 48 TERMINAL, 0.5 PITCH (7 X 7 X 1)                      |           | STANDARD: JEDEC-MO-220 VKKD-2 |                  |             |

Figure 32. 48-pin QFN Package Drawing (Case 1314, Doc #98ARH99048A), Sheet 3 of 3

| © FREESCALE SEMICONDUCTOR, INC.<br>ALL RIGHTS RESERVED. | MECHANICAL OUTLINE |              | PRINT VERSION NOT TO SCALE |             |

|---------------------------------------------------------|--------------------|--------------|----------------------------|-------------|

| TITLE:                                                  |                    | DOCUMENT NE  | 1: 98ASS23225W             | RE∨∶D       |

| 44 LD LQFP,<br>10 X 10 PKG, 0.8 PITCH,                  | .4 THICK           | CASE NUMBER  | 2: 824D-02                 | 26 FEB 2007 |

|                                                         |                    | STANDARD: JE | DEC MS-026-BCB             |             |

NOTES:

- 1. DIMENSIONS ARE IN MILLIMETERS.

- 2. INTERPRET DIMENSIONS AND TOLERANCES PER ASME Y14.5-1994.

$\sqrt{3}$  datums a, b, and d to be determined at datum plane H.

$\overline{/4.}$  dimensions to be determined at seating plane datum c.

5. DIMENSION DOES NOT INCLUDE DAMBAR PROTRUSION. ALLOWABLE DAMBAR PROTRUSION SHALL NOT CAUSE THE LEAD WIDTH TO EXCEED THE MAXIMUM DIMENSION BY MORE THAN 0.08 MM. DAMBAR CANNOT BE LOCATED ON THE LOWER RADIUS OR THE FOOT. MINIMUM SPACE BETWEEN PROTRUSION AND ADJACENT LEAD OR PROTRUSION: 0.07 MM.

6. DIMENSIONS DO NOT INCLUDE MOLD PROTRUSION. ALLOWABLE PROTRUSION IS 0.25 MM PER SIDE. DIMENSIONS ARE MAXIMUM PLASTIC BODY SIZE DIMENSIONS INCLUDING MOLD MISMATCH.

/7. EXACT SHAPE OF EACH CORNER IS OPTIONAL.

8. THESE DIMENSIONS APPLY TO THE FLAT SECTION OF THE LEAD BETWEEN 0.1 MM AND 0.25 MM FROM THE LEAD TIP.

| © FREESCALE SEMICONDUCTOR, INC.<br>ALL RIGHTS RESERVED.        | MECHANICAL OUTLINE |              | PRINT VERSION NOT TO SCALE |             |

|----------------------------------------------------------------|--------------------|--------------|----------------------------|-------------|

| TITLE:                                                         |                    | DOCUMENT NO  | ]: 98ASH70029A             | RE∨: D      |

| $32 \text{ IFAD } 08 \text{ PITCH} (7 \times 7 \times 14)^{2}$ |                    | CASE NUMBER  | 2: 873A-03                 | 19 MAY 2005 |

|                                                                |                    | STANDARD: JE | DEC MS-026 BBA             |             |

Figure 38. 32-pin LQFP Package Drawing (Case 873A, Doc #98ASH70029A), Sheet 3 of 3