Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFl

| Product Status             | Not For New Designs                                                           |

|----------------------------|-------------------------------------------------------------------------------|

| Core Processor             | H8S/2000                                                                      |

| Core Size                  | 16-Bit                                                                        |

| Speed                      | 16MHz                                                                         |

| Connectivity               | SCI, SmartCard, USB                                                           |

| Peripherals                | DMA, POR, PWM, WDT                                                            |

| Number of I/O              | 68                                                                            |

| Program Memory Size        | 256KB (256K x 8)                                                              |

| Program Memory Type        | FLASH                                                                         |

| EEPROM Size                | -                                                                             |

| RAM Size                   | 16K x 8                                                                       |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                                                   |

| Data Converters            | A/D 6x10b; D/A 2x8b                                                           |

| Oscillator Type            | External                                                                      |

| Operating Temperature      | -20°C ~ 75°C (TA)                                                             |

| Mounting Type              | Surface Mount                                                                 |

| Package / Case             | 120-TQFP                                                                      |

| Supplier Device Package    | 120-TQFP (14x14)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/df2215ute16v |

|                            |                                                                               |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Table 13.12 | SCI Interrupt Sources                                                      | 2 |

|-------------|----------------------------------------------------------------------------|---|

| Table 13.13 | Interrupt Sources in Smart Card Interface Mode                             | 3 |

|             |                                                                            |   |

| Section 14  | Boundary Scan Function                                                     |   |

| Table 14.1  | Pin Configuration                                                          | 3 |

| Table 14.2  | Instruction configuration                                                  | 4 |

| Table 14.3  | IDCODE Register Configuration                                              | 6 |

| Table 14.4  | Correspondence between LSI Pins and Boundary Scan Register                 | 8 |

| Section 15  | Universal Serial Bus Interface (USB)                                       |   |

| Table 15.1  | Pin Configuration                                                          | 2 |

| Table 15.2  | EPINFO Data Settings                                                       |   |

| Table 15.3  | Relationship between the UTSTR0 Setting and Pin Outputs                    |   |

| Table 15.4  | Relationship between the UTSTR1 Settings and Pin Inputs                    |   |

| Table 15.5  | SCI Interrupt Sources                                                      |   |

| Table 15.6  | Command Decoding on Firmware                                               |   |

| Table 15.7  | Register Name Modification List                                            |   |

| Table 15.8  | Bit Name Modification List                                                 |   |

| Table 15.9  | EPINFO Data Settings                                                       |   |

|             |                                                                            |   |

| Section 16  | A/D Converter                                                              |   |

| Table 16.1  | Pin Configuration                                                          | 3 |

| Table 16.2  | Analog Input Channels and Corresponding ADDR Registers                     | 4 |

| Table 16.3  | A/D Conversion Time (Single Mode)                                          | 1 |

| Table 16.4  | A/D Conversion Time (Scan Mode)                                            | 2 |

| Table 16.5  | A/D Converter Interrupt Source                                             | 3 |

| Table 16.6  | Analog Pin Specifications                                                  | 7 |

| Section 17  | D/A Converter                                                              |   |

| Table 17.1  | Pin Configuration                                                          | 0 |

|             |                                                                            | U |

| Section 19  | Flash Memory (F-ZTAT Version)                                              |   |

| Table 19.1  | Differences between Boot Mode and User Program Mode                        |   |

| Table 19.2  | Pin Configuration                                                          | 4 |

| Table 19.3  | Setting On-Board Programming Modes                                         | 1 |

| Table 19.4  | SCI Boot Mode Operation                                                    | 4 |

| Table 19.5  | System Clock Frequencies for Which Automatic Adjustment of LSI Bit Rate Is |   |

|             | Possible                                                                   | 4 |

| Table 19.6  | Enumeration Information                                                    | - |

| Table 19.7  | USB Boot Mode Operation                                                    | 8 |

### 2.4.4 Condition-Code Register (CCR)

This 8-bit register contains internal CPU status information, including an interrupt mask bit (I) and half-carry (H), negative (N), zero (Z), overflow (V), and carry (C) flags.

Operations can be performed on the CCR bits by the LDC, STC, ANDC, ORC, and XORC instructions. The N, Z, V, and C flags are used as branching conditions for conditional branch (Bcc) instructions.

| Bit | Bit Name | Initial Value | R/W | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|-----|----------|---------------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | l        | 1             | R/W | Interrupt Mask Bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|     |          |               |     | Masks interrupts other than NMI when set to 1. NMI is<br>accepted regardless of the I bit setting. The I bit is set to 1<br>by hardware at the start of an exception-handling<br>sequence. For details, refer to section 5, Interrupt<br>Controller.                                                                                                                                                                                                                                                                     |

| 6   | UI       | undefined     | R/W | User Bit or Interrupt Mask Bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|     |          |               |     | Can be written and read by software using the LDC, STC, ANDC, ORC, and XORC instructions. This bit cannot be used as an interrupt mask bit in this LSI.                                                                                                                                                                                                                                                                                                                                                                  |

| 5   | Н        | undefined     | R/W | Half-Carry Flag                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|     |          |               |     | When the ADD.B, ADDX.B, SUB.B, SUBX.B, CMP.B or<br>NEG.B instruction is executed, this flag is set to 1 if there is<br>a carry or borrow at bit 3, and cleared to 0 otherwise. When<br>the ADD.W, SUB.W, CMP.W, or NEG.W instruction is<br>executed, the H flag is set to 1 if there is a carry or borrow<br>at bit 11, and cleared to 0 otherwise. When the ADD.L,<br>SUB.L, CMP.L, or NEG.L instruction is executed, the H flag<br>is set to 1 if there is a carry or borrow at bit 27, and cleared<br>to 0 otherwise. |

| 4   | U        | undefined     | R/W | User Bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|     |          |               |     | Can be written and read by software using the LDC, STC, ANDC, ORC, and XORC instructions.                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 3   | Ν        | undefined     | R/W | Negative Flag                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|     |          |               |     | Stores the value of the most significant bit of data as a sign bit.                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 2   | Z        | undefined     | R/W | Zero Flag                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|     |          |               |     | Set to 1 to indicate zero data, and cleared to 0 to indicate non-zero data.                                                                                                                                                                                                                                                                                                                                                                                                                                              |

## 2.7.1 Register Direct—Rn

The register field of the instruction specifies an 8-, 16-, or 32-bit general register containing the operand. R0H to R7H and R0L to R7L can be specified as 8-bit registers. R0 to R7 and E0 to E7 can be specified as 16-bit registers. ER0 to ER7 can be specified as 32-bit registers.

## 2.7.2 Register Indirect—@ERn

The register field of the instruction code specifies an address register (ERn) which contains the address of the operand on memory. If the address is a program instruction address, the lower 24 bits are valid and the upper 8 bits are all assumed to be 0 (H'00).

# 2.7.3 Register Indirect with Displacement—@(d:16, ERn) or @(d:32, ERn)

A 16-bit or 32-bit displacement contained in the instruction is added to an address register (ERn) specified by the register field of the instruction, and the sum gives the address of a memory operand. A 16-bit displacement is sign-extended when added.

# 2.7.4 Register Indirect with Post-Increment or Pre-Decrement—@ERn+ or @-ERn

**Register indirect with post-increment**—@**ERn+:** The register field of the instruction code specifies an address register (ERn) which contains the address of a memory operand. After the operand is accessed, 1, 2, or 4 is added to the address register contents and the sum is stored in the address register. The value added is 1 for byte access, 2 for word transfer instruction, or 4 for longword transfer instruction. For word or longword transfer instruction, the register value should be even.

**Register indirect with pre-decrement**—@-**ERn:** The value 1, 2, or 4 is subtracted from an address register (ERn) specified by the register field in the instruction code, and the result becomes the address of a memory operand. The result is also stored in the address register. The value subtracted is 1 for byte access, 2 for word transfer instruction, or 4 for longword transfer instruction. For word or longword transfer instruction, the register value should be even.

# 2.7.5 Absolute Address—@aa:8, @aa:16, @aa:24, or @aa:32

The instruction code contains the absolute address of a memory operand. The absolute address may be 8 bits long (@aa:8), 16 bits long (@aa:16), 24 bits long (@aa:24), or 32 bits long (@aa:32). Table 2.12 indicates the accessible absolute address ranges.

To access data, the absolute address should be 8 bits (@aa:8), 16 bits (@aa:16), or 32 bits (@aa:32) long. For an 8-bit absolute address, the upper 24 bits are all assumed to be 1 (H'FFFF).

| Bit | Bit Name | Initial Value | R/W | Description                                                                                        |

|-----|----------|---------------|-----|----------------------------------------------------------------------------------------------------|

| 9   | IRQ4SCB  | 0             | R/W | IRQ4 Sense Control B                                                                               |

| 8   | IRQ4SCA  | 0             | R/W | IRQ4 Sense Control A                                                                               |

|     |          |               |     | 00: Interrupt request generated at IRQ4 input low level                                            |

|     |          |               |     | 01: Interrupt request generated at falling edge of IRQ4 input                                      |

|     |          |               |     | <ol> <li>Interrupt request generated at rising edge of IRQ4 input</li> </ol>                       |

|     |          |               |     | <ol> <li>Interrupt request generated at both falling and<br/>rising edges of IRQ4 input</li> </ol> |

| 7   | IRQ3SCB  | 0             | R/W | IRQ3 Sense Control B                                                                               |

| 6   | IRQ3SCA  | 0             | R/W | IRQ3 Sense Control A                                                                               |

|     |          |               |     | 00: Interrupt request generated at IRQ3 input low level                                            |

|     |          |               |     | 01: Interrupt request generated at falling edge of IRQ3 input                                      |

|     |          |               |     | <ol> <li>Interrupt request generated at rising edge of IRQ3 input</li> </ol>                       |

|     |          |               |     | <ol> <li>Interrupt request generated at both falling and<br/>rising edges of IRQ3 input</li> </ol> |

| 5   | IRQ2SCB  | 0             | R/W | IRQ2 Sense Control B                                                                               |

| 4   | IRQ2SCA  | 0             | R/W | IRQ2 Sense Control A                                                                               |

|     |          |               |     | 00: Interrupt request generated at IRQ2 input low level                                            |

|     |          |               |     | 01: Interrupt request generated at falling edge of IRQ2 input                                      |

|     |          |               |     | <ol> <li>Interrupt request generated at rising edge of IRQ2 input</li> </ol>                       |

|     |          |               |     | <ol> <li>Interrupt request generated at both falling and<br/>rising edges of IRQ2 input</li> </ol> |

| 3   | IRQ1SCB  | 0             | R/W | IRQ1 Sense Control B                                                                               |

| 2   | IRQ1SCA  | 0             | R/W | IRQ1 Sense Control A                                                                               |

|     |          |               |     | 00: Interrupt request generated at IRQ1 input low level                                            |

|     |          |               |     | 01: Interrupt request generated at falling edge of IRQ1 input                                      |

|     |          |               |     | 10: Interrupt request generated at rising edge of IRQ1 input                                       |

|     |          |               |     | 11: Interrupt request generated at both falling and rising edges of IRQ1 input                     |

#### 5.7.2 Instructions that Disable Interrupts

Instructions that disable interrupts are LDC, ANDC, ORC, and XORC. After any of these instructions is executed, all interrupts including NMI are disabled and the next instruction is always executed. When the I bit is set by one of these instructions, the new value becomes valid two states after execution of the instruction ends.

#### 5.7.3 Times when Interrupts Are Disabled

There are times when interrupt acceptance is disabled by the interrupt controller.

The interrupt controller disables interrupt acceptance for a 3-state period after the CPU has updated the mask level with an LDC, ANDC, ORC, or XORC instruction.

### 5.7.4 Interrupts during Execution of EEPMOV Instruction

Interrupt operation differs between the EEPMOV.B instruction and the EEPMOV.W instruction.

With the EEPMOV.B instruction, an interrupt request (including NMI) issued during the transfer is not accepted until the move is completed.

With the EEPMOV.W instruction, if an interrupt request is issued during the transfer, interrupt exception handling starts at a break in the transfer cycle. The PC value saved on the stack in this case is the address of the next instruction.

Therefore, if an interrupt is generated during execution of an EEPMOV.W instruction, the following coding should be used.

```

L1:EEPMOV.W

MOV.W R4,R4

BNE L1

```

### 5.7.5 IRQ Interrupt

During clock operation, IRQ input is accepted in synchronization with the clock.

In software standby mode, non-synchronous input is accepted.

For details of the input conditions, see the Control Signal Timing description in the Electrical Characteristics section for the product in question.

### 8.2 Register Descriptions

DTC has the following registers.

- DTC mode register A (MRA)

- DTC mode register B (MRB)

- DTC source address register (SAR)

- DTC destination address register (DAR)

- DTC transfer count register A (CRA)

- DTC transfer count register B (CRB)

These six registers cannot be directly accessed from the CPU. When activated, the DTC reads a set of register information that is stored in an on-chip RAM to the corresponding DTC registers and transfers data. After the data transfer, it writes a set of updated register information back to the RAM.

- DTC enable registers (DTCERA to DTCERF)

- DTC vector register (DTVECR)

### 8.2.2 DTC Mode Register B (MRB)

MRB selects the DTC operating mode.

| Bit  | Bit Name | Initial Value | R/W | Description                                                                                                                                                                                   |

|------|----------|---------------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7    | CHNE     | Undefined     |     | DTC Chain Transfer Enable                                                                                                                                                                     |

|      |          |               |     | This bit specifies a chain transfer. For details, refer to section 8.5.4, Chain Transfer.                                                                                                     |

|      |          |               |     | In data transfer with CHNE set to 1, determination of the<br>end of the specified number of transfers, clearing of the<br>interrupt source flag, and clearing of DTCER, are not<br>performed. |

|      |          |               |     | 0: DTC data transfer completed (waiting for start)                                                                                                                                            |

|      |          |               |     | 1: DTC chain transfer (reads new register information and transfers data)                                                                                                                     |

| 6    | DISEL    | Undefined     | _   | DTC Interrupt Select                                                                                                                                                                          |

|      |          |               |     | This bit specifies whether CPU interrupt is disabled or<br>enabled after a data transfer.                                                                                                     |

|      |          |               |     | <ol> <li>Interrupt request is issued to the CPU when the<br/>specified data transfer is completed.</li> </ol>                                                                                 |

|      |          |               |     | <ol> <li>DTC issues interrupt request to the CPU in every<br/>data transfer (DTC does not clear the interrupt<br/>request flag that is a cause of the activation).</li> </ol>                 |

| 5 to | _        | Undefined     | _   | Reserved                                                                                                                                                                                      |

| 0    |          |               |     | These bits have no effect on DTC operation, and the write value should always be 0.                                                                                                           |

### 8.2.3 DTC Source Address Register (SAR)

SAR is a 24-bit register that designates the source address of data to be transferred by the DTC. For word-size transfer, specify an even source address.

### 8.2.4 DTC Destination Address Register (DAR)

DAR is a 24-bit register that designates the destination address of data to be transferred by the DTC. For word-size transfer, specify an even destination address.

# 8.7 Examples of Use of the DTC

### 8.7.1 Normal Mode

An example is shown in which the DTC is used to receive 128 bytes of data via the SCI.

- Set MRA to fixed source address (SM1 = SM0 = 0), incrementing destination address (DM1 = 1, DM0 = 0), normal mode (MD1 = MD0 = 0), and byte size (Sz = 0). The DTS bit can have any value. Set MRB for one data transfer by one interrupt (CHNE = 0, DISEL = 0). Set the SCI RDR address in SAR, the start address of the RAM area where the data will be received in DAR, and 128 (H'0080) in CRA. CRB can be set to any value.

- 2. Set the start address of the register information at the DTC vector address.

- 3. Set the corresponding bit in DTCER to 1.

- 4. Set the SCI to the appropriate receive mode. Set the RIE bit in SCR to 1 to enable the reception complete (RXI) interrupt. Since the generation of a receive error during the SCI reception operation will disable subsequent reception, the CPU should be enabled to accept receive error interrupts.

- 5. Each time reception of one byte of data ends on the SCI, the RDRF flag in SSR is set to 1, an RXI interrupt is generated, and the DTC is activated. The receive data is transferred from RDR to RAM by the DTC. DAR is incremented and CRA is decremented. The RDRF flag is automatically cleared to 0.

- 6. When CRA becomes 0 after the 128 data transfers have ended, the RDRF flag is held at 1, the DTCE bit is cleared to 0, and an RXI interrupt request is sent to the CPU. The interrupt handling routine should perform wrap-up processing.

# 8.7.2 Software Activation

An example is shown in which the DTC is used to transfer a block of 128 bytes of data by means of software activation. The transfer source address is H'1000 and the destination address is H'2000. The vector number is H'60, so the vector address is H'04C0.

- Set MRA to incrementing source address (SM1 = 1, SM0 = 0), incrementing destination address (DM1 = 1, DM0 = 0), block transfer mode (MD1 = 1, MD0 = 0), and byte size (Sz = 0). The DTS bit can have any value. Set MRB for one block transfer by one interrupt (CHNE = 0). Set the transfer source address (H'1000) in SAR, the destination address (H'2000) in DAR, and 128 (H'8080) in CRA. Set 1 (H'0001) in CRB.

- 2. Set the start address of the register information at the DTC vector address (H'04C0).

- 3. Check that the SWDTE bit in DTVECR is 0. Check that there is currently no transfer activated by software.

# 9.11 Port F

Port F is an 8-bit I/O port that also has external interrupt input ( $\overline{IRQ2}$ ,  $\overline{IRQ3}$ ), bus control sign I/O, system clock output. The port F has the following registers.

- Port F data direction register (PFDDR)

- Port F data register (PFDR)

- Port F register (PORTF)

### 9.11.1 Port F Data Direction Register (PFDDR)

The individual bits of PFDDR specify input or output for the pins of port F. Since this is a writeonly register, bit manipulation instructions should not be used to write to it. For details, see section 2.9.4, Accessing Registers Containing Write-Only Bits.

| Bit | Bit Name | Initial Value | R/W | Description                                                                                                                                                                                                    |

|-----|----------|---------------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | PF7DDR   | 1/0*          | W   | Modes 4 to 6                                                                                                                                                                                                   |

| 6   | PF6DDR   | 0             | W   | Pin PF7 functions as the $\phi$ output pin when the corresponding PFDDR bit is set to 1, and as an input port                                                                                                  |

| 5   | PF5DDR   | 0             | W   | when the bit is cleared to 0. The input/output direction                                                                                                                                                       |

| 4   | PF4DDR   | 0             | W   | specification in PFDDR is ignored for pins PF6 to PF3,                                                                                                                                                         |

| 3   | PF3DDR   | 0             | W   | which are automatically designated as bus control<br>outputs. Pins PF2 to PF0 are made bus control                                                                                                             |

| 2   | PF2DDR   | 0             | W   | input/output pins by bus controller settings. Otherwise,                                                                                                                                                       |

| 1   | PF1DDR   | 0             | W   | setting a PFDDR bit to 1 makes the corresponding pin an output port, while clearing the bit to 0 makes the pin an                                                                                              |

| 0   | PF0DDR   | 0             | W   | input port.                                                                                                                                                                                                    |

|     |          |               |     | Mode 7<br>Setting a PFDDR bit to 1 makes the corresponding port F<br>pin PF6 to PF0 an output port, or in the case of pin PF7,<br>the $\phi$ output pin. Clearing the bit to 0 makes the pin an<br>input port. |

Note: \* In modes 4 to 6, set to 1; in mode 7 cleared to 0.

# 9.13 Handling of Unused Pins

Unused input pins should be fixed high or low. Generally, the input pins of CMOS products are high-impedance. Leaving unused pins open can cause the generation of intermediate levels due to peripheral noise induction. This can result in shoot-through current inside the device and cause it to malfunction. Table 9.76 lists examples of ways to handle unused pins.

For the handling of dedicated boundary scan pins that are unused, see section 14.2, Pin Configuration, and section 14.5, Usage Notes. For the handling of dedicated USB pins that are unused, see section 15.9.14, Pin Processing when USB Not Used.

| Pin Name | Pin Handling Example                                                      |

|----------|---------------------------------------------------------------------------|

| Port 1   | Connect each pin to Vcc (pull-up) or to Vss (pull-down) via a resistor.   |

| Port 3   | —                                                                         |

| Port 4   | Connect each pin to AVcc (pull-up) or to AVss (pull-down) via a resistor. |

| Port 7   | Connect each pin to Vcc (pull-up) or to Vss (pull-down) via a resistor.   |

| Port 9   | Connect each pin to AVcc (pull-up) or to AVss (pull-down) via a resistor. |

| Port A   | Connect each pin to Vcc (pull-up) or to Vss (pull-down) via a resistor.   |

| Port B   | —                                                                         |

| Port C   | —                                                                         |

| Port D   | _                                                                         |

| Port E   | —                                                                         |

| Port F   | _                                                                         |

| Port G   | _                                                                         |

### Table 9.76 Examples of Ways to Handle Unused Input Pins

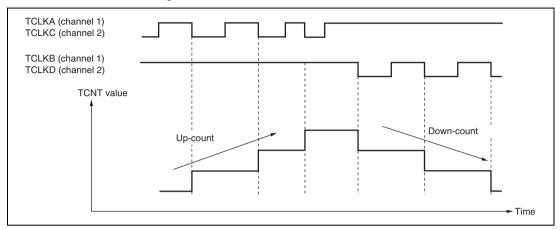

3. Phase counting mode 3

Figure 10.28 shows an example of phase counting mode 3 operation, and table 10.22 summarizes the TCNT up/down-count conditions.

### Table 10.22 Up/Down-Count Conditions in Phase Counting Mode 3

| TCLKA (Channel 1) | TCLKB (Channel 1) |            |

|-------------------|-------------------|------------|

| TCLKC (Channel 2) | TCLKD (Channel 2) | Operation  |

| High level        | _                 | Don't care |

| Low level         | Ĩ.                |            |

| _                 | Low level         |            |

| ₹_                | High level        | Up-count   |

| High level        | T_                | Down-count |

| Low level         | _                 | Don't care |

| _ <b>_</b>        | High level        |            |

| ₹.                | Low level         |            |

Legend:

📕 : Rising edge

📜 : Falling edge

### 13.3.5 Serial Mode Register (SMR)

SMR is used to set the SCI's serial transfer format and select the baud rate generator clock source. Some bits in SMR have different functions in normal mode and smart card interface mode.

| ٠ | Normal Serial | Communication | Interface | Mode ( | When | SMIF in | SCMR is 0) | ) |

|---|---------------|---------------|-----------|--------|------|---------|------------|---|

|---|---------------|---------------|-----------|--------|------|---------|------------|---|

| Bit | Bit Name | Initial Value | R/W | Description                                                                                                                                                                                                                                                        |

|-----|----------|---------------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | C/Ā      | 0             | R/W | Communication Mode                                                                                                                                                                                                                                                 |

|     |          |               |     | 0: Asynchronous mode                                                                                                                                                                                                                                               |

|     |          |               |     | 1: Clocked synchronous mode                                                                                                                                                                                                                                        |

| 6   | CHR      | 0             | R/W | Character Length (enabled only in asynchronous mode)                                                                                                                                                                                                               |

|     |          |               |     | 0: Selects 8 bits as the data length                                                                                                                                                                                                                               |

|     |          |               |     | 1: Selects 7 bits as the data length. LSB-first is fixed and the MSB of TDR is not transmitted in transmission                                                                                                                                                     |

|     |          |               |     | In clocked synchronous mode, a fixed data length of 8 bits is used.                                                                                                                                                                                                |

| 5   | PE       | 0             | R/W | Parity Enable (enabled only in asynchronous mode)                                                                                                                                                                                                                  |

|     |          |               |     | When this bit is set to 1, the parity bit is added to<br>transmit data before transmission, and the parity bit is<br>checked in reception. For a multiprocessor format, parity<br>bit addition and checking are not performed regardless<br>of the PE bit setting. |

| 4   | O/E      | 0             | R/W | Parity Mode (enabled only when the PE bit is 1 in asynchronous mode)                                                                                                                                                                                               |

|     |          |               |     | 0: Selects even parity                                                                                                                                                                                                                                             |

|     |          |               |     | 1: Selects odd parity                                                                                                                                                                                                                                              |

| 3   | STOP     | 0             | R/W | Stop Bit Length (enabled only in asynchronous mode)                                                                                                                                                                                                                |

|     |          |               |     | Selects the stop bit length in transmission.                                                                                                                                                                                                                       |

|     |          |               |     | 0: 1 stop bit                                                                                                                                                                                                                                                      |

|     |          |               |     | 1: 2 stop bits                                                                                                                                                                                                                                                     |

|     |          |               |     | In reception, only the first stop bit is checked. If the second stop bit is 0, it is treated as the start bit of the next transmit character.                                                                                                                      |

| Bit   | Bit Name   | Initial Value   | R/W       | Description                                                                                                                                             |

|-------|------------|-----------------|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2     | TEND       | 1               | R         | Transmit End                                                                                                                                            |

|       |            |                 |           | This bit is set to 1 when no error signal has been sent<br>back from the receiving end and the next transmit data is<br>ready to be transferred to TDR. |

|       |            |                 |           | [Setting conditions]                                                                                                                                    |

|       |            |                 |           | • When the TE bit in SCR is 0 and the ERS bit is also 0                                                                                                 |

|       |            |                 |           | • When the ESR bit is 0 and the TDRE bit is 1 after the specified interval following transmission of 1-byte data.                                       |

|       |            |                 |           | The timing of bit setting differs according to the register setting as follows:                                                                         |

|       |            |                 |           | When $GM = 0$ and $BLK = 0$ , 2.5 etu after transmission starts                                                                                         |

|       |            |                 |           | When $GM = 0$ and $BLK = 1$ , 1.0 etu after transmission starts                                                                                         |

|       |            |                 |           | When $GM = 1$ and $BLK = 0$ , 1.5 etu after transmission starts                                                                                         |

|       |            |                 |           | When $GM = 1$ and $BLK = 1$ , 1.0 etu after transmission starts                                                                                         |

|       |            |                 |           | [Clearing conditions]                                                                                                                                   |

|       |            |                 |           | • When 0 is written to TDRE after reading TDRE = 1                                                                                                      |

|       |            |                 |           | • When the DMAC or the DTC* <sup>2</sup> is activated by a TXI interrupt and transfers transmission data to TDR                                         |

| 1     | MPB        | 0               | R         | Multiprocessor Bit                                                                                                                                      |

|       |            |                 |           | This bit is not used in Smart Card interface mode.                                                                                                      |

| 0     | MPBT       | 0               | R/W       | Multiprocessor Bit Transfer                                                                                                                             |

|       |            |                 |           | Write 0 to this bit in Smart Card interface mode.                                                                                                       |

| Notes | : 1. The w | rite value shou | uld alwav | s be 0 to clear the flag.                                                                                                                               |

Notes: 1. The write value should always be 0 to clear the flag.

2. The clearing conditions using the DTC are that DISEL bit be cleared to 0 and the transfer counter value be other than 0.

3. To clear the flag by the CPU on the H8S/2215R, H8S/2215T, and H8S/2215C, reread the flag after writing 0 to it.

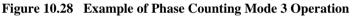

Figure 15.22 EP3o Isochronous-Out Transfer Operation

### 15.9.14 Pin Processing when USB Not Used

Pin processing should be performed as follows.

$DrVCC = Vcc, DrVSS = 0 V, USD + = USD - = USPND = open state, VBUS = \overline{UBPM} = 0 V$

### 15.9.15 Notes on Emulator Usage

Using the I/O register window function, or the like, to display UEDR00, UEDR20, UEDR30, and UEDR40 can cause the EP0oFIFO, EP2oFIFO, EP3oFIFO, and EP4oFIFO read pointers to malfunction, preventing UEDR00 to UEDR40 and UESZ00 to UESZ40 from being read correctly. Therefore, UEDR00 to UEDR40 should not be displayed.

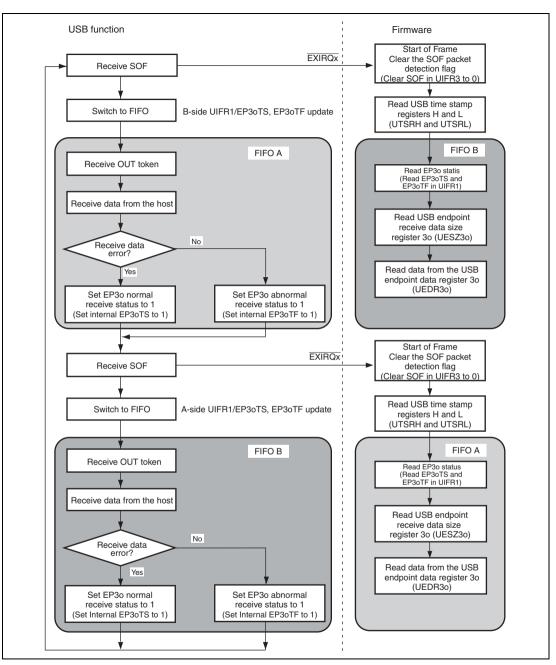

### 15.9.16 Notes on TR Interrupt

Note the following when using the transfer request interrupt (TR interrupt) for IN transfer to EP0i, EP2i, EP3i, EP4i, or EP5i.

The TR interrupt flag is set if the FIFO for the target EP has no data when the IN token is sent from the USB host. However, at the timing shown in figure 15.38, multiple TR interrupts occur successively. Take appropriate measures against malfunction in such a case.

Note: This module determines whether to return NAK if the FIFO of the target EP has no data when receiving the IN token, but the TR interrupt flag is set only after a NAK handshake is sent. If the next IN token is sent before PKTE of UTRGx is written to, the TR interrupt flag is set again.

Figure 15.38 TR Interrupt Flag Set Timing

#### 22.4.3 Setting Oscillation Stabilization Time after Clearing Software Standby Mode

Bits STS2 to STS0 in SBYCR should be set as described below.

• Using a Crystal Oscillator

Set bits STS2 to STS0 so that the standby time is at least  $t_{osc2}$  ms (the oscillation stabilization time).

Table 22.3 shows the standby times for different operating frequencies and settings of bits STS2 to STS0.

• Using an External Clock

Set bits STS2 to STS0 as any value. Usually, minimum value is recommended. A 16-state standby time cannot be used in the F-ZTAT version; a standby time of 2,048 states or longer should be used.

| STS2 | STS1 | STS0 | Standby Time  | 24<br>MHz <sup>*2</sup> | 20<br>MHz <sup>*1</sup> | 16<br>MHz | 13<br>MHz | 10<br>MHz | 8<br>MHz | 6<br>MHz | 4<br>MHz | 2<br>MHz | Unit |

|------|------|------|---------------|-------------------------|-------------------------|-----------|-----------|-----------|----------|----------|----------|----------|------|

| 0    | 0    | 0    | 8192 states   | 0.3                     | 0.4                     | 0.51      | 0.6       | 0.8       | 1.0      | 1.3      | 2.0      | 4.1      | ms   |

|      |      | 1    | 16384 states  | 0.7                     | 0.8                     | 1.0       | 1.3       | 1.6       | 2.0      | 2.7      | 4.1      | 8.2      |      |

|      | 1    | 0    | 32768 states  | 1.4                     | 1.6                     | 2.0       | 2.5       | 3.3       | 4.1      | 5.5      | 8.2      | 16.4     | -    |

|      |      | 1    | 65536 states  | 2.7                     | 3.3                     | 4.1       | 5.0       | 6.6       | 8.2      | 10.9     | 16.4     | 32.8     | -    |

| 1    | 0    | 0    | 131072 states | 5.5                     | 6.6                     | 8.2       | 10.1      | 13.1      | 16.4     | 21.8     | 32.8     | 65.5     | -    |

|      |      | 1    | 262144 states | 10.9                    | 13.1                    | 16.4      | 20.2      | 26.2      | 32.8     | 43.6     | 65.6     | 131.2    | -    |

|      | 1    | 0    | 2048 states   | 0.09                    | 0.1                     | 0.13      | 0.16      | 0.2       | 0.3      | 0.3      | 0.5      | 1.0      | _    |

|      |      | 1    | 16 states     | 0.7                     | 0.8                     | 1.0       | 1.2       | 1.6       | 2.0      | 1.7      | 4.0      | 8.0      | μs   |

#### Table 22.3 Oscillation Stabilization Time Settings

Notes: 1. Only in H8S/2215R and H8S/2215C.

2. Only in H8S/2215R, H8S/2215T and H8S/2215C.

Recommended time setting (See the  $t_{osc2}$  item in table 24.4 or table 25.4, for conditions)

# 24.3 DC Characteristics

Table 24.2 lists the DC characteristics. Table 24.3 lists the permissible output currents.

### Table 24.2 DC Characteristics

### Conditions: $V_{cc} = PLLV_{cc} = DrV_{cc} = 2.7 \text{ V to } 3.6 \text{ V}, AV_{cc} = 2.7 \text{ V to } 3.6 \text{ V}, V_{ref} = 2.7 \text{ V to } AV_{cc}$ , $V_{ss} = PLLV_{ss} = DrV_{ss} = AV_{ss} = 0 \text{ V}, T_a = -20^{\circ}\text{C to } +75^{\circ}\text{C}$ (regular specifications), $T_a = -40^{\circ}\text{C to } +85^{\circ}\text{C}$ (wide-range specifications)<sup>\*1</sup>

| ltem                  |                                                                                                  | Symbol                          | Min.                | Тур. | Max.                  | Unit           | Test<br>Conditions        |

|-----------------------|--------------------------------------------------------------------------------------------------|---------------------------------|---------------------|------|-----------------------|----------------|---------------------------|

| Schmitt               | IRQ0 to IRQ5                                                                                     | V <sub>T</sub> <sup>-</sup>     | $V_{cc} \times 0.2$ | _    |                       | V              |                           |

| trigger input         | IRQ7                                                                                             | $V_{T}^{+}$                     |                     | _    | $V_{cc} \times 0.8$   | V              |                           |

| voltage               |                                                                                                  | $V_{\rm T}^{^+}-V_{\rm T}^{^-}$ | $V_{cc} 	imes 0.05$ | _    |                       | V              | _                         |

| Input high<br>voltage | RES, STBY,<br>NMI,<br>MD2 to MD0,<br>TRST, TCK,<br>TMS, TDI,<br>VBUS, UBPM,<br>FWE <sup>*5</sup> | V <sub>IH</sub>                 | $V_{cc} \times 0.9$ | _    | V <sub>cc</sub> +0.3  | V              | _                         |

|                       | EXTAL,<br>EXTAL48,<br>Ports 1, 3, 7,<br>and A to G                                               |                                 | $V_{cc} \times 0.8$ | _    | V <sub>cc</sub> + 0.3 | V              |                           |

|                       | Ports 4 <sup>*6</sup> and 9                                                                      | -                               | $V_{cc} \times 0.8$ | _    | $AV_{cc} + 0.3^{*}$   | <sup>6</sup> V | _                         |

| Input Iow<br>voltage  | RES, STBY,<br>MD2 to MD0,<br>TRST, TCK,<br>TMS, TDI,<br>VBUS, UBPM,<br>FWE <sup>*5</sup>         | V <sub>IL</sub>                 | -0.3                | _    | $V_{cc} \times 0.1$   | V              |                           |

|                       | EXTAL,<br>EXTAL48,<br>NMI, Ports 1,<br>3, 4, 7, 9, and<br>A to G                                 | -                               | -0.3                | _    | $V_{cc} \times 0.2$   | V              | _                         |

| Output high           | All output pins                                                                                  | V <sub>oh</sub>                 | $V_{cc} - 0.5$      | _    |                       | V              | I <sub>OH</sub> = -200 μA |

| voltage               |                                                                                                  |                                 | $V_{cc} - 1.0$      | _    | —                     | V              | I <sub>он</sub> = -1 mA   |

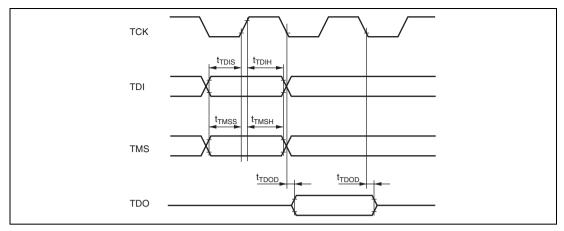

Figure 24.23 Boundary Scan Data Transmission Timing

#### 25.4.4 Timing of On-Chip Supporting Modules

Table 25.7 lists the timing of on-chip supporting modules.

#### Table 25.7 Timing of On-Chip Supporting Modules

- Condition A:  $V_{cc} = PLLV_{cc} = DrV_{cc} = 2.7 \text{ V}$  to 3.6 V,  $AV_{cc} = 2.7 \text{ V}$  to 3.6 V,  $V_{ref} = 2.7 \text{ V}$  to  $AV_{cc}$ ,  $V_{ss} = PLLV_{ss} = DrV_{ss} = AV_{ss} = 0 \text{ V}$ ,  $\phi = 13 \text{ MHz}$  to 16 MHz,  $T_a = -20^{\circ}\text{C}$  to  $+75^{\circ}\text{C}$ (regular specifications),  $T_a = -40^{\circ}\text{C}$  to  $+85^{\circ}\text{C}$  (wide-range specifications)

- Condition B:  $V_{cc} = PLLV_{cc} = DrV_{cc} = 3.0 \text{ V}$  to 3.6 V,  $AV_{cc} = 3.0 \text{ V}$  to 3.6 V,  $V_{ref} = 3.0 \text{ V}$  to  $AV_{cc}$ ,  $V_{ss} = PLLV_{ss} = DrV_{ss} = AV_{ss} = 0 \text{ V}$ ,  $\phi = 13 \text{ MHz}$  to 24 MHz,  $T_a = -20^{\circ}\text{C}$  to  $+75^{\circ}\text{C}$ (regular specifications),  $T_a = -40^{\circ}\text{C}$  to  $+85^{\circ}\text{C}$  (wide-range specifications)

|          |                                  |                    |                                 | Cond | lition A | Condition B |      |                       | Test         |

|----------|----------------------------------|--------------------|---------------------------------|------|----------|-------------|------|-----------------------|--------------|

| Item     |                                  | Symbol             | Min.                            | Max. | Min.     | Max.        | Unit | Conditions            |              |

| I/O port | Output data delay time           |                    | t <sub>PWD</sub>                | _    | 60       | _           | 40   | ns                    | Figure 25.12 |

|          | Input data setup<br>time         |                    | t <sub>PRS</sub>                | 50   | _        | 30          | —    | _                     |              |

|          | Input data hold<br>time          |                    | t <sub>PRH</sub>                | 50   | _        | 30          | _    | _                     |              |

| TPU      | Timer output delay time          |                    | t <sub>TOCD</sub>               | _    | 60       | _           | 40   | ns                    | Figure 25.13 |

|          | Timer input setup time           |                    | t <sub>TICS</sub>               | 40   | _        | 30          | _    | _                     |              |

|          | Timer clock input setup time     |                    | t <sub>TCKS</sub>               | 40   | _        | 30          | —    | ns                    | Figure 25.14 |

|          | Timer<br>clock<br>pulse<br>width | Single<br>edge     | t <sub>тскwн</sub>              | 1.5  | _        | 1.5         | _    | $t_{_{\mathrm{cyc}}}$ | _            |

|          |                                  | Both<br>edges      | t <sub>TCKWL</sub>              | 2.5  | _        | 2.5         | —    | _                     |              |

| TMR      | Timer o<br>delay t               |                    | $\mathbf{t}_{_{\mathrm{TMOD}}}$ | _    | 60       | —           | 41   | ns                    | Figure 25.15 |

|          | Timer i<br>setup t               | reset input<br>ime | t <sub>TMRS</sub>               | 50   | _        | 29          | _    | ns                    | Figure 25.17 |

|          | Timer of setup t                 | clock input<br>ime | t <sub>TMCS</sub>               | 50   |          | 29          |      | ns                    | Figure 25.16 |

| Item                                    |                                                                     | Symbol                     | Min. | Тур.                            | Max.                            | Unit                            | Test<br>Conditions                                      |

|-----------------------------------------|---------------------------------------------------------------------|----------------------------|------|---------------------------------|---------------------------------|---------------------------------|---------------------------------------------------------|

| Output low voltage                      | All output pins                                                     | V <sub>ol</sub>            | _    | _                               | 0.4                             | V                               | I <sub>он</sub> = 0.4 mA                                |

|                                         |                                                                     |                            | _    | _                               | 0.4                             | V                               | I <sub>oL</sub> = 0.8 mA                                |

| Input<br>leakage<br>current             | RES, STBY,<br>NMI, MD2 to<br>MD0, FWE <sup>*5</sup> ,<br>VBUS, UBPM | I <sub>in</sub>            | _    | _                               | 1.0                             | μA                              | $V_{in} = 0.5 \text{ V to}$<br>$V_{cc} - 0.5 \text{ V}$ |

|                                         | Ports 4, 9                                                          | I <sub>in</sub>            | _    | —                               | 1.0                             | μA                              | $V_{in} = 0.5 \text{ V to}$<br>AV <sub>cc</sub> - 0.5 V |

| 3-state leak<br>current (off<br>status) | Ports 1, 3, 7, A to G                                               | <sub>tsi</sub>             | _    | _                               | 1.0                             | μA                              | $V_{in} = 0.5 \text{ V to}$ $V_{cc} - 0.5 \text{ V}$    |

| Input pull-up<br>MOS current            |                                                                     | -I <sub>P</sub>            | 10   | _                               | 300                             | μA                              | $V_{in} = 0 V$                                          |

| Input<br>capacity                       | RES, NMI                                                            | $\mathbf{C}_{\mathrm{in}}$ | _    |                                 | 30                              | pF                              | $V_{in} = 0 V$                                          |

|                                         | All input pins<br>other than<br>RES and NMI                         | -                          | _    | _                               | 15                              | pF                              | f = 1 MHz<br>$T_a = 25^{\circ}C$                        |

| Current<br>dissipation <sup>*2</sup>    | Normal<br>operation<br>(USB halts)                                  | I <sub>cc</sub> *3         | _    | 23<br>(V <sub>cc</sub> = 3.3 V) | 40<br>(V <sub>cc</sub> = 3.6 V) | mA                              | f = 16 MHz                                              |

|                                         |                                                                     |                            |      | _                               | 34<br>(V <sub>cc</sub> = 3.3 V) | 55<br>(V <sub>cc</sub> = 3.6 V) | mA                                                      |

|                                         | Normal<br>operation<br>(USB<br>operates)                            | -                          | _    | 28<br>(V <sub>cc</sub> = 3.3 V) | 50<br>(V <sub>cc</sub> = 3.6 V) | mA                              | f = 16 MHz<br>(PLL 3<br>multiplication)                 |

|                                         |                                                                     |                            |      | _                               | 40<br>(V <sub>cc</sub> = 3.3 V) | 60<br>(V <sub>cc</sub> = 3.6 V) | mA                                                      |

|                                         | Sleep mode                                                          |                            | _    | 18<br>(V <sub>cc</sub> = 3.3 V) | 35<br>(V <sub>cc</sub> = 3.6 V) | mA                              | f = 16 MHz<br>(when USB<br>and PLL are<br>halted)       |

|                                         |                                                                     |                            | _    | 26<br>(V <sub>cc</sub> = 3.3 V) | 45<br>(V <sub>cc</sub> = 3.6 V) | mA                              | f = 24 MHz<br>(when USB<br>and PLL are<br>halted)       |