Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                   |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 20MHz                                                                    |

| Connectivity               | UART/USART                                                               |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                    |

| Number of I/O              | 22                                                                       |

| Program Memory Size        | 3.5KB (2K x 14)                                                          |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | 64 x 8                                                                   |

| RAM Size                   | 128 x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 4V ~ 5.5V                                                                |

| Data Converters            | A/D 5x10b                                                                |

| Oscillator Type            | External                                                                 |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                           |

| Supplier Device Package    | 28-SOIC                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f870-e-so |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### 2.2.2.5 PIR1 Register

The PIR1 register contains the individual flag bits for the peripheral interrupts.

| Note: | Interrupt flag bits get set when an interrupt |  |  |  |  |  |  |

|-------|-----------------------------------------------|--|--|--|--|--|--|

|       | condition occurs, regardless of the state of  |  |  |  |  |  |  |

|       | its corresponding enable bit or the global    |  |  |  |  |  |  |

|       | enable bit, GIE (INTCON<7>). User soft-       |  |  |  |  |  |  |

|       | ware should ensure the appropriate inter-     |  |  |  |  |  |  |

|       | rupt bits are clear prior to enabling an      |  |  |  |  |  |  |

|       | interrupt.                                    |  |  |  |  |  |  |

| 0.    |                      |             | DDILLOO.                       | uon)                         |                       |               |            |        |

|-------|----------------------|-------------|--------------------------------|------------------------------|-----------------------|---------------|------------|--------|

|       | R/W-0                | R/W-0       | R-0                            | R-0                          | U-0                   | R/W-0         | R/W-0      | R/W-0  |

|       | PSPIF <sup>(1)</sup> | ADIF        | RCIF                           | TXIF                         | —                     | CCP1IF        | TMR2IF     | TMR1IF |

|       | bit 7                |             |                                |                              |                       |               |            | bit 0  |

|       | (1)                  |             |                                |                              |                       |               |            |        |

| bit 7 |                      |             |                                |                              | rrupt Flag bit        |               |            |        |

|       |                      |             | peration ha                    |                              | e (must be cle        | eared in sof  | tware)     |        |

| bit 6 |                      |             | nterrupt Fla                   |                              |                       |               |            |        |

| Sit 0 |                      |             | completed                      | •                            |                       |               |            |        |

|       |                      |             | on is not cor                  |                              |                       |               |            |        |

| bit 5 | RCIF: USA            | RT Receive  | e Interrupt F                  | lag bit                      |                       |               |            |        |

|       |                      |             | /e buffer is f                 |                              |                       |               |            |        |

|       |                      |             | /e buffer is                   |                              |                       |               |            |        |

| bit 4 |                      |             | it Interrupt F                 | -                            |                       |               |            |        |

|       |                      |             | mit buffer is<br>mit buffer is |                              |                       |               |            |        |

| bit 3 | Unimplem             | ented: Rea  | d as '0'                       |                              |                       |               |            |        |

| bit 2 | CCP1IF: C            | CP1 Interru | pt Flag bit                    |                              |                       |               |            |        |

|       | Capture me           |             |                                |                              |                       |               |            |        |

|       |                      |             | apture occu<br>capture occ     |                              | be cleared in s       | oftware)      |            |        |

|       | Compare n            |             |                                |                              |                       |               |            |        |

|       |                      |             |                                | tch occurred<br>atch occurre | d (must be clea<br>ed | ared in softw | vare)      |        |

|       | PWM mode             |             |                                |                              |                       |               |            |        |

| 1.1.4 | Unused in            |             |                                |                              | .,                    |               |            |        |

| bit 1 |                      |             |                                | errupt Flag b                | eared in softw        | ara)          |            |        |

|       |                      |             | match occu                     |                              |                       | ale)          |            |        |

| bit 0 | TMR1IF: T            | MR1 Overfl  | ow Interrup                    | t Flag bit                   |                       |               |            |        |

|       |                      |             | •                              | •                            | ed in software)       |               |            |        |

|       |                      |             | not overflow                   |                              |                       |               |            |        |

|       | Note 1:              | PSPIF is r  | eserved on                     | the PIC16F                   | 870; always m         | aintain this  | bit clear. |        |

|       |                      |             |                                |                              |                       |               |            |        |

| Legend:            |                  |                      |                    |

|--------------------|------------------|----------------------|--------------------|

| R = Readable bit   | W = Writable bit | U = Unimplemented    | l bit, read as '0' |

| - n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

#### 2.2.2.7 PIR2 Register

The PIR2 register contains the flag bit for the EEPROM write operation interrupt.

```

Note: Interrupt flag bits get set when an interrupt condition occurs, regardless of the state of its corresponding enable bit or the global enable bit, GIE (INTCON<7>). User software should ensure the appropriate interrupt flag bits are clear prior to enabling an interrupt.

```

## REGISTER 2-7: PIR2 REGISTER (ADDRESS: 0Dh)

| U-0   | U-0 | U-0 | R/W-0 | U-0 | U-0 | U-0 | U-0   |

|-------|-----|-----|-------|-----|-----|-----|-------|

| —     | —   | —   | EEIF  | —   | —   | _   | —     |

| bit 7 |     |     |       |     |     |     | bit 0 |

#### bit 7-5 Unimplemented: Read as '0'

bit 4 **EEIF**: EEPROM Write Operation Interrupt Flag bit

- 1 = The write operation completed (must be cleared in software)

- 0 = The write operation is not complete or has not been started

bit 3-0 Unimplemented: Read as '0'

| Legend:            |                  |                      |                    |

|--------------------|------------------|----------------------|--------------------|

| R = Readable bit   | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

| - n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

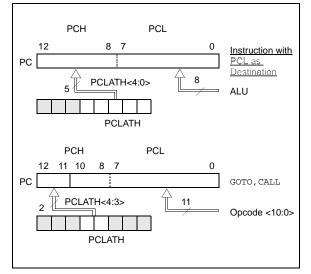

# 2.3 PCL and PCLATH

The Program Counter (PC) is 13-bits wide. The low byte comes from the PCL register, which is a readable and writable register. The upper bits (PC<12:8>) are not readable, but are indirectly writable through the PCLATH register. On any RESET, the upper bits of the PC will be cleared. Figure 2-3 shows the two situations for the loading of the PC. The upper example in the figure shows how the PC is loaded on a write to PCL (PCLATH<4:0>  $\rightarrow$  PCH). The lower example in the figure shows how the PC is loaded during a CALL or GOTO instruction (PCLATH<4:3>  $\rightarrow$  PCH).

#### FIGURE 2-3: LOADING OF PC IN DIFFERENT SITUATIONS

## 2.3.1 COMPUTED GOTO

A computed GOTO is accomplished by adding an offset to the program counter (ADDWF PCL). When doing a table read using a computed GOTO method, care should be exercised if the table location crosses a PCL memory boundary (each 256-byte block). Refer to the application note, *"Implementing a Table Read"* (AN556).

### 2.3.2 STACK

The PIC16FXXX family has an 8-level deep x 13-bit wide hardware stack. The stack space is not part of either program or data space and the stack pointer is not readable or writable. The PC is PUSHed onto the stack when a CALL instruction is executed, or an interrupt causes a branch. The stack is POPed in the event of a RETURN, RETLW or a RETFIE instruction execution. PCLATH is not affected by a PUSH or POP operation.

The stack operates as a circular buffer. This means that after the stack has been PUSHed eight times, the ninth push overwrites the value that was stored from the first push. The tenth push overwrites the second push (and so on).

**Note 1:** There are no status bits to indicate stack overflow or stack underflow conditions.

2: There are no instructions/mnemonics called PUSH or POP. These are actions that occur from the execution of the CALL, RETURN, RETLW and RETFIE instructions, or the vectoring to an interrupt address.

# 2.4 Program Memory Paging

The PIC16FXXX architecture is capable of addressing a continuous 8K word block of program memory. The CALL and GOTO instructions provide 11 bits of the address, which allows branches within any 2K program memory page. Therefore, the 8K words of program memory are broken into four pages. Since the PIC16F872 has only 2K words of program memory or one page, additional code is not required to ensure that the correct page is selected before a CALL or GOTO instruction is executed. The PCLATH<4:3> bits should always be maintained as zeros. If a return from a CALL instruction (or interrupt) is executed, the entire 13-bit PC is popped off the stack. Manipulation of the PCLATH is not required for the return instructions.

# 2.5 Indirect Addressing, INDF and FSR Registers

The INDF register is not a physical register. Addressing the INDF register will cause indirect addressing.

Indirect addressing is possible by using the INDF register. Any instruction using the INDF register actually accesses the register pointed to by the File Select register, FSR. Reading the INDF register itself indirectly (FSR = 0) will read 00h. Writing to the INDF register indirectly results in a no operation (although status bits may be affected). An effective 9-bit address is obtained by concatenating the 8-bit FSR register and the IRP bit (STATUS<7>), as shown in Figure 2-4.

A simple program to clear RAM locations 20h-2Fh using indirect addressing is shown in Example 2-1.

| EXAMPLE 2-1: IND | IRECT ADDRESSING |

|------------------|------------------|

|------------------|------------------|

| NEXT   | movlw<br>movwf<br>clrf<br>incf<br>btfss<br>goto | 0x20<br>FSR<br>INDF<br>FSR,F<br>FSR,4<br>NEXT | ;initialize pointer<br>;to RAM<br>;clear INDF register<br>;inc pointer<br>;all done?<br>;no clear next |

|--------|-------------------------------------------------|-----------------------------------------------|--------------------------------------------------------------------------------------------------------|

| CONTIN | UE                                              |                                               |                                                                                                        |

| :      |                                                 |                                               | ;yes continue                                                                                          |

#### 3.10 FLASH Program Memory Write Protection

The configuration word contains a bit that write protects the FLASH program memory, called WRT. This bit can only be accessed when programming the PIC16F870/871 devices via ICSP. Once write protection is enabled, only an erase of the entire device will disable it. When enabled, write protection prevents any writes to FLASH program memory. Write protection does not affect program memory reads.

| Con | <b>Configuration Bits</b> |     | Momentie           | Internal | Internal |           |            |  |

|-----|---------------------------|-----|--------------------|----------|----------|-----------|------------|--|

| CP1 | CP0                       | WRT | Memory Location    | Read     | Write    | ICSP Read | ICSP Write |  |

| 0   | 0                         | x   | All program memory | Yes      | No       | No        | No         |  |

| 0   | 1                         | 0   | Unprotected areas  | Yes      | No       | Yes       | No         |  |

| 0   | 1                         | 0   | Protected areas    | Yes      | No       | No        | No         |  |

| 0   | 1                         | 1   | Unprotected areas  | Yes      | Yes      | Yes       | No         |  |

| 0   | 1                         | 1   | Protected areas    | Yes      | No       | No        | No         |  |

| 1   | 0                         | 0   | Unprotected areas  | Yes      | No       | Yes       | No         |  |

| 1   | 0                         | 0   | Protected areas    | Yes      | No       | No        | No         |  |

| 1   | 0                         | 1   | Unprotected areas  | Yes      | Yes      | Yes       | No         |  |

| 1   | 0                         | 1   | Protected areas    | Yes      | No       | No        | No         |  |

| 1   | 1                         | 0   | All program memory | Yes      | No       | Yes       | Yes        |  |

| 1   | 1                         | 1   | All program memory | Yes      | Yes      | Yes       | Yes        |  |

## TABLE 3-1: READ/WRITE STATE OF INTERNAL FLASH PROGRAM MEMORY

#### TABLE 3-2: REGISTERS ASSOCIATED WITH DATA EEPROM/PROGRAM FLASH

| Address                 | Name   | Bit 7  | Bit 6   | Bit 5      | Bit 4                           | Bit 3        | Bit 2     | Bit 1 | Bit 0 | Value on:<br>POR, BOR | Value on<br>all other<br>RESETS |

|-------------------------|--------|--------|---------|------------|---------------------------------|--------------|-----------|-------|-------|-----------------------|---------------------------------|

| 0Bh, 8Bh,<br>10Bh, 18Bh | INTCON | GIE    | PEIE    | TOIE       | INTE                            | RBIE         | TOIF      | INTF  | RBIF  | 0000 000x             | 0000 000u                       |

| 10Dh                    | EEADR  | EEPROM | Address | Register   | , Low Byte                      | 9            |           |       |       | xxxx xxxx             | uuuu uuuu                       |

| 10Fh                    | EEADRH |        |         |            | EEPRON                          | 1 Address,   | High Byte |       |       | xxxx xxxx             | uuuu uuuu                       |

| 10Ch                    | EEDATA | EEPROM | Data Re | gister, Lo | w Byte                          |              |           |       |       | xxxx xxxx             | uuuu uuuu                       |

| 10Eh                    | EEDATH |        | _       | EEPRON     | EEPROM Data Register, High Byte |              |           |       |       | xxxx xxxx             | uuuu uuuu                       |

| 18Ch                    | EECON1 | EEPGD  | —       | —          | —                               | WRERR        | WREN      | WR    | RD    | x x000                | x u000                          |

| 18Dh                    | EECON2 | EEPROM | Control | Register2  | (not a ph                       | ysical regis | ster)     |       |       | _                     | _                               |

Legend: x = unknown, u = unchanged, r = reserved, - = unimplemented, read as '0'. Shaded cells are not used during FLASH/EEPROM access.

Note 1: These bits are reserved; always maintain these bits clear.

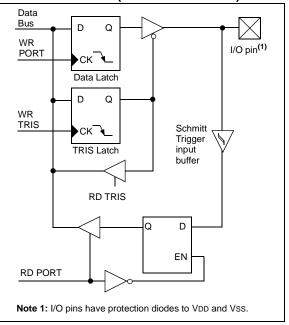

### 4.5 **PORTE and TRISE Register**

This section is not applicable to the PIC16F870.

PORTE has three pins, RE0/RD/AN5, RE1/WR/AN6 and RE2/CS/AN7, which are individually configurable as inputs or outputs. These pins have Schmitt Trigger input buffers.

I/O PORTE becomes control inputs for the microprocessor port when bit PSPMODE (TRISE<4>) is set. In this mode, the user must make sure that the TRISE<2:0> bits are set (pins are configured as digital inputs). Ensure ADCON1 is configured for digital I/O. In this mode, the input buffers are TTL.

Register 4-1 shows the TRISE register, which also controls the parallel slave port operation.

PORTE pins are multiplexed with analog inputs. When selected as an analog input, these pins will read as '0's.

TRISE controls the direction of the RE pins, even when they are being used as analog inputs. The user must make sure to keep the pins configured as inputs when using them as analog inputs.

**Note:** On a Power-on Reset, these pins are configured as analog inputs.

#### FIGURE 4-7: POR

#### PORTE BLOCK DIAGRAM (IN I/O PORT MODE)

| REGISTER 4-1: | TRISE RE                                                                  | GISTER (                                                                                                                     | ADDRESS        | : 89h)                 |               |             |                |       |  |  |  |

|---------------|---------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------|----------------|------------------------|---------------|-------------|----------------|-------|--|--|--|

|               | R-0                                                                       | R-0                                                                                                                          | R/W-0          | R/W-0                  | U-0           | R/W-1       | R/W-1          | R/W-1 |  |  |  |

|               | IBF                                                                       | OBF                                                                                                                          | IBOV           | PSPMODE                |               | Bit2        | Bit1           | Bit0  |  |  |  |

|               | bit 7                                                                     |                                                                                                                              |                |                        |               |             |                | bit 0 |  |  |  |

|               |                                                                           |                                                                                                                              |                |                        |               |             |                |       |  |  |  |

| bit 7         | Parallel Slave Port Status/Control Bits IBF: Input Buffer Full Status bit |                                                                                                                              |                |                        |               |             |                |       |  |  |  |

|               | 1 = A word                                                                | <ul> <li>1 = A word has been received and is waiting to be read by the CPU</li> <li>0 = No word has been received</li> </ul> |                |                        |               |             |                |       |  |  |  |

| bit 6         | OBF: Outp                                                                 | out Buffer Fu                                                                                                                | ull Status bit |                        |               |             |                |       |  |  |  |

|               |                                                                           | utput buffer s<br>utput buffer l                                                                                             |                | previously writt<br>ad | en word       |             |                |       |  |  |  |

| bit 5         | IBOV: Inpu                                                                | ut Buffer Ov                                                                                                                 | erflow Dete    | ct bit (in Microp      | processor m   | ode)        |                |       |  |  |  |

|               | (must                                                                     | e occurred v<br>be cleared<br>erflow occu                                                                                    | in software)   | iously input wo        | ord has not l | been read   |                |       |  |  |  |

| bit 4         | PSPMODE                                                                   | E: Parallel S                                                                                                                | lave Port M    | ode Select bit         |               |             |                |       |  |  |  |

|               | 1 = Parallel Slave Port mode                                              |                                                                                                                              |                |                        |               |             |                |       |  |  |  |

|               |                                                                           | al Purpose I                                                                                                                 |                |                        |               |             |                |       |  |  |  |

| bit 3         |                                                                           | ented: Rea                                                                                                                   |                |                        |               |             |                |       |  |  |  |

| <b>h</b> it 0 |                                                                           | ata Directio                                                                                                                 |                |                        |               |             |                |       |  |  |  |

| bit 2         | 1 = Input                                                                 | tion Control                                                                                                                 | bit for pin r  | RE2/CS/AN7             |               |             |                |       |  |  |  |

|               | 1 = Input 0 = Output                                                      | t                                                                                                                            |                |                        |               |             |                |       |  |  |  |

| bit 1         | -                                                                         |                                                                                                                              | bit for pin F  | RE1/WR/AN6             |               |             |                |       |  |  |  |

|               | 1 = Input<br>0 = Output                                                   | t                                                                                                                            |                |                        |               |             |                |       |  |  |  |

| bit 0         | Bit0: Direc                                                               | tion Contro                                                                                                                  | bit for pin F  | RE0/RD/AN5             |               |             |                |       |  |  |  |

|               | 1 = Input                                                                 |                                                                                                                              |                |                        |               |             |                |       |  |  |  |

|               | 0 = Output                                                                | t                                                                                                                            |                |                        |               |             |                |       |  |  |  |

|               | Legend:                                                                   |                                                                                                                              |                |                        |               |             |                |       |  |  |  |

|               | R = Reada                                                                 | able bit                                                                                                                     | W = \          | Vritable bit           | U = Unimr     | plemented b | oit, read as ' | 0'    |  |  |  |

|               | - n = Value                                                               |                                                                                                                              |                | Bit is set             | '0' = Bit is  |             | x = Bit is u   |       |  |  |  |

|               |                                                                           |                                                                                                                              |                |                        |               |             |                |       |  |  |  |

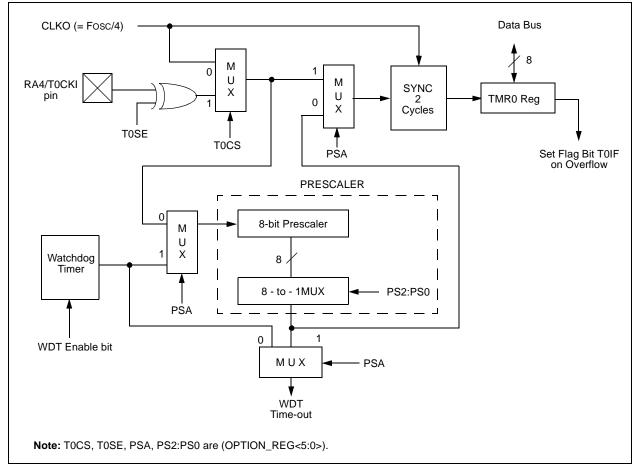

# 5.0 TIMER0 MODULE

The Timer0 module timer/counter has the following features:

- 8-bit timer/counter

- Readable and writable

- 8-bit software programmable prescaler

- · Internal or external clock select

- Interrupt on overflow from FFh to 00h

- Edge select for external clock

Figure 5-1 is a block diagram of the Timer0 module and the prescaler shared with the WDT.

Additional information on the Timer0 module is available in the PIC® Mid-Range MCU Family Reference Manual (DS33023).

Timer mode is selected by clearing bit TOCS (OPTION\_REG<5>). In Timer mode, the Timer0 module will increment every instruction cycle (without prescaler). If the TMR0 register is written, the increment is inhibited for the following two instruction cycles. The user can work around this by writing an adjusted value to the TMR0 register. Counter mode is selected by setting bit T0CS (OPTION\_REG<5>). In Counter mode, Timer0 will increment either on every rising, or falling edge of pin RA4/T0CKI. The incrementing edge is determined by the Timer0 Source Edge Select bit, T0SE (OPTION\_REG<4>). Clearing bit T0SE selects the rising edge. Restrictions on the external clock input are discussed in detail in Section 5.2.

The prescaler is mutually exclusively shared between the Timer0 module and the Watchdog Timer. The prescaler is not readable or writable. Section 5.3 details the operation of the prescaler.

## 5.1 Timer0 Interrupt

The TMR0 interrupt is generated when the TMR0 register overflows from FFh to 00h. This overflow sets bit T0IF (INTCON<2>). The interrupt can be masked by clearing bit T0IE (INTCON<5>). Bit T0IF must be cleared in software by the Timer0 module Interrupt Service Routine before re-enabling this interrupt. The TMR0 interrupt cannot awaken the processor from SLEEP, since the timer is shut-off during SLEEP.

FIGURE 5-1: BLOCK DIAGRAM OF THE TIMER0/WDT PRESCALER

## 6.7 Resetting of Timer1 Register Pair (TMR1H, TMR1L)

TMR1H and TMR1L registers are not reset to 00h on a POR, or any other RESET, except by the CCP1 special event trigger.

T1CON register is reset to 00h on a Power-on Reset, or a Brown-out Reset, which shuts off the timer and leaves a 1:1 prescale. In all other RESETS, the register is unaffected.

## 6.8 Timer1 Prescaler

The prescaler counter is cleared on writes to the TMR1H or TMR1L registers.

## TABLE 6-2: REGISTERS ASSOCIATED WITH TIMER1 AS A TIMER/COUNTER

| Address                | Name   | Bit 7                | Bit 6      | Bit 5       | Bit 4       | Bit 3       | Bit 2      | Bit 1      | Bit 0  | Value<br>POR, |      | all c | e on<br>other<br>SETS |

|------------------------|--------|----------------------|------------|-------------|-------------|-------------|------------|------------|--------|---------------|------|-------|-----------------------|

| 0Bh,8Bh,<br>10Bh, 18Bh | INTCON | GIE                  | PEIE       | TOIE        | INTE        | RBIE        | TOIF       | INTF       | RBIF   | 0000          | 000x | 0000  | 000u                  |

| 0Ch                    | PIR1   | PSPIF <sup>(1)</sup> | ADIF       | RCIF        | TXIF        | _           | CCP1IF     | TMR2IF     | TMR1IF | 0000          | -000 | 0000  | -000                  |

| 8Ch                    | PIE1   | PSPIE <sup>(1)</sup> | ADIE       | RCIE        | TXIE        | _           | CCP1IE     | TMR2IE     | TMR1IE | 0000          | -000 | 0000  | -000                  |

| 0Eh                    | TMR1L  | Holding R            | egister fo | r the Least | Significant | Byte of the | 16-bit TM  | R1 Registe | er     | xxxx          | xxxx | uuuu  | uuuu                  |

| 0Fh                    | TMR1H  | Holding R            | egister fo | r the Most  | Significant | Byte of the | 16-bit TMF | R1 Registe | r      | xxxx          | xxxx | uuuu  | uuuu                  |

| 10h                    | T1CON  | _                    | _          | T1CKPS1     | T1CKPS0     | T1OSCEN     | T1SYNC     | TMR1CS     | TMR10N | 00            | 0000 | uu    | uuuu                  |

Legend: x = unknown, u = unchanged, - = unimplemented, read as '0'. Shaded cells are not used by the Timer1 module.

Note 1: Bits PSPIE and PSPIF are reserved on the PIC16F870; always maintain these bits clear.

# 9.1 USART Baud Rate Generator (BRG)

The BRG supports both the Asynchronous and Synchronous modes of the USART. It is a dedicated 8-bit baud rate generator. The SPBRG register controls the period of a free running 8-bit timer. In Asynchronous mode, bit BRGH (TXSTA<2>) also controls the baud rate. In Synchronous mode, bit BRGH is ignored. Table 9-1 shows the formula for computation of the baud rate for different USART modes which only apply in Master mode (internal clock).

Given the desired baud rate and Fosc, the nearest integer value for the SPBRG register can be calculated using the formula in Table 9-1. From this, the error in baud rate can be determined.

It may be advantageous to use the high baud rate (BRGH = 1), even for slower baud clocks. This is because the FOSC/(16(X + 1)) equation can reduce the baud rate error in some cases.

Writing a new value to the SPBRG register causes the BRG timer to be reset (or cleared). This ensures the BRG does not wait for a timer overflow before outputting the new baud rate.

#### 9.1.1 SAMPLING

The data on the RC7/RX/DT pin is sampled three times by a majority detect circuit to determine if a high or a low level is present at the RX pin.

## TABLE 9-1: BAUD RATE FORMULA

| SYNC | BRGH = 0 (Low Speed)                      | BRGH = 1 (High Speed)      |

|------|-------------------------------------------|----------------------------|

| 0    | (Asynchronous) Baud Rate = Fosc/(64(X+1)) | Baud Rate = Fosc/(16(X+1)) |

| 1    | (Synchronous) Baud Rate = FOSC/(4(X+1))   | N/A                        |

|      |                                           |                            |

Legend: X = value in SPBRG (0 to 255)

#### TABLE 9-2: REGISTERS ASSOCIATED WITH BAUD RATE GENERATOR

| Address | Name  | Bit 7    | Bit 6                                                | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Value on:<br>POR, BOR | Value on<br>all other<br>RESETS |

|---------|-------|----------|------------------------------------------------------|-------|-------|-------|-------|-------|-------|-----------------------|---------------------------------|

| 98h     | TXSTA | CSRC     | TX9                                                  | TXEN  | SYNC  |       | BRGH  | TRMT  | TX9D  | 0000 -010             | 0000 -010                       |

| 18h     | RCSTA | SPEN     | RX9                                                  | SREN  | CREN  | ADDEN | FERR  | OERR  | RX9D  | 0000 000x             | x000 000x                       |

| 99h     | SPBRG | Baud Rat | Baud Rate Generator Register     0000 0000 0000 0000 |       |       |       |       |       |       |                       |                                 |

Legend: x = unknown, - = unimplemented, read as '0'. Shaded cells are not used by the BRG.

#### 11.11 Context Saving During Interrupts

During an interrupt, only the return PC value is saved on the stack. Typically, users may wish to save key registers during an interrupt, (i.e., W register and STATUS register). This will have to be implemented in software.

For the PIC16F870/871 devices, the register W\_TEMP must be defined in both banks 0 and 1 and must be defined at the same offset from the bank base address (i.e., If W\_TEMP is defined at 0x20 in bank 0, it must also be defined at 0xA0 in bank 1). The registers, PCLATH\_TEMP and STATUS\_TEMP, are only defined in bank 0.

Since the upper 16 bytes of each bank are common in the PIC16F870/871 devices, temporary holding registers W\_TEMP, STATUS\_TEMP, and PCLATH\_TEMP should be placed in here. These 16 locations don't require banking and therefore, make it easier for context save and restore. The same code shown in Example 11-1 can be used.

#### EXAMPLE 11-1: SAVING STATUS, W, AND PCLATH REGISTERS IN RAM

| MOVWF  | W_TEMP         | ;Copy W to TEMP register                                |

|--------|----------------|---------------------------------------------------------|

| SWAPF  | STATUS,W       | ;Swap status to be saved into W                         |

| CLRF   | STATUS         | ;bank 0, regardless of current bank, Clears IRP,RP1,RP0 |

| MOVWF  | STATUS TEMP    | ;Save status to bank zero STATUS TEMP register          |

| MOVF   | PCLATH, W      | ;Only required if using pages 1, 2 and/or 3             |

| MOVWF  | PCLATH_TEMP    | ;Save PCLATH into W                                     |

| CLRF   | PCLATH         | ;Page zero, regardless of current page                  |

| :      |                |                                                         |

| :(ISR) |                | ;(Insert user code here)                                |

| :      |                |                                                         |

| MOVF   | PCLATH_TEMP, W | ;Restore PCLATH                                         |

| MOVWF  | PCLATH         | ;Move W into PCLATH                                     |

| SWAPF  | STATUS_TEMP,W  | ;Swap STATUS_TEMP register into W                       |

|        |                | ;(sets bank to original state)                          |

| MOVWF  | STATUS         | ;Move W into STATUS register                            |

| SWAPF  | W_TEMP,F       | ;Swap W_TEMP                                            |

| SWAPF  | W_TEMP,W       | ;Swap W_TEMP into W                                     |

|        |                |                                                         |

| ADDLW            | Add Literal and W                                                                                                          |

|------------------|----------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] ADDLW k                                                                                                   |

| Operands:        | $0 \le k \le 255$                                                                                                          |

| Operation:       | $(W) + k \to (W)$                                                                                                          |

| Status Affected: | C, DC, Z                                                                                                                   |

| Description:     | The contents of the W register<br>are added to the eight-bit literal 'k'<br>and the result is placed in the W<br>register. |

| ADDWF            | Add W and f                                                                                                                                                                    |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] ADDWF f,d                                                                                                                                                              |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \end{array}$                                                                                                                |

| Operation:       | (W) + (f) $\rightarrow$ (destination)                                                                                                                                          |

| Status Affected: | C, DC, Z                                                                                                                                                                       |

| Description:     | Add the contents of the W register<br>with register 'f'. If 'd' is 0, the result<br>is stored in the W register. If 'd' is<br>1, the result is stored back in<br>register 'f'. |

| BCF              | Bit Clear f                                                         |

|------------------|---------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ]BCF f,b                                             |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ 0 \leq b \leq 7 \end{array}$ |

| Operation:       | $0 \rightarrow (f < b >)$                                           |

| Status Affected: | None                                                                |

| Description:     | Bit 'b' in register 'f' is cleared.                                 |

| BSF              | Bit Set f                                                           |

|------------------|---------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] BSF f,b                                            |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ 0 \leq b \leq 7 \end{array}$ |

| Operation:       | $1 \rightarrow (f < b >)$                                           |

| Status Affected: | None                                                                |

| Description:     | Bit 'b' in register 'f' is set.                                     |

| ANDLW            | AND Literal with W                                                                                                     |  |  |  |

|------------------|------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Syntax:          | [ <i>label</i> ] ANDLW k                                                                                               |  |  |  |

| Operands:        | $0 \leq k \leq 255$                                                                                                    |  |  |  |

| Operation:       | (W) .AND. (k) $\rightarrow$ (W)                                                                                        |  |  |  |

| Status Affected: | Z                                                                                                                      |  |  |  |

| Description:     | The contents of W register are<br>AND'ed with the eight-bit literal<br>'k'. The result is placed in the W<br>register. |  |  |  |

| BTFSS            | Bit Test f, Skip if Set                                                                                                                                                                           |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ label ] BTFSS f,b                                                                                                                                                                               |

| Operands:        | $0 \le f \le 127$<br>$0 \le b < 7$                                                                                                                                                                |

| Operation:       | skip if (f <b>) = 1</b>                                                                                                                                                                           |

| Status Affected: | None                                                                                                                                                                                              |

| Description:     | If bit 'b' in register 'f' is '0', the next instruction is executed.<br>If bit 'b' is '1', then the next instruction is discarded and a NOP is executed instead, making this a 2 TCY instruction. |

| ANDWF            | AND W with f                                                                                                                                                |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] ANDWF f,d                                                                                                                                  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \end{array}$                                                                                             |

| Operation:       | (W) .AND. (f) $\rightarrow$ (destination)                                                                                                                   |

| Status Affected: | Z                                                                                                                                                           |

| Description:     | AND the W register with register<br>'f'. If 'd' is 0, the result is stored in<br>the W register. If 'd' is 1, the result<br>is stored back in register 'f'. |

| BTFSC            | Bit Test, Skip if Clear                                                                                                                                                                                         |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ label ] BTFSC f,b                                                                                                                                                                                             |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ 0 \leq b \leq 7 \end{array}$                                                                                                                                             |

| Operation:       | skip if (f <b>) = <math>0</math></b>                                                                                                                                                                            |

| Status Affected: | None                                                                                                                                                                                                            |

| Description:     | If bit 'b' in register 'f' is '1', the next instruction is executed.<br>If bit 'b', in register 'f', is '0', the next instruction is discarded, and a NOP is executed instead, making this a 2 TCY instruction. |

| MOVF             | Move f                                                                                                                                                                                                                                                                            |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] MOVF f,d                                                                                                                                                                                                                                                         |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d  \in  [0,1] \end{array}$                                                                                                                                                                                                                 |

| Operation:       | (f) $\rightarrow$ (destination)                                                                                                                                                                                                                                                   |

| Status Affected: | Z                                                                                                                                                                                                                                                                                 |

| Description:     | The contents of register f are<br>moved to a destination dependant<br>upon the status of d. If $d = 0$ ,<br>destination is W register. If $d = 1$ ,<br>the destination is file register f itself.<br>d = 1 is useful to test a file register,<br>since status flag Z is affected. |

| NOP              | No Operation  |

|------------------|---------------|

| Syntax:          | [label] NOP   |

| Operands:        | None          |

| Operation:       | No operation  |

| Status Affected: | None          |

| Description:     | No operation. |

| MOVLW            | Move Literal to W                                                                                |

|------------------|--------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] MOVLW k                                                                         |

| Operands:        | $0 \leq k \leq 255$                                                                              |

| Operation:       | $k \rightarrow (W)$                                                                              |

| Status Affected: | None                                                                                             |

| Description:     | The eight-bit literal 'k' is loaded<br>into W register. The don't cares<br>will assemble as 0's. |

| RETFIE           | Return from Interrupt                      |

|------------------|--------------------------------------------|

| Syntax:          | [label] RETFIE                             |

| Operands:        | None                                       |

| Operation:       | $TOS \rightarrow PC, \\ 1 \rightarrow GIE$ |

| Status Affected: | None                                       |

| MOVWF            | Move W to f                                |

|------------------|--------------------------------------------|

| Syntax:          | [ <i>label</i> ] MOVWF f                   |

| Operands:        | $0 \leq f \leq 127$                        |

| Operation:       | $(W) \rightarrow (f)$                      |

| Status Affected: | None                                       |

| Description:     | Move data from W register to register 'f'. |

| RETLW            | Return with Literal in W                                                                                                                                                            |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] RETLW k                                                                                                                                                            |

| Operands:        | $0 \leq k \leq 255$                                                                                                                                                                 |

| Operation:       | $k \rightarrow (W);$<br>TOS $\rightarrow$ PC                                                                                                                                        |

| Status Affected: | None                                                                                                                                                                                |

| Description:     | The W register is loaded with the<br>eight-bit literal 'k'. The program<br>counter is loaded from the top of<br>the stack (the return address).<br>This is a two-cycle instruction. |

## 13.14 PICDEM 1 PIC MCU Demonstration Board

The PICDEM 1 demonstration board demonstrates the capabilities of the PIC16C5X (PIC16C54 to PIC16C58A), PIC16C61, PIC16C62X, PIC16C71, PIC16C8X, PIC17C42, PIC17C43 and PIC17C44. All necessary hardware and software is included to run basic demo programs. The sample microcontrollers provided with the PICDEM 1 demonstration board can be programmed with a PRO MATE II device programmer, or a PICSTART Plus development programmer. The PICDEM 1 demonstration board can be connected to the MPLAB ICE in-circuit emulator for testing. A prototype area extends the circuitry for additional application components. Features include an RS-232 interface, a potentiometer for simulated analog input, push button switches and eight LEDs.

## 13.15 PICDEM.net Internet/Ethernet Demonstration Board

The PICDEM.net demonstration board is an Internet/ Ethernet demonstration board using the PIC18F452 microcontroller and TCP/IP firmware. The board supports any 40-pin DIP device that conforms to the standard pinout used by the PIC16F877 or PIC18C452. This kit features a user friendly TCP/IP stack, web server with HTML, a 24L256 Serial EEPROM for Xmodem download to web pages into Serial EEPROM, ICSP/MPLAB ICD 2 interface connector, an Ethernet interface, RS-232 interface, and a 16 x 2 LCD display. Also included is the book and CD-ROM *"TCP/IP Lean, Web Servers for Embedded Systems,"* by Jeremy Bentham

# 13.16 PICDEM 2 Plus Demonstration Board

The PICDEM 2 Plus demonstration board supports many 18-, 28-, and 40-pin microcontrollers, including PIC16F87X and PIC18FXX2 devices. All the necessarv hardware and software is included to run the demonstration programs. The sample microcontrollers provided with the PICDEM 2 demonstration board can be programmed with a PRO MATE II device programmer, PICSTART Plus development programmer, or MPLAB ICD 2 with a Universal Programmer Adapter. The MPLAB ICD 2 and MPLAB ICE in-circuit emulators may also be used with the PICDEM 2 demonstration board to test firmware. A prototype area extends the circuitry for additional application components. Some of the features include an RS-232 interface, a 2 x 16 LCD display, a piezo speaker, an on-board temperature sensor, four LEDs, and sample PIC18F452 and PIC16F877 FLASH microcontrollers.

# 13.17 PICDEM 3 PIC16C92X Demonstration Board

The PICDEM 3 demonstration board supports the PIC16C923 and PIC16C924 in the PLCC package. All the necessary hardware and software is included to run the demonstration programs.

# 13.18 PICDEM 4 8/14/18-Pin Demonstration Board

The PICDEM 4 can be used to demonstrate the capabilities of the 8-, 14-, and 18-pin PIC16XXXX and PIC18XXXX MCUs, including the PIC16F818/819, PIC16F87/88, PIC16F62XA and the PIC18F1320 family of microcontrollers. PICDEM 4 is intended to showcase the many features of these low pin count parts, including LIN and Motor Control using ECCP. Special provisions are made for low power operation with the supercapacitor circuit, and jumpers allow on-board hardware to be disabled to eliminate current draw in this mode. Included on the demo board are provisions for Crystal, RC or Canned Oscillator modes, a five volt regulator for use with a nine volt wall adapter or battery, DB-9 RS-232 interface. ICD connector for programming via ICSP and development with MPLAB ICD 2, 2x16 liquid crystal display, PCB footprints for H-Bridge motor driver, LIN transceiver and EEPROM. Also included are: header for expansion, eight LEDs, four potentiometers, three push buttons and a prototyping area. Included with the kit is a PIC16F627A and a PIC18F1320. Tutorial firmware is included along with the User's Guide.

## 13.19 PICDEM 17 Demonstration Board

The PICDEM 17 demonstration board is an evaluation board that demonstrates the capabilities of several Microchip microcontrollers, including PIC17C752, PIC17C756A, PIC17C762 and PIC17C766. A programmed sample is included. The PRO MATE II device programmer, or the PICSTART Plus development programmer, can be used to reprogram the device for user tailored application development. The PICDEM 17 demonstration board supports program download and execution from external on-board FLASH memory. A generous prototype area is available for user hardware expansion.

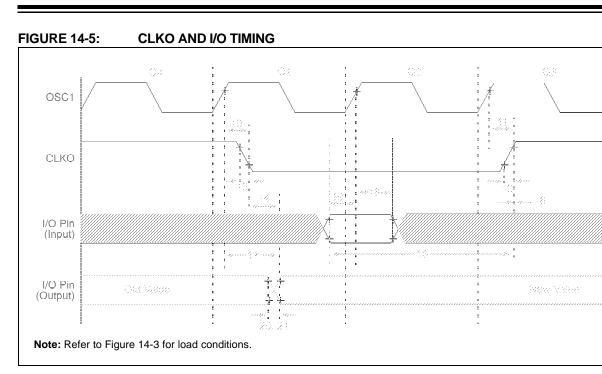

| <b>TABLE 14-2:</b> | CLKO AND I/O TIMING REQUIREMENTS |

|--------------------|----------------------------------|

|--------------------|----------------------------------|

| Param<br>No. | Sym      | Characteristic                                |               | Min        | Тур† | Мах          | Units | Conditions |

|--------------|----------|-----------------------------------------------|---------------|------------|------|--------------|-------|------------|

| 10*          | TosH2ckL | OSC1↑ to CLKO↓                                |               | _          | 75   | 200          | ns    | (Note 1)   |

| 11*          | TosH2ckH | OSC1↑ to CLKO↑                                |               | _          | 75   | 200          | ns    | (Note 1)   |

| 12*          | TckR     | CLKO rise time                                |               | —          | 35   | 100          | ns    | (Note 1)   |

| 13*          | TckF     | CLKO fall time                                |               | _          | 35   | 100          | ns    | (Note 1)   |

| 14*          | TckL2ioV | CLKO↓ to Port out valid                       |               |            | —    | 0.5 Tcy + 20 | ns    | (Note 1)   |

| 15*          | TioV2ckH | Port in valid before CLKO↑                    |               | Tosc + 200 | _    | —            | ns    | (Note 1)   |

| 16*          | TckH2iol | Port in hold after CLKO↑                      |               | 0          | _    | _            | ns    | (Note 1)   |

| 17*          | TosH2ioV | OSC1↑ (Q1 cycle) to Port out val              | lid           |            | 100  | 255          | ns    |            |

| 18*          | TosH2iol | OSC1↑ (Q2 cycle) to Port input                | Standard (F)  | 100        | —    | —            | ns    |            |

|              |          | invalid (I/O in hold time)                    | Extended (LF) | 200        | _    | _            | ns    |            |

| 19*          | TioV2osH | Port input valid to OSC1 <sup>↑</sup> (I/O in | setup time)   | 0          | _    | —            | ns    |            |

| 20*          | TIOR     | Port output rise time                         | Standard (F)  | _          | 10   | 40           | ns    |            |

|              |          |                                               | Extended (LF) | _          | _    | 145          | ns    |            |

| 21*          | TIOF     | Port output fall time                         | Standard (F)  |            | 10   | 40           | ns    |            |

|              |          |                                               | Extended (LF) | _          | _    | 145          | ns    |            |

| 22††*        | TINP     | INT pin high or low time                      |               | Тсү        | —    | _            | ns    |            |

| 23††*        | Trbp     | RB7:RB4 change INT high or low                | v time        | Тсү        | _    | —            | ns    |            |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

tt These parameters are asynchronous events not related to any internal clock edges.

Note 1: Measurements are taken in RC mode where CLKO output is 4 x Tosc.

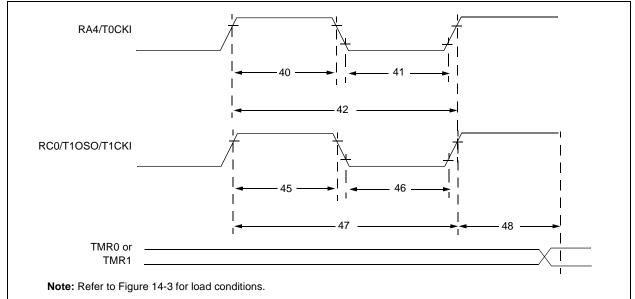

#### FIGURE 14-8: TIMER0 AND TIMER1 EXTERNAL CLOCK TIMINGS

| Param<br>No. | Sym       |                                                | Characteristic     |                       | Min                                              | Тур†                        | Max          | Units | Conditions                         |

|--------------|-----------|------------------------------------------------|--------------------|-----------------------|--------------------------------------------------|-----------------------------|--------------|-------|------------------------------------|

| 40*          | Tt0H      | T0CKI High Pulse V                             | Vidth              | No Prescaler          | 0.5 TCY + 20                                     | —                           | _            | ns    | Must also meet                     |

|              |           |                                                |                    | With Prescaler        | 10                                               | _                           | _            | ns    | parameter 42                       |

| 41*          | Tt0L      | T0CKI Low Pulse W                              | /idth              | No Prescaler          | 0.5 TCY + 20                                     | —                           | _            | ns    | Must also meet                     |

|              |           |                                                |                    | With Prescaler        | 10                                               | —                           |              | ns    | parameter 42                       |

| 42*          | Tt0P      | T0CKI Period                                   |                    | No Prescaler          | TCY + 40                                         | —                           | _            | ns    |                                    |

|              |           |                                                |                    | With Prescaler        | Greater of:<br>20 or <u>TcY + 40</u><br>N        | -                           |              | ns    | N = prescale value<br>(2, 4,, 256) |

| 45*          | Tt1H      | T1CKI High Time                                | Synchronous, Pres  | scaler = 1            | 0.5 TCY + 20                                     | —                           | _            | ns    | Must also meet                     |

|              |           |                                                | Synchronous,       | Standard(F)           | 15                                               | 15 — <u>ns</u> parameter 47 | parameter 47 |       |                                    |

|              |           |                                                | Prescaler = 2,4,8  | Extended(LF)          | 25                                               | —                           |              | ns    |                                    |

|              |           |                                                | Asynchronous       | Standard(F)           | 30                                               | —                           | —            | ns    |                                    |

|              |           |                                                |                    | Extended(LF)          | 50                                               | —                           | _            | ns    |                                    |

| 46*          | Tt1L      | T1CKI Low Time                                 | Synchronous, Pres  | scaler = 1            | 0.5 TCY + 20                                     | _                           |              | ns    | Must also meet                     |

|              |           |                                                | Synchronous,       | Standard(F)           | 15                                               | —                           |              | ns    | parameter 47                       |

|              |           |                                                | Prescaler = 2,4,8  | Extended(LF)          | 25                                               | —                           |              | ns    |                                    |

|              |           |                                                | Asynchronous       | Standard(F)           | 30                                               | —                           | _            | ns    |                                    |

|              |           |                                                |                    | Extended(LF)          | 50                                               | —                           | _            | ns    |                                    |

| 47*          | Tt1P      | T1CKI input period                             | Synchronous        | Standard( <b>F</b> )  | <u>Greater of:</u><br>30 or <u>Tcy + 40</u><br>N | _                           |              | ns    | N = prescale value<br>(1, 2, 4, 8) |

|              |           |                                                |                    | Extended( <b>LF</b> ) | <u>Greater of:</u><br>50 or <u>Tcy + 40</u><br>N |                             |              |       | N = prescale value<br>(1, 2, 4, 8) |

|              |           |                                                | Asynchronous       | Standard(F)           | 60                                               | —                           | _            | ns    |                                    |

|              |           |                                                |                    | Extended(LF)          | 100                                              | _                           | _            | ns    |                                    |

|              | Ft1       | Timer1 oscillator inp<br>(oscillator enabled b |                    |                       | DC                                               | —                           | 200          | kHz   |                                    |

| 48           | TCKEZtmr1 | Delay from external                            | clock edge to time | rincrement            | 2 Tosc                                           | —                           | 7 Tosc       | —     |                                    |

| TABLE 14-4: | TIMER0 AND TIMER1 EXTERNAL CLOCK REQUIREMENTS |

|-------------|-----------------------------------------------|

|             |                                               |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

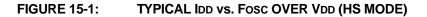

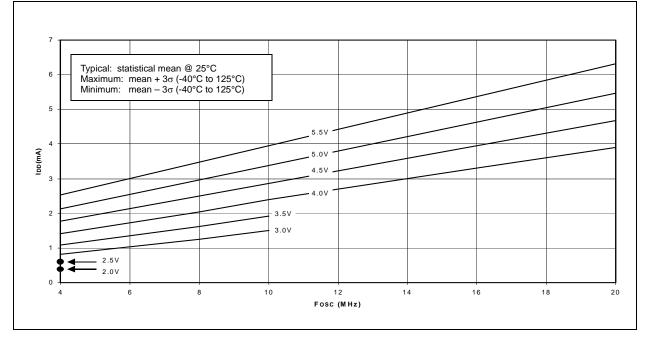

# 15.0 DC AND AC CHARACTERISTICS GRAPHS AND TABLES

**Note:** The graphs and tables provided following this note are a statistical summary based on a limited number of samples and are provided for informational purposes only. The performance characteristics listed herein are not tested or guaranteed. In some graphs or tables, the data presented may be outside the specified operating range (e.g., outside specified power supply range) and therefore, outside the warranted range.

"Typical" represents the mean of the distribution at 25°C. "Maximum" or "minimum" represents (mean +  $3\sigma$ ) or (mean -  $3\sigma$ ) respectively, where  $\sigma$  is a standard deviation, over the whole temperature range.

FIGURE 15-2: MAXIMUM IDD vs. Fosc OVER VDD (HS MODE)

© 2000-2013 Microchip Technology Inc.

# APPENDIX C: CONVERSION CONSIDERATIONS

This appendix discusses the considerations for converting from previous versions of a device to the ones listed in this data sheet. Typically, these changes are due to the differences in the process technology used. An example of this type of conversion is from a PIC17C756 to a PIC18F8720.

#### **Not Applicable**

# APPENDIX D: MIGRATION FROM MID-RANGE TO ENHANCED DEVICES

A detailed discussion of the differences between the mid-range MCU devices (i.e., PIC16CXXX) and the enhanced devices (i.e., PIC18FXXX) is provided in AN716, "Migrating Designs from PIC16C74A/74B to PIC18C442." The changes discussed, while device specific, are generally applicable to all mid-range to enhanced device migrations.

This Application Note is available as Literature Number DS00716.

# APPENDIX E: MIGRATION FROM HIGH-END TO ENHANCED DEVICES

A detailed discussion of the migration pathway and differences between the high-end MCU devices (i.e., PIC17CXXX) and the enhanced devices (i.e., PIC18FXXX) is provided in AN726, "PIC17CXXX to PIC18CXXX Migration." This Application Note is available as Literature Number DS00726.

| PORTC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Associated Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| PORTC Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| RC0/T1OSO/T1CKI Pin7, 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| RC1/T1OSI Pin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |