Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                   |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 20MHz                                                                    |

| Connectivity               | UART/USART                                                               |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                    |

| Number of I/O              | 22                                                                       |

| Program Memory Size        | 3.5KB (2K x 14)                                                          |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | 64 x 8                                                                   |

| RAM Size                   | 128 x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 4V ~ 5.5V                                                                |

| Data Converters            | A/D 5x10b                                                                |

| Oscillator Type            | External                                                                 |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                           |

| Supplier Device Package    | 28-SOIC                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f870-i-so |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### PIC16F870/871 REGISTER FILE MAP

|                      | File<br>Address |                      | File<br>Address |                     | File<br>Address |                         | File<br>Addres |

|----------------------|-----------------|----------------------|-----------------|---------------------|-----------------|-------------------------|----------------|

| ndirect addr.(*)     | 00h             | Indirect addr.(*)    | 80h             | Indirect addr.(*)   | 100h            | Indirect addr.(*)       | 180ŀ           |

| TMR0                 | 01h             | OPTION_REG           | 81h             | TMR0                | 101h            | OPTION_REG              | 181ŀ           |

| PCL                  | 02h             | PCL                  | 82h             | PCL                 | 102h            | PCL                     | 182ł           |

| STATUS               | 03h             | STATUS               | 83h             | STATUS              | 103h            | STATUS                  | 183ł           |

| FSR                  | 04h             | FSR                  | 84h             | FSR                 | 104h            | FSR                     | 184ł           |

| PORTA                | 05h             | TRISA                | 85h             |                     | 105h            |                         | 185ł           |

| PORTB                | 06h             | TRISB                | 86h             | PORTB               | 106h            | TRISB                   | 186ł           |

| PORTC                | 07h             | TRISC                | 87h             |                     | 107h            |                         | 187ł           |

| PORTD <sup>(2)</sup> | 08h             | TRISD <sup>(2)</sup> | 88h             |                     | 108h            |                         | 188ł           |

| PORTE <sup>(2)</sup> | 09h             | TRISE <sup>(2)</sup> | 89h             |                     | 109h            |                         | 189            |

| PCLATH               | 0Ah             | PCLATH               | 8Ah             | PCLATH              | 10Ah            | PCLATH                  | 18A            |

| INTCON               | 0Bh             | INTCON               | 8Bh             | INTCON              | 10Bh            | INTCON                  | 18B            |

| PIR1                 | 0Ch             | PIE1                 | 8Ch             | EEDATA              | 10Ch            | EECON1                  | 18C            |

| PIR2                 | 0Dh             | PIE2                 | 8Dh             | EEADR               | 10Dh            | EECON2                  | 18D            |

| TMR1L                | 0Eh             | PCON                 | 8Eh             | EEDATH              | 10Eh            | Reserved <sup>(1)</sup> | 18E            |

| TMR1H                | 0Fh             |                      | 8Fh             | EEADRH              | 10Fh            | Reserved <sup>(1)</sup> | 18F            |

| T1CON                | 10h             |                      | 90h             |                     | 110h            |                         | 190            |

| TMR2                 | 11h             |                      | 91h             |                     |                 |                         |                |

| T2CON                | 12h             | PR2                  | 92h             |                     |                 |                         |                |

|                      | 13h             |                      | 93h             |                     |                 |                         |                |

|                      | 14h             |                      | 94h             |                     |                 |                         |                |

| CCPR1L               | 15h             |                      | 95h             |                     |                 |                         |                |

| CCPR1H               | 16h             |                      | 96h             |                     |                 |                         |                |

| CCP1CON              | 17h             |                      | 97h             |                     |                 |                         |                |

| RCSTA                | 18h             | TXSTA                | 98h             |                     |                 |                         |                |

| TXREG                | 19h             | SPBRG                | 99h             |                     |                 |                         |                |

| RCREG                | 1Ah             |                      | 9Ah             |                     |                 |                         |                |

|                      | 1Bh             |                      | 9Bh             |                     |                 |                         |                |

|                      | 1Ch             |                      | 9Ch             |                     |                 |                         |                |

|                      | 1Dh             |                      | 9Dh             |                     |                 |                         |                |

| ADRESH               | 1Eh             | ADRESL               | 9Eh             |                     |                 |                         |                |

| ADCON0               | 1Fh             | ADCON1               | 9Fh             |                     | 1005            |                         | 1 4 01         |

|                      | 20h             | General<br>Purpose   | A0h             | accesses            | 120h            | accesses                | 1A0            |

| General              |                 | Register             |                 | 20h-7Fh             |                 | A0h - BFh               |                |

| Purpose<br>Register  |                 | 32 Bytes             | BFh<br>C0h      |                     |                 |                         | 1BF<br>1C0     |

| 96 Bytes             |                 |                      | EFh<br>F0h      |                     | 16Fh<br>170h    |                         | 1EF            |

|                      | 7Fh             | accesses<br>70h-7Fh  | FFh             | accesses<br>70h-7Fh | 17Fh            | accesses<br>70h-7Fh     | 1F0I<br>1FF    |

| Bank 0               |                 | Bank 1               |                 | Bank 2              |                 | Bank 3                  |                |

\* Not a physical register.

Note 1: These registers are reserved; maintain these registers clear.

2: These registers are not implemented on the PIC16F870.

#### 2.2.2.4 **PIE1** Register

The PIE1 register contains the individual enable bits for the peripheral interrupts.

| Note: | Bit PEIE (INTCON<6>) must be set to |

|-------|-------------------------------------|

|       | enable any peripheral interrupt.    |

| <b>REGISTER 2-4:</b> | PIE1 REGI                  | STER (AD     | DRESS:        | 8Ch)          |                |              |           |        |

|----------------------|----------------------------|--------------|---------------|---------------|----------------|--------------|-----------|--------|

|                      | R/W-0                      | R/W-0        | R/W-0         | R/W-0         | U-0            | R/W-0        | R/W-0     | R/W-0  |

|                      | PSPIE <sup>(1)</sup>       | ADIE         | RCIE          | TXIE          | —              | CCP1IE       | TMR2IE    | TMR1IE |

|                      | bit 7                      |              |               |               |                |              |           | bit 0  |

|                      |                            |              |               |               |                |              |           |        |

| bit 7                | PSPIE <sup>(1)</sup> : P   | arallel Slav | e Port Read   | d/Write Inter | rupt Enable bi | t            |           |        |

|                      | 1 = Enables<br>0 = Disable |              |               |               |                |              |           |        |

| bit 6                | ADIE: A/D                  | Converter li | nterrupt Ena  | able bit      |                |              |           |        |

|                      | 1 = Enable:<br>0 = Disable |              |               | •             |                |              |           |        |

| bit 5                | RCIE: USA                  | RT Receive   | Interrupt E   | nable bit     |                |              |           |        |

|                      | 1 = Enables                |              |               |               |                |              |           |        |

|                      | 0 = Disable                | s the USAF   | RT receive i  | nterrupt      |                |              |           |        |

| bit 4                | TXIE: USA                  | RT Transmi   | t Interrupt E | nable bit     |                |              |           |        |

|                      | 1 = Enables<br>0 = Disable |              |               | •             |                |              |           |        |

| bit 3                | Unimplem                   | ented: Rea   | d as '0'      |               |                |              |           |        |

| bit 2                | CCP1IE: C                  | CP1 Interru  | pt Enable b   | it            |                |              |           |        |

|                      | 1 = Enables                |              | •             |               |                |              |           |        |

|                      | 0 = Disable                | s the CCP1   | interrupt     |               |                |              |           |        |

| bit 1                | TMR2IE: TI                 | MR2 to PR2   | 2 Match Inte  | errupt Enabl  | e bit          |              |           |        |

|                      |                            |              |               | tch interrup  |                |              |           |        |

|                      |                            |              |               | atch interrup | ot             |              |           |        |

| bit 0                | TMR1IE: TI                 |              | -             |               |                |              |           |        |

|                      | 1 = Enables                |              |               | •             |                |              |           |        |

|                      | 0 = Disable                | s the TIVIR1 | overnow II    | iterrupt      |                |              |           |        |

|                      | Note 1.                    |              |               |               | 070. alwaya m  | aintain thia | hit cloar |        |

Note 1: PSPIE is reserved on the PIC16F870; always maintain this bit clear.

| Legend:            |                  |                      |                    |

|--------------------|------------------|----------------------|--------------------|

| R = Readable bit   | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

| - n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

#### 2.2.2.7 PIR2 Register

The PIR2 register contains the flag bit for the EEPROM write operation interrupt.

```

Note: Interrupt flag bits get set when an interrupt condition occurs, regardless of the state of its corresponding enable bit or the global enable bit, GIE (INTCON<7>). User software should ensure the appropriate interrupt flag bits are clear prior to enabling an interrupt.

```

#### REGISTER 2-7: PIR2 REGISTER (ADDRESS: 0Dh)

| U-0   | U-0 | U-0 | R/W-0 | U-0 | U-0 | U-0 | U-0   |

|-------|-----|-----|-------|-----|-----|-----|-------|

| —     | —   | —   | EEIF  | —   | —   | _   | —     |

| bit 7 |     |     |       |     |     |     | bit 0 |

#### bit 7-5 Unimplemented: Read as '0'

bit 4 **EEIF**: EEPROM Write Operation Interrupt Flag bit

- 1 = The write operation completed (must be cleared in software)

- 0 = The write operation is not complete or has not been started

bit 3-0 Unimplemented: Read as '0'

| Legend:            |                  |                      |                    |

|--------------------|------------------|----------------------|--------------------|

| R = Readable bit   | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

| - n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

At the completion of the write cycle, the WR bit is cleared and the EEIF interrupt flag bit is set. (EEIF must be cleared by firmware.) Since the microcontroller does not execute instructions during the write cycle, the firmware does not necessarily have to check either EEIF, or WR, to determine if the write had finished.

EXAMPLE 3-4: FLASH PROGRAM WRITE

| BSF<br>BCF | STATUS, RP1<br>STATUS, RP0 | ;<br>;Bank 2             |

|------------|----------------------------|--------------------------|

|            | ADDRL, W                   |                          |

|            | EEADR                      | ;of desired              |

| MOVF       |                            |                          |

| MOVWF      | ,<br>EEADRH                | 1 5 1                    |

|            | VALUEL, W                  |                          |

|            | EEDATA                     | ;program at              |

| MOVF       | VALUEH, W                  | ;desired memory          |

| MOVWF      | EEDATH                     | ;location                |

| BSF        | STATUS, RPO                | ;Bank 3                  |

| BSF        | EECON1, EEPGD              | ;Point to Program memory |

| BSF        | EECON1, WREN               | ;Enable writes           |

|            |                            | ;Only disable interrupts |

| BCF        | INTCON, GIE                | ; if already enabled,    |

|            |                            | ;otherwise discard       |

| MOVLW      | 0x55                       | ;Write 55h to            |

| MOVWF      | EECON2                     | ;EECON2                  |

| MOVLW      | 0xAA                       | ;Write AAh to            |

|            | EECON2                     | ;EECON2                  |

| BSF        | EECON1, WR                 | ;Start write operation   |

| NOP        |                            | ;Two NOPs to allow micro |

| NOP        |                            | ;to setup for write      |

|            |                            | ;Only enable interrupts  |

| BSF        | INTCON, GIE                |                          |

|            |                            | ;otherwise discard       |

| BCF        | EECON1, WREN               | ;Disable writes          |

### 3.7 Write Verify

The PIC16F870/871 devices do not automatically verify the value written during a write operation. Depending on the application, good programming practice may dictate that the value written to memory be verified against the original value. This should be used in applications where excessive writes can stress bits near the specified endurance limits.

#### 3.8 Protection Against Spurious Writes

There are conditions when the device may not want to write to the EEPROM data memory or FLASH program memory. To protect against these spurious write conditions, various mechanisms have been built into the PIC16F870/871 devices. On power-up, the WREN bit is cleared and the Power-up Timer (if enabled) prevents writes.

The write initiate sequence and the WREN bit together, help prevent any accidental writes during brown-out, power glitches, or firmware malfunction.

#### 3.9 Operation While Code Protected

The PIC16F870/871 devices have two code protect mechanisms, one bit for EEPROM data memory and two bits for FLASH program memory. Data can be read and written to the EEPROM data memory, regardless of the state of the code protection bit, CPD. When code protection is enabled and CPD cleared, external access via ICSP is disabled, regardless of the state of the program memory code protect bits. This prevents the contents of EEPROM data memory from being read out of the device.

The state of the program memory code protect bits, CP0 and CP1, do not affect the execution of instructions out of program memory. The PIC16F870/871 devices can always read the values in program memory, regardless of the state of the code protect bits. However, the state of the code protect bits and the WRT bit will have different effects on writing to program memory. Table 4-1 shows the effect of the code protect bits and the WRT bit on program memory.

Once code protection has been enabled for either EEPROM data memory or FLASH program memory, only a full erase of the entire device will disable code protection.

#### 3.10 FLASH Program Memory Write Protection

The configuration word contains a bit that write protects the FLASH program memory, called WRT. This bit can only be accessed when programming the PIC16F870/871 devices via ICSP. Once write protection is enabled, only an erase of the entire device will disable it. When enabled, write protection prevents any writes to FLASH program memory. Write protection does not affect program memory reads.

| Con | figuration | Bits | Momentie           | Internal | Internal | ICSP Read | ICSP Write |

|-----|------------|------|--------------------|----------|----------|-----------|------------|

| CP1 | CP0        | WRT  | Memory Location    | Read     | Write    | ICSP Read | ICSP write |

| 0   | 0          | x    | All program memory | Yes      | No       | No        | No         |

| 0   | 1          | 0    | Unprotected areas  | Yes      | No       | Yes       | No         |

| 0   | 1          | 0    | Protected areas    | Yes      | No       | No        | No         |

| 0   | 1          | 1    | Unprotected areas  | Yes      | Yes      | Yes       | No         |

| 0   | 1          | 1    | Protected areas    | Yes      | No       | No        | No         |

| 1   | 0          | 0    | Unprotected areas  | Yes      | No       | Yes       | No         |

| 1   | 0          | 0    | Protected areas    | Yes      | No       | No        | No         |

| 1   | 0          | 1    | Unprotected areas  | Yes      | Yes      | Yes       | No         |

| 1   | 0          | 1    | Protected areas    | Yes      | No       | No        | No         |

| 1   | 1          | 0    | All program memory | Yes      | No       | Yes       | Yes        |

| 1   | 1          | 1    | All program memory | Yes      | Yes      | Yes       | Yes        |

#### TABLE 3-1: READ/WRITE STATE OF INTERNAL FLASH PROGRAM MEMORY

#### TABLE 3-2: REGISTERS ASSOCIATED WITH DATA EEPROM/PROGRAM FLASH

| Address                 | Name   | Bit 7  | Bit 6   | Bit 5      | Bit 4                           | Bit 3        | Bit 2     | Bit 1 | Bit 0 | Value on:<br>POR, BOR | Value on<br>all other<br>RESETS |

|-------------------------|--------|--------|---------|------------|---------------------------------|--------------|-----------|-------|-------|-----------------------|---------------------------------|

| 0Bh, 8Bh,<br>10Bh, 18Bh | INTCON | GIE    | PEIE    | TOIE       | INTE                            | RBIE         | TOIF      | INTF  | RBIF  | 0000 000x             | 0000 000u                       |

| 10Dh                    | EEADR  | EEPROM | Address | Register   | , Low Byte                      | 9            |           |       |       | xxxx xxxx             | uuuu uuuu                       |

| 10Fh                    | EEADRH |        |         |            | EEPRON                          | 1 Address,   | High Byte |       |       | xxxx xxxx             | uuuu uuuu                       |

| 10Ch                    | EEDATA | EEPROM | Data Re | gister, Lo | w Byte                          |              |           |       |       | xxxx xxxx             | uuuu uuuu                       |

| 10Eh                    | EEDATH |        | _       | EEPRON     | EEPROM Data Register, High Byte |              |           |       |       | xxxx xxxx             | uuuu uuuu                       |

| 18Ch                    | EECON1 | EEPGD  | —       | —          | — — WRERR WREN WR RD            |              |           |       |       |                       | x u000                          |

| 18Dh                    | EECON2 | EEPROM | Control | Register2  | (not a ph                       | ysical regis | ster)     |       |       | _                     | _                               |

Legend: x = unknown, u = unchanged, r = reserved, - = unimplemented, read as '0'. Shaded cells are not used during FLASH/EEPROM access.

Note 1: These bits are reserved; always maintain these bits clear.

| IABLE 4 0. |      |                       | -                                                                                                                                                 |

|------------|------|-----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|

| Name       | Bit# | Buffer                | Function                                                                                                                                          |

| RB0/INT    | bit0 | TTL/ST <sup>(1)</sup> | Input/output pin or external interrupt input. Internal software programmable weak pull-up.                                                        |

| RB1        | bit1 | TTL                   | Input/output pin. Internal software programmable weak pull-up.                                                                                    |

| RB2        | bit2 | TTL                   | Input/output pin. Internal software programmable weak pull-up.                                                                                    |

| RB3/PGM    | bit3 | TTL/ST <sup>(1)</sup> | Input/output pin or programming pin in LVP mode. Internal software programmable weak pull-up.                                                     |

| RB4        | bit4 | TTL                   | Input/output pin (with interrupt-on-change). Internal software programmable weak pull-up.                                                         |

| RB5        | bit5 | TTL                   | Input/output pin (with interrupt-on-change). Internal software programmable weak pull-up.                                                         |

| RB6/PGC    | bit6 | TTL/ST <sup>(2)</sup> | Input/output pin (with interrupt-on-change) or In-Circuit Debugger pin.<br>Internal software programmable weak pull-up. Serial programming clock. |

| RB7/PGD    | bit7 | TTL/ST <sup>(2)</sup> | Input/output pin (with interrupt-on-change) or In-Circuit Debugger pin.<br>Internal software programmable weak pull-up. Serial programming data.  |

#### TABLE 4-3:PORTB FUNCTIONS

Legend: TTL = TTL input, ST = Schmitt Trigger input

**Note 1:** This buffer is a Schmitt Trigger input when configured as the external interrupt or LVP mode.

2: This buffer is a Schmitt Trigger input when used in Serial Programming mode.

#### TABLE 4-4: SUMMARY OF REGISTERS ASSOCIATED WITH PORTB

| Address   | Name       | Bit 7   | Bit 6                         | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Value on:<br>POR, BOR | Value on<br>all other<br>RESETS |

|-----------|------------|---------|-------------------------------|-------|-------|-------|-------|-------|-------|-----------------------|---------------------------------|

| 06h, 106h | PORTB      | RB7     | RB6                           | RB5   | RB4   | RB3   | RB2   | RB1   | RB0   | XXXX XXXX             | uuuu uuuu                       |

| 86h, 186h | TRISB      | PORTB [ | PORTB Data Direction Register |       |       |       |       |       |       | 1111 1111             | 1111 1111                       |

| 81h, 181h | OPTION_REG | RBPU    | INTEDG                        | TOCS  | T0SE  | PSA   | PS2   | PS1   | PS0   | 1111 1111             | 1111 1111                       |

Legend: x = unknown, u = unchanged. Shaded cells are not used by PORTB.

NOTES:

#### **TIMER1 MODULE** 6.0

The Timer1 module is a 16-bit timer/counter consisting of two 8-bit registers (TMR1H and TMR1L), which are readable and writable. The TMR1 register pair (TMR1H:TMR1L) increments from 0000h to FFFFh and rolls over to 0000h. The TMR1 interrupt, if enabled, is generated on overflow, which is latched in interrupt flag bit, TMR1IF (PIR1<0>). This interrupt can be enabled/disabled by setting/clearing TMR1 interrupt enable bit, TMR1IE (PIE1<0>).

Timer1 can operate in one of two modes:

- As a timer

- · As a counter

The Operating mode is determined by the clock select bit, TMR1CS (T1CON<1>).

In Timer mode, Timer1 increments every instruction cycle. In Counter mode, it increments on every rising edge of the external clock input.

Timer1 can be enabled/disabled by setting/clearing control bit, TMR1ON (T1CON<0>).

Timer1 also has an internal "RESET input". This RESET can be generated by either of the two CCP modules (Section 8.0). Register 6-1 shows the Timer1 control register.

When the Timer1 oscillator is enabled (T1OSCEN is set), the RC1/T1OSI and RC0/T1OSO/T1CKI pins become inputs. That is, the TRISC<1:0> value is ignored, and these pins read as '0'.

Additional information on timer modules is available in the PIC<sup>®</sup> Mid-Range MCU Family Reference Manual (DS33023).

| ER 6-1: | 11CON: IIMER1 CONTROL REGISTER (ADDRESS: 10h)                    |                                                                                                                |                 |                |                  |             |                |        |  |  |

|---------|------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|-----------------|----------------|------------------|-------------|----------------|--------|--|--|

|         | U-0                                                              | U-0                                                                                                            | R/W-0           | R/W-0          | R/W-0            | R/W-0       | R/W-0          | R/W-0  |  |  |

|         | —                                                                | —                                                                                                              | T1CKPS1         | T1CKPS0        | T1OSCEN          | T1SYNC      | TMR1CS         | TMR10N |  |  |

|         | bit 7                                                            |                                                                                                                |                 |                |                  |             |                | bit 0  |  |  |

|         |                                                                  |                                                                                                                |                 |                |                  |             |                |        |  |  |

| bit 7-6 | Unimplem                                                         | ented: Rea                                                                                                     | ad as '0'       |                |                  |             |                |        |  |  |

| bit 5-4 | T1CKPS1:                                                         | T1CKPS0:                                                                                                       | Timer1 Inpu     | t Clock Pres   | cale Select bit  | S           |                |        |  |  |

|         | -                                                                | rescale valu                                                                                                   |                 |                |                  |             |                |        |  |  |

|         |                                                                  | rescale valu                                                                                                   |                 |                |                  |             |                |        |  |  |

|         |                                                                  | rescale valı<br>rescale valı                                                                                   |                 |                |                  |             |                |        |  |  |

| bit 3   |                                                                  |                                                                                                                | scillator Enal  | ole Control b  | it               |             |                |        |  |  |

|         |                                                                  | tor is enabl                                                                                                   |                 |                |                  |             |                |        |  |  |

|         | 0 = Oscilla                                                      | tor is shut-                                                                                                   | off (the oscill | ator inverter  | is turned off to | eliminate p | ower drain     | )      |  |  |

| bit 2   | T1SYNC: 7                                                        | Fimer1 Exte                                                                                                    | ernal Clock Ir  | nput Synchro   | onization Contr  | ol bit      |                |        |  |  |

|         | When TMF                                                         |                                                                                                                |                 |                |                  |             |                |        |  |  |

|         |                                                                  |                                                                                                                | e external cl   |                |                  |             |                |        |  |  |

|         | 0 = Synchr<br>When TMF                                           |                                                                                                                | nal clock inp   | out            |                  |             |                |        |  |  |

|         |                                                                  |                                                                                                                | ner1 uses th    | e internal clo | ock when TMR     | 1CS = 0.    |                |        |  |  |

| bit 1   |                                                                  | This bit is ignored. Timer1 uses the internal clock when TMR1CS = 0.<br>TMR1CS: Timer1 Clock Source Select bit |                 |                |                  |             |                |        |  |  |

|         | 1 = External clock from pin RC0/T1OSO/T1CKI (on the rising edge) |                                                                                                                |                 |                |                  |             |                |        |  |  |

|         |                                                                  | 0 = Internal clock (Fosc/4)                                                                                    |                 |                |                  |             |                |        |  |  |

| bit 0   | TMR1ON:                                                          | Timer1 On                                                                                                      | bit             |                |                  |             |                |        |  |  |

|         | 1 = Enable                                                       | s Timer1                                                                                                       |                 |                |                  |             |                |        |  |  |

|         | 0 = Stops 7                                                      | Timer1                                                                                                         |                 |                |                  |             |                |        |  |  |

|         |                                                                  |                                                                                                                |                 |                |                  |             |                |        |  |  |

|         | Legend:                                                          |                                                                                                                |                 |                |                  |             |                |        |  |  |

|         | R = Reada                                                        | ble bit                                                                                                        | W = V           | Vritable bit   | U = Unimpl       | emented b   | it, read as '( | )'     |  |  |

|         | - n = Value                                                      | at POR                                                                                                         | '1' = E         | Bit is set     | '0' = Bit is c   | leared      | x = Bit is ur  | nknown |  |  |

#### T1CON: TIMER1 CONTROL REGISTER (ADDRESS: 10b) **REGISTER 6-1:**

#### 6.7 Resetting of Timer1 Register Pair (TMR1H, TMR1L)

TMR1H and TMR1L registers are not reset to 00h on a POR, or any other RESET, except by the CCP1 special event trigger.

T1CON register is reset to 00h on a Power-on Reset, or a Brown-out Reset, which shuts off the timer and leaves a 1:1 prescale. In all other RESETS, the register is unaffected.

#### 6.8 Timer1 Prescaler

The prescaler counter is cleared on writes to the TMR1H or TMR1L registers.

#### TABLE 6-2: REGISTERS ASSOCIATED WITH TIMER1 AS A TIMER/COUNTER

| Address                | Name   | Bit 7                                                                      | Bit 6                                                                       | Bit 5   | Bit 4   | Bit 3   | Bit 2  | Bit 1  | Bit 0  | Value<br>POR, |      | all c | e on<br>other<br>SETS |

|------------------------|--------|----------------------------------------------------------------------------|-----------------------------------------------------------------------------|---------|---------|---------|--------|--------|--------|---------------|------|-------|-----------------------|

| 0Bh,8Bh,<br>10Bh, 18Bh | INTCON | GIE                                                                        | PEIE                                                                        | TOIE    | INTE    | RBIE    | TOIF   | INTF   | RBIF   | 0000          | 000x | 0000  | 000u                  |

| 0Ch                    | PIR1   | PSPIF <sup>(1)</sup>                                                       | ADIF                                                                        | RCIF    | TXIF    | _       | CCP1IF | TMR2IF | TMR1IF | 0000          | -000 | 0000  | -000                  |

| 8Ch                    | PIE1   | PSPIE <sup>(1)</sup>                                                       | ADIE                                                                        | RCIE    | TXIE    | _       | CCP1IE | TMR2IE | TMR1IE | 0000          | -000 | 0000  | -000                  |

| 0Eh                    | TMR1L  | Holding R                                                                  | Holding Register for the Least Significant Byte of the 16-bit TMR1 Register |         |         |         |        |        |        | xxxx          | xxxx | uuuu  | uuuu                  |

| 0Fh                    | TMR1H  | Holding Register for the Most Significant Byte of the 16-bit TMR1 Register |                                                                             |         |         |         |        | r      | xxxx   | xxxx          | uuuu | uuuu  |                       |

| 10h                    | T1CON  | _                                                                          | _                                                                           | T1CKPS1 | T1CKPS0 | T1OSCEN | T1SYNC | TMR1CS | TMR10N | 00            | 0000 | uu    | uuuu                  |

Legend: x = unknown, u = unchanged, - = unimplemented, read as '0'. Shaded cells are not used by the Timer1 module.

Note 1: Bits PSPIE and PSPIF are reserved on the PIC16F870; always maintain these bits clear.

When setting up an Asynchronous Reception, follow these steps:

- 1. Initialize the SPBRG register for the appropriate baud rate. If a high speed baud rate is desired, set bit BRGH (Section 9.1).

- 2. Enable the asynchronous serial port by clearing bit SYNC and setting bit SPEN.

- 3. If interrupts are desired, then set enable bit RCIE.

- 4. If 9-bit reception is desired, then set bit RX9.

- 5. Enable the reception by setting bit CREN.

- Flag bit RCIF will be set when reception is complete and an interrupt will be generated if enable bit RCIE is set.

- 7. Read the RCSTA register to get the ninth bit (if enabled) and determine if any error occurred during reception.

- 8. Read the 8-bit received data by reading the RCREG register.

- 9. If any error occurred, clear the error by clearing enable bit CREN.

- 10. If using interrupts, ensure that GIE and PEIE (bits 7 and 6) of the INTCON register are set.

| TABLE 9-               | ABLE 9-6: REGISTERS ASSOCIATED WITH ASTNCHRONOUS RECEPTION |                              |                        |       |       |       |        |        |           |                       |                                 |

|------------------------|------------------------------------------------------------|------------------------------|------------------------|-------|-------|-------|--------|--------|-----------|-----------------------|---------------------------------|

| Address                | Name                                                       | Bit 7                        | Bit 6                  | Bit 5 | Bit 4 | Bit 3 | Bit 2  | Bit 1  | Bit 0     | Value on:<br>POR, BOR | Value on<br>all other<br>RESETS |

| 0Bh, 8Bh,<br>10Bh,18Bh | INTCON                                                     | GIE                          | PEIE                   | TOIE  | INTE  | RBIE  | TOIF   | INTF   | R0IF      | 0000 000x             | 0000 000u                       |

| 0Ch                    | PIR1                                                       | PSPIF <sup>(1)</sup>         | ADIF                   | RCIF  | TXIF  | _     | CCP1IF | TMR2IF | TMR1IF    | -000 0000             | -000 0000                       |

| 18h                    | RCSTA                                                      | SPEN                         | RX9                    | SREN  | CREN  | —     | FERR   | OERR   | RX9D      | 0000 -00x             | 0000 -00x                       |

| 1Ah                    | RCREG                                                      | USART R                      | USART Receive Register |       |       |       |        |        |           | 0000 0000             | 0000 0000                       |

| 8Ch                    | PIE1                                                       | PSPIE <sup>(1)</sup>         | ADIE                   | RCIE  | TXIE  | —     | CCP1IE | TMR2IE | TMR1IE    | 0000 -000             | 0000 -000                       |

| 98h                    | TXSTA                                                      | CSRC                         | TX9                    | TXEN  | SYNC  | _     | BRGH   | TRMT   | TX9D      | 0000 -010             | 0000 -010                       |

| 99h                    | SPBRG                                                      | Baud Rate Generator Register |                        |       |       |       |        |        | 0000 0000 | 0000 0000             |                                 |

TABLE 9-6:

REGISTERS ASSOCIATED WITH ASYNCHRONOUS RECEPTION

Legend: x = unknown, - = unimplemented locations read as '0'. Shaded cells are not used for asynchronous reception.

Note 1: Bits PSPIE and PSPIF are reserved on the PIC16F870; always maintain these bits clear.

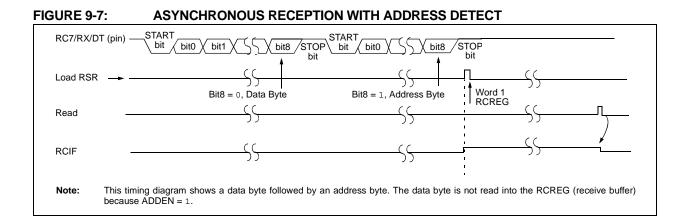

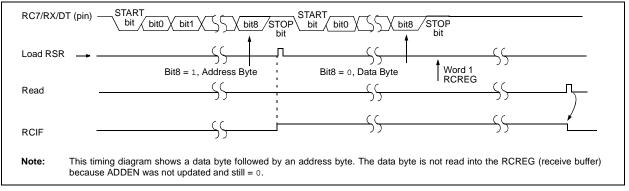

#### FIGURE 9-8: ASYNCHRONOUS RECEPTION WITH ADDRESS BYTE FIRST

#### TABLE 9-7: REGISTERS ASSOCIATED WITH ASYNCHRONOUS RECEPTION

| Address                | Name   | Bit 7                        | Bit 6    | Bit 5  | Bit 4 | Bit 3 | Bit 2  | Bit 1  | Bit 0     | Value on:<br>POR, BOR | Value on<br>all other<br>RESETS |

|------------------------|--------|------------------------------|----------|--------|-------|-------|--------|--------|-----------|-----------------------|---------------------------------|

| 0Bh, 8Bh,<br>10Bh,18Bh | INTCON | GIE                          | PEIE     | TOIE   | INTE  | RBIE  | TOIF   | INTF   | R0IF      | 0000 000x             | 0000 000u                       |

| 0Ch                    | PIR1   | PSPIF <sup>(1)</sup>         | ADIF     | RCIF   | TXIF  | —     | CCP1IF | TMR2IF | TMR1IF    | 0000 -000             | 0000 -000                       |

| 18h                    | RCSTA  | SPEN                         | RX9      | SREN   | CREN  | ADDEN | FERR   | OERR   | RX9D      | 0000 000x             | x000 000x                       |

| 1Ah                    | RCREG  | USART Re                     | ceive Re | gister |       |       |        |        |           | 0000 0000             | 0000 0000                       |

| 8Ch                    | PIE1   | PSPIE <sup>(1)</sup>         | ADIE     | RCIE   | TXIE  | —     | CCP1IE | TMR2IE | TMR1IE    | 0000 -000             | 0000 -000                       |

| 98h                    | TXSTA  | CSRC                         | TX9      | TXEN   | SYNC  | —     | BRGH   | TRMT   | TX9D      | 0000 -010             | 0000 -010                       |

| 99h                    | SPBRG  | Baud Rate Generator Register |          |        |       |       |        |        | 0000 0000 | 0000 0000             |                                 |

Legend: x = unknown, - = unimplemented locations read as '0'. Shaded cells are not used for asynchronous reception.

Note 1: Bits PSPIE and PSPIF are reserved on the PIC16F870; always maintain these bits clear.

NOTES:

#### 11.11 Context Saving During Interrupts

During an interrupt, only the return PC value is saved on the stack. Typically, users may wish to save key registers during an interrupt, (i.e., W register and STATUS register). This will have to be implemented in software.

For the PIC16F870/871 devices, the register W\_TEMP must be defined in both banks 0 and 1 and must be defined at the same offset from the bank base address (i.e., If W\_TEMP is defined at 0x20 in bank 0, it must also be defined at 0xA0 in bank 1). The registers, PCLATH\_TEMP and STATUS\_TEMP, are only defined in bank 0.

Since the upper 16 bytes of each bank are common in the PIC16F870/871 devices, temporary holding registers W\_TEMP, STATUS\_TEMP, and PCLATH\_TEMP should be placed in here. These 16 locations don't require banking and therefore, make it easier for context save and restore. The same code shown in Example 11-1 can be used.

#### EXAMPLE 11-1: SAVING STATUS, W, AND PCLATH REGISTERS IN RAM

| MOVWF  | W_TEMP         | ;Copy W to TEMP register                                |

|--------|----------------|---------------------------------------------------------|

| SWAPF  | STATUS,W       | ;Swap status to be saved into W                         |

| CLRF   | STATUS         | ;bank 0, regardless of current bank, Clears IRP,RP1,RP0 |

| MOVWF  | STATUS TEMP    | ;Save status to bank zero STATUS TEMP register          |

| MOVF   | PCLATH, W      | ;Only required if using pages 1, 2 and/or 3             |

| MOVWF  | PCLATH TEMP    | ;Save PCLATH into W                                     |

| CLRF   | PCLATH         | ;Page zero, regardless of current page                  |

| :      |                |                                                         |

| :(ISR) |                | ;(Insert user code here)                                |

| :      |                |                                                         |

| MOVF   | PCLATH_TEMP, W | ;Restore PCLATH                                         |

| MOVWF  | PCLATH         | ;Move W into PCLATH                                     |

| SWAPF  | STATUS TEMP,W  | ;Swap STATUS TEMP register into W                       |

|        |                | ;(sets bank to original state)                          |

| MOVWF  | STATUS         | ;Move W into STATUS register                            |

| SWAPF  | W TEMP,F       | ;Swap W TEMP                                            |

| SWAPF  | W_TEMP,W       | ;Swap W_TEMP into W                                     |

|        |                |                                                         |

| MOVF             | Move f                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Syntax:          | [ <i>label</i> ] MOVF f,d                                                                                                                                                                                                                                                         |  |  |  |  |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d  \in  [0,1] \end{array}$                                                                                                                                                                                                                 |  |  |  |  |  |  |

| Operation:       | (f) $\rightarrow$ (destination)                                                                                                                                                                                                                                                   |  |  |  |  |  |  |

| Status Affected: | Z                                                                                                                                                                                                                                                                                 |  |  |  |  |  |  |

| Description:     | The contents of register f are<br>moved to a destination dependant<br>upon the status of d. If $d = 0$ ,<br>destination is W register. If $d = 1$ ,<br>the destination is file register f itself.<br>d = 1 is useful to test a file register,<br>since status flag Z is affected. |  |  |  |  |  |  |

| NOP              | No Operation  |  |  |  |  |

|------------------|---------------|--|--|--|--|

| Syntax:          | [label] NOP   |  |  |  |  |

| Operands:        | None          |  |  |  |  |

| Operation:       | No operation  |  |  |  |  |

| Status Affected: | None          |  |  |  |  |

| Description:     | No operation. |  |  |  |  |

| MOVLW            | Move Literal to W                                                                                |  |  |  |  |  |  |

|------------------|--------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Syntax:          | [ <i>label</i> ] MOVLW k                                                                         |  |  |  |  |  |  |

| Operands:        | $0 \leq k \leq 255$                                                                              |  |  |  |  |  |  |

| Operation:       | $k \rightarrow (W)$                                                                              |  |  |  |  |  |  |

| Status Affected: | None                                                                                             |  |  |  |  |  |  |

| Description:     | The eight-bit literal 'k' is loaded<br>into W register. The don't cares<br>will assemble as 0's. |  |  |  |  |  |  |

| RETFIE           | Return from Interrupt                      |  |  |  |  |  |

|------------------|--------------------------------------------|--|--|--|--|--|

| Syntax:          | [label] RETFIE                             |  |  |  |  |  |

| Operands:        | None                                       |  |  |  |  |  |

| Operation:       | $TOS \rightarrow PC, \\ 1 \rightarrow GIE$ |  |  |  |  |  |

| Status Affected: | None                                       |  |  |  |  |  |

| MOVWF            | Move W to f                                |  |  |  |  |  |  |

|------------------|--------------------------------------------|--|--|--|--|--|--|

| Syntax:          | [ <i>label</i> ] MOVWF f                   |  |  |  |  |  |  |

| Operands:        | $0 \leq f \leq 127$                        |  |  |  |  |  |  |

| Operation:       | $(W) \rightarrow (f)$                      |  |  |  |  |  |  |

| Status Affected: | None                                       |  |  |  |  |  |  |

| Description:     | Move data from W register to register 'f'. |  |  |  |  |  |  |

| RETLW            | Return with Literal in W                                                                                                                                                            |  |  |  |  |  |  |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Syntax:          | [ <i>label</i> ] RETLW k                                                                                                                                                            |  |  |  |  |  |  |

| Operands:        | $0 \leq k \leq 255$                                                                                                                                                                 |  |  |  |  |  |  |

| Operation:       | $k \rightarrow (W);$<br>TOS $\rightarrow PC$                                                                                                                                        |  |  |  |  |  |  |

| Status Affected: | None                                                                                                                                                                                |  |  |  |  |  |  |

| Description:     | The W register is loaded with the<br>eight-bit literal 'k'. The program<br>counter is loaded from the top of<br>the stack (the return address).<br>This is a two-cycle instruction. |  |  |  |  |  |  |

#### 13.20 PICDEM 18R PIC18C601/801 Demonstration Board

The PICDEM 18R demonstration board serves to assist development of the PIC18C601/801 family of Microchip microcontrollers. It provides hardware implementation of both 8-bit Multiplexed/De-multiplexed and 16-bit Memory modes. The board includes 2 Mb external FLASH memory and 128 Kb SRAM memory, as well as serial EEPROM, allowing access to the wide range of memory types supported by the PIC18C601/801.

#### 13.21 PICDEM LIN PIC16C43X Demonstration Board

The powerful LIN hardware and software kit includes a series of boards and three PIC microcontrollers. The small footprint PIC16C432 and PIC16C433 are used as slaves in the LIN communication and feature onboard LIN transceivers. A PIC16F874 FLASH microcontroller serves as the master. All three microcontrollers are programmed with firmware to provide LIN bus communication.

### 13.22 PICkit<sup>™</sup> 1 FLASH Starter Kit

A complete "development system in a box", the PICkit FLASH Starter Kit includes a convenient multi-section board for programming, evaluation, and development of 8/14-pin FLASH PIC<sup>®</sup> microcontrollers. Powered via USB, the board operates under a simple Windows GUI. The PICkit 1 Starter Kit includes the user's guide (on CD ROM), PICkit 1 tutorial software and code for various applications. Also included are MPLAB<sup>®</sup> IDE (Integrated Development Environment) software, software and hardware "Tips 'n Tricks for 8-pin FLASH PIC<sup>®</sup> Microcontrollers" Handbook and a USB Interface Cable. Supports all current 8/14-pin FLASH PIC microcontrollers, as well as many future planned devices.

#### 13.23 PICDEM USB PIC16C7X5 Demonstration Board

The PICDEM USB Demonstration Board shows off the capabilities of the PIC16C745 and PIC16C765 USB microcontrollers. This board provides the basis for future USB products.

#### 13.24 Evaluation and Programming Tools

In addition to the PICDEM series of circuits, Microchip has a line of evaluation kits and demonstration software for these products.

- KEELOQ evaluation and programming tools for Microchip's HCS Secure Data Products

- CAN developers kit for automotive network applications

- Analog design boards and filter design software

- PowerSmart battery charging evaluation/ calibration kits

- IrDA<sup>®</sup> development kit

- microID development and rfLab<sup>™</sup> development software

- SEEVAL<sup>®</sup> designer kit for memory evaluation and endurance calculations

- PICDEM MSC demo boards for Switching mode power supply, high power IR driver, delta sigma ADC, and flow rate sensor

Check the Microchip web page and the latest Product Line Card for the complete list of demonstration and evaluation kits.

NOTES:

### 14.4 Timing Parameter Symbology

The timing parameter symbols have been created following one of the following formats:

| 1. TppS2pp            | S                                     | 3. Tcc:st | (I <sup>2</sup> C specifications only) |  |  |  |  |

|-----------------------|---------------------------------------|-----------|----------------------------------------|--|--|--|--|

| 2. TppS               |                                       | 4. Ts     | (I <sup>2</sup> C specifications only) |  |  |  |  |

| Т                     |                                       |           | · · · · · · · · · · · · · · · · · · ·  |  |  |  |  |

| F                     | Frequency                             | Т         | Time                                   |  |  |  |  |

| Lowercas              | e letters (pp) and their meanings:    |           |                                        |  |  |  |  |

| рр                    |                                       |           |                                        |  |  |  |  |

| СС                    | CCP1                                  | OSC       | OSC1                                   |  |  |  |  |

| ck                    | CLKO                                  | rd        | RD                                     |  |  |  |  |

| CS                    | CS                                    | rw        | RD or WR                               |  |  |  |  |

| di                    | SDI                                   | SC        | SCK                                    |  |  |  |  |

| do                    | SDO                                   | SS        | SS                                     |  |  |  |  |

| dt                    | Data in                               | tO        | TOCKI                                  |  |  |  |  |

| io                    | I/O port                              | t1        | T1CKI                                  |  |  |  |  |

| mc                    | MCLR                                  | wr        | WR                                     |  |  |  |  |

| Uppercas              | Uppercase letters and their meanings: |           |                                        |  |  |  |  |

| S                     |                                       |           |                                        |  |  |  |  |

| F                     | Fall                                  | Р         | Period                                 |  |  |  |  |

| н                     | High                                  | R         | Rise                                   |  |  |  |  |

| I                     | Invalid (Hi-impedance)                | V         | Valid                                  |  |  |  |  |

| L                     | Low                                   | Z         | Hi-impedance                           |  |  |  |  |

| I <sup>2</sup> C only |                                       |           |                                        |  |  |  |  |

| AA                    | output access                         | High      | High                                   |  |  |  |  |

| BUF                   | Bus free                              | Low       | Low                                    |  |  |  |  |

| TCC:ST (I             | <sup>2</sup> C specifications only)   |           |                                        |  |  |  |  |

| CC                    |                                       |           |                                        |  |  |  |  |

| HD                    | Hold                                  | SU        | Setup                                  |  |  |  |  |

| ST                    |                                       |           |                                        |  |  |  |  |

| DAT                   | DATA input hold                       | STO       | STOP condition                         |  |  |  |  |

| STA                   | START condition                       |           |                                        |  |  |  |  |

#### Package Marking Information (Cont'd)

# Example PIC16F871-I/P

#### Example

44-Lead TQFP

#### 44-Lead PLCC

Example

#### APPENDIX E: MIGRATION FROM HIGH-END TO ENHANCED DEVICES

A detailed discussion of the migration pathway and differences between the high-end MCU devices (i.e., PIC17CXXX) and the enhanced devices (i.e., PIC18FXXX) is provided in AN726, "PIC17CXXX to PIC18CXXX Migration." This Application Note is available as Literature Number DS00726.

| STATUS Register                 |    |

|---------------------------------|----|

| PD Bit                          |    |

| TO Bit                          |    |

| Synchronous Master Reception    |    |

| Associated Registers            | 75 |

| Synchronous Master Transmission |    |

| Associated Registers            | 73 |

| Synchronous Slave Reception     |    |

| Associated Registers            | 77 |

| Synchronous Slave Transmission  |    |

| Associated Registers            | 76 |

|                                 |    |

### Т

| T1CKPS0 Bit                                         | 49         |

|-----------------------------------------------------|------------|

| T1CKPS1 Bit                                         | 49         |

| T1CON Register                                      |            |

| T1OSCEN Bit                                         |            |

| T1SYNC Bit                                          | 49         |

| T2CKPS0 Bit                                         | 53         |

| T2CKPS1 Bit                                         |            |

| T2CON Register                                      |            |

| TAD                                                 |            |

| Time-out Sequence                                   |            |

| Timer0                                              |            |

| Associated Registers                                |            |

| Clock Source Edge Select (T0SE Bit)                 |            |

| Clock Source Select (TOCS Bit)                      |            |

| External Clock                                      |            |

| Interrupt                                           |            |

| Overflow Enable (T0IE Bit)                          |            |

| Overflow Flag (T0IF Bit)                            |            |

| Overflow Interrupt                                  |            |

| Prescaler                                           |            |

| TOCKI                                               |            |

| Timer1                                              | -          |

|                                                     |            |

| Associated Registers                                | 52         |

| Asynchronous Counter Mode<br>Reading and Writing to | <b>F</b> 4 |

|                                                     |            |

| Counter Operation                                   |            |

| Incrementing Edge (figure)                          |            |

| Operation in Asynchronous Counter Mode              |            |

| Operation in Synchronized Counter Mode              | 50         |

| Operation in Timer Mode                             |            |

| Oscillator                                          |            |

| Capacitor Selection                                 |            |

| Prescaler                                           | 52         |

| Resetting of Timer1 Register Pair                   |            |

| (TMR1H, TMR1L)                                      |            |

| Resetting Timer1 Using a CCP Trigger Output         |            |

| TMR1H                                               |            |

| TMR1L                                               |            |

| Timer2                                              |            |

| Associated Registers                                |            |

| Output                                              |            |

| Postscaler                                          |            |

| Prescaler                                           |            |

| Prescaler and Postscaler                            | 54         |

| Timing Diagrams                                     |            |

| A/D Conversion                                      |            |

| Asynchronous Master Transmission                    | 67         |

| Asynchronous Master Transmission                    |            |

| (Back to Back)                                      | 67         |

| Asynchronous Reception with                         |            |

| Address Byte First                                  | 71         |

| Asynchronous Reception with                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Address Detect 71                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Brown-out Reset 129                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Capture/Compare/PWM (CCP1) 131                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| CLKO and I/O 128                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| External Clock 126                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Parallel Slave Port (PSP) Read 43                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Parallel Slave Port (PSP) Write 43                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| RESET, Watchdog Timer, Oscillator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Start-up Timer and Power-up Timer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Slow Rise Time (MCLR Tied to VDD)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |