Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                   |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 20MHz                                                                    |

| Connectivity               | UART/USART                                                               |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                    |

| Number of I/O              | 22                                                                       |

| Program Memory Size        | 3.5KB (2K x 14)                                                          |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | 64 x 8                                                                   |

| RAM Size                   | 128 x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 4V ~ 5.5V                                                                |

| Data Converters            | A/D 5x10b                                                                |

| Oscillator Type            | External                                                                 |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                        |

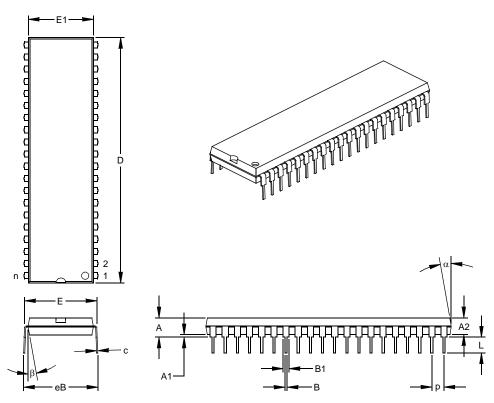

| Mounting Type              | Through Hole                                                             |

| Package / Case             | 28-DIP (0.300", 7.62mm)                                                  |

| Supplier Device Package    | 28-SPDIP                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f870-i-sp |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Key Features<br>PICmicro™ Mid-Range MCU Family Reference Manual<br>(DS33023) | PIC16F870            | PIC16F871            |

|------------------------------------------------------------------------------|----------------------|----------------------|

| Operating Frequency                                                          | DC - 20 MHz          | DC - 20 MHz          |

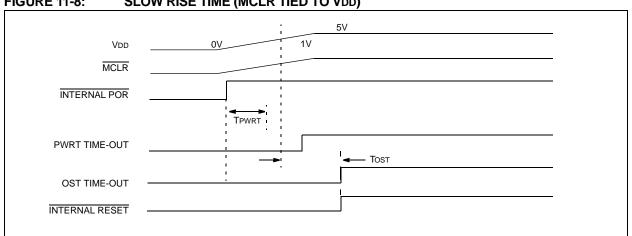

| RESETS (and Delays)                                                          | POR, BOR (PWRT, OST) | POR, BOR (PWRT, OST) |

| FLASH Program Memory (14-bit words)                                          | 2K                   | 2K                   |

| Data Memory (bytes)                                                          | 128                  | 128                  |

| EEPROM Data Memory                                                           | 64                   | 64                   |

| Interrupts                                                                   | 10                   | 11                   |

| I/O Ports                                                                    | Ports A,B,C          | Ports A,B,C,D,E      |

| Timers                                                                       | 3                    | 3                    |

| Capture/Compare/PWM modules                                                  | 1                    | 1                    |

| Serial Communications                                                        | USART                | USART                |

| Parallel Communications                                                      | —                    | PSP                  |

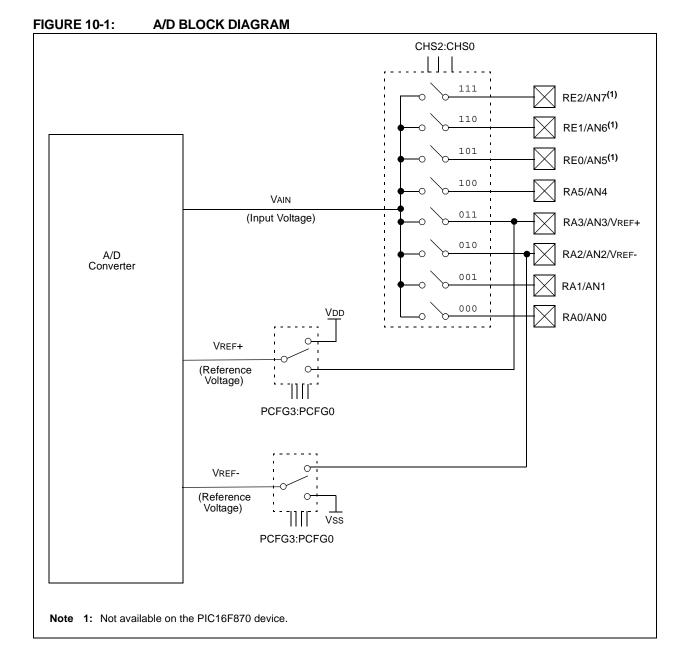

| 10-bit Analog-to-Digital Module                                              | 5 input channels     | 8 input channels     |

| Instruction Set                                                              | 35 Instructions      | 35 Instructions      |

#### 2.2.2 SPECIAL FUNCTION REGISTERS

The Special Function Registers are registers used by the CPU and peripheral modules for controlling the desired operation of the device. These registers are implemented as static RAM. A list of these registers is given in Table 2-1. The Special Function Registers can be classified into two sets: core (CPU) and peripheral. Those registers associated with the core functions are described in detail in this section. Those related to the operation of the peripheral features are described in detail in the peripheral feature section.

TABLE 2-1:SPECIAL FUNCTION REGISTER SUMMARY

| Address              | Name    | Bit 7                | Bit 6          | Bit 5         | Bit 4          | Bit 3          | Bit 2           | Bit 1        | Bit 0       | Value on:<br>POR, BOR | Value on<br>all other<br>RESETS <sup>(2)</sup> |

|----------------------|---------|----------------------|----------------|---------------|----------------|----------------|-----------------|--------------|-------------|-----------------------|------------------------------------------------|

| Bank 0               |         |                      |                |               |                |                |                 |              |             |                       |                                                |

| 00h <sup>(4)</sup>   | INDF    | Addressing           | this location  | uses conte    | ents of FSR to | o address dat  | ta memory (n    | ot a physica | l register) | 0000 0000             | 0000 0000                                      |

| 01h                  | TMR0    | Timer0 Mod           | dule's Regist  | er            |                |                |                 |              |             | xxxx xxxx             | uuuu uuuu                                      |

| 02h <sup>(4)</sup>   | PCL     | Program Co           | ounter's (PC   | ) Least Sigr  | ificant Byte   |                |                 |              |             | 0000 0000             | 0000 0000                                      |

| 03h <sup>(4)</sup>   | STATUS  | IRP                  | RP1            | RP0           | TO             | PD             | Z               | DC           | С           | 0001 1xxx             | 000q quuu                                      |

| 04h <sup>(4)</sup>   | FSR     | Indirect Dat         | ta Memory A    | ddress Poir   | nter           |                |                 | •            |             | xxxx xxxx             | uuuu uuuu                                      |

| 05h                  | PORTA   | —                    | —              | PORTA Da      | ta Latch whe   | n written: PO  | RTA pins wh     | ien read     |             | 0x 0000               | 0u 0000                                        |

| 06h                  | PORTB   | PORTB Da             | ta Latch whe   | en written: P | ORTB pins v    | vhen read      |                 |              |             | xxxx xxxx             | uuuu uuuu                                      |

| 07h                  | PORTC   | PORTC Da             | ta Latch whe   | en written: F | ORTC pins v    | when read      |                 |              |             | xxxx xxxx             | uuuu uuuu                                      |

| 08h <sup>(5)</sup>   | PORTD   | PORTD Da             | ta Latch whe   | en written: F | ORTD pins v    | when read      |                 |              |             | XXXX XXXX             | uuuu uuuu                                      |

| 09h <sup>(5)</sup>   | PORTE   | _                    | _              | _             | _              | _              | RE2             | RE1          | RE0         | xxx                   | uuu                                            |

| 0Ah <sup>(1,4)</sup> | PCLATH  | _                    | _              | _             | Write Buffer   | for the upper  | r 5 bits of the | Program Co   | ounter      | 0 0000                | 0 0000                                         |

| 0Bh <sup>(4)</sup>   | INTCON  | GIE                  | PEIE           | TOIE          | INTE           | RBIE           | T0IF            | INTF         | RBIF        | 0000 000x             | 0000 000u                                      |

| 0Ch                  | PIR1    | PSPIF <sup>(3)</sup> | ADIF           | RCIF          | TXIF           | _              | CCP1IF          | TMR2IF       | TMR1IF      | 0000 -000             | 0000 -000                                      |

| 0Dh                  | PIR2    | _                    | _              | _             | EEIF           | _              | _               | _            | _           |                       | 0                                              |

| 0Eh                  | TMR1L   | Holding Re           | gister for the | Least Sign    | ificant Byte o | f the 16-bit T | MR1 Registe     | er           |             | xxxx xxxx             | uuuu uuuu                                      |

| 0Fh                  | TMR1H   | Holding Re           | gister for the | Most Signi    | ficant Byte of | the 16-bit TM  | VR1 Register    | r            |             | XXXX XXXX             | uuuu uuuu                                      |

| 10h                  | T1CON   | —                    | —              | T1CKPS1       | T1CKPS0        | T1OSCEN        | T1SYNC          | TMR1CS       | TMR1ON      | 00 0000               | uu uuuu                                        |

| 11h                  | TMR2    | Timer2 Mod           | dule's Regist  | er            |                |                |                 |              |             | 0000 0000             | 0000 0000                                      |

| 12h                  | T2CON   | —                    | TOUTPS3        | TOUTPS2       | TOUTPS1        | TOUTPS0        | TMR2ON          | T2CKPS1      | T2CKPS0     | -000 0000             | -000 0000                                      |

| 13h                  | _       | Unimpleme            | nted           |               |                |                |                 |              |             | _                     | _                                              |

| 14h                  | _       | Unimpleme            | nted           |               |                |                |                 |              |             | _                     | _                                              |

| 15h                  | CCPR1L  | Capture/Co           | mpare/PWN      | 1 Register1   | (LSB)          |                |                 |              |             | xxxx xxxx             | uuuu uuuu                                      |

| 16h                  | CCPR1H  | Capture/Co           | mpare/PWN      | 1 Register1   | (MSB)          |                |                 |              |             | XXXX XXXX             | uuuu uuuu                                      |

| 17h                  | CCP1CON | _                    | _              | CCP1X         | CCP1Y          | CCP1M3         | CCP1M2          | CCP1M1       | CCP1M0      | 00 0000               | 00 0000                                        |

| 18h                  | RCSTA   | SPEN                 | RX9            | SREN          | CREN           | ADDEN          | FERR            | OERR         | RX9D        | 0000 000x             | 0000 000x                                      |

| 19h                  | TXREG   | USART Tra            | Insmit Data I  | Register      |                |                |                 |              |             | 0000 0000             | 0000 0000                                      |

| 1Ah                  | RCREG   | USART Re             | ceive Data F   | Register      |                |                |                 |              |             | 0000 0000             | 0000 0000                                      |

| 1Bh                  | _       | Unimpleme            | nted           |               |                |                |                 |              |             | _                     | _                                              |

| 1Ch                  | —       | Unimpleme            | nted           |               |                |                |                 |              |             | _                     | _                                              |

| 1Dh                  | _       | Unimpleme            | nted           |               |                |                |                 |              |             | _                     | _                                              |

| 1Eh                  | ADRESH  | -                    | Register Hig   | h Byte        |                |                |                 |              |             | xxxx xxxx             | uuuu uuuu                                      |

| 1Fh                  | ADCON0  | ADCS1                | ADCS0          | CHS2          | CHS1           | CHS0           | GO/DONE         |              | ADON        | 0000 00-0             | 0000 00-0                                      |

Legend: x = unknown, u = unchanged, q = value depends on condition, - = unimplemented, read as '0', r = reserved. Shaded locations are unimplemented, read as '0'.

**Note 1:** The upper byte of the program counter is not directly accessible. PCLATH is a holding register for the PC<12:8> whose contents are transferred to the upper byte of the program counter.

2: Other (non Power-up) Resets include external RESET through MCLR and Watchdog Timer Reset.

3: Bits PSPIE and PSPIF are reserved on the 28-pin devices; always maintain these bits clear.

4: These registers can be addressed from any bank.

5: PORTD, PORTE, TRISD and TRISE are not physically implemented on the 28-pin devices, read as '0'.

| Address              | Name       | Bit 7                | Bit 6         | Bit 5       | Bit 4           | Bit 3         | Bit 2           | Bit 1         | Bit 0       | Value on:<br>POR, BOR | Value on<br>all other<br>RESETS <sup>(2)</sup> |

|----------------------|------------|----------------------|---------------|-------------|-----------------|---------------|-----------------|---------------|-------------|-----------------------|------------------------------------------------|

| Bank 1               |            |                      |               |             |                 |               |                 |               |             |                       |                                                |

| 80h <sup>(4)</sup>   | INDF       | Addressing           | this location | uses conte  | ents of FSR to  | o address dat | ta memory (n    | ot a physica  | l register) | 0000 0000             | 0000 0000                                      |

| 81h                  | OPTION_REG | RBPU                 | INTEDG        | TOCS        | TOSE            | PSA           | PS2             | PS1           | PS0         | 1111 1111             | 1111 1111                                      |

| 82h <sup>(4)</sup>   | PCL        | Program Co           | ounter's (PC  | ) Least Sig | nificant Byte   |               |                 |               |             | 0000 0000             | 0000 0000                                      |

| 83h <sup>(4)</sup>   | STATUS     | IRP                  | RP1           | RP0         | TO              | PD            | Z               | DC            | С           | 0001 1xxx             | 000q quuu                                      |

| 84h <sup>(4)</sup>   | FSR        | Indirect Dat         | a Memory A    | ddress Poi  | nter            |               |                 |               |             | xxxx xxxx             | uuuu uuuu                                      |

| 85h                  | TRISA      | _                    | _             | PORTA Da    | ata Direction F | Register      |                 |               |             | 11 1111               | 11 1111                                        |

| 86h                  | TRISB      | PORTB Da             | ta Direction  | Register    |                 |               |                 |               |             | 1111 1111             | 1111 1111                                      |

| 87h                  | TRISC      | PORTC Da             | ta Direction  | Register    |                 |               |                 |               |             | 1111 1111             | 1111 1111                                      |

| 88h <sup>(5)</sup>   | TRISD      | PORTD Da             | ta Direction  | Register    |                 |               |                 |               |             | 1111 1111             | 1111 1111                                      |

| 89h <sup>(5)</sup>   | TRISE      | IBF                  | OBF           | IBOV        | PSPMODE         | _             | PORTE Dat       | a Direction E | Bits        | 0000 -111             | 0000 -111                                      |

| 8Ah <sup>(1,4)</sup> | PCLATH     | _                    | _             | _           | Write Buffer    | for the uppe  | r 5 bits of the | Program Co    | ounter      | 0 0000                | 0 0000                                         |

| 8Bh <sup>(4)</sup>   | INTCON     | GIE                  | PEIE          | TOIE        | INTE            | RBIE          | T0IF            | INTF          | RBIF        | 0000 000x             | 0000 000u                                      |

| 8Ch                  | PIE1       | PSPIE <sup>(3)</sup> | ADIE          | RCIE        | TXIE            | _             | CCP1IE          | TMR2IE        | TMR1IE      | 0000 -000             | 0000 -000                                      |

| 8Dh                  | PIE2       | _                    | _             | _           | EEIE            | _             | _               | _             | _           | 0                     | 0                                              |

| 8Eh                  | PCON       | _                    | _             | _           | _               | _             | _               | POR           | BOR         | dd                    | uu                                             |

| 8Fh                  |            | Unimpleme            | nted          |             |                 |               |                 |               |             | _                     | —                                              |

| 90h                  |            | Unimpleme            | nted          |             |                 |               |                 |               |             | _                     | —                                              |

| 91h                  |            | Unimpleme            | nted          |             |                 |               |                 |               |             | _                     | —                                              |

| 92h                  | PR2        | Timer2 Per           | iod Register  |             |                 |               |                 |               |             | 1111 1111             | 1111 1111                                      |

| 93h                  | _          | Unimpleme            | nted          |             |                 |               |                 |               |             | _                     | —                                              |

| 94h                  |            | Unimpleme            | nted          |             |                 |               |                 |               |             | _                     | —                                              |

| 95h                  |            | Unimpleme            | nted          |             |                 |               |                 |               |             | _                     | —                                              |

| 96h                  | —          | Unimpleme            | nted          |             |                 |               |                 |               |             | _                     | _                                              |

| 97h                  | —          | Unimpleme            | nted          |             |                 |               |                 |               |             | _                     | _                                              |

| 98h                  | TXSTA      | CSRC                 | TX9           | TXEN        | SYNC            | _             | BRGH            | TRMT          | TX9D        | 0000 -010             | 0000 -010                                      |

| 99h                  | SPBRG      | Baud Rate            | Generator R   | egister     |                 |               |                 |               |             | 0000 0000             | 0000 0000                                      |

| 9Ah                  | —          | Unimpleme            | nted          |             |                 |               |                 |               |             | _                     | _                                              |

| 9Bh                  | _          | Unimpleme            | nted          |             |                 |               |                 |               |             | _                     | _                                              |

| 9Ch                  | _          | Unimpleme            | nted          |             |                 |               |                 |               |             | _                     | _                                              |

| 9Dh                  | _          | Unimpleme            |               |             |                 |               |                 |               |             | _                     | _                                              |

| 9Eh                  | ADRESL     | A/D Result           | Register Lov  | w Byte      |                 |               |                 |               |             | xxxx xxxx             | uuuu uuuu                                      |

| 9Fh                  | ADCON1     | ADFM                 | _             | _           |                 | PCFG3         | PCFG2           | PCFG1         | PCFG0       | 0 0000                | 0 0000                                         |

#### TABLE 2-1: SPECIAL FUNCTION REGISTER SUMMARY (CONTINUED)

Legend: x = unknown, u = unchanged, q = value depends on condition, - = unimplemented, read as '0', r = reserved. Shaded locations are unimplemented, read as '0'.

**Note 1:** The upper byte of the program counter is not directly accessible. PCLATH is a holding register for the PC<12:8> whose contents are transferred to the upper byte of the program counter.

2: Other (non Power-up) Resets include external RESET through MCLR and Watchdog Timer Reset.

3: Bits PSPIE and PSPIF are reserved on the 28-pin devices; always maintain these bits clear.

4: These registers can be addressed from any bank.

5: PORTD, PORTE, TRISD and TRISE are not physically implemented on the 28-pin devices, read as '0'.

#### 2.2.2.4 **PIE1** Register

The PIE1 register contains the individual enable bits for the peripheral interrupts.

| Note: | Bit PEIE (INTCON<6>) must be set to |

|-------|-------------------------------------|

|       | enable any peripheral interrupt.    |

| <b>REGISTER 2-4:</b> | PIE1 REGI                  | STER (AD     | DRESS:        | 8Ch)          |                |              |           |        |

|----------------------|----------------------------|--------------|---------------|---------------|----------------|--------------|-----------|--------|

|                      | R/W-0                      | R/W-0        | R/W-0         | R/W-0         | U-0            | R/W-0        | R/W-0     | R/W-0  |

|                      | PSPIE <sup>(1)</sup>       | ADIE         | RCIE          | TXIE          | —              | CCP1IE       | TMR2IE    | TMR1IE |

|                      | bit 7                      |              |               |               |                |              |           | bit 0  |

|                      |                            |              |               |               |                |              |           |        |

| bit 7                | PSPIE <sup>(1)</sup> : P   | arallel Slav | e Port Read   | d/Write Inter | rupt Enable bi | t            |           |        |

|                      | 1 = Enables<br>0 = Disable |              |               |               |                |              |           |        |

| bit 6                | ADIE: A/D                  | Converter li | nterrupt Ena  | able bit      |                |              |           |        |

|                      | 1 = Enable:<br>0 = Disable |              |               | •             |                |              |           |        |

| bit 5                | RCIE: USA                  | RT Receive   | Interrupt E   | nable bit     |                |              |           |        |

|                      | 1 = Enables                |              |               |               |                |              |           |        |

|                      | 0 = Disable                | s the USAF   | RT receive i  | nterrupt      |                |              |           |        |

| bit 4                | TXIE: USA                  | RT Transmi   | t Interrupt E | nable bit     |                |              |           |        |

|                      | 1 = Enables<br>0 = Disable |              |               | •             |                |              |           |        |

| bit 3                | Unimplem                   | ented: Rea   | d as '0'      |               |                |              |           |        |

| bit 2                | CCP1IE: C                  | CP1 Interru  | pt Enable b   | it            |                |              |           |        |

|                      | 1 = Enables                |              | •             |               |                |              |           |        |

|                      | 0 = Disable                | s the CCP1   | interrupt     |               |                |              |           |        |

| bit 1                | TMR2IE: TI                 | MR2 to PR2   | 2 Match Inte  | errupt Enabl  | e bit          |              |           |        |

|                      |                            |              |               | tch interrup  |                |              |           |        |

|                      |                            |              |               | atch interrup | ot             |              |           |        |

| bit 0                | TMR1IE: TI                 |              | -             |               |                |              |           |        |

|                      | 1 = Enables                |              |               | •             |                |              |           |        |

|                      | 0 = Disable                | s the TIVIR1 | overnow II    | iterrupt      |                |              |           |        |

|                      | Note 1.                    |              |               |               | 070. alwaya m  | aintain thia | hit cloar |        |

Note 1: PSPIE is reserved on the PIC16F870; always maintain this bit clear.

| Legend:            |                  |                      |                    |

|--------------------|------------------|----------------------|--------------------|

| R = Readable bit   | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

| - n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

#### 2.2.2.5 PIR1 Register

The PIR1 register contains the individual flag bits for the peripheral interrupts.

| Note: | Interrupt flag bits get set when an interrupt |  |  |  |  |  |  |  |  |  |

|-------|-----------------------------------------------|--|--|--|--|--|--|--|--|--|

|       | condition occurs, regardless of the state of  |  |  |  |  |  |  |  |  |  |

|       | its corresponding enable bit or the global    |  |  |  |  |  |  |  |  |  |

|       | enable bit, GIE (INTCON<7>). User soft-       |  |  |  |  |  |  |  |  |  |

|       | ware should ensure the appropriate inter-     |  |  |  |  |  |  |  |  |  |

|       | rupt bits are clear prior to enabling an      |  |  |  |  |  |  |  |  |  |

|       | interrupt.                                    |  |  |  |  |  |  |  |  |  |

| 0.    |                                                                                                                                              |             | DDILLOO.                       | uon)                         |                       |               |            |        |  |  |  |  |  |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------|-------------|--------------------------------|------------------------------|-----------------------|---------------|------------|--------|--|--|--|--|--|

|       | R/W-0                                                                                                                                        | R/W-0       | R-0                            | R-0                          | U-0                   | R/W-0         | R/W-0      | R/W-0  |  |  |  |  |  |

|       | PSPIF <sup>(1)</sup>                                                                                                                         | ADIF        | RCIF                           | TXIF                         | —                     | CCP1IF        | TMR2IF     | TMR1IF |  |  |  |  |  |

|       | bit 7                                                                                                                                        |             |                                |                              |                       |               |            | bit 0  |  |  |  |  |  |

|       | (1)                                                                                                                                          |             |                                |                              |                       |               |            |        |  |  |  |  |  |

| bit 7 |                                                                                                                                              |             |                                |                              | rrupt Flag bit        |               |            |        |  |  |  |  |  |

|       | <ul> <li>1 = A read or a write operation has taken place (must be cleared in software)</li> <li>0 = No read or write has occurred</li> </ul> |             |                                |                              |                       |               |            |        |  |  |  |  |  |

| bit 6 |                                                                                                                                              |             |                                |                              |                       |               |            |        |  |  |  |  |  |

| Sit 0 | ADIF: A/D Converter Interrupt Flag bit<br>1 = An A/D conversion completed<br>0 = The A/D conversion is not complete                          |             |                                |                              |                       |               |            |        |  |  |  |  |  |

|       |                                                                                                                                              |             |                                |                              |                       |               |            |        |  |  |  |  |  |

| bit 5 | RCIF: USA                                                                                                                                    | RT Receive  | e Interrupt F                  | lag bit                      |                       |               |            |        |  |  |  |  |  |

|       |                                                                                                                                              |             | /e buffer is f                 |                              |                       |               |            |        |  |  |  |  |  |

|       |                                                                                                                                              |             | /e buffer is                   |                              |                       |               |            |        |  |  |  |  |  |

| bit 4 |                                                                                                                                              |             | it Interrupt F                 | -                            |                       |               |            |        |  |  |  |  |  |

|       |                                                                                                                                              |             | mit buffer is<br>mit buffer is |                              |                       |               |            |        |  |  |  |  |  |

| bit 3 | Unimplem                                                                                                                                     | ented: Rea  | d as '0'                       |                              |                       |               |            |        |  |  |  |  |  |

| bit 2 | CCP1IF: C                                                                                                                                    | CP1 Interru | pt Flag bit                    |                              |                       |               |            |        |  |  |  |  |  |

|       | Capture me                                                                                                                                   |             |                                |                              |                       |               |            |        |  |  |  |  |  |

|       |                                                                                                                                              |             | apture occu<br>capture occ     |                              | be cleared in s       | oftware)      |            |        |  |  |  |  |  |

|       | Compare n                                                                                                                                    |             |                                |                              |                       |               |            |        |  |  |  |  |  |

|       |                                                                                                                                              |             |                                | tch occurred<br>atch occurre | d (must be clea<br>ed | ared in softw | vare)      |        |  |  |  |  |  |

|       | PWM mode                                                                                                                                     |             |                                |                              |                       |               |            |        |  |  |  |  |  |

| 1.1.4 | Unused in                                                                                                                                    |             |                                |                              | .,                    |               |            |        |  |  |  |  |  |

| bit 1 |                                                                                                                                              |             |                                | errupt Flag b                |                       | ara)          |            |        |  |  |  |  |  |

|       | <ul> <li>1 = TMR2 to PR2 match occurred (must be cleared in software)</li> <li>0 = No TMR2 to PR2 match occurred</li> </ul>                  |             |                                |                              |                       |               |            |        |  |  |  |  |  |

| bit 0 | TMR1IF: T                                                                                                                                    | MR1 Overfl  | ow Interrup                    | t Flag bit                   |                       |               |            |        |  |  |  |  |  |

|       |                                                                                                                                              |             | •                              | •                            | ed in software)       |               |            |        |  |  |  |  |  |

|       |                                                                                                                                              |             | not overflow                   |                              |                       |               |            |        |  |  |  |  |  |

|       | Note 1:                                                                                                                                      | PSPIF is r  | eserved on                     | the PIC16F                   | 870; always m         | aintain this  | bit clear. |        |  |  |  |  |  |

|       |                                                                                                                                              |             |                                |                              |                       |               |            |        |  |  |  |  |  |

| Legend:            |                  |                      |                    |

|--------------------|------------------|----------------------|--------------------|

| R = Readable bit   | W = Writable bit | U = Unimplemented    | l bit, read as '0' |

| - n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

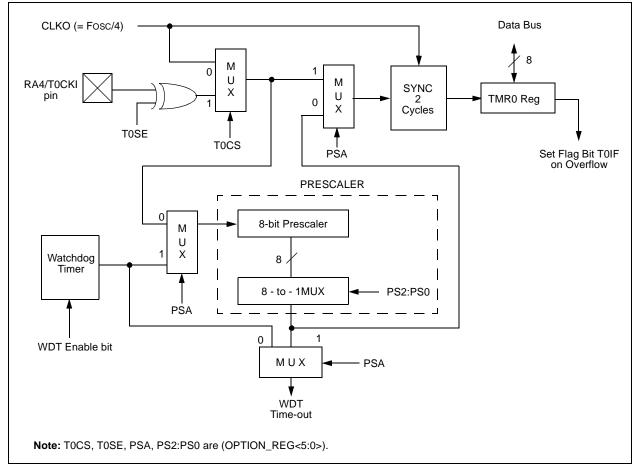

### 5.0 TIMER0 MODULE

The Timer0 module timer/counter has the following features:

- 8-bit timer/counter

- Readable and writable

- 8-bit software programmable prescaler

- · Internal or external clock select

- Interrupt on overflow from FFh to 00h

- Edge select for external clock

Figure 5-1 is a block diagram of the Timer0 module and the prescaler shared with the WDT.

Additional information on the Timer0 module is available in the PIC® Mid-Range MCU Family Reference Manual (DS33023).

Timer mode is selected by clearing bit TOCS (OPTION\_REG<5>). In Timer mode, the Timer0 module will increment every instruction cycle (without prescaler). If the TMR0 register is written, the increment is inhibited for the following two instruction cycles. The user can work around this by writing an adjusted value to the TMR0 register. Counter mode is selected by setting bit T0CS (OPTION\_REG<5>). In Counter mode, Timer0 will increment either on every rising, or falling edge of pin RA4/T0CKI. The incrementing edge is determined by the Timer0 Source Edge Select bit, T0SE (OPTION\_REG<4>). Clearing bit T0SE selects the rising edge. Restrictions on the external clock input are discussed in detail in Section 5.2.

The prescaler is mutually exclusively shared between the Timer0 module and the Watchdog Timer. The prescaler is not readable or writable. Section 5.3 details the operation of the prescaler.

#### 5.1 Timer0 Interrupt

The TMR0 interrupt is generated when the TMR0 register overflows from FFh to 00h. This overflow sets bit T0IF (INTCON<2>). The interrupt can be masked by clearing bit T0IE (INTCON<5>). Bit T0IF must be cleared in software by the Timer0 module Interrupt Service Routine before re-enabling this interrupt. The TMR0 interrupt cannot awaken the processor from SLEEP, since the timer is shut-off during SLEEP.

FIGURE 5-1: BLOCK DIAGRAM OF THE TIMER0/WDT PRESCALER

NOTES:

| Address                | Name    | Bit 7                | Bit 6         | Bit 5       | Bit 4      | Bit 3   | Bit 2  | Bit 1   | Bit 0   | Value o<br>POR, B | -   | Valu<br>all o<br>RES | ther |

|------------------------|---------|----------------------|---------------|-------------|------------|---------|--------|---------|---------|-------------------|-----|----------------------|------|

| 0Bh,8Bh,<br>10Bh, 18Bh | INTCON  | GIE                  | PEIE          | TOIE        | INTE       | RBIE    | T0IF   | INTF    | RBIF    | 0000 0            | 00x | 0000                 | 000u |

| 0Ch                    | PIR1    | PSPIF <sup>(1)</sup> | ADIF          | RCIF        | TXIF       | —       | CCP1IF | TMR2IF  | TMR1IF  | 0000 -            | 000 | 0000                 | -000 |

| 8Ch                    | PIE1    | PSPIE <sup>(1)</sup> | ADIE          | RCIE        | TXIE       | _       | CCP1IE | TMR2IE  | TMR1IE  | 0000 -            | 000 | 0000                 | -000 |

| 87h                    | TRISC   | PORTC D              | Data Directio | n Register  |            |         |        |         |         | 1111 1            | 111 | 1111                 | 1111 |

| 11h                    | TMR2    | Timer2 M             | odule's Reg   | ister       |            |         |        |         |         | 0000 0            | 000 | 0000                 | 0000 |

| 92h                    | PR2     | Timer2 M             | odule's Peri  | od Register |            |         |        |         |         | 1111 1            | 111 | 1111                 | 1111 |

| 12h                    | T2CON   | _                    | TOUTPS3       | TOUTPS2     | TOUTPS1    | TOUTPS0 | TMR2ON | T2CKPS1 | T2CKPS0 | -000 0            | 000 | -000                 | 0000 |

| 15h                    | CCPR1L  | Capture/C            | Compare/PV    | /M Register | r1 (LSB)   |         |        |         |         | XXXX X            | xxx | uuuu                 | uuuu |

| 16h                    | CCPR1H  | Capture/C            | Compare/PV    | /M Register | r1 (MSB)   |         |        |         |         | xxxx x            | xxx | uuuu                 | uuuu |

| 17h                    | CCP1CON | _                    | —             | CCP1X       | CCP1Y      | CCP1M3  | CCP1M2 | CCP1M1  | CCP1M0  | 00 0              | 000 | 00                   | 0000 |

| Logond                 |         | (n                   | . I           |             | monted rea |         |        |         |         | <b></b>           |     | •                    |      |

#### TABLE 8-4: REGISTERS ASSOCIATED WITH PWM AND TIMER2

Legend: x = unknown, u = unchanged, - = unimplemented, read as '0'. Shaded cells are not used by PWM and Timer2.

Note 1: Bits PSPIE and PSPIF are reserved on the PIC16F870; always maintain these bits clear.

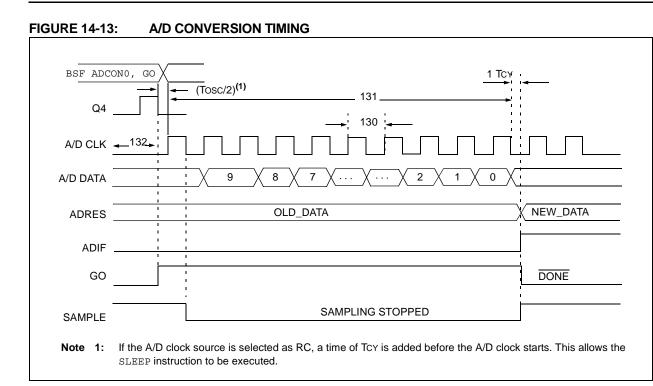

These steps should be followed for doing an A/D Conversion:

- 1. Configure the A/D module:

- Configure analog pins/voltage reference and digital I/O (ADCON1)

- Select A/D input channel (ADCON0)

- Select A/D conversion clock (ADCON0)

- Turn on A/D module (ADCON0)

- 2. Configure A/D interrupt (if desired):

- Clear ADIF bit

- Set ADIE bit

- Set PEIE bit

- Set GIE bit

- 3. Wait the required acquisition time.

- 4. Start conversion:

Set GO/DONE bit (ADCON0)

- 5. Wait for A/D conversion to complete, by either:

- Polling for the GO/DONE bit to be cleared (with interrupts enabled); OR

- Waiting for the A/D interrupt

- 6. Read A/D Result register pair (ADRESH:ADRESL), clear bit ADIF if required.

- 7. For the next conversion, go to step 1 or step 2, as required. The A/D conversion time per bit is defined as TAD. A minimum wait of 2 TAD is required before the next acquisition starts.

#### SLOW RISE TIME (MCLR TIED TO VDD) **FIGURE 11-8:**

#### 11.10 Interrupts

The PIC16F870/871 family has up to 14 sources of interrupt. The Interrupt Control register (INTCON) records individual interrupt requests in flag bits. It also has individual and global interrupt enable bits.

| Note: | Individual | interru | pt fla | ag    | bits  | are   | set,  |

|-------|------------|---------|--------|-------|-------|-------|-------|

|       | regardless | of      | the    | stat  | tus   | of    | their |

|       | correspond | ling ma | sk bit | t, or | the G | SIE b | it.   |

A global interrupt enable bit, GIE (INTCON<7>), enables (if set) all unmasked interrupts, or disables (if cleared) all interrupts. When bit GIE is enabled, and an interrupt's flag bit and mask bit are set, the interrupt will vector immediately. Individual interrupts can be disabled through their corresponding enable bits in various registers. Individual interrupt bits are set, regardless of the status of the GIE bit. The GIE bit is cleared on RESET.

The "return from interrupt" instruction, RETFIE, exits the interrupt routine as well as sets the GIE bit, which re-enables interrupts.

The RB0/INT pin interrupt, the RB port change interrupt, and the TMR0 overflow interrupt flags are contained in the INTCON register.

The peripheral interrupt flags are contained in the special function registers, PIR1 and PIR2. The corresponding interrupt enable bits are contained in special function registers, PIE1 and PIE2, and the peripheral interrupt enable bit is contained in special function register, INTCON.

When an interrupt is responded to, the GIE bit is cleared to disable any further interrupt, the return address is pushed onto the stack and the PC is loaded with 0004h. Once in the Interrupt Service Routine, the source(s) of the interrupt can be determined by polling the interrupt flag bits. The interrupt flag bit(s) must be cleared in software before re-enabling interrupts to avoid recursive interrupts.

For external interrupt events, such as the INT pin or PORTB change interrupt, the interrupt latency will be three or four instruction cycles. The exact latency depends when the interrupt event occurs. The latency is the same for one or two-cycle instructions. Individual interrupt flag bits are set, regardless of the status of their corresponding mask bit, PEIE bit, or GIE bit.

| ; Q1 Q2 Q3 Q4; Q1 Q2 Q3 Q<br>OSC1 ////////////////////////////////////                                                                                                                             | 4, Q1                 |                   | ; Q1  Q2  Q3  Q4;<br>;/~_/~_/^_/<br>;// | 011 021 031 04;<br>    | Q1 Q2 Q3 Q4<br>\/\/\/\ |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|-------------------|-----------------------------------------|------------------------|------------------------|

| INTF Flag<br>(INTCON<1>)                                                                                                                                                                           |                       |                   | Interrupt Latency                       | 2)                     |                        |

| GIE bit<br>(INTCON<7>)                                                                                                                                                                             | Processor in<br>SLEEP | <br>              |                                         | i                      | 1<br>1<br>1            |

| INSTRUCTION FLOW                                                                                                                                                                                   |                       | l<br>l            | 1 I<br>1 I                              | 1                      | I<br>I                 |

| PC X PC X PC+1                                                                                                                                                                                     | X PC+2                | PC+2              | X PC + 2 X                              | <u>    0004h     X</u> | 0005h                  |

| $ \begin{array}{l} \text{Instruction} \\ \text{Fetched} \end{array} \Big\{ \begin{array}{l} \text{Inst}(\text{PC}) = \text{SLEEP} & \text{Inst}(\text{PC}+1) \end{array} \Big\} \\ \end{array} \\$ |                       | Inst(PC + 2)      | 1 1<br>1 1<br>1 1                       | Inst(0004h)            | Inst(0005h)            |

| Instruction<br>Executed { Inst(PC - 1) SLEEP                                                                                                                                                       |                       | Inst(PC + 1)      | Dummy cycle                             | Dummy cycle            | Inst(0004h)            |

| Note 1: XT, HS or LP Oscillator mode assume<br>2: Tost = 1024 Tosc (drawing not to sca                                                                                                             |                       | e there for RC Os | c mode.                                 |                        |                        |

3: GIE = 1 assumed. In this case, after wake-up, the processor jumps to the interrupt routine. If GIE = 0, execution will continue in-line.

4: CLKO is not available in these Osc modes, but shown here for timing reference.

#### 11.14 In-Circuit Debugger

When the DEBUG bit in the configuration word is programmed to a '0', the In-Circuit Debugger functionality is enabled. This function allows simple debugging functions when used with MPLAB<sup>®</sup> ICD. When the microcontroller has this feature enabled, some of the resources are not available for general use. Table 11-8 shows which features are consumed by the background debugger.

|  | TABLE 11-8: | DEBUGGER RESOURCES |

|--|-------------|--------------------|

|--|-------------|--------------------|

| I/O pins       | RB6, RB7                    |

|----------------|-----------------------------|

| Stack          | 1 level                     |

| Program Memory | Address 0000h must be NOP   |

|                | Last 100h words             |

| Data Memory    | 0x070 (0x0F0, 0x170, 0x1F0) |

|                | 0x1EB - 0x1EF               |

To use the In-Circuit Debugger function of the microcontroller, the design must implement In-Circuit Serial Programming connections to MCLR/VPP, VDD, GND, RB7 and RB6. This will interface to the In-Circuit Debugger module available from Microchip, or one of the third party development tool companies.

#### 11.15 Program Verification/Code Protection

If the code protection bit(s) have not been programmed, the on-chip program memory can be read out for verification purposes.

#### 11.16 ID Locations

Four memory locations (2000h - 2003h) are designated as ID locations, where the user can store checksum or other code identification numbers. These locations are not accessible during normal execution, but are readable and writable during program/verify. It is recommended that only the 4 Least Significant bits of the ID location are used.

### 12.0 INSTRUCTION SET SUMMARY

Each PIC16F870/871 instruction is a 14-bit word, divided into an OPCODE, which specifies the instruction type, and one or more operands, which further specify the operation of the instruction. The PIC16F870/871 instruction set summary in Table 12-2 lists **byte-oriented**, **bit-oriented**, and **literal and control** operations. Table 12-1 shows the opcode field descriptions.

For **byte-oriented** instructions, 'f' represents a file register designator and 'd' represents a destination designator. The file register designator specifies which file register is to be used by the instruction.

The destination designator specifies where the result of the operation is to be placed. If 'd' is zero, the result is placed in the W register. If 'd' is one, the result is placed in the file register specified in the instruction.

For **bit-oriented** instructions, 'b' represents a bit field designator which selects the number of the bit affected by the operation, while 'f' represents the address of the file in which the bit is located.

For **literal and control** operations, 'k' represents an eight or eleven bit constant or literal value.

#### TABLE 12-1: OPCODE FIELD DESCRIPTIONS

| Field | Description                                                                                                                                                                       |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| f     | Register file address (0x00 to 0x7F)                                                                                                                                              |

| W     | Working register (accumulator)                                                                                                                                                    |

| b     | Bit address within an 8-bit file register                                                                                                                                         |

| k     | Literal field, constant data or label                                                                                                                                             |

| x     | Don't care location (= $0$ or 1).<br>The assembler will generate code with x = $0$ .<br>It is the recommended form of use for<br>compatibility with all Microchip software tools. |

| d     | Destination select; $d = 0$ : store result in W,<br>d = 1: store result in file register f.<br>Default is $d = 1$ .                                                               |

| PC    | Program Counter                                                                                                                                                                   |

| ТО    | Time-out bit                                                                                                                                                                      |

| PD    | Power-down bit                                                                                                                                                                    |

The instruction set is highly orthogonal and is grouped into three basic categories:

- Byte-oriented operations

- Bit-oriented operations

- Literal and control operations

All instructions are executed within one single instruction cycle, unless a conditional test is true, or the program counter is changed as a result of an instruction. In this case, the execution takes two instruction cycles, with the second cycle executed as a NOP. One instruction cycle consists of four oscillator periods. Thus, for an oscillator frequency of 4 MHz, the normal instruction execution time is 1  $\mu$ s. If a conditional test is true, or the program counter is changed as a result of an instruction, the instruction execution time is 2  $\mu$ s.

Table 12-2 lists the instructions recognized by the MPASM<sup>™</sup> assembler.

Figure 12-1 shows the general formats that the instructions can have.

| Note: | To maintain upward compatibility with |

|-------|---------------------------------------|

|       | future PIC16F870/871 products, do not |

|       | use the OPTION and TRIS instructions. |

All examples use the following format to represent a hexadecimal number:

0xhh

where h signifies a hexadecimal digit.

### FIGURE 12-1: GENERAL FORMAT FOR INSTRUCTIONS

| Byte-orie                    | nted file reg                                                                         | jister op | eratio | ns          |   |

|------------------------------|---------------------------------------------------------------------------------------|-----------|--------|-------------|---|

| 13                           |                                                                                       | 8 7       | 6      |             | 0 |

| OP                           | CODE                                                                                  | d         |        | f (FILE #)  |   |

| d =                          | d = 0 for destination W<br>d = 1 for destination f<br>f = 7-bit file register address |           |        |             |   |

| Bit-orient                   | ed file regis                                                                         | ter oper  | ations | 6           |   |

| 13                           |                                                                                       | 10 9      | 7      | 6           | 0 |

| 0                            | PCODE                                                                                 | b (Bl     | T #)   | f (FILE #)  |   |

| f =<br>Literal an<br>General | 3-bit bit add<br>7-bit file reg<br>d control op                                       | pister ac | 6      | 5           |   |

| 13                           |                                                                                       | 8         | 7      |             | 0 |

| 0                            | PCODE                                                                                 |           |        | k (literal) |   |

| k = 8-bit immediate value    |                                                                                       |           |        |             |   |

| CALL and                     | I GOTO insti                                                                          | uctions   | only   |             |   |

| 13                           | 11                                                                                    | 10        |        |             | 0 |

| OP                           | CODE                                                                                  |           | k (l   | iteral)     |   |

| k =                          | k = 11-bit immediate value                                                            |           |        |             |   |

A description of each instruction is available in the PIC<sup>®</sup> Mid-Range MCU Family Reference Manual (DS33023).

| Rotate Left f through Carry                                                                                                                                                                                   |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [ <i>label</i> ] RLF f,d                                                                                                                                                                                      |

| $\begin{array}{l} 0 \leq f \leq 127 \\ d  \in  [0,1] \end{array}$                                                                                                                                             |

| See description below                                                                                                                                                                                         |

| С                                                                                                                                                                                                             |

| The contents of register 'f' are rotated<br>one bit to the left through the Carry<br>Flag. If 'd' is 0, the result is placed in<br>the W register. If 'd' is 1, the result is<br>stored back in register 'f'. |

|                                                                                                                                                                                                               |

### SLEEP

| Syntax:          | [label] SLEEP                                                                                                                                                                                                                        |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Operands:        | None                                                                                                                                                                                                                                 |

| Operation:       | $\begin{array}{l} 00h \rightarrow WDT, \\ 0 \rightarrow WDT \ prescaler, \\ 1 \rightarrow \overline{TO}, \\ 0 \rightarrow \overline{PD} \end{array}$                                                                                 |

| Status Affected: | TO, PD                                                                                                                                                                                                                               |

| Description:     | The power-down status bit, $\overline{\text{PD}}$ is cleared. Time-out status bit, $\overline{\text{TO}}$ is set. Watchdog Timer and its prescaler are cleared.<br>The processor is put into SLEEP mode with the oscillator stopped. |

| RETURN           | Return from Subroutine                                                                                                                                     |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] RETURN                                                                                                                                             |

| Operands:        | None                                                                                                                                                       |

| Operation:       | $TOS\toPC$                                                                                                                                                 |

| Status Affected: | None                                                                                                                                                       |

| Description:     | Return from subroutine. The stack<br>is POPed and the top of the stack<br>(TOS) is loaded into the program<br>counter. This is a two-cycle<br>instruction. |

| RRF              | Rotate Right f through Carry                                                                                                                                                                                      |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] RRF f,d                                                                                                                                                                                          |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \end{array}$                                                                                                                                                   |

| Operation:       | See description below                                                                                                                                                                                             |

| Status Affected: | С                                                                                                                                                                                                                 |

| Description:     | The contents of register 'f' are<br>rotated one bit to the right through<br>the Carry Flag. If 'd' is 0, the result<br>is placed in the W register. If 'd' is<br>1, the result is placed back in<br>register 'f'. |

|                  | C Register f                                                                                                                                                                                                      |

| SUBLW            | Subtract W from Literal                                                                                                      |  |  |  |

|------------------|------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Syntax:          | [ <i>label</i> ] SUBLW k                                                                                                     |  |  |  |

| Operands:        | $0 \leq k \leq 255$                                                                                                          |  |  |  |

| Operation:       | $k \text{ - } (W) \rightarrow (W)$                                                                                           |  |  |  |

| Status Affected: | C, DC, Z                                                                                                                     |  |  |  |

| Description:     | The W register is subtracted (2's complement method) from the eight-bit literal 'k'. The result is placed in the W register. |  |  |  |

| SUBWF               | Subtract W from f                                                                                                                                                                       |  |  |  |  |

|---------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:             | [ <i>label</i> ] SUBWF f,d                                                                                                                                                              |  |  |  |  |

| Operands:           | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \end{array}$                                                                                                                         |  |  |  |  |

| Operation:          | (f) - (W) $\rightarrow$ (destination)                                                                                                                                                   |  |  |  |  |

| Status<br>Affected: | C, DC, Z                                                                                                                                                                                |  |  |  |  |

| Description:        | Subtract (2's complement method)<br>W register from register 'f'. If 'd' is 0,<br>the result is stored in the W<br>register. If 'd' is 1, the result is<br>stored back in register 'f'. |  |  |  |  |

#### 13.20 PICDEM 18R PIC18C601/801 Demonstration Board

The PICDEM 18R demonstration board serves to assist development of the PIC18C601/801 family of Microchip microcontrollers. It provides hardware implementation of both 8-bit Multiplexed/De-multiplexed and 16-bit Memory modes. The board includes 2 Mb external FLASH memory and 128 Kb SRAM memory, as well as serial EEPROM, allowing access to the wide range of memory types supported by the PIC18C601/801.

#### 13.21 PICDEM LIN PIC16C43X Demonstration Board

The powerful LIN hardware and software kit includes a series of boards and three PIC microcontrollers. The small footprint PIC16C432 and PIC16C433 are used as slaves in the LIN communication and feature onboard LIN transceivers. A PIC16F874 FLASH microcontroller serves as the master. All three microcontrollers are programmed with firmware to provide LIN bus communication.

### 13.22 PICkit<sup>™</sup> 1 FLASH Starter Kit

A complete "development system in a box", the PICkit FLASH Starter Kit includes a convenient multi-section board for programming, evaluation, and development of 8/14-pin FLASH PIC<sup>®</sup> microcontrollers. Powered via USB, the board operates under a simple Windows GUI. The PICkit 1 Starter Kit includes the user's guide (on CD ROM), PICkit 1 tutorial software and code for various applications. Also included are MPLAB<sup>®</sup> IDE (Integrated Development Environment) software, software and hardware "Tips 'n Tricks for 8-pin FLASH PIC<sup>®</sup> Microcontrollers" Handbook and a USB Interface Cable. Supports all current 8/14-pin FLASH PIC microcontrollers, as well as many future planned devices.

#### 13.23 PICDEM USB PIC16C7X5 Demonstration Board

The PICDEM USB Demonstration Board shows off the capabilities of the PIC16C745 and PIC16C765 USB microcontrollers. This board provides the basis for future USB products.

#### 13.24 Evaluation and Programming Tools

In addition to the PICDEM series of circuits, Microchip has a line of evaluation kits and demonstration software for these products.

- KEELOQ evaluation and programming tools for Microchip's HCS Secure Data Products

- CAN developers kit for automotive network applications

- Analog design boards and filter design software

- PowerSmart battery charging evaluation/ calibration kits

- IrDA<sup>®</sup> development kit

- microID development and rfLab<sup>™</sup> development software

- SEEVAL<sup>®</sup> designer kit for memory evaluation and endurance calculations

- PICDEM MSC demo boards for Switching mode power supply, high power IR driver, delta sigma ADC, and flow rate sensor

Check the Microchip web page and the latest Product Line Card for the complete list of demonstration and evaluation kits.

#### 14.1 DC Characteristics: PIC16F870/871 (Industrial, Extended) PIC16LF870/871 (Commercial, Industrial)

| PIC16LF870/871<br>(Commercial, Industrial) |                    | $\begin{array}{l} \mbox{Standard Operating Conditions (unless otherwise stated)} \\ \mbox{Operating temperature -40°C} \leq TA \leq +85°C \mbox{ for Industrial} \\ \mbox{0°C} \leq TA \leq +70°C \mbox{ for Commercial} \end{array}$ |              |      |            |        |                                                                                       |  |

|--------------------------------------------|--------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|------|------------|--------|---------------------------------------------------------------------------------------|--|

| PIC16F870/871<br>(Industrial, Extended)    |                    | Standard Operating Conditions (unless otherwise stated)<br>Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial<br>$-40^{\circ}C \le TA \le +125^{\circ}C$ for Extended                                        |              |      |            |        |                                                                                       |  |

| Param<br>No.                               | Sym Characteristic |                                                                                                                                                                                                                                       | Min          | Тур† | Max        | Units  | Conditions                                                                            |  |

|                                            | VDD Supply Voltage |                                                                                                                                                                                                                                       |              |      |            |        |                                                                                       |  |

| D001                                       |                    | PIC16LF870/871                                                                                                                                                                                                                        | 2.0          |      | 5.5        | V      | All configurations. See Figure 14-2 for details.                                      |  |

| D001<br>D001A                              |                    | PIC16F870/871                                                                                                                                                                                                                         | 4.0<br>Vbor* | _    | 5.5<br>5.5 | V<br>V | All configurations.<br>BOR enabled, FMAX = 14 MHz <b>(Note 7)</b> ,<br>-40°C to +85°C |  |

|                                            |                    |                                                                                                                                                                                                                                       | VBOR         | —    | 5.5        | V      | BOR enabled, FMAX = 10 MHz <b>(Note 7)</b> ,<br>-40°C to +125°C                       |  |

| D002*                                      | Vdr                | RAM Data Retention<br>Voltage <sup>(1)</sup>                                                                                                                                                                                          | —            | 1.5  | —          | V      |                                                                                       |  |

| D003                                       | Vpor               | VDD Start Voltage to<br>ensure internal Power-on<br>Reset signal                                                                                                                                                                      | —            | Vss  | —          | V      | See section on Power-on Reset for details                                             |  |

| D004*                                      | SVDD               | VDD Rise Rate to ensure<br>internal Power-on Reset<br>signal                                                                                                                                                                          | 0.05         | —    | —          | V/ms   | See section on Power-on Reset for details                                             |  |

| D005                                       | VBOR               | Brown-out Reset<br>Voltage                                                                                                                                                                                                            | 3.7          | 4.0  | 4.35       | V      | BOREN bit in configuration word enabled                                               |  |

These parameters are characterized but not tested.

- † Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

- **Note 1:** This is the limit to which VDD can be lowered without losing RAM data.

- 2: The supply current is mainly a function of the operating voltage and frequency. Other factors such as I/O pin loading and switching rate, oscillator type, internal code execution pattern and temperature also have an impact on the current consumption.

- The test conditions for all IDD measurements in active Operation mode are:

- <u>OSC1</u> = external square wave, from rail to rail; all I/O pins tri-stated, pulled to VDD MCLR = VDD; WDT enabled/disabled as specified.