#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                   |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 20MHz                                                                    |

| Connectivity               | UART/USART                                                               |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                    |

| Number of I/O              | 22                                                                       |

| Program Memory Size        | 3.5KB (2K x 14)                                                          |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | 64 x 8                                                                   |

| RAM Size                   | 128 x 8                                                                  |

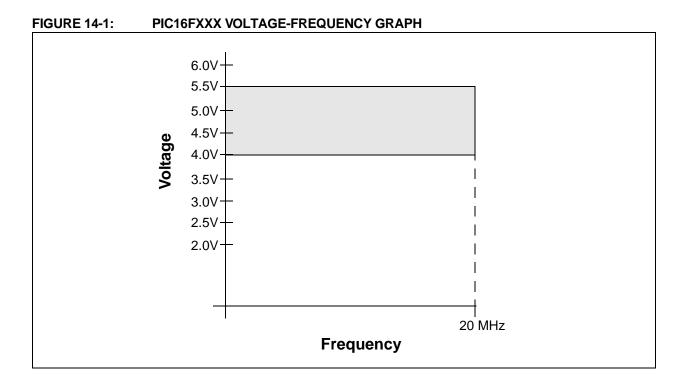

| Voltage - Supply (Vcc/Vdd) | 4V ~ 5.5V                                                                |

| Data Converters            | A/D 5x10b                                                                |

| Oscillator Type            | External                                                                 |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 28-SSOP (0.209", 5.30mm Width)                                           |

| Supplier Device Package    | 28-SSOP                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f870-i-ss |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

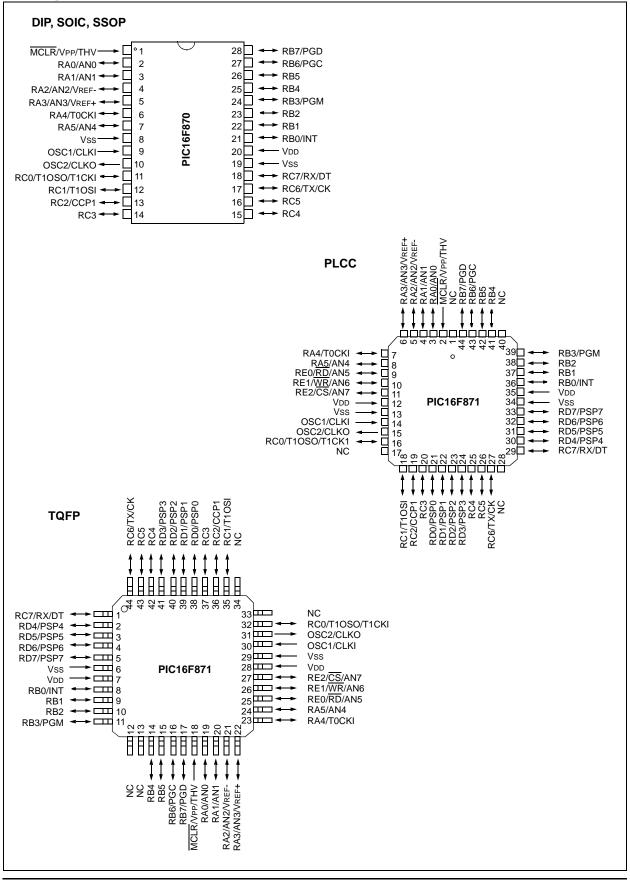

### **Pin Diagrams**

| Pin Name                     | DIP<br>Pin# | PLCC<br>Pin#    | QFP<br>Pin#       | I/O/P<br>Type | Buffer<br>Type                 | Description                                                                                         |

|------------------------------|-------------|-----------------|-------------------|---------------|--------------------------------|-----------------------------------------------------------------------------------------------------|

|                              |             |                 |                   |               |                                | PORTD is a bi-directional I/O port or parallel slave port when interfacing to a microprocessor bus. |

| RD0/PSP0                     | 19          | 21              | 38                | I/O           | ST/TTL <sup>(3)</sup>          |                                                                                                     |

| RD1/PSP1                     | 20          | 22              | 39                | I/O           | ST/TTL <sup>(3)</sup>          |                                                                                                     |

| RD2/PSP2                     | 21          | 23              | 40                | I/O           | ST/TTL <sup>(3)</sup>          |                                                                                                     |

| RD3/PSP3                     | 22          | 24              | 41                | I/O           | ST/TTL <sup>(3)</sup>          |                                                                                                     |

| RD4/PSP4                     | 27          | 30              | 2                 | I/O           | ST/TTL <sup>(3)</sup>          |                                                                                                     |

| RD5/PSP5                     | 28          | 31              | 3                 | I/O           | ST/TTL <sup>(3)</sup>          |                                                                                                     |

| RD6/PSP6                     | 29          | 32              | 4                 | I/O           | ST/TTL <sup>(3)</sup>          |                                                                                                     |

| RD7/PSP7                     | 30          | 33              | 5                 | I/O           | ST/TTL <sup>(3)</sup>          |                                                                                                     |

|                              |             |                 |                   |               |                                | PORTE is a bi-directional I/O port.                                                                 |

| RE0/RD/AN5                   | 8           | 9               | 25                | I/O           | ST/TTL <sup>(3)</sup>          | RE0 can also be read control for the parallel slave port, or analog input 5.                        |

| RE1/WR/AN6                   | 9           | 10              | 26                | I/O           | ST/TTL <sup>(3)</sup>          | RE1 can also be write control for the parallel slave port, or analog input 6.                       |

| RE2/CS/AN7                   | 10          | 11              | 27                | I/O           | ST/TTL <sup>(3)</sup>          | RE2 can also be select control for the parallel slave port, or analog input 7.                      |

| Vss                          | 12,31       | 13,34           | 6,29              | Р             | _                              | Ground reference for logic and I/O pins.                                                            |

| Vdd                          | 11,32       | 12,35           | 7,28              | Р             |                                | Positive supply for logic and I/O pins.                                                             |

| NC                           | -           | 1,17,28,<br>40  | 12,13,<br>33,34   |               | _                              | These pins are not internally connected. These pins should be left unconnected.                     |

| Legend: I = input<br>— = Not |             | O = ou<br>TTL = | ıtput<br>TTL inpu | ut            | I/O = input/ou<br>ST = Schmitt |                                                                                                     |

## TABLE 1-2: PIC16F871 PINOUT DESCRIPTION (CONTINUED)

**Note 1:** This buffer is a Schmitt Trigger input when configured as an external interrupt or LVP mode.

2: This buffer is a Schmitt Trigger input when used in Serial Programming mode.

**3:** This buffer is a Schmitt Trigger input when configured as general purpose I/O and a TTL input when used in the Parallel Slave Port mode (for interfacing to a microprocessor bus).

4: This buffer is a Schmitt Trigger input when configured in RC Oscillator mode and a CMOS input otherwise.

| Name         | Bit# | Buffer | Function                                                                    |

|--------------|------|--------|-----------------------------------------------------------------------------|

| RA0/AN0      | bit0 | TTL    | Input/output or analog input.                                               |

| RA1/AN1      | bit1 | TTL    | Input/output or analog input.                                               |

| RA2/AN2      | bit2 | TTL    | Input/output or analog input.                                               |

| RA3/AN3/VREF | bit3 | TTL    | Input/output or analog input or VREF.                                       |

| RA4/T0CKI    | bit4 | ST     | Input/output or external clock input for Timer0. Output is open drain type. |

| RA5/AN4      | bit5 | TTL    | Input/output or analog input.                                               |

#### TABLE 4-1: PORTA FUNCTIONS

Legend: TTL = TTL input, ST = Schmitt Trigger input

#### TABLE 4-2: SUMMARY OF REGISTERS ASSOCIATED WITH PORTA

| Address | Name   | Bit 7 | Bit 6 | Bit 5 | Bit 4                         | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Value on:<br>POR, BOR | Value on<br>all other<br>RESETS |

|---------|--------|-------|-------|-------|-------------------------------|-------|-------|-------|-------|-----------------------|---------------------------------|

| 05h     | PORTA  |       |       | RA5   | RA4                           | RA3   | RA2   | RA1   | RA0   | 0x 0000               | 0u 0000                         |

| 85h     | TRISA  | —     | —     | PORTA | PORTA Data Direction Register |       |       |       |       | 11 1111               | 11 1111                         |

| 9Fh     | ADCON1 | ADFM  | _     | _     |                               | PCFG3 | PCFG2 | PCFG1 | PCFG0 | 0- 0000               | 0- 0000                         |

Legend: x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells are not used by PORTA.

### 6.7 Resetting of Timer1 Register Pair (TMR1H, TMR1L)

TMR1H and TMR1L registers are not reset to 00h on a POR, or any other RESET, except by the CCP1 special event trigger.

T1CON register is reset to 00h on a Power-on Reset, or a Brown-out Reset, which shuts off the timer and leaves a 1:1 prescale. In all other RESETS, the register is unaffected.

## 6.8 Timer1 Prescaler

The prescaler counter is cleared on writes to the TMR1H or TMR1L registers.

## TABLE 6-2: REGISTERS ASSOCIATED WITH TIMER1 AS A TIMER/COUNTER

| Address                | Name   | Bit 7                                                                      | Bit 6      | Bit 5       | Bit 4       | Bit 3       | Bit 2     | Bit 1      | Bit 0  | Value<br>POR, |      | all c | e on<br>other<br>SETS |

|------------------------|--------|----------------------------------------------------------------------------|------------|-------------|-------------|-------------|-----------|------------|--------|---------------|------|-------|-----------------------|

| 0Bh,8Bh,<br>10Bh, 18Bh | INTCON | GIE                                                                        | PEIE       | TOIE        | INTE        | RBIE        | TOIF      | INTF       | RBIF   | 0000          | 000x | 0000  | 000u                  |

| 0Ch                    | PIR1   | PSPIF <sup>(1)</sup>                                                       | ADIF       | RCIF        | TXIF        | _           | CCP1IF    | TMR2IF     | TMR1IF | 0000          | -000 | 0000  | -000                  |

| 8Ch                    | PIE1   | PSPIE <sup>(1)</sup>                                                       | ADIE       | RCIE        | TXIE        | _           | CCP1IE    | TMR2IE     | TMR1IE | 0000          | -000 | 0000  | -000                  |

| 0Eh                    | TMR1L  | Holding R                                                                  | egister fo | r the Least | Significant | Byte of the | 16-bit TM | R1 Registe | er     | xxxx          | xxxx | uuuu  | uuuu                  |

| 0Fh                    | TMR1H  | Holding Register for the Most Significant Byte of the 16-bit TMR1 Register |            |             |             |             |           | xxxx       | xxxx   | uuuu          | uuuu |       |                       |

| 10h                    | T1CON  | _                                                                          | _          | T1CKPS1     | T1CKPS0     | T1OSCEN     | T1SYNC    | TMR1CS     | TMR10N | 00            | 0000 | uu    | uuuu                  |

Legend: x = unknown, u = unchanged, - = unimplemented, read as '0'. Shaded cells are not used by the Timer1 module.

Note 1: Bits PSPIE and PSPIF are reserved on the PIC16F870; always maintain these bits clear.

## 7.1 Timer2 Prescaler and Postscaler

The prescaler and postscaler counters are cleared when any of the following occurs:

- a write to the TMR2 register

- a write to the T2CON register

- any device RESET (POR, MCLR Reset, WDT Reset, or BOR)

TMR2 is not cleared when T2CON is written.

## 7.2 Output of TMR2

The output of TMR2 (before the postscaler) is fed to the SSP module, which optionally uses it to generate shift clock.

| TABLE 7-1: | <b>REGISTERS ASSOCIATED WITH TIMER2 AS A TIMER/COUNTER</b> |

|------------|------------------------------------------------------------|

|            |                                                            |

| Address               | Name   | Bit 7                | Bit 6       | Bit 5   | Bit 4   | Bit 3   | Bit 2  | Bit 1   | Bit 0   | Value<br>POR, |      | Valu<br>all c<br>RES | other |

|-----------------------|--------|----------------------|-------------|---------|---------|---------|--------|---------|---------|---------------|------|----------------------|-------|

| 0Bh,8Bh,<br>10Bh,18Bh | INTCON | GIE                  | PEIE        | TOIE    | INTE    | RBIE    | TOIF   | INTF    | RBIF    | 0000          | 000x | 0000                 | 000u  |

| 0Ch                   | PIR1   | PSPIF <sup>(1)</sup> | ADIF        | RCIF    | TXIF    | _       | CCP1IF | TMR2IF  | TMR1IF  | 0000          | -000 | 0000                 | -000  |

| 8Ch                   | PIE1   | PSPIE <sup>(1)</sup> | ADIE        | RCIE    | TXIE    | -       | CCP1IE | TMR2IE  | TMR1IE  | 0000          | -000 | 0000                 | -000  |

| 11h                   | TMR2   | Timer2 M             | lodule's Re | gister  |         |         |        |         |         | 0000          | 0000 | 0000                 | 0000  |

| 12h                   | T2CON  |                      | TOUTPS3     | TOUTPS2 | TOUTPS1 | TOUTPS0 | TMR2ON | T2CKPS1 | T2CKPS0 | -000          | 0000 | -000                 | 0000  |

| 92h                   | PR2    | Timer2 P             | eriod Regis | ter     |         |         |        |         |         | 1111          | 1111 | 1111                 | 1111  |

Legend: x = unknown, u = unchanged, - = unimplemented, read as '0'. Shaded cells are not used by the Timer2 module.

Note 1: Bits PSPIE and PSPIF are reserved on the PIC16F870; always maintain these bits clear.

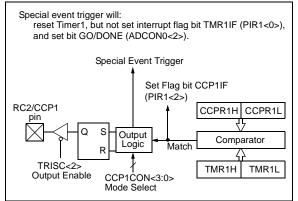

## 8.3 Compare Mode

In Compare mode, the 16-bit CCPR1 register value is constantly compared against the TMR1 register pair value. When a match occurs, the RC2/CCP1 pin is:

- Driven high

- Driven low

- · Remains unchanged

The action on the pin is based on the value of control bits, CCP1M3:CCP1M0 (CCP1CON<3:0>). At the same time, interrupt flag bit CCP1IF is set.

#### FIGURE 8-2: COMPARE MODE OPERATION BLOCK DIAGRAM

## 8.3.1 CCP PIN CONFIGURATION

The user must configure the RC2/CCP1 pin as an output by clearing the TRISC<2> bit.

| Note: | Clearing the CCP1CON register will force |

|-------|------------------------------------------|

|       | the RC2/CCP1 compare output latch to     |

|       | the default low level. This is not the   |

|       | PORTC I/O data latch.                    |

### 8.3.2 TIMER1 MODE SELECTION

Timer1 must be running in Timer mode, or Synchronized Counter mode, if the CCP module is using the compare feature. In Asynchronous Counter mode, the compare operation may not work.

#### 8.3.3 SOFTWARE INTERRUPT MODE

When Generate Software Interrupt mode is chosen, the CCP1 pin is not affected. The CCPIF bit is set, causing a CCP interrupt (if enabled).

#### 8.3.4 SPECIAL EVENT TRIGGER

In this mode, an internal hardware trigger is generated, which may be used to initiate an action.

The special event trigger output of CCP1 resets the TMR1 register pair, and starts an A/D conversion (if A/D module is enabled). This allows the CCPR1 register to effectively be a 16-bit programmable period register for Timer1.

**Note:** The special event trigger from the CCP1 module will not set interrupt flag bit TMR1IF (PIR1<0>).

## 9.2 USART Asynchronous Mode

In this mode, the USART uses standard non-return-tozero (NRZ) format (one START bit, eight or nine data bits, and one STOP bit). The most common data format is 8-bits. An on-chip, dedicated, 8-bit baud rate generator can be used to derive standard baud rate frequencies from the oscillator. The USART transmits and receives the LSb first. The transmitter and receiver are functionally independent, but use the same data format and baud rate. The baud rate generator produces a clock, either x16 or x64 of the bit shift rate, depending on bit BRGH (TXSTA<2>). Parity is not supported by the hardware, but can be implemented in software (and stored as the ninth data bit). Asynchronous mode is stopped during SLEEP.

Asynchronous mode is selected by clearing bit SYNC (TXSTA<4>).

The USART Asynchronous module consists of the following important elements:

- Baud Rate Generator

- · Sampling Circuit

- Asynchronous Transmitter

- Asynchronous Receiver

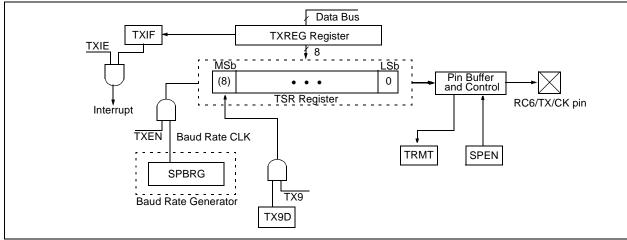

#### 9.2.1 USART ASYNCHRONOUS TRANSMITTER

The USART transmitter block diagram is shown in Figure 9-1. The heart of the transmitter is the Transmit (Serial) Shift register (TSR). The Shift register obtains its data from the read/write transmit buffer, TXREG. The TXREG register is loaded with data in software. The TSR register is not loaded until the STOP bit has been transmitted from the previous load. As soon as the STOP bit is transmitted, the TSR is loaded with new data from the TXREG register (if available). Once the TXREG register transfers the data to the TSR register (occurs in one TCY), the TXREG register is empty and flag bit TXIF (PIR1<4>) is set. This interrupt can be

enabled/disabled by setting/clearing enable bit TXIE (PIE1<4>). Flag bit TXIF will be set, regardless of the state of enable bit TXIE and cannot be cleared in software. It will reset only when new data is loaded into the TXREG register. While flag bit TXIF indicates the status of the TXREG register, another bit, TRMT (TXSTA<1>), shows the status of the TSR register. Status bit TRMT is a read only bit, which is set when the TSR register is empty. No interrupt logic is tied to this bit, so the user has to poll this bit in order to determine if the TSR register is empty.

| Note 1: | The TSR register is not mapped in data memory, so it is not available to the user.  |

|---------|-------------------------------------------------------------------------------------|

| 2:      | Flag bit TXIF is set when enable bit TXEN is set. TXIF is cleared by loading TXREG. |

Transmission is enabled by setting enable bit TXEN (TXSTA<5>). The actual transmission will not occur until the TXREG register has been loaded with data and the baud rate generator (BRG) has produced a shift clock (Figure 9-2). The transmission can also be started by first loading the TXREG register and then setting enable bit TXEN. Normally, when transmission is first started, the TSR register is empty. At that point, transfer to the TXREG register will result in an immediate transfer to TSR, resulting in an empty TXREG. A back-to-back transfer is thus possible (Figure 9-3). Clearing enable bit TXEN during a transmission will cause the transmission to be aborted and will reset the transmitter. As a result, the RC6/TX/CK pin will revert to hi-impedance.

In order to select 9-bit transmission, transmit bit TX9 (TXSTA<6>) should be set and the ninth bit should be written to TX9D (TXSTA<0>). The ninth bit must be written before writing the 8-bit data to the TXREG register. This is because a data write to the TXREG register can result in an immediate transfer of the data to the TSR register (if the TSR is empty). In such a case, an incorrect ninth data bit may be loaded in the TSR register.

#### FIGURE 9-1: USART TRANSMIT BLOCK DIAGRAM

## 9.4 USART Synchronous Slave Mode

Synchronous Slave mode differs from the Master mode in the fact that the shift clock is supplied externally at the RC6/TX/CK pin (instead of being supplied internally in Master mode). This allows the device to transfer or receive data while in SLEEP mode. Slave mode is entered by clearing bit CSRC (TXSTA<7>).

#### 9.4.1 USART SYNCHRONOUS SLAVE TRANSMIT

The operation of the Synchronous Master and Slave modes is identical, except in the case of the SLEEP mode.

If two words are written to the TXREG and then the SLEEP instruction is executed, the following will occur:

- a) The first word will immediately transfer to the TSR register and transmit.

- b) The second word will remain in TXREG register.

- c) Flag bit TXIF will not be set.

- When the first word has been shifted out of TSR, the TXREG register will transfer the second word to the TSR and flag bit TXIF will now be set.

- e) If enable bit TXIE is set, the interrupt will wake the chip from SLEEP and if the global interrupt is enabled, the program will branch to the interrupt vector (0004h).

When setting up a Synchronous Slave Transmission, follow these steps:

- 1. Enable the synchronous slave serial port by setting bits SYNC and SPEN and clearing bit CSRC.

- 2. Clear bits CREN and SREN.

- 3. If interrupts are desired, then set enable bit TXIE.

- 4. If 9-bit transmission is desired, then set bit TX9.

- 5. Enable the transmission by setting enable bit TXEN.

- 6. If 9-bit transmission is selected, the ninth bit should be loaded in bit TX9D.

- 7. Start transmission by loading data to the TXREG register.

- 8. If using interrupts, ensure that GIE and PEIE (bits 7 and 6) of the INTCON register are set.

| Address                | Name                                   | Bit 7                | Bit 6     | Bit 5   | Bit 4 | Bit 3 | Bit 2  | Bit 1  | Bit 0  | Value on:<br>POR, BOR | Value on<br>all other<br>RESETS |

|------------------------|----------------------------------------|----------------------|-----------|---------|-------|-------|--------|--------|--------|-----------------------|---------------------------------|

| 0Bh, 8Bh,<br>10Bh,18Bh | INTCON                                 | GIE                  | PEIE      | TOIE    | INTE  | RBIE  | TOIF   | INTF   | R0IF   | 0000 000x             | 0000 000u                       |

| 0Ch                    | PIR1                                   | PSPIF <sup>(1)</sup> | ADIF      | RCIF    | TXIF  | —     | CCP1IF | TMR2IF | TMR1IF | 0000 -000             | 0000 -000                       |

| 18h                    | RCSTA                                  | SPEN                 | RX9       | SREN    | CREN  | ADDEN | FERR   | OERR   | RX9D   | x000 000x             | x000 000x                       |

| 19h                    | TXREG                                  | USART Tr             | ansmit Re | egister |       |       |        |        |        | 0000 0000             | 0000 0000                       |

| 8Ch                    | PIE1                                   | PSPIE <sup>(1)</sup> | ADIE      | RCIE    | TXIE  | —     | CCP1IE | TMR2IE | TMR1IE | 0000 -000             | 0000 -000                       |

| 98h                    | TXSTA                                  | CSRC                 | TX9       | TXEN    | SYNC  | _     | BRGH   | TRMT   | TX9D   | 0000 -010             | 0000 -010                       |

| 99h                    | 99h SPBRG Baud Rate Generator Register |                      |           |         |       |       |        |        |        | 0000 0000             | 0000 0000                       |

#### TABLE 9-10: REGISTERS ASSOCIATED WITH SYNCHRONOUS SLAVE TRANSMISSION

Legend: x = unknown, - = unimplemented, read as '0'. Shaded cells are not used for synchronous slave transmission.

Note 1: Bits PSPIE and PSPIF are reserved on the PIC16F870; always maintain these bits clear.

NOTES:

## TABLE 11-2:CAPACITOR SELECTION FOR<br/>CRYSTAL OSCILLATOR

| Osc Type | Crystal<br>Freq. | Cap. Range<br>C1 | Cap. Range<br>C2 |

|----------|------------------|------------------|------------------|

| LP       | 32 kHz           | 33 pF            | 33 pF            |

|          | 200 kHz          | 15 pF            | 15 pF            |

| XT       | 200 kHz          | 47-68 pF         | 47-68 pF         |

|          | 1 MHz            | 15 pF            | 15 pF            |

|          | 4 MHz            | 15 pF            | 15 pF            |

| HS       | 4 MHz            | 15 pF            | 15 pF            |

|          | 8 MHz            | 15-33 pF         | 15-33 pF         |

|          | 20 MHz           | 15-33 pF         | 15-33 pF         |

**These values are for design guidance only.** See notes following this table.

|         | Crystals Used          |          |  |  |  |  |  |  |

|---------|------------------------|----------|--|--|--|--|--|--|

| 32 kHz  | Epson C-001R32.768K-A  | ± 20 PPM |  |  |  |  |  |  |

| 200 kHz | STD XTL 200.000KHz     | ± 20 PPM |  |  |  |  |  |  |

| 1 MHz   | ECS ECS-10-13-1        | ± 50 PPM |  |  |  |  |  |  |

| 4 MHz   | ECS ECS-40-20-1        | ± 50 PPM |  |  |  |  |  |  |

| 8 MHz   | EPSON CA-301 8.000M-C  | ± 30 PPM |  |  |  |  |  |  |

| 20 MHz  | EPSON CA-301 20.000M-C | ± 30 PPM |  |  |  |  |  |  |

- Note 1: Higher capacitance increases the stability of oscillator, but also increases the start-up time.

- Since each resonator/crystal has its own characteristics, the user should consult the resonator/crystal manufacturer for appropriate values of external components.

- **3:** *R*<sub>s</sub> may be required in HS mode, as well as XT mode, to avoid overdriving crystals with low drive level specification.

- 4: When migrating from other PIC<sup>®</sup> devices, oscillator performance should be verified.

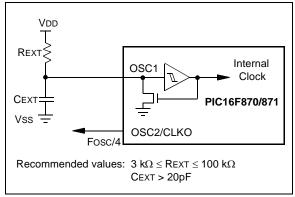

## 11.2.3 RC OSCILLATOR

For timing insensitive applications, the "RC" device option offers additional cost savings. The RC oscillator frequency is a function of the supply voltage, the resistor (REXT) and capacitor (CEXT) values, and the operating temperature. In addition to this, the oscillator frequency will vary from unit to unit due to normal process parameter variation. Furthermore, the difference in lead frame capacitance between package types will also affect the oscillation frequency, especially for low CEXT values. The user also needs to take into account variation due to tolerance of external R and C components used. Figure 11-3 shows how the R/C combination is connected to the PIC16F870/871.

#### FIGURE 11-3: RC OSCILLATOR MODE

| TABLE 11-6: | INITIALIZATION CONDITIONS FOR ALL REGISTERS (CONTINUED) |           |                                    |                          |                                 |  |  |  |  |

|-------------|---------------------------------------------------------|-----------|------------------------------------|--------------------------|---------------------------------|--|--|--|--|

| Register    | Devices                                                 |           | Power-on Reset,<br>Brown-out Reset | MCLR Resets<br>WDT Reset | Wake-up via WDT or<br>Interrupt |  |  |  |  |

| PIR1        | PIC16F870                                               | PIC16F871 | r000 -000                          | r000 -000                | ruuu -uuu <b>(1)</b>            |  |  |  |  |

|             | PIC16F870                                               | PIC16F871 | 0000 -000                          | 0000 -000                | uuuu -uuu <b>(1)</b>            |  |  |  |  |

| PIR2        | PIC16F870                                               | PIC16F871 | 0                                  | 0                        | u(1)                            |  |  |  |  |

| TMR1L       | PIC16F870                                               | PIC16F871 | XXXX XXXX                          | uuuu uuuu                | uuuu uuuu                       |  |  |  |  |

| TMR1H       | PIC16F870                                               | PIC16F871 | XXXX XXXX                          | uuuu uuuu                | uuuu uuuu                       |  |  |  |  |

| T1CON       | PIC16F870                                               | PIC16F871 | 00 0000                            | uu uuuu                  | uu uuuu                         |  |  |  |  |

| TMR2        | PIC16F870                                               | PIC16F871 | 0000 0000                          | 0000 0000                | uuuu uuuu                       |  |  |  |  |

| T2CON       | PIC16F870                                               | PIC16F871 | -000 0000                          | -000 0000                | -uuu uuuu                       |  |  |  |  |

| CCPR1L      | PIC16F870                                               | PIC16F871 | XXXX XXXX                          | uuuu uuuu                | uuuu uuuu                       |  |  |  |  |

| CCPR1H      | PIC16F870                                               | PIC16F871 | XXXX XXXX                          | uuuu uuuu                | uuuu uuuu                       |  |  |  |  |

| CCP1CON     | PIC16F870                                               | PIC16F871 | 00 0000                            | 00 0000                  | uu uuuu                         |  |  |  |  |

| RCSTA       | PIC16F870                                               | PIC16F871 | 0000 000x                          | 0000 000x                | uuuu uuuu                       |  |  |  |  |

| TXREG       | PIC16F870                                               | PIC16F871 | 0000 0000                          | 0000 0000                | uuuu uuuu                       |  |  |  |  |

| RCREG       | PIC16F870                                               | PIC16F871 | 0000 0000                          | 0000 0000                | uuuu uuuu                       |  |  |  |  |

| ADRESH      | PIC16F870                                               | PIC16F871 | XXXX XXXX                          | uuuu uuuu                | uuuu uuuu                       |  |  |  |  |

| ADCON0      | PIC16F870                                               | PIC16F871 | 0000 00-0                          | 0000 00-0                | uuuu uu-u                       |  |  |  |  |

| OPTION_REG  | PIC16F870                                               | PIC16F871 | 1111 1111                          | 1111 1111                | uuuu uuuu                       |  |  |  |  |

| TRISA       | PIC16F870                                               | PIC16F871 | 11 1111                            | 11 1111                  | uu uuuu                         |  |  |  |  |

| TRISB       | PIC16F870                                               | PIC16F871 | 1111 1111                          | 1111 1111                | uuuu uuuu                       |  |  |  |  |

| TRISC       | PIC16F870                                               | PIC16F871 | 1111 1111                          | 1111 1111                | uuuu uuuu                       |  |  |  |  |

| TRISD       | PIC16F870                                               | PIC16F871 | 1111 1111                          | 1111 1111                | uuuu uuuu                       |  |  |  |  |

| TRISE       | PIC16F870                                               | PIC16F871 | 0000 -111                          | 0000 -111                | uuuu -uuu                       |  |  |  |  |

| PIE1        | PIC16F870                                               | PIC16F871 | r000 -000                          | r000 -000                | ruuu -uuu                       |  |  |  |  |

|             | PIC16F870                                               | PIC16F871 | 0000 0000                          | 0000 0000                | uuuu uuuu                       |  |  |  |  |

| PIE2        | PIC16F870                                               | PIC16F871 | 0                                  | 0                        | u                               |  |  |  |  |

| PCON        | PIC16F870                                               | PIC16F871 | dd                                 | uu                       | uu                              |  |  |  |  |

| PR2         | PIC16F870                                               | PIC16F871 | 1111 1111                          | 1111 1111                | 1111 1111                       |  |  |  |  |

| TXSTA       | PIC16F870                                               | PIC16F871 | 0000 -010                          | 0000 -010                | uuuu -uuu                       |  |  |  |  |

| SPBRG       | PIC16F870                                               | PIC16F871 | 0000 0000                          | 0000 0000                | uuuu uuuu                       |  |  |  |  |

| ADRESL      | PIC16F870                                               | PIC16F871 | XXXX XXXX                          | uuuu uuuu                | uuuu uuuu                       |  |  |  |  |

| ADCON1      | PIC16F870                                               | PIC16F871 | 0 0000                             | 0 0000                   | u uuuu                          |  |  |  |  |

| EEDATA      | PIC16F870                                               | PIC16F871 | 0 0000                             | 0 0000                   | u uuuu                          |  |  |  |  |

| EEADR       | PIC16F870                                               | PIC16F871 | XXXX XXXX                          | uuuu uuuu                | uuuu uuuu                       |  |  |  |  |

| EEDATH      | PIC16F870                                               | PIC16F871 | XXXX XXXX                          | uuuu uuuu                | uuuu uuuu                       |  |  |  |  |

| EEADRH      | PIC16F870                                               | PIC16F871 | XXXX XXXX                          | uuuu uuuu                | uuuu uuuu                       |  |  |  |  |

| EECON1      | PIC16F870                                               | PIC16F871 | x x000                             | u u000                   | u uuuu                          |  |  |  |  |

| EECON2      | PIC16F870                                               | PIC16F871 |                                    |                          |                                 |  |  |  |  |

## TABLE 11-6: INITIALIZATION CONDITIONS FOR ALL REGISTERS (CONTINUED)

Legend: u = unchanged, x = unknown, - = unimplemented bit, read as '0', q = value depends on condition, r = reserved, maintain clear

Note 1: One or more bits in INTCON, PIR1 and/or PIR2 will be affected (to cause wake-up).

2: When the wake-up is due to an interrupt and the GIE bit is set, the PC is loaded with the interrupt vector (0004h).

3: See Table 11-5 for RESET value for specific condition.

| DECFSZ           | Decrement f, Skip if 0                                                                                                                                                                                                                                                                                |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] DECFSZ f,d                                                                                                                                                                                                                                                                                    |

| Operands:        | $\begin{array}{l} 0\leq f\leq 127\\ d\in [0,1] \end{array}$                                                                                                                                                                                                                                           |

| Operation:       | (f) - 1 $\rightarrow$ (destination);<br>skip if result = 0                                                                                                                                                                                                                                            |

| Status Affected: | None                                                                                                                                                                                                                                                                                                  |

| Description:     | The contents of register 'f' are decremented. If 'd' is 0, the result is placed in the W register. If 'd' is 1, the result is placed back in register 'f'.<br>If the result is 1, the next instruction is executed. If the result is 0, then a NOP is executed instead making it a 2 TCY instruction. |

| INCFSZ           | Increment f, Skip if 0                                                                                                                                                                                                                                                                                                   |  |  |  |  |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:          | [label] INCFSZ f,d                                                                                                                                                                                                                                                                                                       |  |  |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d  \in  [0,1] \end{array}$                                                                                                                                                                                                                                                        |  |  |  |  |

| Operation:       | (f) + 1 $\rightarrow$ (destination),<br>skip if result = 0                                                                                                                                                                                                                                                               |  |  |  |  |

| Status Affected: | None                                                                                                                                                                                                                                                                                                                     |  |  |  |  |

| Description:     | The contents of register 'f' are<br>incremented. If 'd' is 0, the result is<br>placed in the W register. If 'd' is 1,<br>the result is placed back in<br>register 'f'.<br>If the result is 1, the next instruc-<br>tion is executed. If the result is 0,<br>a NOP is executed instead, making<br>it a 2 TCY instruction. |  |  |  |  |

| GOTO             | Unconditional Branch                                                                                                                                                                             |  |  |  |  |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:          | [ <i>label</i> ] GOTO k                                                                                                                                                                          |  |  |  |  |

| Operands:        | $0 \leq k \leq 2047$                                                                                                                                                                             |  |  |  |  |

| Operation:       | $k \rightarrow PC<10:0>$<br>PCLATH<4:3> $\rightarrow$ PC<12:11>                                                                                                                                  |  |  |  |  |

| Status Affected: | None                                                                                                                                                                                             |  |  |  |  |

| Description:     | GOTO is an unconditional branch.<br>The eleven-bit immediate value is<br>loaded into PC bits <10:0>. The<br>upper bits of PC are loaded from<br>PCLATH<4:3>. GOTO is a<br>two-cycle instruction. |  |  |  |  |

| IORLW            | Inclusive OR Literal with W                                                                                               |  |  |  |  |

|------------------|---------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:          | [ <i>label</i> ] IORLW k                                                                                                  |  |  |  |  |

| Operands:        | $0 \leq k \leq 255$                                                                                                       |  |  |  |  |

| Operation:       | (W) .OR. $k \rightarrow$ (W)                                                                                              |  |  |  |  |

| Status Affected: | Z                                                                                                                         |  |  |  |  |

| Description:     | The contents of the W register are<br>OR'ed with the eight bit literal 'k'.<br>The result is placed in the W<br>register. |  |  |  |  |

| INCF             | Increment f                                                                                                                                                            | IORWF            | Inclusive OR W with f                                                                                                                                                 |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] INCF f,d                                                                                                                                                       | Syntax:          | [ <i>label</i> ] IORWF f,d                                                                                                                                            |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \end{array}$                                                                                                        | Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \end{array}$                                                                                                       |

| Operation:       | (f) + 1 $\rightarrow$ (destination)                                                                                                                                    | Operation:       | (W) .OR. (f) $\rightarrow$ (destination)                                                                                                                              |

| Status Affected: | Z                                                                                                                                                                      | Status Affected: | Z                                                                                                                                                                     |

| Description:     | The contents of register 'f' are<br>incremented. If 'd' is 0, the result<br>is placed in the W register. If 'd' is<br>1, the result is placed back in<br>register 'f'. | Description:     | Inclusive OR the W register with<br>register 'f'. If 'd' is 0 the result is<br>placed in the W register. If 'd' is 1<br>the result is placed back in<br>register 'f'. |

## 13.0 DEVELOPMENT SUPPORT

The PIC<sup>®</sup> microcontrollers are supported with a full range of hardware and software development tools:

- Integrated Development Environment

- MPLAB<sup>®</sup> IDE Software

- Assemblers/Compilers/Linkers

- MPASM<sup>™</sup> Assembler

- MPLAB C17 and MPLAB C18 C Compilers

- MPLINK<sup>™</sup> Object Linker/

- MPLIB<sup>™</sup> Object Librarian

- MPLAB C30 C Compiler

- MPLAB ASM30 Assembler/Linker/Library

- Simulators

- MPLAB SIM Software Simulator

- MPLAB dsPIC30 Software Simulator

- Emulators

- MPLAB ICE 2000 In-Circuit Emulator

- MPLAB ICE 4000 In-Circuit Emulator

- In-Circuit Debugger

- MPLAB ICD 2

- Device Programmers

- PRO MATE<sup>®</sup> II Universal Device Programmer

- PICSTART<sup>®</sup> Plus Development Programmer

- Low Cost Demonstration Boards

- PICDEM<sup>™</sup> 1 Demonstration Board

- PICDEM.net<sup>™</sup> Demonstration Board

- PICDEM 2 Plus Demonstration Board

- PICDEM 3 Demonstration Board

- PICDEM 4 Demonstration Board

- PICDEM 17 Demonstration Board

- PICDEM 18R Demonstration Board

- PICDEM LIN Demonstration Board

- PICDEM USB Demonstration Board

- Evaluation Kits

- KEELOQ<sup>®</sup>

- PICDEM MSC

- microID®

- CAN

- PowerSmart®

- Analog

## 13.1 MPLAB Integrated Development Environment Software

The MPLAB IDE software brings an ease of software development previously unseen in the 8/16-bit microcontroller market. The MPLAB IDE is a Windows<sup>®</sup> based application that contains:

- An interface to debugging tools

- simulator

- programmer (sold separately)

- emulator (sold separately)

- in-circuit debugger (sold separately)

- A full-featured editor with color coded context

- A multiple project manager

- Customizable data windows with direct edit of contents

- High level source code debugging

- Mouse over variable inspection

- Extensive on-line help

- The MPLAB IDE allows you to:

- Edit your source files (either assembly or C)

- One touch assemble (or compile) and download to PIC MCU emulator and simulator tools (automatically updates all project information)

- Debug using:

- source files (assembly or C)

- absolute listing file (mixed assembly and C)

- machine code

MPLAB IDE supports multiple debugging tools in a single development paradigm, from the cost effective simulators, through low cost in-circuit debuggers, to full-featured emulators. This eliminates the learning curve when upgrading to tools with increasing flexibility and power.

## 13.2 MPASM Assembler

The MPASM assembler is a full-featured, universal macro assembler for all PIC MCUs.

The MPASM assembler generates relocatable object files for the MPLINK object linker, Intel<sup>®</sup> standard HEX files, MAP files to detail memory usage and symbol reference, absolute LST files that contain source lines and generated machine code and COFF files for debugging.

The MPASM assembler features include:

- Integration into MPLAB IDE projects

- User defined macros to streamline assembly code

- Conditional assembly for multi-purpose source files

- Directives that allow complete control over the assembly process

| Param<br>No. | Sym   | Characteristic                     | Min | Тур† | Max    | Units | Conditions         |

|--------------|-------|------------------------------------|-----|------|--------|-------|--------------------|

|              | Fosc  | External CLKI Frequency            | DC  |      | 4      | MHz   | XT and RC Osc mode |

|              |       | (Note 1)                           | DC  |      | 4      | MHz   | HS Osc mode (-04)  |

|              |       |                                    | DC  |      | 20     | MHz   | HS Osc mode (-20)  |

|              |       |                                    | DC  | _    | 200    | kHz   | LP Osc mode        |

|              |       | Oscillator Frequency               | DC  | _    | 4      | MHz   | RC Osc mode        |

|              |       | (Note 1)                           | 0.1 |      | 4      | MHz   | XT Osc mode        |

|              |       |                                    | 4   | _    | 20     | MHz   | HS Osc mode        |

|              |       |                                    | 5   | _    | 200    | kHz   | LP Osc mode        |

|              |       | External CLKI Period               | 250 | —    | —      | ns    | XT and RC Osc mode |

|              |       | (Note 1)                           | 250 | _    | —      | ns    | HS Osc mode (-04)  |

|              |       |                                    | 50  | —    | —      | ns    | HS Osc mode (-20)  |

|              |       |                                    | 5   | _    |        | μS    | LP Osc mode        |

|              |       | Oscillator Period                  | 250 | _    | —      | ns    | RC Osc mode        |

|              |       | (Note 1)                           | 250 |      | 10,000 | ns    | XT Osc mode        |

|              |       |                                    | 250 |      | 250    | ns    | HS Osc mode (-04)  |

|              |       |                                    | 50  |      | 250    | ns    | HS Osc mode (-20)  |

|              |       |                                    | 5   |      | —      | μS    | LP Osc mode        |

| 2            | Тсү   | Instruction Cycle Time<br>(Note 1) | 200 | Тсү  | DC     | ns    | TCY = 4/FOSC       |

| 3            | TosL, | External Clock in (OSC1) High      | 100 |      | —      | ns    | XT oscillator      |

|              | TosH  | or Low Time                        | 2.5 |      | —      | μS    | LP oscillator      |

|              |       |                                    | 15  |      | —      | ns    | HS oscillator      |

| 4            | TosR, | External Clock in (OSC1) Rise      | _   | _    | 25     | ns    | XT oscillator      |

|              | TosF  | or Fall Time                       | _   | _    | 50     | ns    | LP oscillator      |

|              |       |                                    | _   | _    | 15     | ns    | HS oscillator      |

TABLE 14-1: EXTERNAL CLOCK TIMING REQUIREMENTS

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

**Note 1:** Instruction cycle period (TCY) equals four times the input oscillator time base period. All specified values are based on characterization data for that particular oscillator type under standard operating conditions with the device executing code. Exceeding these specified limits may result in an unstable oscillator operation and/or higher than expected current consumption. All devices are tested to operate at "min." values with an external clock applied to the OSC1/CLKI pin. When an external clock input is used, the "Max." cycle time limit is "DC" (no clock) for all devices.

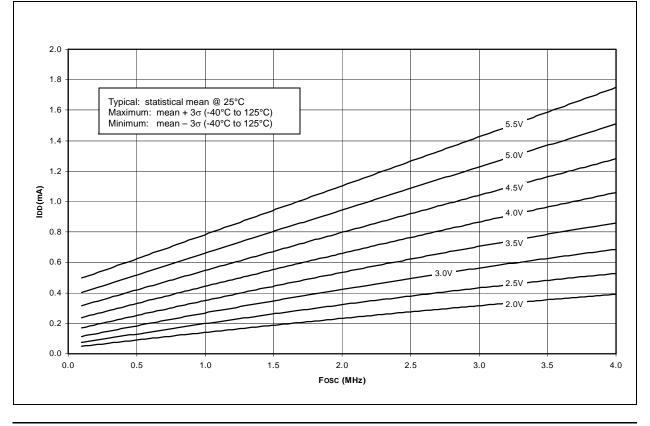

## 44-Lead Plastic Leaded Chip Carrier (L) – Square (PLCC)

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          |     | INCHES* |      | MILLIMETERS |       |       |       |

|--------------------------|-----|---------|------|-------------|-------|-------|-------|

| Dimension Limits         |     | MIN     | NOM  | MAX         | MIN   | NOM   | MAX   |

| Number of Pins           | n   |         | 44   |             |       | 44    |       |

| Pitch                    | р   |         | .050 |             |       | 1.27  |       |

| Pins per Side            | n1  |         | 11   |             |       | 11    |       |

| Overall Height           | А   | .165    | .173 | .180        | 4.19  | 4.39  | 4.57  |

| Molded Package Thickness | A2  | .145    | .153 | .160        | 3.68  | 3.87  | 4.06  |

| Standoff §               | A1  | .020    | .028 | .035        | 0.51  | 0.71  | 0.89  |

| Side 1 Chamfer Height    | A3  | .024    | .029 | .034        | 0.61  | 0.74  | 0.86  |

| Corner Chamfer 1         | CH1 | .040    | .045 | .050        | 1.02  | 1.14  | 1.27  |

| Corner Chamfer (others)  | CH2 | .000    | .005 | .010        | 0.00  | 0.13  | 0.25  |

| Overall Width            | Е   | .685    | .690 | .695        | 17.40 | 17.53 | 17.65 |

| Overall Length           | D   | .685    | .690 | .695        | 17.40 | 17.53 | 17.65 |

| Molded Package Width     | E1  | .650    | .653 | .656        | 16.51 | 16.59 | 16.66 |

| Molded Package Length    | D1  | .650    | .653 | .656        | 16.51 | 16.59 | 16.66 |

| Footprint Width          | E2  | .590    | .620 | .630        | 14.99 | 15.75 | 16.00 |

| Footprint Length         | D2  | .590    | .620 | .630        | 14.99 | 15.75 | 16.00 |

| Lead Thickness           | С   | .008    | .011 | .013        | 0.20  | 0.27  | 0.33  |

| Upper Lead Width         | B1  | .026    | .029 | .032        | 0.66  | 0.74  | 0.81  |

| Lower Lead Width         | В   | .013    | .020 | .021        | 0.33  | 0.51  | 0.53  |

| Mold Draft Angle Top     | α   | 0       | 5    | 10          | 0     | 5     | 10    |

| Mold Draft Angle Bottom  | β   | 0       | 5    | 10          | 0     | 5     | 10    |

\* Controlling Parameter

§ Significant Characteristic

Notes:

Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed .010" (0.254mm) per side.

JEDEC Equivalent: MO-047

Drawing No. C04-048

## THE MICROCHIP WEB SITE

Microchip provides online support via our WWW site at www.microchip.com. This web site is used as a means to make files and information easily available to customers. Accessible by using your favorite Internet browser, the web site contains the following information:

- Product Support Data sheets and errata, application notes and sample programs, design resources, user's guides and hardware support documents, latest software releases and archived software

- General Technical Support Frequently Asked Questions (FAQ), technical support requests, online discussion groups, Microchip consultant program member listing

- Business of Microchip Product selector and ordering guides, latest Microchip press releases, listing of seminars and events, listings of Microchip sales offices, distributors and factory representatives

## CUSTOMER CHANGE NOTIFICATION SERVICE

Microchip's customer notification service helps keep customers current on Microchip products. Subscribers will receive e-mail notification whenever there are changes, updates, revisions or errata related to a specified product family or development tool of interest.

To register, access the Microchip web site at www.microchip.com. Under "Support", click on "Customer Change Notification" and follow the registration instructions.

## **CUSTOMER SUPPORT**

Users of Microchip products can receive assistance through several channels:

- Distributor or Representative

- Local Sales Office

- Field Application Engineer (FAE)

- Technical Support

Customers should contact their distributor, representative or field application engineer (FAE) for support. Local sales offices are also available to help customers. A listing of sales offices and locations is included in the back of this document.

Technical support is available through the web site at: http://microchip.com/support

NOTES:

## Worldwide Sales and Service

#### AMERICAS

Corporate Office 2355 West Chandler Blvd. Chandler, AZ 85224-6199 Tel: 480-792-7200 Fax: 480-792-7277 Technical Support: http://www.microchip.com/ support Web Address: www.microchip.com

Atlanta Duluth, GA Tel: 678-957-9614 Fax: 678-957-1455

Boston Westborough, MA Tel: 774-760-0087 Fax: 774-760-0088

Chicago Itasca, IL Tel: 630-285-0071 Fax: 630-285-0075

**Cleveland** Independence, OH Tel: 216-447-0464 Fax: 216-447-0643

**Dallas** Addison, TX Tel: 972-818-7423 Fax: 972-818-2924

Detroit Farmington Hills, MI Tel: 248-538-2250 Fax: 248-538-2260

Indianapolis Noblesville, IN Tel: 317-773-8323 Fax: 317-773-5453

Los Angeles Mission Viejo, CA Tel: 949-462-9523 Fax: 949-462-9608

Santa Clara Santa Clara, CA Tel: 408-961-6444 Fax: 408-961-6445

Toronto Mississauga, Ontario, Canada Tel: 905-673-0699 Fax: 905-673-6509

#### ASIA/PACIFIC

Asia Pacific Office Suites 3707-14, 37th Floor Tower 6, The Gateway Harbour City, Kowloon Hong Kong Tel: 852-2401-1200 Fax: 852-2401-3431 Australia - Sydney

Tel: 61-2-9868-6733 Fax: 61-2-9868-6755

**China - Beijing** Tel: 86-10-8569-7000 Fax: 86-10-8528-2104

**China - Chengdu** Tel: 86-28-8665-5511 Fax: 86-28-8665-7889

China - Chongqing Tel: 86-23-8980-9588 Fax: 86-23-8980-9500

**China - Hangzhou** Tel: 86-571-2819-3187 Fax: 86-571-2819-3189

**China - Hong Kong SAR** Tel: 852-2943-5100 Fax: 852-2401-3431

**China - Nanjing** Tel: 86-25-8473-2460 Fax: 86-25-8473-2470

**China - Qingdao** Tel: 86-532-8502-7355 Fax: 86-532-8502-7205

**China - Shanghai** Tel: 86-21-5407-5533 Fax: 86-21-5407-5066

**China - Shenyang** Tel: 86-24-2334-2829 Fax: 86-24-2334-2393

**China - Shenzhen** Tel: 86-755-8864-2200 Fax: 86-755-8203-1760

**China - Wuhan** Tel: 86-27-5980-5300 Fax: 86-27-5980-5118

**China - Xian** Tel: 86-29-8833-7252 Fax: 86-29-8833-7256

**China - Xiamen** Tel: 86-592-2388138 Fax: 86-592-2388130

**China - Zhuhai** Tel: 86-756-3210040 Fax: 86-756-3210049

#### ASIA/PACIFIC

India - Bangalore Tel: 91-80-3090-4444 Fax: 91-80-3090-4123

India - New Delhi Tel: 91-11-4160-8631 Fax: 91-11-4160-8632

India - Pune Tel: 91-20-2566-1512 Fax: 91-20-2566-1513

**Japan - Osaka** Tel: 81-6-6152-7160 Fax: 81-6-6152-9310

**Japan - Tokyo** Tel: 81-3-6880- 3770 Fax: 81-3-6880-3771

**Korea - Daegu** Tel: 82-53-744-4301 Fax: 82-53-744-4302

Korea - Seoul Tel: 82-2-554-7200 Fax: 82-2-558-5932 or 82-2-558-5934

Malaysia - Kuala Lumpur Tel: 60-3-6201-9857 Fax: 60-3-6201-9859

**Malaysia - Penang** Tel: 60-4-227-8870 Fax: 60-4-227-4068

Philippines - Manila Tel: 63-2-634-9065 Fax: 63-2-634-9069

**Singapore** Tel: 65-6334-8870 Fax: 65-6334-8850

**Taiwan - Hsin Chu** Tel: 886-3-5778-366 Fax: 886-3-5770-955

Taiwan - Kaohsiung Tel: 886-7-213-7828 Fax: 886-7-330-9305

**Taiwan - Taipei** Tel: 886-2-2508-8600 Fax: 886-2-2508-0102

**Thailand - Bangkok** Tel: 66-2-694-1351 Fax: 66-2-694-1350

#### EUROPE

Austria - Wels Tel: 43-7242-2244-39 Fax: 43-7242-2244-393 Denmark - Copenhagen Tel: 45-4450-2828

Fax: 45-4485-2829 France - Paris Tel: 33-1-69-53-63-20 Fax: 33-1-69-30-90-79

**Germany - Munich** Tel: 49-89-627-144-0 Fax: 49-89-627-144-44

**Italy - Milan** Tel: 39-0331-742611 Fax: 39-0331-466781

Netherlands - Drunen Tel: 31-416-690399 Fax: 31-416-690340

**Spain - Madrid** Tel: 34-91-708-08-90 Fax: 34-91-708-08-91

**UK - Wokingham** Tel: 44-118-921-5869 Fax: 44-118-921-5820

11/29/12