Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Product Status             | Active                                                                    |

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 20MHz                                                                     |

| Connectivity               | UART/USART                                                                |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                     |

| Number of I/O              | 22                                                                        |

| Program Memory Size        | 3.5KB (2K x 14)                                                           |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 64 x 8                                                                    |

| RAM Size                   | 128 × 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 4V ~ 5.5V                                                                 |

| Data Converters            | A/D 5x10b                                                                 |

| Oscillator Type            | External                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 28-SSOP (0.209", 5.30mm Width)                                            |

| Supplier Device Package    | 28-SSOP                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f870t-i-ss |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Address               | Name       | Bit 7                              | Bit 6         | Bit 5         | Bit 4         | Bit 3         | Bit 2           | Bit 1        | Bit 0       | Value on:<br>POR, BOR | Value on<br>all other<br>RESETS <sup>(2)</sup> |

|-----------------------|------------|------------------------------------|---------------|---------------|---------------|---------------|-----------------|--------------|-------------|-----------------------|------------------------------------------------|

| Bank 2                |            |                                    |               |               | •             |               | •               | •            |             | •                     | •                                              |

| 100h <sup>(4)</sup>   | INDF       | Addressing                         | this location | uses conte    | ents of FSR t | o address dat | a memory (n     | ot a physica | l register) | 0000 0000             | 0000 0000                                      |

| 101h                  | TMR0       | Timer0 Mod                         | dule's Regist | er            |               |               |                 |              |             | XXXX XXXX             | uuuu uuuu                                      |

| 102h <sup>(4)</sup>   | PCL        | Program Co                         | ounter's (PC  | ) Least Sigr  | nificant Byte |               |                 |              |             | 0000 0000             | 0000 0000                                      |

| 103h <sup>(4)</sup>   | STATUS     | IRP                                | RP1           | RP0           | то            | PD            | Z               | DC           | С           | 0001 1xxx             | 000q quuu                                      |

| 104h <sup>(4)</sup>   | FSR        | Indirect Dat                       | a Memory A    | ddress Poir   | nter          |               |                 |              |             | XXXX XXXX             | uuuu uuuu                                      |

| 105h                  | _          | Unimpleme                          | nted          |               |               |               |                 |              |             | _                     | —                                              |

| 106h                  | PORTB      | PORTB Da                           | ta Latch whe  | en written: F | ORTB pins     | when read     |                 |              |             | XXXX XXXX             | uuuu uuuu                                      |

| 107h                  | —          | Unimpleme                          | nted          |               |               |               |                 |              |             | _                     | _                                              |

| 108h                  | —          | Unimpleme                          | nted          |               |               |               |                 |              |             | _                     | _                                              |

| 109h                  | —          | Unimpleme                          | nted          |               |               |               |                 |              |             | _                     | _                                              |

| 10Ah <sup>(1,4)</sup> | PCLATH     | _                                  | _             | _             | Write Buffe   | for the upper | r 5 bits of the | Program Co   | ounter      | 0 0000                | 0 0000                                         |

| 10Bh <sup>(4)</sup>   | INTCON     | GIE                                | PEIE          | TOIE          | INTE          | RBIE          | T0IF            | INTF         | RBIF        | 0000 000x             | 0000 000u                                      |

| 10Ch                  | EEDATA     | EEPROM D                           | Data Registe  | r             |               |               |                 |              |             | XXXX XXXX             | uuuu uuuu                                      |

| 10Dh                  | EEADR      | EEPROM A                           | ddress Reg    | ister         |               |               |                 |              |             | XXXX XXXX             | uuuu uuuu                                      |

| 10Eh                  | EEDATH     | — — EEPROM Data Register High Byte |               |               |               |               |                 |              |             | XXXX XXXX             | uuuu uuuu                                      |

| 10Fh                  | EEADRH     | _                                  | _             | _             | EEPROM A      | ddress Regis  | ter High Byte   | )            |             | XXXX XXXX             | uuuu uuuu                                      |

| Bank 3                |            |                                    |               |               |               |               |                 |              |             |                       |                                                |

| 180h <sup>(4)</sup>   | INDF       | Addressing                         | this location | uses conte    | ents of FSR t | o address dat | a memory (n     | ot a physica | l register) | 0000 0000             | 0000 0000                                      |

| 181h                  | OPTION_REG | RBPU                               | INTEDG        | TOCS          | TOSE          | PSA           | PS2             | PS1          | PS0         | 1111 1111             | 1111 1111                                      |

| 182h <sup>(4)</sup>   | PCL        | Program Co                         | ounter's (PC  | ) Least Sigr  | nificant Byte |               |                 |              |             | 0000 0000             | 0000 0000                                      |

| 183h <sup>(4)</sup>   | STATUS     | IRP                                | RP1           | RP0           | то            | PD            | Z               | DC           | С           | 0001 1xxx             | 000q quuu                                      |

| 184h <sup>(4)</sup>   | FSR        | Indirect Dat                       | a Memory A    | ddress Poir   | nter          |               |                 |              |             | XXXX XXXX             | uuuu uuuu                                      |

| 185h                  | _          | Unimpleme                          | nted          |               |               |               |                 |              |             | _                     | —                                              |

| 186h                  | TRISB      | PORTB Da                           | ta Direction  | Register      |               |               |                 |              |             | 1111 1111             | 1111 1111                                      |

| 187h                  | _          | Unimpleme                          | nted          |               |               |               |                 |              |             | _                     | —                                              |

| 188h                  | _          | Unimpleme                          | nted          |               |               |               |                 |              |             | _                     | —                                              |

| 189h                  | _          | Unimpleme                          | nted          |               |               |               |                 |              |             | _                     | —                                              |

| 18Ah <sup>(1,4)</sup> | PCLATH     |                                    | _             | —             | Write Buffe   | for the upper | r 5 bits of the | Program Co   | ounter      | 0 0000                | 0 0000                                         |

| 18Bh <sup>(4)</sup>   | INTCON     | GIE                                | PEIE          | TOIE          | INTE          | RBIE          | T0IF            | INTF         | RBIF        | 0000 000x             | 0000 000u                                      |

| 18Ch                  | EECON1     | EEPGD                              | —             | —             | —             | WRERR         | WREN            | WR           | RD          | x x000                | x u000                                         |

| 18Dh                  | EECON2     | EEPROM (                           | Control Regis | ster2 (not a  | physical reg  | ster)         |                 |              |             |                       |                                                |

| 18Eh                  | —          | Reserved n                         | naintain clea | r             |               |               |                 |              |             | 0000 0000             | 0000 0000                                      |

| 18Fh                  | _          | Reserved n                         | naintain clea | r             |               |               |                 |              |             | 0000 0000             | 0000 0000                                      |

| TABLE 2-1: | SPECIAL FUNCTION REGISTER SUMMARY ( | (CONTINUED) |

|------------|-------------------------------------|-------------|

|------------|-------------------------------------|-------------|

**Note 1:** The upper byte of the program counter is not directly accessible. PCLATH is a holding register for the PC<12:8> whose contents are transferred to the upper byte of the program counter.

2: Other (non Power-up) Resets include external RESET through MCLR and Watchdog Timer Reset.

3: Bits PSPIE and PSPIF are reserved on the 28-pin devices; always maintain these bits clear.

4: These registers can be addressed from any bank.

5: PORTD, PORTE, TRISD and TRISE are not physically implemented on the 28-pin devices, read as '0'.

#### 2.2.2.2 OPTION\_REG Register

bit

bit

bit

bit

bit

bit

The OPTION\_REG register is a readable and writable register, which contains various control bits to configure the TMR0 prescaler/WDT postscaler (single assignable register known also as the prescaler), the External INT interrupt, TMR0 and the weak pull-ups on PORTB.

| Note: | To achieve a 1:1 prescaler assignment for  |

|-------|--------------------------------------------|

|       | the TMR0 register, assign the prescaler to |

|       | the Watchdog Timer.                        |

#### **REGISTER 2-2: OPTION\_REG REGISTER (ADDRESS: 81h,181h)**

| R/W-1                                                                                                                 | R/W-1                                      | R/W-1                                       | R/W-1             | R/W-1            | R/W-1    | R/W-1        | R/W-1 |  |  |  |  |  |

|-----------------------------------------------------------------------------------------------------------------------|--------------------------------------------|---------------------------------------------|-------------------|------------------|----------|--------------|-------|--|--|--|--|--|

| RBPL                                                                                                                  | INTED                                      | G TOCS                                      | T0SE              | PSA              | PS2      | PS1          | PS0   |  |  |  |  |  |

| bit 7                                                                                                                 |                                            |                                             |                   |                  |          |              | bit   |  |  |  |  |  |

| RBPU:                                                                                                                 | PORTB Pull                                 | -up Enable b                                | it                |                  |          |              |       |  |  |  |  |  |

|                                                                                                                       |                                            | are disabled<br>are enabled                 |                   | l port latch val | Jes      |              |       |  |  |  |  |  |

| INTEDG: Interrupt Edge Select bit                                                                                     |                                            |                                             |                   |                  |          |              |       |  |  |  |  |  |

| <ul> <li>1 = Interrupt on rising edge of RB0/INT pin</li> <li>0 = Interrupt on falling edge of RB0/INT pin</li> </ul> |                                            |                                             |                   |                  |          |              |       |  |  |  |  |  |

| TOCS: 1                                                                                                               | <b>TOCS</b> : TMR0 Clock Source Select bit |                                             |                   |                  |          |              |       |  |  |  |  |  |

|                                                                                                                       | L = Transition on RA4/T0CKI pin            |                                             |                   |                  |          |              |       |  |  |  |  |  |

|                                                                                                                       |                                            | on cycle cloc                               | . ,               |                  |          |              |       |  |  |  |  |  |

| T0SE: 7                                                                                                               | MR0 Sourc                                  | e Edge Selec                                | t bit             |                  |          |              |       |  |  |  |  |  |

|                                                                                                                       |                                            | gh-to-low trar<br>w-to-high trar            |                   |                  |          |              |       |  |  |  |  |  |

| PSA: P                                                                                                                | escaler Ass                                | ignment bit                                 |                   |                  |          |              |       |  |  |  |  |  |

|                                                                                                                       |                                            | igned to the \<br>igned to the <sup>-</sup> |                   | le               |          |              |       |  |  |  |  |  |

| PS2:PS                                                                                                                | 0: Prescale                                | Rate Select                                 | bits              |                  |          |              |       |  |  |  |  |  |

|                                                                                                                       | Bit Value                                  | TMR0 Rate                                   | WDT Rate          |                  |          |              |       |  |  |  |  |  |

|                                                                                                                       | 000<br>001<br>010                          | 1:2<br>1:4<br>1:8                           | 1:1<br>1:2<br>1:4 |                  |          |              |       |  |  |  |  |  |

|                                                                                                                       | 011                                        | 1:16                                        | 1:8               |                  |          |              |       |  |  |  |  |  |

|                                                                                                                       | 100                                        | 1:32                                        | 1:16              |                  |          |              |       |  |  |  |  |  |

|                                                                                                                       | 101                                        | 1:64                                        | 1:32<br>1:64      |                  |          |              |       |  |  |  |  |  |

|                                                                                                                       | 110<br>111                                 | 1 : 128<br>1 : 256                          | 1:128             |                  |          |              |       |  |  |  |  |  |

|                                                                                                                       |                                            | 1.200                                       | •                 |                  |          |              |       |  |  |  |  |  |

| Legend                                                                                                                | :                                          |                                             |                   |                  |          |              |       |  |  |  |  |  |

| R = Rea                                                                                                               | adable bit                                 | VV =                                        | Writable bit      | U = Unimp        | lemented | bit, read as | '0'   |  |  |  |  |  |

| - n = Value at POR (1' = Bit is set (0' = Bit is cleared x = Bit is unknown                                           |                                            |                                             |                   |                  |          |              |       |  |  |  |  |  |

Write operations have two control bits, WR and WREN, and two status bits, WRERR and EEIF. The WREN bit is used to enable or disable the write operation. When WREN is clear, the write operation will be disabled. Therefore, the WREN bit must be set before executing a write operation. The WR bit is used to initiate the write operation. It also is automatically cleared at the end of the write operation. The interrupt flag EEIF is used to determine when the memory write completes. This flag must be cleared in software before setting the WR bit. For EEPROM data memory, once the WREN bit and the WR bit have been set, the desired memory address in EEADR will be erased, followed by a write of the data in EEDATA. This operation takes place in parallel with the microcontroller continuing to execute normally. When the write is complete, the EEIF flag bit will be set. For program memory, once the WREN bit and the WR bit have been set, the microcontroller will cease to execute instructions. The desired memory location pointed to by EEADRH:EEADR will be erased. Then, the data value in EEDATH:EEDATA will be programmed. When complete, the EEIF flag bit will be set and the microcontroller will continue to execute code.

The WRERR bit is used to indicate when the PIC16F870/871 devices have been reset during a write operation. WRERR should be cleared after Power-on Reset. Thereafter, it should be checked on any other RESET. The WRERR bit is set when a write operation is interrupted by a MCLR Reset, or a WDT Time-out Reset, during normal operation. In these situations, following a RESET, the user should check the WRERR bit and rewrite the memory location, if set. The contents of the data registers, address registers and EEPGD bit are not affected by either MCLR Reset, or WDT Time-out Reset, during normal operation.

#### REGISTER 3-1: EECON1 REGISTER (ADDRESS: 18Ch)

- n = Value at POR

|         | R/W-x                                                                                   | U-0                                                                      | U-0         | U-0          | R/W-x           | R/W-0       | R/S-0       | R/S-0       |  |  |  |  |  |

|---------|-----------------------------------------------------------------------------------------|--------------------------------------------------------------------------|-------------|--------------|-----------------|-------------|-------------|-------------|--|--|--|--|--|

|         | EEPGD                                                                                   | _                                                                        | _           | _            | WRERR           | WREN        | WR          | RD          |  |  |  |  |  |

|         | bit 7                                                                                   |                                                                          |             |              | •               |             |             | bit 0       |  |  |  |  |  |

|         |                                                                                         |                                                                          |             |              |                 |             |             |             |  |  |  |  |  |

| bit 7   | EEPGD: Program/Data EEPROM Select bit                                                   |                                                                          |             |              |                 |             |             |             |  |  |  |  |  |

|         | 1 = Access                                                                              | 1 = Accesses program memory                                              |             |              |                 |             |             |             |  |  |  |  |  |

|         | 0 = Accesses data memory                                                                |                                                                          |             |              |                 |             |             |             |  |  |  |  |  |

|         | (This bit cannot be changed while a read or write operation is in progress.)            |                                                                          |             |              |                 |             |             |             |  |  |  |  |  |

| bit 6-4 | Unimplemented: Read as '0'                                                              |                                                                          |             |              |                 |             |             |             |  |  |  |  |  |

| bit 3   | WRERR: EEPROM Error Flag bit                                                            |                                                                          |             |              |                 |             |             |             |  |  |  |  |  |

|         | 1 = A write operation is prematurely terminated (any MCLR Reset or any WDT Reset during |                                                                          |             |              |                 |             |             |             |  |  |  |  |  |

|         |                                                                                         | l operation)                                                             |             |              |                 |             |             |             |  |  |  |  |  |

|         | 0 = The w                                                                               | rite operatio                                                            | n complete  | d            |                 |             |             |             |  |  |  |  |  |

| bit 2   | WREN: EE                                                                                | PROM Writ                                                                | e Enable bi | t            |                 |             |             |             |  |  |  |  |  |

|         |                                                                                         | write cycles                                                             |             |              |                 |             |             |             |  |  |  |  |  |

|         | 0 = Inhibits                                                                            | write to the                                                             | EEPROM      |              |                 |             |             |             |  |  |  |  |  |

| bit 1   | WR: Write                                                                               | Control bit                                                              |             |              |                 |             |             |             |  |  |  |  |  |

|         |                                                                                         | -                                                                        |             |              | by hardware on  | ce write is | complete.   | The WR bit  |  |  |  |  |  |

|         |                                                                                         |                                                                          | ,           | n software.) |                 |             |             |             |  |  |  |  |  |

|         |                                                                                         | cycle to the                                                             | EEPROM IS   | s complete   |                 |             |             |             |  |  |  |  |  |

| bit 0   | RD: Read (                                                                              |                                                                          |             |              |                 |             |             |             |  |  |  |  |  |

|         |                                                                                         | s an EEPR<br>d) in softwa                                                | •           | RD is cleare | ed in hardware. | The RD bi   | t can only  | be set (not |  |  |  |  |  |

|         | 0 = Does not initiate an EEPROM read                                                    |                                                                          |             |              |                 |             |             |             |  |  |  |  |  |

|         | Legend:                                                                                 |                                                                          |             |              |                 |             |             |             |  |  |  |  |  |

|         | •                                                                                       | hla hit                                                                  | 10/ 1/      | Vritable hit |                 | omontod L   | t road as f | 0,          |  |  |  |  |  |

|         | к = кeada                                                                               | R = Readable bit $W = Writable bit$ $U = Unimplemented bit, read as '0'$ |             |              |                 |             |             |             |  |  |  |  |  |

'1' = Bit is set

x = Bit is unknown

'0' = Bit is cleared

## PIC16F870/871

| REGISTER 4-1: | TRISE RE                                                                      | GISTER (                                                                                                                                                    | ADDRESS       | : 89h)            |                                                                           |             |                |       |  |  |  |  |  |  |

|---------------|-------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|-------------------|---------------------------------------------------------------------------|-------------|----------------|-------|--|--|--|--|--|--|

|               | R-0                                                                           | R-0                                                                                                                                                         | R/W-0         | R/W-0             | U-0                                                                       | R/W-1       | R/W-1          | R/W-1 |  |  |  |  |  |  |

|               | IBF                                                                           | OBF                                                                                                                                                         | IBOV          | PSPMODE           |                                                                           | Bit2        | Bit1           | Bit0  |  |  |  |  |  |  |

|               | bit 7                                                                         |                                                                                                                                                             |               |                   |                                                                           |             |                | bit 0 |  |  |  |  |  |  |

|               |                                                                               |                                                                                                                                                             |               |                   |                                                                           |             |                |       |  |  |  |  |  |  |

| bit 7         |                                                                               | lave Port Si<br>Buffer Full S                                                                                                                               |               | ol Bits           |                                                                           |             |                |       |  |  |  |  |  |  |

|               | 1 = A word                                                                    |                                                                                                                                                             | eceived and   | d is waiting to b | e read by t                                                               | he CPU      |                |       |  |  |  |  |  |  |

| bit 6         | OBF: Outp                                                                     | <b>OBF</b> : Output Buffer Full Status bit                                                                                                                  |               |                   |                                                                           |             |                |       |  |  |  |  |  |  |

|               |                                                                               | <ul> <li>1 = The output buffer still holds a previously written word</li> <li>0 = The output buffer has been read</li> </ul>                                |               |                   |                                                                           |             |                |       |  |  |  |  |  |  |

| bit 5         | bit 5 <b>IBOV</b> : Input Buffer Overflow Detect bit (in Microprocessor mode) |                                                                                                                                                             |               |                   |                                                                           |             |                |       |  |  |  |  |  |  |

|               | (must                                                                         | <ul> <li>1 = A write occurred when a previously input word has not been read<br/>(must be cleared in software)</li> <li>0 = No overflow occurred</li> </ul> |               |                   |                                                                           |             |                |       |  |  |  |  |  |  |

| bit 4         | PSPMODE: Parallel Slave Port Mode Select bit                                  |                                                                                                                                                             |               |                   |                                                                           |             |                |       |  |  |  |  |  |  |

|               | 1 = Parallel Slave Port mode                                                  |                                                                                                                                                             |               |                   |                                                                           |             |                |       |  |  |  |  |  |  |

|               |                                                                               | al Purpose I                                                                                                                                                |               |                   |                                                                           |             |                |       |  |  |  |  |  |  |

| bit 3         |                                                                               | ented: Rea                                                                                                                                                  |               |                   |                                                                           |             |                |       |  |  |  |  |  |  |

| <b>h</b> it 0 |                                                                               | ata Directio                                                                                                                                                |               |                   |                                                                           |             |                |       |  |  |  |  |  |  |

| bit 2         |                                                                               | tion Control                                                                                                                                                | bit for pin r | RE2/CS/AN7        |                                                                           |             |                |       |  |  |  |  |  |  |

|               | 1 = Input 0 = Output                                                          | 1 = Input<br>0 = Output                                                                                                                                     |               |                   |                                                                           |             |                |       |  |  |  |  |  |  |

| bit 1         | -                                                                             |                                                                                                                                                             | bit for pin F | RE1/WR/AN6        |                                                                           |             |                |       |  |  |  |  |  |  |

|               | 1 = Input<br>0 = Output                                                       | t                                                                                                                                                           |               |                   |                                                                           |             |                |       |  |  |  |  |  |  |

| bit 0         | Bit0: Direc                                                                   | tion Contro                                                                                                                                                 | bit for pin F | RE0/RD/AN5        |                                                                           |             |                |       |  |  |  |  |  |  |

|               | 1 = Input                                                                     |                                                                                                                                                             |               |                   |                                                                           |             |                |       |  |  |  |  |  |  |

|               | 0 = Output                                                                    | t                                                                                                                                                           |               |                   |                                                                           |             |                |       |  |  |  |  |  |  |

|               | Legend:                                                                       |                                                                                                                                                             |               |                   |                                                                           |             |                |       |  |  |  |  |  |  |

|               | R = Reada                                                                     | able bit                                                                                                                                                    | W = \         | Vritable bit      | U = Unimr                                                                 | plemented b | oit, read as ' | 0'    |  |  |  |  |  |  |

|               | -n = Value                                                                    |                                                                                                                                                             |               | Bit is set        | '0' = Bit is                                                              |             | x = Bit is u   |       |  |  |  |  |  |  |

|               |                                                                               |                                                                                                                                                             |               |                   | -11 = Value at FOR $1 = Bit is set 0 = Bit is cleared x = Bit is unknown$ |             |                |       |  |  |  |  |  |  |

#### **TIMER1 MODULE** 6.0

The Timer1 module is a 16-bit timer/counter consisting of two 8-bit registers (TMR1H and TMR1L), which are readable and writable. The TMR1 register pair (TMR1H:TMR1L) increments from 0000h to FFFFh and rolls over to 0000h. The TMR1 interrupt, if enabled, is generated on overflow, which is latched in interrupt flag bit, TMR1IF (PIR1<0>). This interrupt can be enabled/disabled by setting/clearing TMR1 interrupt enable bit, TMR1IE (PIE1<0>).

Timer1 can operate in one of two modes:

- As a timer

- · As a counter

The Operating mode is determined by the clock select bit, TMR1CS (T1CON<1>).

In Timer mode, Timer1 increments every instruction cycle. In Counter mode, it increments on every rising edge of the external clock input.

Timer1 can be enabled/disabled by setting/clearing control bit, TMR1ON (T1CON<0>).

Timer1 also has an internal "RESET input". This RESET can be generated by either of the two CCP modules (Section 8.0). Register 6-1 shows the Timer1 control register.

When the Timer1 oscillator is enabled (T1OSCEN is set), the RC1/T1OSI and RC0/T1OSO/T1CKI pins become inputs. That is, the TRISC<1:0> value is ignored, and these pins read as '0'.

Additional information on timer modules is available in the PIC<sup>®</sup> Mid-Range MCU Family Reference Manual (DS33023).

| ER 6-1: | I1CON: I               | 11CON: HMER1 CONTROL REGISTER (ADDRESS: 10h)                                                |                |                |                                         |           |                |        |  |  |  |  |  |

|---------|------------------------|---------------------------------------------------------------------------------------------|----------------|----------------|-----------------------------------------|-----------|----------------|--------|--|--|--|--|--|

|         | U-0                    | U-0                                                                                         | R/W-0          | R/W-0          | R/W-0                                   | R/W-0     | R/W-0          | R/W-0  |  |  |  |  |  |

|         | —                      | —                                                                                           | T1CKPS1        | T1CKPS0        | T1OSCEN                                 | T1SYNC    | TMR1CS         | TMR10N |  |  |  |  |  |

|         | bit 7                  |                                                                                             |                |                |                                         |           |                | bit 0  |  |  |  |  |  |

|         |                        |                                                                                             |                |                |                                         |           |                |        |  |  |  |  |  |

| bit 7-6 | Unimplem               | ented: Rea                                                                                  | ad as '0'      |                |                                         |           |                |        |  |  |  |  |  |

| bit 5-4 | T1CKPS1:               | T1CKPS0:                                                                                    | Timer1 Inpu    | t Clock Pres   | cale Select bit                         | S         |                |        |  |  |  |  |  |

|         | -                      | rescale valu                                                                                |                |                |                                         |           |                |        |  |  |  |  |  |

|         |                        | rescale valu                                                                                |                |                |                                         |           |                |        |  |  |  |  |  |

|         |                        | rescale valı<br>rescale valı                                                                |                |                |                                         |           |                |        |  |  |  |  |  |

| bit 3   |                        | <b>TIOSCEN</b> : Timer1 Oscillator Enable Control bit                                       |                |                |                                         |           |                |        |  |  |  |  |  |

|         |                        | 1 = Oscillator is enabled                                                                   |                |                |                                         |           |                |        |  |  |  |  |  |

|         | 0 = Oscilla            | 0 = Oscillator is shut-off (the oscillator inverter is turned off to eliminate power drain) |                |                |                                         |           |                |        |  |  |  |  |  |

| bit 2   | T1SYNC: 7              | Fimer1 Exte                                                                                 | ernal Clock Ir | nput Synchro   | onization Contr                         | ol bit    |                |        |  |  |  |  |  |

|         | When TMF               |                                                                                             |                |                |                                         |           |                |        |  |  |  |  |  |

|         |                        |                                                                                             | e external cl  |                |                                         |           |                |        |  |  |  |  |  |

|         | 0 = Synchr<br>When TMF |                                                                                             | nal clock inp  | out            |                                         |           |                |        |  |  |  |  |  |

|         |                        |                                                                                             | ner1 uses th   | e internal clo | ock when TMR                            | 1CS = 0.  |                |        |  |  |  |  |  |

| bit 1   |                        | •                                                                                           | ck Source Se   |                |                                         |           |                |        |  |  |  |  |  |

|         |                        |                                                                                             |                |                | (I (on the rising                       | edae)     |                |        |  |  |  |  |  |

|         |                        | l clock (Fo                                                                                 |                |                | (************************************** | 5         |                |        |  |  |  |  |  |

| bit 0   | TMR1ON:                | Timer1 On                                                                                   | bit            |                |                                         |           |                |        |  |  |  |  |  |

|         | 1 = Enable             | s Timer1                                                                                    |                |                |                                         |           |                |        |  |  |  |  |  |

|         | 0 = Stops 7            | Timer1                                                                                      |                |                |                                         |           |                |        |  |  |  |  |  |

|         |                        |                                                                                             |                |                |                                         |           |                |        |  |  |  |  |  |

|         | Legend:                |                                                                                             |                |                |                                         |           |                |        |  |  |  |  |  |

|         | R = Reada              | ble bit                                                                                     | W = V          | Vritable bit   | U = Unimpl                              | emented b | it, read as '( | )'     |  |  |  |  |  |

|         | - n = Value            | at POR                                                                                      | '1' = E        | Bit is set     | '0' = Bit is c                          | leared    | x = Bit is ur  | nknown |  |  |  |  |  |

#### T1CON: TIMER1 CONTROL REGISTER (ADDRESS: 10b) **REGISTER 6-1:**

#### 6.4 Timer1 Operation in Asynchronous Counter Mode

If control bit  $\overline{T1SYNC}$  (T1CON<2>) is set, the external clock input is not synchronized. The timer continues to increment asynchronous to the internal phase clocks. The timer will continue to run during SLEEP and can generate an interrupt-on-overflow, which will wake-up the processor. However, special precautions in software are needed to read/write the timer (Section 6.4.1).

In Asynchronous Counter mode, Timer1 cannot be used as a time base for capture or compare operations.

#### 6.4.1 READING AND WRITING TIMER1 IN ASYNCHRONOUS COUNTER MODE

Reading TMR1H or TMR1L while the timer is running from an external asynchronous clock, will ensure a valid read (taken care of in hardware). However, the user should keep in mind that reading the 16-bit timer in two 8-bit values itself, poses certain problems, since the timer may overflow between the reads.

For writes, it is recommended that the user simply stop the timer and write the desired values. A write contention may occur by writing to the timer registers, while the register is incrementing. This may produce an unpredictable value in the timer register.

Reading the 16-bit value requires some care. Examples 12-2 and 12-3 in the PIC<sup>®</sup> Mid-Range MCU Family Reference Manual (DS33023) show how to read and write Timer1 when it is running in Asynchronous mode.

#### 6.5 Timer1 Oscillator

A crystal oscillator circuit is built-in between pins T1OSI (input) and T1OSO (amplifier output). It is enabled by setting control bit, T1OSCEN (T1CON<3>). The oscillator is a low power oscillator, rated up to 200 kHz. It will continue to run during SLEEP. It is primarily intended for use with a 32 kHz crystal. Table 6-1 shows the capacitor selection for the Timer1 oscillator.

The Timer1 oscillator is identical to the LP oscillator. The user must provide a software time delay to ensure proper oscillator start-up.

### TABLE 6-1:CAPACITOR SELECTION FOR<br/>THE TIMER1 OSCILLATOR

| Osc Typ                                    | е                             | Freq.                                                                         | C2                                                                                                       |                                    |  |  |  |  |  |  |

|--------------------------------------------|-------------------------------|-------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|------------------------------------|--|--|--|--|--|--|

| LP                                         |                               | 32 kHz                                                                        | 33 pF                                                                                                    | 33 pF                              |  |  |  |  |  |  |

|                                            |                               | 100 kHz                                                                       | 15 pF                                                                                                    | 15 pF                              |  |  |  |  |  |  |

|                                            |                               | 200 kHz 15 pF                                                                 |                                                                                                          | 15 pF                              |  |  |  |  |  |  |

| These values are for design guidance only. |                               |                                                                               |                                                                                                          |                                    |  |  |  |  |  |  |

| Crystals Tested:                           |                               |                                                                               |                                                                                                          |                                    |  |  |  |  |  |  |

| 32.768 kl                                  | Ηz                            | Epson C-00                                                                    | ± 20 PPM                                                                                                 |                                    |  |  |  |  |  |  |

| 100 kH:                                    | Z                             | Epson C-2 100.00 KC-P ± 20 PPN                                                |                                                                                                          |                                    |  |  |  |  |  |  |

| 200 kH:                                    | Z                             | STD XTL                                                                       | ± 20 PPM                                                                                                 |                                    |  |  |  |  |  |  |

| Note 1:<br>2:                              | of<br>tim<br>Sii<br>ch<br>res | oscillator, but<br>ne.<br>nce each reso<br>aracteristics, t<br>sonator/crysta | nce increases<br>also increases<br>nator/crystal h<br>he user should<br>I manufactured<br>es of external | as its own<br>d consult the<br>for |  |  |  |  |  |  |

#### 6.6 Resetting Timer1 Using a CCP Trigger Output

If the CCP1 module is configured in Compare mode to generate a "special event trigger" (CCP1M3:CCP1M0 = 1011), this signal will reset Timer1.

| Note: | The special event triggers from the CCP1 |  |  |  |  |  |  |  |  |  |  |

|-------|------------------------------------------|--|--|--|--|--|--|--|--|--|--|

|       | module will not set interrupt flag bit   |  |  |  |  |  |  |  |  |  |  |

|       | TMR1IF (PIR1<0>).                        |  |  |  |  |  |  |  |  |  |  |

Timer1 must be configured for either Timer or Synchronized Counter mode to take advantage of this feature. If Timer1 is running in Asynchronous Counter mode, this RESET operation may not work.

In the event that a write to Timer1 coincides with a special event trigger from CCP1, the write will take precedence.

In this mode of operation, the CCPRH:CCPRL register pair effectively becomes the period register for Timer1.

#### 8.4.3 SETUP FOR PWM OPERATION

The following steps should be taken when configuring the CCP module for PWM operation:

- 1. Set the PWM period by writing to the PR2 register.

- 2. Set the PWM duty cycle by writing to the CCPR1L register and CCP1CON<5:4> bits.

- 3. Make the CCP1 pin an output by clearing the TRISC<2> bit.

- 4. Set the TMR2 prescale value and enable Timer2 by writing to T2CON.

- 5. Configure the CCP1 module for PWM operation.

| PWM Frequency              | 1.22 kHz | 4.88 kHz | 19.53 kHz | 78.12kHz | 156.3 kHz | 208.3 kHz |

|----------------------------|----------|----------|-----------|----------|-----------|-----------|

| Timer Prescaler (1, 4, 16) | 16       | 4        | 1         | 1        | 1         | 1         |

| PR2 Value                  | 0xFFh    | 0xFFh    | 0xFFh     | 0x3Fh    | 0x1Fh     | 0x17h     |

| Maximum Resolution (bits)  | 10       | 10       | 10        | 8        | 7         | 6.5       |

#### TABLE 8-2: EXAMPLE PWM FREQUENCIES AND RESOLUTIONS AT 20 MHz

#### TABLE 8-3: REGISTERS ASSOCIATED WITH CAPTURE, COMPARE, AND TIMER1

| Address                | Name    | Bit 7                | Bit 6                               | Bit 5        | Bit 4        | Bit 3         | Bit 2       | Bit 1       | Bit 1 Bit 0 |      | Value on:<br>POR, BOR |      |      |  | ie on<br>other<br>SETS |

|------------------------|---------|----------------------|-------------------------------------|--------------|--------------|---------------|-------------|-------------|-------------|------|-----------------------|------|------|--|------------------------|

| 0Bh,8Bh,<br>10Bh, 18Bh | INTCON  | GIE                  | PEIE                                | TOIE         | INTE         | RBIE          | TOIF        | INTF        | RBIF        | 0000 | 000x                  | 0000 | 000u |  |                        |

| 0Ch                    | PIR1    | PSPIF <sup>(1)</sup> | ADIF                                | RCIF         | TXIF         | —             | CCP1IF      | TMR2IF      | TMR1IF      | 0000 | -000                  | 0000 | -000 |  |                        |

| 8Ch                    | PIE1    | PSPIE <sup>(1)</sup> | ADIE                                | RCIE         | TXIE         | _             | CCP1IE      | TMR2IE      | TMR1IE      | 0000 | -000                  | 0000 | -000 |  |                        |

| 87h                    | TRISC   | PORTC [              | Data Dire                           | ection Regis | ster         |               |             |             |             | 1111 | 1111                  | 1111 | 1111 |  |                        |

| 0Eh                    | TMR1L   | Holding F            | Register                            | for the Leas | st Significa | nt Byte of th | e 16-bit TN | /IR1 Regist | ter         | xxxx | xxxx                  | uuuu | uuuu |  |                        |

| 0Fh                    | TMR1H   | Holding F            | Register                            | for the Mos  | t Significan | t Byte of the | e 16-bit TM | IR1 Regist  | er          | xxxx | xxxx                  | uuuu | uuuu |  |                        |

| 10h                    | T1CON   |                      | _                                   | T1CKPS1      | T1CKPS0      | T1OSCEN       | T1SYNC      | TMR1CS      | TMR1ON      | 00   | 0000                  | uu   | uuuu |  |                        |

| 15h                    | CCPR1L  | Capture/0            | Compare                             | e/PWM Reg    | jister1 (LSE | 3)            |             |             |             | xxxx | xxxx                  | uuuu | uuuu |  |                        |

| 16h                    | CCPR1H  | Capture/0            | Capture/Compare/PWM Register1 (MSB) |              |              |               |             |             |             | xxxx | xxxx                  | uuuu | uuuu |  |                        |

| 17h                    | CCP1CON | —                    | —                                   | CCP1X        | CCP1Y        | CCP1M3        | CCP1M2      | CCP1M1      | CCP1M0      | 00   | 0000                  | 00   | 0000 |  |                        |

Legend: x = unknown, u = unchanged, - = unimplemented, read as '0'. Shaded cells are not used by Capture and Timer1.

Note 1: The PSP is not implemented on the PIC16F870; always maintain these bits clear.

## 9.1 USART Baud Rate Generator (BRG)

The BRG supports both the Asynchronous and Synchronous modes of the USART. It is a dedicated 8-bit baud rate generator. The SPBRG register controls the period of a free running 8-bit timer. In Asynchronous mode, bit BRGH (TXSTA<2>) also controls the baud rate. In Synchronous mode, bit BRGH is ignored. Table 9-1 shows the formula for computation of the baud rate for different USART modes which only apply in Master mode (internal clock).

Given the desired baud rate and Fosc, the nearest integer value for the SPBRG register can be calculated using the formula in Table 9-1. From this, the error in baud rate can be determined.

It may be advantageous to use the high baud rate (BRGH = 1), even for slower baud clocks. This is because the FOSC/(16(X + 1)) equation can reduce the baud rate error in some cases.

Writing a new value to the SPBRG register causes the BRG timer to be reset (or cleared). This ensures the BRG does not wait for a timer overflow before outputting the new baud rate.

#### 9.1.1 SAMPLING

The data on the RC7/RX/DT pin is sampled three times by a majority detect circuit to determine if a high or a low level is present at the RX pin.

#### TABLE 9-1: BAUD RATE FORMULA

| SYNC | BRGH = 0 (Low Speed)                      | BRGH = 1 (High Speed)      |

|------|-------------------------------------------|----------------------------|

| 0    | (Asynchronous) Baud Rate = Fosc/(64(X+1)) | Baud Rate = Fosc/(16(X+1)) |

| 1    | (Synchronous) Baud Rate = FOSC/(4(X+1))   | N/A                        |

|      |                                           |                            |

Legend: X = value in SPBRG (0 to 255)

#### TABLE 9-2: REGISTERS ASSOCIATED WITH BAUD RATE GENERATOR

| Address | Name  | Bit 7                             | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Value on:<br>POR, BOR | Value on<br>all other<br>RESETS |

|---------|-------|-----------------------------------|-------|-------|-------|-------|-------|-------|-------|-----------------------|---------------------------------|

| 98h     | TXSTA | CSRC                              | TX9   | TXEN  | SYNC  |       | BRGH  | TRMT  | TX9D  | 0000 -010             | 0000 -010                       |

| 18h     | RCSTA | SPEN                              | RX9   | SREN  | CREN  | ADDEN | FERR  | OERR  | RX9D  | 0000 000x             | x000 000x                       |

| 99h     | SPBRG | PBRG Baud Rate Generator Register |       |       |       |       |       |       |       | 0000 0000             | 0000 0000                       |

Legend: x = unknown, - = unimplemented, read as '0'. Shaded cells are not used by the BRG.

#### 9.2 USART Asynchronous Mode

In this mode, the USART uses standard non-return-tozero (NRZ) format (one START bit, eight or nine data bits, and one STOP bit). The most common data format is 8-bits. An on-chip, dedicated, 8-bit baud rate generator can be used to derive standard baud rate frequencies from the oscillator. The USART transmits and receives the LSb first. The transmitter and receiver are functionally independent, but use the same data format and baud rate. The baud rate generator produces a clock, either x16 or x64 of the bit shift rate, depending on bit BRGH (TXSTA<2>). Parity is not supported by the hardware, but can be implemented in software (and stored as the ninth data bit). Asynchronous mode is stopped during SLEEP.

Asynchronous mode is selected by clearing bit SYNC (TXSTA<4>).

The USART Asynchronous module consists of the following important elements:

- Baud Rate Generator

- · Sampling Circuit

- Asynchronous Transmitter

- Asynchronous Receiver

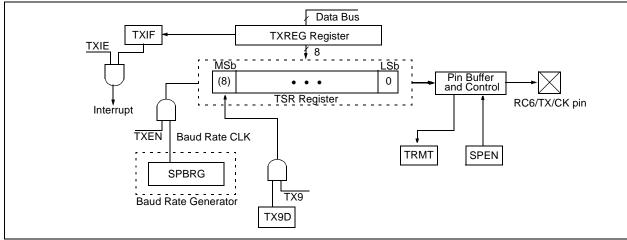

#### 9.2.1 USART ASYNCHRONOUS TRANSMITTER

The USART transmitter block diagram is shown in Figure 9-1. The heart of the transmitter is the Transmit (Serial) Shift register (TSR). The Shift register obtains its data from the read/write transmit buffer, TXREG. The TXREG register is loaded with data in software. The TSR register is not loaded until the STOP bit has been transmitted from the previous load. As soon as the STOP bit is transmitted, the TSR is loaded with new data from the TXREG register (if available). Once the TXREG register transfers the data to the TSR register (occurs in one TCY), the TXREG register is empty and flag bit TXIF (PIR1<4>) is set. This interrupt can be

enabled/disabled by setting/clearing enable bit TXIE (PIE1<4>). Flag bit TXIF will be set, regardless of the state of enable bit TXIE and cannot be cleared in software. It will reset only when new data is loaded into the TXREG register. While flag bit TXIF indicates the status of the TXREG register, another bit, TRMT (TXSTA<1>), shows the status of the TSR register. Status bit TRMT is a read only bit, which is set when the TSR register is empty. No interrupt logic is tied to this bit, so the user has to poll this bit in order to determine if the TSR register is empty.

| Note 1: | The TSR register is not mapped in data memory, so it is not available to the user.  |

|---------|-------------------------------------------------------------------------------------|

| 2:      | Flag bit TXIF is set when enable bit TXEN is set. TXIF is cleared by loading TXREG. |

Transmission is enabled by setting enable bit TXEN (TXSTA<5>). The actual transmission will not occur until the TXREG register has been loaded with data and the baud rate generator (BRG) has produced a shift clock (Figure 9-2). The transmission can also be started by first loading the TXREG register and then setting enable bit TXEN. Normally, when transmission is first started, the TSR register is empty. At that point, transfer to the TXREG register will result in an immediate transfer to TSR, resulting in an empty TXREG. A back-to-back transfer is thus possible (Figure 9-3). Clearing enable bit TXEN during a transmission will cause the transmission to be aborted and will reset the transmitter. As a result, the RC6/TX/CK pin will revert to hi-impedance.

In order to select 9-bit transmission, transmit bit TX9 (TXSTA<6>) should be set and the ninth bit should be written to TX9D (TXSTA<0>). The ninth bit must be written before writing the 8-bit data to the TXREG register. This is because a data write to the TXREG register can result in an immediate transfer of the data to the TSR register (if the TSR is empty). In such a case, an incorrect ninth data bit may be loaded in the TSR register.

#### FIGURE 9-1: USART TRANSMIT BLOCK DIAGRAM

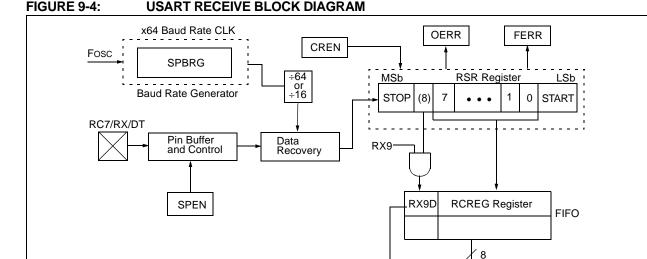

#### 9.2.2 USART ASYNCHRONOUS RECEIVER

The receiver block diagram is shown in Figure 9-4. The data is received on the RC7/RX/DT pin and drives the data recovery block. The data recovery block is actually a high speed shifter, operating at x16 times the baud rate; whereas, the main receive serial shifter operates at the bit rate or at Fosc.

Once Asynchronous mode is selected, reception is enabled by setting bit CREN (RCSTA<4>).

The heart of the receiver is the Receive (Serial) Shift register (RSR). After sampling the STOP bit, the received data in the RSR is transferred to the RCREG register (if it is empty). If the transfer is complete, flag bit RCIF (PIR1<5>) is set. The actual interrupt can be enabled/disabled by setting/clearing enable bit RCIE (PIE1<5>). Flag bit RCIF is a read only bit, which is cleared by the hardware. It is cleared when the RCREG register has been read and is empty. The RCREG is a double-buffered register (i.e., it is a two-deep FIFO). It is possible for two bytes of data to be received and transferred to the RCREG FIFO and a third byte to begin shifting to the RSR register. On the detection of the STOP bit of the third byte, if the RCREG register is still full, the overrun error bit OERR (RCSTA<1>) will be set. The word in the RSR will be lost. The RCREG register can be read twice to retrieve the two bytes in the FIFO. Overrun bit OERR has to be cleared in software. This is done by resetting the receive logic (CREN is cleared and then set). If bit OERR is set, transfers from the RSR register to the RCREG register are inhibited, and no further data will be received. It is therefore, essential to clear error bit OERR if it is set. Framing error bit FERR (RCSTA<2>) is set if a STOP bit is detected as clear. Bit FERR and the 9th receive bit are buffered the same way as the receive data. Reading the RCREG will load bits RX9D and FERR with new values, therefore, it is essential for the user to read the RCSTA register before reading the RCREG register in order not to lose the old FERR and RX9D information.

Data Bus

Interrupt

#### FIGURE 9-5:

#### **ASYNCHRONOUS RECEPTION**

RCIF

RCIE

#### 9.4 USART Synchronous Slave Mode

Synchronous Slave mode differs from the Master mode in the fact that the shift clock is supplied externally at the RC6/TX/CK pin (instead of being supplied internally in Master mode). This allows the device to transfer or receive data while in SLEEP mode. Slave mode is entered by clearing bit CSRC (TXSTA<7>).

#### 9.4.1 USART SYNCHRONOUS SLAVE TRANSMIT

The operation of the Synchronous Master and Slave modes is identical, except in the case of the SLEEP mode.

If two words are written to the TXREG and then the SLEEP instruction is executed, the following will occur:

- a) The first word will immediately transfer to the TSR register and transmit.

- b) The second word will remain in TXREG register.

- c) Flag bit TXIF will not be set.

- d) When the first word has been shifted out of TSR, the TXREG register will transfer the second word to the TSR and flag bit TXIF will now be set.

- e) If enable bit TXIE is set, the interrupt will wake the chip from SLEEP and if the global interrupt is enabled, the program will branch to the interrupt vector (0004h).

When setting up a Synchronous Slave Transmission, follow these steps:

- 1. Enable the synchronous slave serial port by setting bits SYNC and SPEN and clearing bit CSRC.

- 2. Clear bits CREN and SREN.

- 3. If interrupts are desired, then set enable bit TXIE.

- 4. If 9-bit transmission is desired, then set bit TX9.

- 5. Enable the transmission by setting enable bit TXEN.

- 6. If 9-bit transmission is selected, the ninth bit should be loaded in bit TX9D.

- 7. Start transmission by loading data to the TXREG register.

- 8. If using interrupts, ensure that GIE and PEIE (bits 7 and 6) of the INTCON register are set.

| Address                | Name                               | Bit 7                   | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2  | Bit 1  | Bit 0     | Value on:<br>POR, BOR | Value on<br>all other<br>RESETS |

|------------------------|------------------------------------|-------------------------|-------|-------|-------|-------|--------|--------|-----------|-----------------------|---------------------------------|

| 0Bh, 8Bh,<br>10Bh,18Bh | INTCON                             | GIE                     | PEIE  | TOIE  | INTE  | RBIE  | TOIF   | INTF   | R0IF      | 0000 000x             | 0000 000u                       |

| 0Ch                    | PIR1                               | PSPIF <sup>(1)</sup>    | ADIF  | RCIF  | TXIF  | —     | CCP1IF | TMR2IF | TMR1IF    | 0000 -000             | 0000 -000                       |

| 18h                    | RCSTA                              | SPEN                    | RX9   | SREN  | CREN  | ADDEN | FERR   | OERR   | RX9D      | x000 000x             | x000 000x                       |

| 19h                    | TXREG                              | USART Transmit Register |       |       |       |       |        |        | 0000 0000 | 0000 0000             |                                 |

| 8Ch                    | PIE1                               | PSPIE <sup>(1)</sup>    | ADIE  | RCIE  | TXIE  | —     | CCP1IE | TMR2IE | TMR1IE    | 0000 -000             | 0000 -000                       |

| 98h                    | TXSTA                              | CSRC                    | TX9   | TXEN  | SYNC  | _     | BRGH   | TRMT   | TX9D      | 0000 -010             | 0000 -010                       |

| 99h                    | SPBRG Baud Rate Generator Register |                         |       |       |       |       |        |        | 0000 0000 | 0000 0000             |                                 |

#### TABLE 9-10: REGISTERS ASSOCIATED WITH SYNCHRONOUS SLAVE TRANSMISSION

Legend: x = unknown, - = unimplemented, read as '0'. Shaded cells are not used for synchronous slave transmission.

Note 1: Bits PSPIE and PSPIF are reserved on the PIC16F870; always maintain these bits clear.

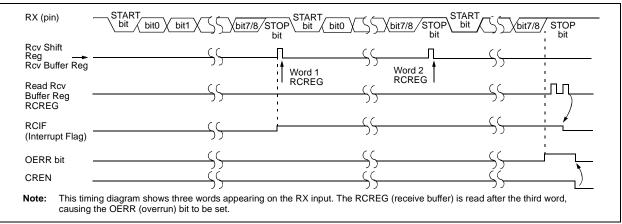

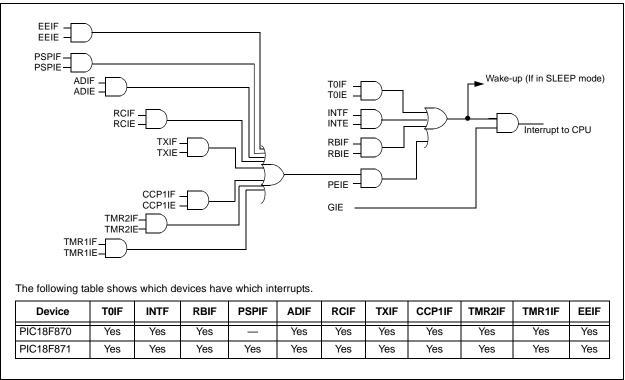

FIGURE 11-9: INTERRUPT LOGIC

#### 11.10.1 INT INTERRUPT

External interrupt on the RB0/INT pin is edge triggered, either rising, if bit INTEDG (OPTION\_REG<6>) is set, or falling, if the INTEDG bit is clear. When a valid edge appears on the RB0/INT pin, flag bit INTF (INTCON<1>) is set. This interrupt can be disabled by clearing enable bit INTE (INTCON<4>). Flag bit INTF must be cleared in software in the Interrupt Service Routine before re-enabling this interrupt. The INT interrupt can wake-up the processor from SLEEP, if bit INTE was set prior to going into SLEEP. The status of global interrupt enable bit, GIE, decides whether or not the processor branches to the interrupt vector following wake-up. See Section 11.13 for details on SLEEP mode.

#### 11.10.2 TMR0 INTERRUPT

An overflow (FFh  $\rightarrow$  00h) in the TMR0 register will set flag bit T0IF (INTCON<2>). The interrupt can be enabled/disabled by setting/clearing enable bit T0IE (INTCON<5>) (Section 5.0).

#### 11.10.3 PORTB INTCON CHANGE

An input change on PORTB<7:4> sets flag bit RBIF (INTCON<0>). The interrupt can be enabled/disabled by setting/clearing enable bit RBIE (INTCON<4>) (Section 4.2).

#### 11.17 In-Circuit Serial Programming

PIC16F870/871 microcontrollers can be serially programmed while in the end application circuit. This is simply done with two lines for clock and data and three other lines for power, ground, and the programming voltage. This allows customers to manufacture boards with unprogrammed devices, and then program the microcontroller just before shipping the product. This also allows the most recent firmware, or a custom firmware to be programmed.

When using ICSP, the part must be supplied at 4.5V to 5.5V, if a bulk erase will be executed. This includes reprogramming of the code protect, both from an onstate to off-state. For all other cases of ICSP, the part may be programmed at the normal operating voltages. This means calibration values, unique user IDs, or user code can be reprogrammed or added.

For complete details of serial programming, please refer to the EEPROM Memory Programming Specification for the PIC16F87X (DS39025).

#### 11.18 Low Voltage ICSP Programming