Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

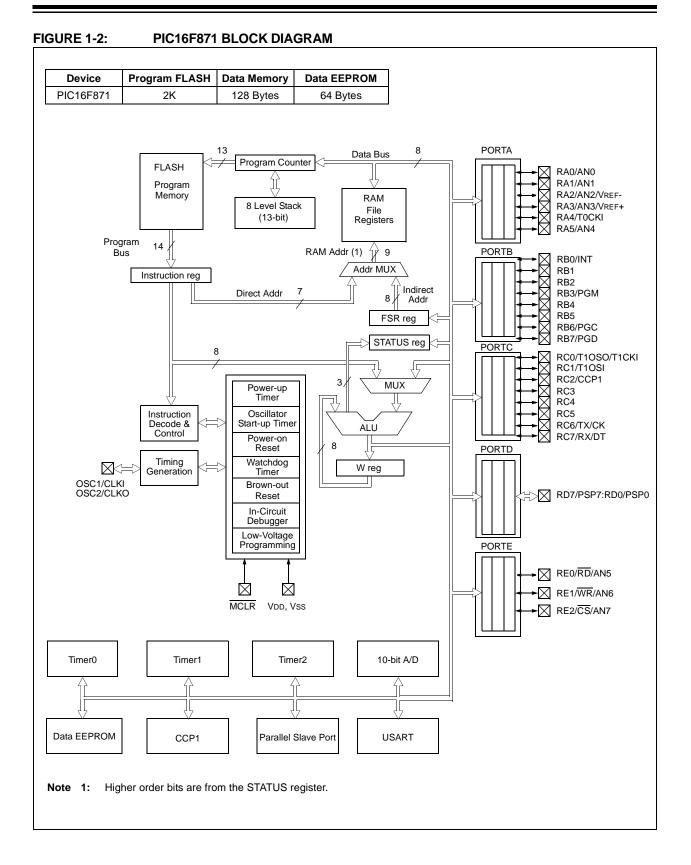

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                         |

|----------------------------|-------------------------------------------------------------------------|

| Product Status             | Active                                                                  |

| Core Processor             | PIC                                                                     |

| Core Size                  | 8-Bit                                                                   |

| Speed                      | 20MHz                                                                   |

| Connectivity               | UART/USART                                                              |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                   |

| Number of I/O              | 33                                                                      |

| Program Memory Size        | 3.5KB (2K x 14)                                                         |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | 64 x 8                                                                  |

| RAM Size                   | 128 x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 4V ~ 5.5V                                                               |

| Data Converters            | A/D 8x10b                                                               |

| Oscillator Type            | External                                                                |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                           |

| Package / Case             | 44-LCC (J-Lead)                                                         |

| Supplier Device Package    | 44-PLCC (16.59x16.59)                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f871-i-l |

|                            |                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## **Table of Contents**

| 1.0   | Device Overview                                                             | 5   |

|-------|-----------------------------------------------------------------------------|-----|

| 2.0   | Memory Organization                                                         | 11  |

| 3.0   | Data EEPROM and Flash Program Memory                                        | 27  |

| 4.0   | I/O Ports                                                                   | 33  |

| 5.0   | Timer0 Module                                                               | 45  |

| 6.0   | Timer1 Module                                                               | 49  |

| 7.0   | Timer2 Module                                                               | 53  |

| 8.0   | Capture/Compare/PWM Modules                                                 |     |

| 9.0   | Addressable Universal Synchronous Asynchronous Receiver Transmitter (USART) | 61  |

| 10.0  | Analog-to-Digital (A/D) Converter Module                                    | 79  |

| 11.0  | Special Features of the CPU                                                 | 87  |

| 12.0  | Instruction Set Summary                                                     | 103 |

| 13.0  | Development Support                                                         | 111 |

| 14.0  | Electrical Characteristics                                                  | 117 |

| 15.0  | DC and AC Characteristics Graphs and Tables                                 |     |

| 16.0  | Packaging Information                                                       | 149 |

| Appe  | ndix A: Revision History                                                    | 157 |

| Appe  | ndix B: Device Differences                                                  | 157 |

| Appe  | ndix C: Conversion Considerations                                           | 158 |

| Appe  | ndix D: Migration from Mid-Range to Enhanced Devices                        | 158 |

| Appe  | ndix E: Migration from High-End to Enhanced Devices                         | 159 |

| Index | ۲                                                                           | 161 |

| On-L  | ine Support                                                                 | 167 |

| Syste | ems Information and Upgrade Hot Line                                        | 167 |

| Read  | ler Response                                                                | 168 |

| PIC1  | 6F870/871 Product Identification System                                     | 169 |

## TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at **docerrors@mail.microchip.com** or fax the **Reader Response Form** in the back of this data sheet to (480) 792-4150. We welcome your feedback.

### Most Current Data Sheet

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000A is version A of document DS30000).

#### Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

- Microchip's Worldwide Web site; http://www.microchip.com

- Your local Microchip sales office (see last page)

- The Microchip Corporate Literature Center; U.S. FAX: (480) 792-7277

When contacting a sales office or the literature center, please specify which device, revision of silicon and data sheet (include literature number) you are using.

#### **Customer Notification System**

Register on our web site at www.microchip.com/cn to receive the most current information on all of our products.

| Pin Name                                                                                                                                                      | DIP<br>Pin# | PLCC<br>Pin#   | QFP<br>Pin#     | I/O/P<br>Type | Buffer<br>Type        | Description                                                                                         |  |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|----------------|-----------------|---------------|-----------------------|-----------------------------------------------------------------------------------------------------|--|--|

|                                                                                                                                                               |             |                |                 |               |                       | PORTD is a bi-directional I/O port or parallel slave port when interfacing to a microprocessor bus. |  |  |

| RD0/PSP0                                                                                                                                                      | 19          | 21             | 38              | I/O           | ST/TTL <sup>(3)</sup> |                                                                                                     |  |  |

| RD1/PSP1                                                                                                                                                      | 20          | 22             | 39              | I/O           | ST/TTL <sup>(3)</sup> |                                                                                                     |  |  |

| RD2/PSP2                                                                                                                                                      | 21          | 23             | 40              | I/O           | ST/TTL <sup>(3)</sup> |                                                                                                     |  |  |

| RD3/PSP3                                                                                                                                                      | 22          | 24             | 41              | I/O           | ST/TTL <sup>(3)</sup> |                                                                                                     |  |  |

| RD4/PSP4                                                                                                                                                      | 27          | 30             | 2               | I/O           | ST/TTL <sup>(3)</sup> |                                                                                                     |  |  |

| RD5/PSP5                                                                                                                                                      | 28          | 31             | 3               | I/O           | ST/TTL <sup>(3)</sup> |                                                                                                     |  |  |

| RD6/PSP6                                                                                                                                                      | 29          | 32             | 4               | I/O           | ST/TTL <sup>(3)</sup> |                                                                                                     |  |  |

| RD7/PSP7                                                                                                                                                      | 30          | 33             | 5               | I/O           | ST/TTL <sup>(3)</sup> |                                                                                                     |  |  |

|                                                                                                                                                               |             |                |                 |               |                       | PORTE is a bi-directional I/O port.                                                                 |  |  |

| RE0/RD/AN5                                                                                                                                                    | 8           | 9              | 25              | I/O           | ST/TTL <sup>(3)</sup> | RE0 can also be read control for the parallel slave port, or analog input 5.                        |  |  |

| RE1/WR/AN6                                                                                                                                                    | 9           | 10             | 26              | I/O           | ST/TTL <sup>(3)</sup> | RE1 can also be write control for the parallel slave port, or analog input 6.                       |  |  |

| RE2/CS/AN7                                                                                                                                                    | 10          | 11             | 27              | I/O           | ST/TTL <sup>(3)</sup> | RE2 can also be select control for the parallel slave port, or analog input 7.                      |  |  |

| Vss                                                                                                                                                           | 12,31       | 13,34          | 6,29            | Р             | _                     | Ground reference for logic and I/O pins.                                                            |  |  |

| Vdd                                                                                                                                                           | 11,32       | 12,35          | 7,28            | Р             |                       | Positive supply for logic and I/O pins.                                                             |  |  |

| NC                                                                                                                                                            | -           | 1,17,28,<br>40 | 12,13,<br>33,34 |               | _                     | These pins are not internally connected. These pins should be left unconnected.                     |  |  |

| Legend:       I = input       O = output       I/O = input/output       P = power         — = Not used       TTL = TTL input       ST = Schmitt Trigger input |             |                |                 |               |                       |                                                                                                     |  |  |

## TABLE 1-2: PIC16F871 PINOUT DESCRIPTION (CONTINUED)

**Note 1:** This buffer is a Schmitt Trigger input when configured as an external interrupt or LVP mode.

2: This buffer is a Schmitt Trigger input when used in Serial Programming mode.

**3:** This buffer is a Schmitt Trigger input when configured as general purpose I/O and a TTL input when used in the Parallel Slave Port mode (for interfacing to a microprocessor bus).

4: This buffer is a Schmitt Trigger input when configured in RC Oscillator mode and a CMOS input otherwise.

| Address               | Name       | Bit 7                                                          | Bit 6                        | Bit 5         | Bit 4         | Bit 3         | Bit 2           | Bit 1        | Bit 0       | Value on:<br>POR, BOR | Value on<br>all other<br>RESETS <sup>(2)</sup> |  |

|-----------------------|------------|----------------------------------------------------------------|------------------------------|---------------|---------------|---------------|-----------------|--------------|-------------|-----------------------|------------------------------------------------|--|

| Bank 2                |            |                                                                |                              |               | •             |               | •               | •            | •           | •                     | •                                              |  |

| 100h <sup>(4)</sup>   | INDF       | Addressing                                                     | this location                | uses conte    | ents of FSR t | o address dat | a memory (n     | ot a physica | l register) | 0000 0000             | 0000 0000                                      |  |

| 101h                  | TMR0       | Timer0 Mod                                                     | 0 Module's Register xxxx xxx |               |               |               |                 |              |             |                       |                                                |  |

| 102h <sup>(4)</sup>   | PCL        | Program Co                                                     | ounter's (PC                 | ) Least Sigr  | nificant Byte |               |                 |              |             | 0000 0000             | 0000 0000                                      |  |

| 103h <sup>(4)</sup>   | STATUS     | IRP                                                            | RP1                          | RP0           | то            | PD            | Z               | DC           | С           | 0001 1xxx             | 000q quuu                                      |  |

| 104h <sup>(4)</sup>   | FSR        | Indirect Dat                                                   | a Memory A                   | ddress Poir   | nter          |               |                 |              |             | XXXX XXXX             | uuuu uuuu                                      |  |

| 105h                  | _          | Unimpleme                                                      | nted                         |               |               |               |                 |              |             | _                     | —                                              |  |

| 106h                  | PORTB      | PORTB Da                                                       | ta Latch whe                 | en written: F | ORTB pins     | when read     |                 |              |             | XXXX XXXX             | uuuu uuuu                                      |  |

| 107h                  | —          | Unimpleme                                                      | nted                         |               |               |               |                 |              |             | _                     | _                                              |  |

| 108h                  | —          | Unimpleme                                                      | nted                         |               |               |               |                 |              |             | _                     | _                                              |  |

| 109h                  | —          | Unimpleme                                                      | nted                         |               |               |               |                 |              |             | _                     | _                                              |  |

| 10Ah <sup>(1,4)</sup> | PCLATH     | _                                                              | _                            | _             | Write Buffe   | for the upper | r 5 bits of the | Program Co   | ounter      | 0 0000                | 0 0000                                         |  |

| 10Bh <sup>(4)</sup>   | INTCON     | GIE                                                            | PEIE                         | TOIE          | INTE          | RBIE          | T0IF            | INTF         | RBIF        | 0000 000x             | 0000 000u                                      |  |

| 10Ch                  | EEDATA     | EEPROM D                                                       | Data Registe                 | r             |               |               |                 |              |             | XXXX XXXX             | uuuu uuuu                                      |  |

| 10Dh                  | EEADR      | EEPROM A                                                       | ddress Reg                   | ister         |               |               |                 |              |             | XXXX XXXX             | uuuu uuuu                                      |  |

| 10Eh                  | EEDATH     | _                                                              | _                            | EEPROM        | Data Registe  | r High Byte   |                 |              |             | XXXX XXXX             | uuuu uuuu                                      |  |

| 10Fh                  | EEADRH     | _                                                              | _                            | _             | EEPROM A      | ddress Regis  | ter High Byte   | )            |             | XXXX XXXX             | uuuu uuuu                                      |  |

| Bank 3                |            |                                                                |                              |               |               |               |                 |              |             |                       |                                                |  |

| 180h <sup>(4)</sup>   | INDF       | Addressing                                                     | this location                | uses conte    | ents of FSR t | o address dat | a memory (n     | ot a physica | l register) | 0000 0000             | 0000 0000                                      |  |

| 181h                  | OPTION_REG | RBPU                                                           | INTEDG                       | TOCS          | TOSE          | PSA           | PS2             | PS1          | PS0         | 1111 1111             | 1111 1111                                      |  |

| 182h <sup>(4)</sup>   | PCL        | Program Co                                                     | ounter's (PC                 | ) Least Sigr  | nificant Byte |               |                 |              |             | 0000 0000             | 0000 0000                                      |  |

| 183h <sup>(4)</sup>   | STATUS     | IRP                                                            | RP1                          | RP0           | то            | PD            | Z               | DC           | С           | 0001 1xxx             | 000q quuu                                      |  |

| 184h <sup>(4)</sup>   | FSR        | Indirect Dat                                                   | a Memory A                   | ddress Poir   | nter          |               |                 |              |             | XXXX XXXX             | uuuu uuuu                                      |  |

| 185h                  | _          | Unimpleme                                                      | nted                         |               |               |               |                 |              |             | _                     | —                                              |  |

| 186h                  | TRISB      | PORTB Da                                                       | ta Direction                 | Register      |               |               |                 |              |             | 1111 1111             | 1111 1111                                      |  |

| 187h                  | _          | Unimpleme                                                      | nted                         |               |               |               |                 |              |             | _                     | —                                              |  |

| 188h                  | _          | Unimpleme                                                      | nted                         |               |               |               |                 |              |             | _                     | —                                              |  |

| 189h                  | _          | Unimplemented                                                  |                              |               |               |               |                 |              |             | _                     | —                                              |  |

| 18Ah <sup>(1,4)</sup> | PCLATH     | — — — Write Buffer for the upper 5 bits of the Program Counter |                              |               |               |               |                 |              |             | 0 0000                | 0 0000                                         |  |

| 18Bh <sup>(4)</sup>   | INTCON     | GIE                                                            | PEIE                         | TOIE          | INTE          | RBIE          | T0IF            | INTF         | RBIF        | 0000 000x             | 0000 000u                                      |  |

| 18Ch                  | EECON1     | EEPGD                                                          | —                            | —             | —             | WRERR         | WREN            | WR           | RD          | x x000                | x u000                                         |  |

| 18Dh                  | EECON2     | EEPROM (                                                       | Control Regis                | ster2 (not a  | physical reg  | ster)         |                 |              |             |                       |                                                |  |

| 18Eh                  | —          | Reserved n                                                     | naintain clea                | r             |               |               |                 |              |             | 0000 0000             | 0000 0000                                      |  |

| 18Fh                  | _          | Reserved n                                                     | naintain clea                | r             |               |               |                 |              |             | 0000 0000             | 0000 0000                                      |  |

| TABLE 2-1: | SPECIAL FUNCTION REGISTER SUMMARY ( | (CONTINUED) |

|------------|-------------------------------------|-------------|

|------------|-------------------------------------|-------------|

**Note 1:** The upper byte of the program counter is not directly accessible. PCLATH is a holding register for the PC<12:8> whose contents are transferred to the upper byte of the program counter.

2: Other (non Power-up) Resets include external RESET through MCLR and Watchdog Timer Reset.

3: Bits PSPIE and PSPIF are reserved on the 28-pin devices; always maintain these bits clear.

4: These registers can be addressed from any bank.

5: PORTD, PORTE, TRISD and TRISE are not physically implemented on the 28-pin devices, read as '0'.

## 2.3 PCL and PCLATH

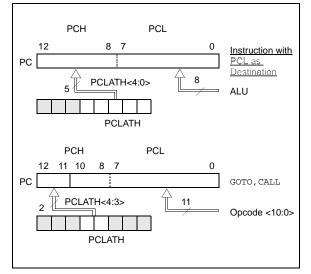

The Program Counter (PC) is 13-bits wide. The low byte comes from the PCL register, which is a readable and writable register. The upper bits (PC<12:8>) are not readable, but are indirectly writable through the PCLATH register. On any RESET, the upper bits of the PC will be cleared. Figure 2-3 shows the two situations for the loading of the PC. The upper example in the figure shows how the PC is loaded on a write to PCL (PCLATH<4:0>  $\rightarrow$  PCH). The lower example in the figure shows how the PC is loaded during a CALL or GOTO instruction (PCLATH<4:3>  $\rightarrow$  PCH).

#### FIGURE 2-3: LOADING OF PC IN DIFFERENT SITUATIONS

## 2.3.1 COMPUTED GOTO

A computed GOTO is accomplished by adding an offset to the program counter (ADDWF PCL). When doing a table read using a computed GOTO method, care should be exercised if the table location crosses a PCL memory boundary (each 256-byte block). Refer to the application note, *"Implementing a Table Read"* (AN556).

### 2.3.2 STACK

The PIC16FXXX family has an 8-level deep x 13-bit wide hardware stack. The stack space is not part of either program or data space and the stack pointer is not readable or writable. The PC is PUSHed onto the stack when a CALL instruction is executed, or an interrupt causes a branch. The stack is POPed in the event of a RETURN, RETLW or a RETFIE instruction execution. PCLATH is not affected by a PUSH or POP operation.

The stack operates as a circular buffer. This means that after the stack has been PUSHed eight times, the ninth push overwrites the value that was stored from the first push. The tenth push overwrites the second push (and so on).

**Note 1:** There are no status bits to indicate stack overflow or stack underflow conditions.

2: There are no instructions/mnemonics called PUSH or POP. These are actions that occur from the execution of the CALL, RETURN, RETLW and RETFIE instructions, or the vectoring to an interrupt address.

## 2.4 Program Memory Paging

The PIC16FXXX architecture is capable of addressing a continuous 8K word block of program memory. The CALL and GOTO instructions provide 11 bits of the address, which allows branches within any 2K program memory page. Therefore, the 8K words of program memory are broken into four pages. Since the PIC16F872 has only 2K words of program memory or one page, additional code is not required to ensure that the correct page is selected before a CALL or GOTO instruction is executed. The PCLATH<4:3> bits should always be maintained as zeros. If a return from a CALL instruction (or interrupt) is executed, the entire 13-bit PC is popped off the stack. Manipulation of the PCLATH is not required for the return instructions.

## 2.5 Indirect Addressing, INDF and FSR Registers

The INDF register is not a physical register. Addressing the INDF register will cause indirect addressing.

Indirect addressing is possible by using the INDF register. Any instruction using the INDF register actually accesses the register pointed to by the File Select register, FSR. Reading the INDF register itself indirectly (FSR = 0) will read 00h. Writing to the INDF register indirectly results in a no operation (although status bits may be affected). An effective 9-bit address is obtained by concatenating the 8-bit FSR register and the IRP bit (STATUS<7>), as shown in Figure 2-4.

A simple program to clear RAM locations 20h-2Fh using indirect addressing is shown in Example 2-1.

| EXAMPLE 2-1: IND | IRECT ADDRESSING |

|------------------|------------------|

|------------------|------------------|

| NEXT   | movlw<br>movwf<br>clrf<br>incf<br>btfss<br>goto | 0x20<br>FSR<br>INDF<br>FSR,F<br>FSR,4<br>NEXT | ;initialize pointer<br>;to RAM<br>;clear INDF register<br>;inc pointer<br>;all done?<br>;no clear next |

|--------|-------------------------------------------------|-----------------------------------------------|--------------------------------------------------------------------------------------------------------|

| CONTIN | UE                                              |                                               |                                                                                                        |

| :      |                                                 |                                               | ;yes continue                                                                                          |

NOTES:

### 5.2 Using Timer0 with an External Clock

When no prescaler is used, the external clock input is the same as the prescaler output. The synchronization of T0CKI with the internal phase clocks is accomplished by sampling the prescaler output on the Q2 and Q4 cycles of the internal phase clocks. Therefore, it is necessary for T0CKI to be high for at least 2 Tosc (and a small RC delay of 20 ns) and low for at least 2 Tosc (and a small RC delay of 20 ns). Refer to the electrical specification of the desired device.

## 5.3 Prescaler

There is only one prescaler available, which is mutually exclusively shared between the Timer0 module and the Watchdog Timer. A prescaler assignment for the Timer0 module means that there is no prescaler for the Watchdog Timer, and vice-versa. This prescaler is not readable or writable (see Figure 5-1).

The PSA and PS2:PS0 bits (OPTION\_REG<3:0>) determine the prescaler assignment and prescale ratio.

When assigned to the Timer0 module, all instructions writing to the TMR0 register (e.g., CLRF1, MOVWF1, BSF1, x....etc.) will clear the prescaler. When assigned to WDT, a CLRWDT instruction will clear the prescaler along with the Watchdog Timer. The prescaler is not readable or writable.

| Note: | Writing to TMR0 when the prescaler is    |  |  |  |  |  |  |  |  |

|-------|------------------------------------------|--|--|--|--|--|--|--|--|

|       | assigned to Timer0, will clear the       |  |  |  |  |  |  |  |  |

|       | prescaler count, but will not change the |  |  |  |  |  |  |  |  |

|       | prescaler assignment.                    |  |  |  |  |  |  |  |  |

### REGISTER 5-1: OPTION\_REG REGISTER

|              | R/W-1                              | R/W-1                            | R/W-1        | R/W-1         | R/W-1          | R/W-1      | R/W-1         | R/W-1 |  |  |

|--------------|------------------------------------|----------------------------------|--------------|---------------|----------------|------------|---------------|-------|--|--|

|              | RBPU                               | INTEDG                           | TOCS         | T0SE          | PSA            | PS2        | PS1           | PS0   |  |  |

|              | bit 7                              |                                  |              |               |                |            |               | bit 0 |  |  |

| bit 7        | RBPU                               |                                  |              |               |                |            |               |       |  |  |

| bit 6        | INTEDG                             |                                  |              |               |                |            |               |       |  |  |

| bit 5        | TOCS: TMR0 Clock Source Select bit |                                  |              |               |                |            |               |       |  |  |

|              | 1 = Transi                         | tion on T0CK                     | l pin        |               |                |            |               |       |  |  |

|              | 0 = Interna                        | al instruction                   | cycle clock  | (CLKO)        |                |            |               |       |  |  |

| bit 4        | TOSE: TM                           | R0 Source E                      | dge Select   | bit           |                |            |               |       |  |  |

|              |                                    | nent on high-t                   |              |               |                |            |               |       |  |  |

|              | 0 = Increm                         | nent on low-to                   | o-high trans | sition on TOC | CKI pin        |            |               |       |  |  |

| bit 3        | PSA: Pres                          | scaler Assign                    | ment bit     |               |                |            |               |       |  |  |

|              |                                    | aler is assign<br>aler is assign |              |               |                |            |               |       |  |  |

| bit 2-0      |                                    | Prescaler Ra                     |              |               |                |            |               |       |  |  |

|              |                                    |                                  |              |               |                |            |               |       |  |  |

|              | Bit Value                          | TMR0 Rate                        | WD1 Rate     | e             |                |            |               |       |  |  |

|              | 000                                | 1:2                              | 1:1          |               |                |            |               |       |  |  |

|              | 001<br>010                         | 1:4<br>1:8                       | 1:2<br>1:4   |               |                |            |               |       |  |  |

|              | 010                                | 1:16                             | 1:8          |               |                |            |               |       |  |  |

|              | 100                                | 1:32                             | 1:16         |               |                |            |               |       |  |  |

|              | 101                                | 1:64                             | 1:32         |               |                |            |               |       |  |  |

|              | 110                                | 1:128                            | 1:64         |               |                |            |               |       |  |  |

|              | 111                                | 1 : 256                          | 1 : 128      |               |                |            |               |       |  |  |

|              | Legend:                            |                                  |              |               |                |            |               |       |  |  |

|              | R = Reada                          | able bit                         | VV = V       | Vritable bit  | U = Unimpl     | lemented b | it, read as ' | )'    |  |  |

|              | - n = Value                        |                                  | '1' = E      | Bit is set    | '0' = Bit is o |            | x = Bit is ur |       |  |  |

| <b>-</b> · · |                                    |                                  |              |               | uence shown ir |            |               |       |  |  |

**Note:** To avoid an unintended device RESET, the instruction sequence shown in the PIC<sup>®</sup> Mid-Range MCU Family Reference Manual (DS33023) must be executed when changing the prescaler assignment from Timer0 to the WDT. This sequence must be followed even if the WDT is disabled.

## 6.4 Timer1 Operation in Asynchronous Counter Mode

If control bit  $\overline{T1SYNC}$  (T1CON<2>) is set, the external clock input is not synchronized. The timer continues to increment asynchronous to the internal phase clocks. The timer will continue to run during SLEEP and can generate an interrupt-on-overflow, which will wake-up the processor. However, special precautions in software are needed to read/write the timer (Section 6.4.1).

In Asynchronous Counter mode, Timer1 cannot be used as a time base for capture or compare operations.

### 6.4.1 READING AND WRITING TIMER1 IN ASYNCHRONOUS COUNTER MODE

Reading TMR1H or TMR1L while the timer is running from an external asynchronous clock, will ensure a valid read (taken care of in hardware). However, the user should keep in mind that reading the 16-bit timer in two 8-bit values itself, poses certain problems, since the timer may overflow between the reads.

For writes, it is recommended that the user simply stop the timer and write the desired values. A write contention may occur by writing to the timer registers, while the register is incrementing. This may produce an unpredictable value in the timer register.

Reading the 16-bit value requires some care. Examples 12-2 and 12-3 in the PIC<sup>®</sup> Mid-Range MCU Family Reference Manual (DS33023) show how to read and write Timer1 when it is running in Asynchronous mode.

## 6.5 Timer1 Oscillator

A crystal oscillator circuit is built-in between pins T1OSI (input) and T1OSO (amplifier output). It is enabled by setting control bit, T1OSCEN (T1CON<3>). The oscillator is a low power oscillator, rated up to 200 kHz. It will continue to run during SLEEP. It is primarily intended for use with a 32 kHz crystal. Table 6-1 shows the capacitor selection for the Timer1 oscillator.

The Timer1 oscillator is identical to the LP oscillator. The user must provide a software time delay to ensure proper oscillator start-up.

## TABLE 6-1:CAPACITOR SELECTION FOR<br/>THE TIMER1 OSCILLATOR

| Osc Typ          | е                                    | Freq.                                                                         | C1                                                                                                       | C2                                 |  |  |  |  |

|------------------|--------------------------------------|-------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|------------------------------------|--|--|--|--|

| LP               |                                      | 32 kHz                                                                        | 33 pF                                                                                                    | 33 pF                              |  |  |  |  |

|                  |                                      | 100 kHz                                                                       | 15 pF                                                                                                    | 15 pF                              |  |  |  |  |

|                  |                                      | 200 kHz                                                                       | 200 kHz 15 pF 15 pl                                                                                      |                                    |  |  |  |  |

| These            | va                                   | lues are for                                                                  | design guida                                                                                             | nce only.                          |  |  |  |  |

| Crystals Tested: |                                      |                                                                               |                                                                                                          |                                    |  |  |  |  |

| 32.768 kl        | 1R32.768K-A                          | ± 20 PPM                                                                      |                                                                                                          |                                    |  |  |  |  |

| 100 kH:          | 00 kHz Epson C-2 100.00 KC-P ± 20 PP |                                                                               |                                                                                                          |                                    |  |  |  |  |

| 200 kH:          | Z                                    | STD XTL                                                                       | ± 20 PPM                                                                                                 |                                    |  |  |  |  |

| Note 1:<br>2:    | of<br>tim<br>Sii<br>ch<br>res        | oscillator, but<br>ne.<br>nce each reso<br>aracteristics, t<br>sonator/crysta | nce increases<br>also increases<br>nator/crystal h<br>he user should<br>I manufactured<br>es of external | as its own<br>d consult the<br>for |  |  |  |  |

## 6.6 Resetting Timer1 Using a CCP Trigger Output

If the CCP1 module is configured in Compare mode to generate a "special event trigger" (CCP1M3:CCP1M0 = 1011), this signal will reset Timer1.

| Note: | The special event triggers from the CCP | י1 |  |  |  |  |  |  |  |  |

|-------|-----------------------------------------|----|--|--|--|--|--|--|--|--|

|       | module will not set interrupt flag bi   |    |  |  |  |  |  |  |  |  |

|       | TMR1IF (PIR1<0>).                       |    |  |  |  |  |  |  |  |  |

Timer1 must be configured for either Timer or Synchronized Counter mode to take advantage of this feature. If Timer1 is running in Asynchronous Counter mode, this RESET operation may not work.

In the event that a write to Timer1 coincides with a special event trigger from CCP1, the write will take precedence.

In this mode of operation, the CCPRH:CCPRL register pair effectively becomes the period register for Timer1.

When setting up an Asynchronous Reception, follow these steps:

- 1. Initialize the SPBRG register for the appropriate baud rate. If a high speed baud rate is desired, set bit BRGH (Section 9.1).

- 2. Enable the asynchronous serial port by clearing bit SYNC and setting bit SPEN.

- 3. If interrupts are desired, then set enable bit RCIE.

- 4. If 9-bit reception is desired, then set bit RX9.

- 5. Enable the reception by setting bit CREN.

- Flag bit RCIF will be set when reception is complete and an interrupt will be generated if enable bit RCIE is set.

- 7. Read the RCSTA register to get the ninth bit (if enabled) and determine if any error occurred during reception.

- 8. Read the 8-bit received data by reading the RCREG register.

- 9. If any error occurred, clear the error by clearing enable bit CREN.

- 10. If using interrupts, ensure that GIE and PEIE (bits 7 and 6) of the INTCON register are set.

| TABLE 9-               | ABLE 9-6: REGISTERS ASSOCIATED WITH ASTNCHRONOUS RECEPTION |                      |            |            |       |       |        |        |        |                       |                                 |

|------------------------|------------------------------------------------------------|----------------------|------------|------------|-------|-------|--------|--------|--------|-----------------------|---------------------------------|

| Address                | Name                                                       | Bit 7                | Bit 6      | Bit 5      | Bit 4 | Bit 3 | Bit 2  | Bit 1  | Bit 0  | Value on:<br>POR, BOR | Value on<br>all other<br>RESETS |

| 0Bh, 8Bh,<br>10Bh,18Bh | INTCON                                                     | GIE                  | PEIE       | TOIE       | INTE  | RBIE  | TOIF   | INTF   | R0IF   | 0000 000x             | 0000 000u                       |

| 0Ch                    | PIR1                                                       | PSPIF <sup>(1)</sup> | ADIF       | RCIF       | TXIF  | _     | CCP1IF | TMR2IF | TMR1IF | -000 0000             | -000 0000                       |

| 18h                    | RCSTA                                                      | SPEN                 | RX9        | SREN       | CREN  | —     | FERR   | OERR   | RX9D   | 0000 -00x             | 0000 -00x                       |

| 1Ah                    | RCREG                                                      | USART R              | eceive Reg | gister     |       |       |        |        |        | 0000 0000             | 0000 0000                       |

| 8Ch                    | PIE1                                                       | PSPIE <sup>(1)</sup> | ADIE       | RCIE       | TXIE  | _     | CCP1IE | TMR2IE | TMR1IE | 0000 -000             | 0000 -000                       |

| 98h                    | TXSTA                                                      | CSRC                 | TX9        | TXEN       | SYNC  | _     | BRGH   | TRMT   | TX9D   | 0000 -010             | 0000 -010                       |

| 99h                    | SPBRG                                                      | Baud Rate            | e Generato | r Register |       |       |        |        |        | 0000 0000             | 0000 0000                       |

TABLE 9-6:

REGISTERS ASSOCIATED WITH ASYNCHRONOUS RECEPTION

Legend: x = unknown, - = unimplemented locations read as '0'. Shaded cells are not used for asynchronous reception.

Note 1: Bits PSPIE and PSPIF are reserved on the PIC16F870; always maintain these bits clear.

| Address                | Name                               | Bit 7                | Bit 6                   | Bit 5 | Bit 4 | Bit 3 | Bit 2  | Bit 1  | Bit 0  | Value on:<br>POR, BOR | Value on<br>all other<br>RESETS |

|------------------------|------------------------------------|----------------------|-------------------------|-------|-------|-------|--------|--------|--------|-----------------------|---------------------------------|

| 0Bh, 8Bh,<br>10Bh,18Bh | INTCON                             | GIE                  | PEIE                    | TOIE  | INTE  | RBIE  | TOIF   | INTF   | R0IF   | 0000 000x             | 0000 000u                       |

| 0Ch                    | PIR1                               | PSPIF <sup>(1)</sup> | ADIF                    | RCIF  | TXIF  | _     | CCP1IF | TMR2IF | TMR1IF | 0000 -000             | 0000 -000                       |

| 18h                    | RCSTA                              | SPEN                 | RX9                     | SREN  | CREN  | _     | FERR   | OERR   | RX9D   | 0000 -00x             | 0000 -00x                       |

| 19h                    | TXREG                              | USART Tr             | USART Transmit Register |       |       |       |        |        |        | 0000 0000             | 0000 0000                       |

| 8Ch                    | PIE1                               | PSPIE <sup>(1)</sup> | ADIE                    | RCIE  | TXIE  | _     | CCP1IE | TMR2IE | TMR1IE | 0000 -000             | 0000 -000                       |

| 98h                    | TXSTA                              | CSRC                 | TX9                     | TXEN  | SYNC  | _     | BRGH   | TRMT   | TX9D   | 0000 -010             | 0000 -010                       |

| 99h                    | SPBRG Baud Rate Generator Register |                      |                         |       |       |       |        |        |        | 0000 0000             | 0000 0000                       |

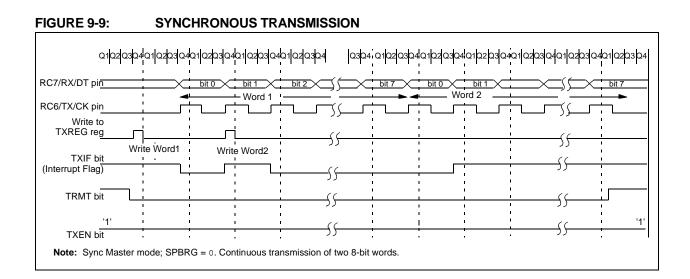

TABLE 9-8:

REGISTERS ASSOCIATED WITH SYNCHRONOUS MASTER TRANSMISSION

Legend: x = unknown, - = unimplemented, read as '0'. Shaded cells are not used for synchronous master transmission.

Note 1: Bits PSPIE and PSPIF are reserved on the PIC16F870; always maintain these bits clear.

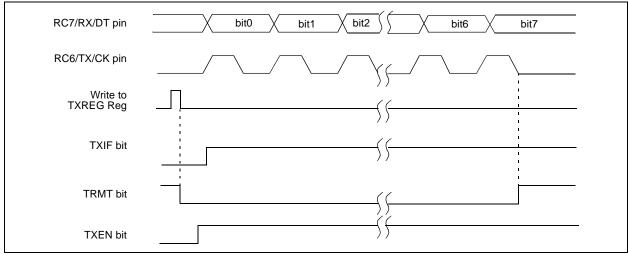

### FIGURE 9-10: SYNCHRONOUS TRANSMISSION (THROUGH TXEN)

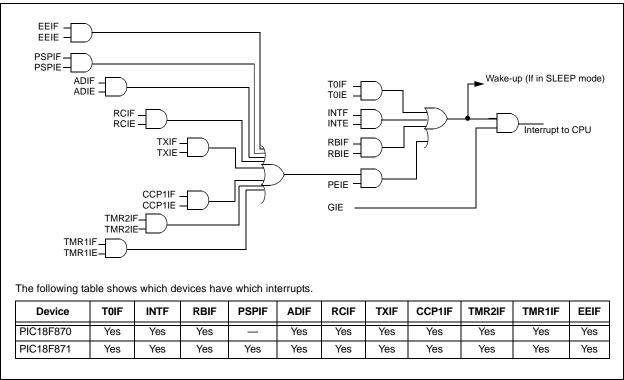

FIGURE 11-9: INTERRUPT LOGIC

### 11.10.1 INT INTERRUPT

External interrupt on the RB0/INT pin is edge triggered, either rising, if bit INTEDG (OPTION\_REG<6>) is set, or falling, if the INTEDG bit is clear. When a valid edge appears on the RB0/INT pin, flag bit INTF (INTCON<1>) is set. This interrupt can be disabled by clearing enable bit INTE (INTCON<4>). Flag bit INTF must be cleared in software in the Interrupt Service Routine before re-enabling this interrupt. The INT interrupt can wake-up the processor from SLEEP, if bit INTE was set prior to going into SLEEP. The status of global interrupt enable bit, GIE, decides whether or not the processor branches to the interrupt vector following wake-up. See Section 11.13 for details on SLEEP mode.

## 11.10.2 TMR0 INTERRUPT

An overflow (FFh  $\rightarrow$  00h) in the TMR0 register will set flag bit T0IF (INTCON<2>). The interrupt can be enabled/disabled by setting/clearing enable bit T0IE (INTCON<5>) (Section 5.0).

### 11.10.3 PORTB INTCON CHANGE

An input change on PORTB<7:4> sets flag bit RBIF (INTCON<0>). The interrupt can be enabled/disabled by setting/clearing enable bit RBIE (INTCON<4>) (Section 4.2).

| TABLE 12-2: | PIC16F870/871 INSTRUCTION SET |

|-------------|-------------------------------|

|-------------|-------------------------------|

| Mnemonic,<br>Operands |      | Description                                    | Cycles         |       | 14-Bit | Status | Notes |          |        |

|-----------------------|------|------------------------------------------------|----------------|-------|--------|--------|-------|----------|--------|

|                       |      | Description                                    | Cycles         | MSb   |        |        | LSb   | Affected | Notes  |

|                       |      | BYTE-ORIENTED FILE                             | E REGISTER OPE | RATIC | ONS    |        |       |          |        |

| ADDWF                 | f, d | Add W and f                                    | 1              | 00    | 0111   | dfff   | ffff  | C,DC,Z   | 1,2    |

| ANDWF                 | f, d | AND W with f                                   | 1              | 00    | 0101   | dfff   | ffff  | Z        | 1,2    |

| CLRF                  | f    | Clear f                                        | 1              | 00    | 0001   | lfff   | ffff  | Z        | 2      |

| CLRW                  | -    | Clear W                                        | 1              | 00    | 0001   | 0xxx   | xxxx  | Z        |        |

| COMF                  | f, d | Complement f                                   | 1              | 00    | 1001   | dfff   | ffff  | Z        | 1,2    |

| DECF                  | f, d | Decrement f                                    | 1              | 00    | 0011   | dfff   | ffff  | Z        | 1,2    |

| DECFSZ                | f, d | Decrement f, Skip if 0                         | 1(2)           | 00    | 1011   | dfff   | ffff  |          | 1,2,3  |

| INCF                  | f, d | Increment f                                    | 1              | 00    | 1010   | dfff   | ffff  | Z        | 1,2    |

| INCFSZ                | f, d | Increment f, Skip if 0                         | 1(2)           | 00    | 1111   | dfff   | ffff  |          | 1,2,3  |

| IORWF                 | f, d | Inclusive OR W with f                          | 1              | 00    | 0100   | dfff   | ffff  | Z        | 1,2    |

| MOVF                  | f, d | Move f                                         | 1              | 00    | 1000   | dfff   | ffff  | Z        | 1,2    |

| MOVWF                 | f    | Move W to f                                    | 1              | 00    | 0000   | lfff   | ffff  |          | -      |

| NOP                   | -    | No Operation                                   | 1              | 00    | 0000   | 0xx0   | 0000  |          |        |

| RLF                   | f, d | Rotate Left f through Carry                    | 1              | 00    | 1101   | dfff   | ffff  | С        | 1,2    |

| RRF                   | f, d | Rotate Right f through Carry                   | 1              | 00    | 1100   | dfff   | ffff  | С        | 1,2    |

| SUBWF                 | f, d | Subtract W from f                              | 1              | 00    | 0010   | dfff   | ffff  | C,DC,Z   | 1,2    |

| SWAPF                 | f, d | Swap nibbles in f                              | 1              | 00    | 1110   |        | ffff  | -, -,    | 1,2    |

| XORWF                 | f, d | Exclusive OR W with f                          | 1              | 00    | 0110   | dfff   | ffff  | Z        | 1,2    |

|                       |      | BIT-ORIENTED FILE                              | REGISTER OPER  | RATIO | NS     |        |       |          |        |

| BCF                   | f, b | Bit Clear f                                    | 1              | 01    | 00bb   | bfff   | ffff  |          | 1,2    |

| BSF                   | f, b | Bit Set f                                      | 1              | 01    | 01bb   | bfff   | ffff  |          | 1,2    |

| BTFSC                 | f, b | Bit Test f, Skip if Clear                      | 1 (2)          | 01    | 10bb   | bfff   | ffff  |          | 3      |

| BTFSS                 | f, b | Bit Test f, Skip if Set                        | 1 (2)          | 01    | 11bb   | bfff   | ffff  |          | 3      |

|                       |      | LITERAL AND CO                                 | NTROL OPERAT   | IONS  |        |        |       |          |        |

| ADDLW                 | k    | Add literal and W                              | 1              | 11    | 111x   | kkkk   | kkkk  | C,DC,Z   |        |

| ANDLW                 | k    | AND literal with W                             | 1              | 11    | 1001   | kkkk   | kkkk  | Z        |        |

| CALL                  | k    | Call subroutine                                | 2              | 10    | 0kkk   | kkkk   | kkkk  |          |        |

| CLRWDT                | -    | Clear Watchdog Timer                           | 1              | 00    | 0000   | 0110   | 0100  | TO,PD    |        |

| GOTO                  | k    | Go to address                                  | 2              | 10    | 1kkk   | kkkk   | kkkk  | 2        |        |

| IORLW                 | k    | Inclusive OR literal with W                    | 1              | 11    | 1000   | kkkk   | kkkk  | Z        |        |

| MOVLW                 | k    | Move literal to W                              | 1              | 11    | 00xx   | kkkk   | kkkk  |          |        |

| RETFIE                | -    | Return from interrupt                          | 2              | 00    | 0000   | 0000   | 1001  |          |        |

| RETLW                 | k    | Return with literal in W                       | 2              | 11    |        | kkkk   |       |          |        |

| RETURN                | -    | Return from Subroutine                         | 2              | 00    | 0000   | 0000   | 1000  |          |        |

| SLEEP                 | -    | Go into Standby mode                           | 1              | 00    | 0000   | 0110   | 0011  | TO,PD    |        |

| SUBLW                 | k    | Subtract W from literal                        | 1              | 11    |        | kkkk   | kkkk  | C,DC,Z   |        |

| XORLW                 | k    | Exclusive OR literal with W                    | 1              | 11    | 1010   | kkkk   | kkkk  | Z        |        |

| Note 1:               |      | I/O register is modified as a function of itse |                |       |        |        |       |          | proces |

Note 1: When an I/O register is modified as a function of itself (e.g., MOVF PORTB, 1), the value used will be that value present on the pins themselves. For example, if the data latch is '1' for a pin configured as input and is driven low by an external device, the data will be written back with a '0'.

2: If this instruction is executed on the TMR0 register (and, where applicable, d = 1), the prescaler will be cleared if assigned to the Timer0 module.

3: If Program Counter (PC) is modified, or a conditional test is true, the instruction requires two cycles. The second cycle is executed as a NOP.

**Note:** Additional information on the mid-range instruction set is available in the PIC<sup>®</sup> Mid-Range MCU Family Reference Manual (DS33023).

| CALL             | Call Subroutine                                                                                                                                                                                                                             |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] CALL k                                                                                                                                                                                                                     |

| Operands:        | $0 \leq k \leq 2047$                                                                                                                                                                                                                        |

| Operation:       | (PC)+ 1 $\rightarrow$ TOS,<br>k $\rightarrow$ PC<10:0>,<br>(PCLATH<4:3>) $\rightarrow$ PC<12:11>                                                                                                                                            |

| Status Affected: | None                                                                                                                                                                                                                                        |

| Description:     | Call Subroutine. First, return<br>address (PC+1) is pushed onto<br>the stack. The eleven-bit<br>immediate address is loaded into<br>PC bits <10:0>. The upper bits of<br>the PC are loaded from PCLATH.<br>CALL is a two-cycle instruction. |

| CLRWDT                         | Clear Watchdog Timer                                                                                                                                                                 |  |  |  |  |  |

|--------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Syntax:                        | [label] CLRWDT                                                                                                                                                                       |  |  |  |  |  |

| Operands:                      | None                                                                                                                                                                                 |  |  |  |  |  |

| Operation:<br>Status Affected: | $\begin{array}{l} 00h \rightarrow WDT \\ 0 \rightarrow WDT \ prescaler, \\ 1 \rightarrow \overline{TO} \\ 1 \rightarrow \overline{PD} \\ \overline{TO}, \ \overline{PD} \end{array}$ |  |  |  |  |  |

| Description:                   | CLRWDT instruction resets the<br>Watchdog Timer. It also resets<br>the prescaler of the WDT. Status<br>bits TO and PD are set.                                                       |  |  |  |  |  |

| CLRF             | Clear f                                                               |

|------------------|-----------------------------------------------------------------------|

| Syntax:          | [label] CLRF f                                                        |

| Operands:        | $0 \leq f \leq 127$                                                   |

| Operation:       | $\begin{array}{l} 00h \rightarrow (f) \\ 1 \rightarrow Z \end{array}$ |

| Status Affected: | Z                                                                     |

| Description:     | The contents of register 'f' are cleared and the Z bit is set.        |

| COMF             | Complement f                                                                                                                                            |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] COMF f,d                                                                                                                                        |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d  \in  [0,1] \end{array}$                                                                                       |

| Operation:       | $(\overline{f}) \rightarrow (destination)$                                                                                                              |

| Status Affected: | Z                                                                                                                                                       |

| Description:     | The contents of register 'f' are<br>complemented. If 'd' is 0, the<br>result is stored in W. If 'd' is 1, the<br>result is stored back in register 'f'. |

| CLRW             | Clear W                                                               |

|------------------|-----------------------------------------------------------------------|

| Syntax:          | [label] CLRW                                                          |

| Operands:        | None                                                                  |

| Operation:       | $\begin{array}{l} 00h \rightarrow (W) \\ 1 \rightarrow Z \end{array}$ |

| Status Affected: | Z                                                                     |

| Description:     | W register is cleared. Zero bit (Z) is set.                           |

| DECF             | Decrement f                                                                                                                                   |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ label ] DECF f,d                                                                                                                            |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d  \in  [0,1] \end{array}$                                                                             |

| Operation:       | (f) - 1 $\rightarrow$ (destination)                                                                                                           |

| Status Affected: | Z                                                                                                                                             |

| Description:     | Decrement register 'f'. If 'd' is 0,<br>the result is stored in the W<br>register. If 'd' is 1, the result is<br>stored back in register 'f'. |

| DC CHA       | RACTI | ERISTICS                               | Standard Operating Conditions (unless otherwise stated)<br>Operating temperature $-40^{\circ}C \le TA \le +125^{\circ}C$<br>Operating voltage VDD range as described in DC specification<br>(Section ) |     |          |            |                                                             |  |

|--------------|-------|----------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|----------|------------|-------------------------------------------------------------|--|

| Param<br>No. | Sym   | n Characteristic Min Typ† Max Units    |                                                                                                                                                                                                        |     | Units    | Conditions |                                                             |  |

|              | VIL   | Input Low Voltage                      |                                                                                                                                                                                                        |     |          |            |                                                             |  |

|              |       | I/O ports:                             |                                                                                                                                                                                                        |     |          |            |                                                             |  |

| D030         |       | with TTL buffer                        | Vss                                                                                                                                                                                                    | —   | 0.15 Vdd | V          | For entire VDD range                                        |  |

| D030A        |       |                                        | Vss                                                                                                                                                                                                    | —   | 0.8V     | V          | $4.5V \le VDD \le 5.5V$                                     |  |

| D031         |       | with Schmitt Trigger buffer            | Vss                                                                                                                                                                                                    | —   | 0.2 Vdd  | V          |                                                             |  |

| D032         |       | MCLR, OSC1 (in RC mode)                | Vss                                                                                                                                                                                                    | —   | 0.2 Vdd  | V          |                                                             |  |

| D033         |       | OSC1 (in XT, HS and LP)                | Vss                                                                                                                                                                                                    | —   | 0.3 Vdd  | V          | (Note 1)                                                    |  |

|              |       | Ports RC3 and RC4:                     |                                                                                                                                                                                                        |     |          |            |                                                             |  |

| D034         |       | with Schmitt Trigger buffer            | Vss                                                                                                                                                                                                    | —   | 0.3 Vdd  | V          | For entire VDD range                                        |  |

| D034A        |       | with SMBus                             | -0.5                                                                                                                                                                                                   | —   | 0.6      | V          | For VDD = 4.5 to 5.5V                                       |  |

|              | Vih   | Input High Voltage                     |                                                                                                                                                                                                        |     |          |            |                                                             |  |

|              |       | I/O ports:                             |                                                                                                                                                                                                        | —   |          |            |                                                             |  |

| D040         |       | with TTL buffer                        | 2.0                                                                                                                                                                                                    | —   | Vdd      | V          | $4.5V \le VDD \le 5.5V$                                     |  |

| D040A        |       |                                        | 0.25 VDD<br>+ 0.8V                                                                                                                                                                                     |     | Vdd      | V          | For entire VDD range                                        |  |

| D041         |       | with Schmitt Trigger buffer            | 0.8 Vdd                                                                                                                                                                                                | —   | Vdd      | V          | For entire VDD range                                        |  |

| D042         |       | MCLR                                   | 0.8 Vdd                                                                                                                                                                                                | —   | Vdd      | V          |                                                             |  |

| D042A        |       | OSC1 (XT, HS and LP)                   | 0.7 Vdd                                                                                                                                                                                                | —   | Vdd      | V          | (Note 1)                                                    |  |

| D043         |       | OSC1 (in RC mode)                      | 0.9 Vdd                                                                                                                                                                                                | —   | Vdd      | V          |                                                             |  |

|              |       | Ports RC3 and RC4:                     |                                                                                                                                                                                                        |     |          |            |                                                             |  |

| D044         |       | with Schmitt Trigger buffer            | 0.7 Vdd                                                                                                                                                                                                | —   | Vdd      | V          | For entire VDD range                                        |  |

| D044A        |       | with SMBus                             | 1.4                                                                                                                                                                                                    | —   | 5.5      | V          | For VDD = 4.5 to 5.5V                                       |  |

| D070A        | Ipurb | PORTB Weak Pull-up Current             | 50                                                                                                                                                                                                     | 250 | 400      | μΑ         | VDD = 5V, VPIN = VSS                                        |  |

|              | lı∟   | Input Leakage Current <sup>(2,3)</sup> |                                                                                                                                                                                                        |     |          |            |                                                             |  |

| D060         |       | I/O ports                              | —                                                                                                                                                                                                      | -   | ±1       | μA         | $Vss \le VPIN \le VDD,$ Pin at hi-impedance                 |  |

| D061         |       | MCLR, RA4/T0CKI                        | —                                                                                                                                                                                                      | —   | ±5       | μA         | $Vss \le VPIN \le VDD$                                      |  |

| D063         |       | OSC1                                   | —                                                                                                                                                                                                      | -   | ±5       | μA         | Vss $\leq$ VPIN $\leq$ VDD, XT, HS and LP osc configuration |  |

## 14.3 DC Characteristics: PIC16F870/871 (Extended)

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

**Note 1:** In RC oscillator configuration, the OSC1/CLKI pin is a Schmitt Trigger input. It is not recommended that the PIC16F87X be driven with external clock in RC mode.

- 2: The leakage current on the MCLR pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages.

- **3:** Negative current is defined as current sourced by the pin.

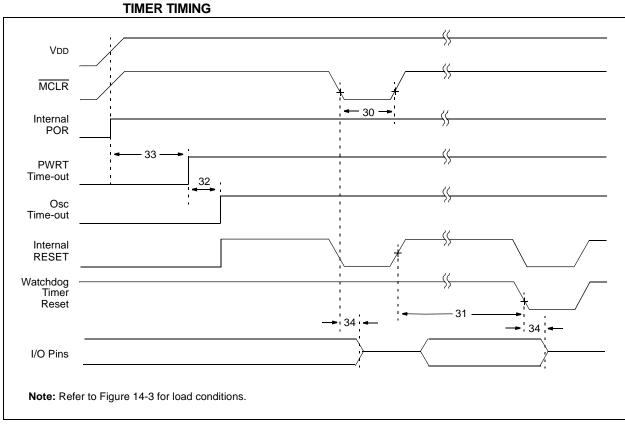

## FIGURE 14-6: RESET, WATCHDOG TIMER, OSCILLATOR START-UP TIMER AND POWER-UP TIMER TIMING

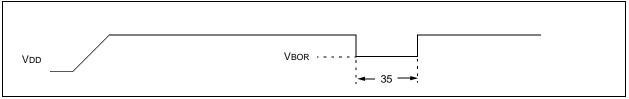

### FIGURE 14-7: BROWN-OUT RESET TIMING

## TABLE 14-3:RESET, WATCHDOG TIMER, OSCILLATOR START-UP TIMER, POWER-UP TIMER,<br/>AND BROWN-OUT RESET REQUIREMENTS

| Param<br>No. | Sym   | Characteristic                                         | Min | Тур†      | Max | Units | Conditions               |

|--------------|-------|--------------------------------------------------------|-----|-----------|-----|-------|--------------------------|

| 30           | TmcL  | MCLR Pulse Width (low)                                 | 2   | _         | _   | μS    | VDD = 5V, -40°C to +85°C |