Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                          |

|----------------------------|--------------------------------------------------------------------------|

| Product Status             | Active                                                                   |

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

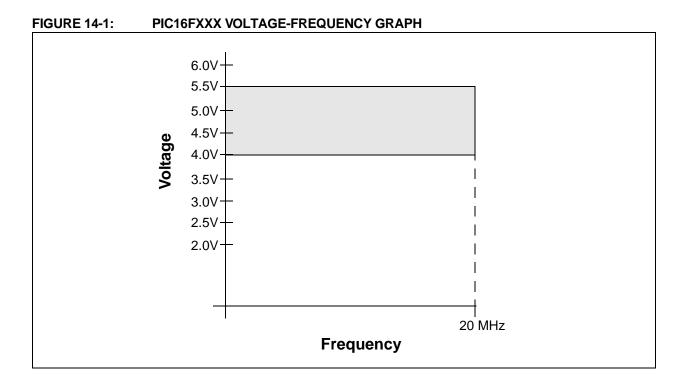

| Speed                      | 20MHz                                                                    |

| Connectivity               | UART/USART                                                               |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                    |

| Number of I/O              | 33                                                                       |

| Program Memory Size        | 3.5KB (2K x 14)                                                          |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | 64 x 8                                                                   |

| RAM Size                   | 128 x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 4V ~ 5.5V                                                                |

| Data Converters            | A/D 8x10b                                                                |

| Oscillator Type            | External                                                                 |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 44-LCC (J-Lead)                                                          |

| Supplier Device Package    | 44-PLCC (16.59x16.59)                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f871t-i-l |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

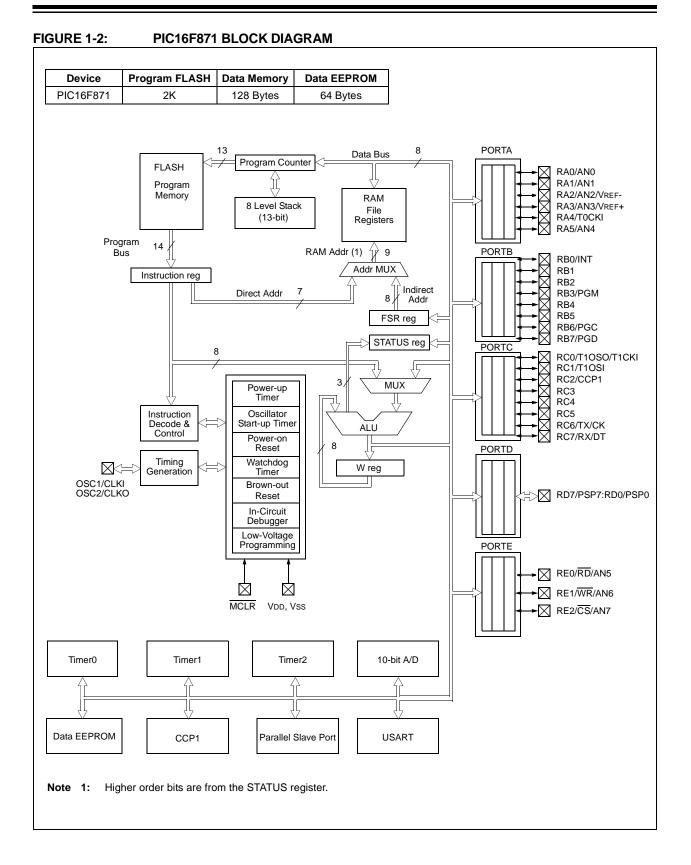

# 2.0 MEMORY ORGANIZATION

The PIC16F870/871 devices have three memory blocks. The Program Memory and Data Memory have separate buses, so that concurrent access can occur, and is detailed in this section. The EEPROM data memory block is detailed in Section 3.0.

Additional information on device memory may be found in the PICmicro<sup>™</sup> Mid-Range MCU Family Reference Manual (DS33023).

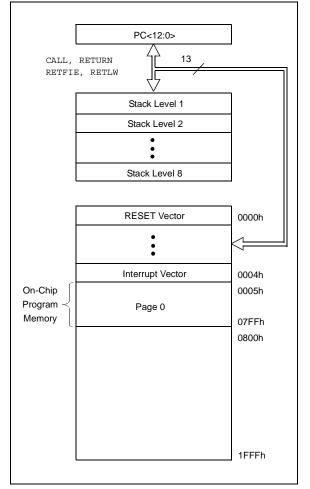

#### 2.1 Program Memory Organization

The PIC16F870/871 devices have a 13-bit program counter capable of addressing an 8K x 14 program memory space. The PIC16F870/871 devices have 2K x 14 words of FLASH program memory. Accessing a location above the physically implemented address will cause a wraparound.

The RESET vector is at 0000h and the interrupt vector is at 0004h.

## 2.2 Data Memory Organization

The data memory is partitioned into multiple banks which contain the General Purpose Registers and the Special Function Registers. Bits RP1 (STATUS<6>) and RP0 (STATUS<5>) are the bank select bits.

| RP<1:0> | Bank |

|---------|------|

| 00      | 0    |

| 01      | 1    |

| 10      | 2    |

| 11      | 3    |

Each bank extends up to 7Fh (128 bytes). The lower locations of each bank are reserved for the Special Function Registers. Above the Special Function Registers are General Purpose Registers, implemented as static RAM. All implemented banks contain Special Function Registers. Some "high use" Special Function Registers from one bank may be mirrored in another bank for code reduction and quicker access.

| Note: | EEPROM Data Memory description can          |

|-------|---------------------------------------------|

|       | be found in Section 3.0 of this Data Sheet. |

|       |                                             |

#### 2.2.1 GENERAL PURPOSE REGISTER FILE

The register file can be accessed either directly, or indirectly through the File Select Register FSR.

| Name         | Bit# | Buffer | Function                                                                    |

|--------------|------|--------|-----------------------------------------------------------------------------|

| RA0/AN0      | bit0 | TTL    | Input/output or analog input.                                               |

| RA1/AN1      | bit1 | TTL    | Input/output or analog input.                                               |

| RA2/AN2      | bit2 | TTL    | Input/output or analog input.                                               |

| RA3/AN3/VREF | bit3 | TTL    | Input/output or analog input or VREF.                                       |

| RA4/T0CKI    | bit4 | ST     | Input/output or external clock input for Timer0. Output is open drain type. |

| RA5/AN4      | bit5 | TTL    | Input/output or analog input.                                               |

#### TABLE 4-1: PORTA FUNCTIONS

Legend: TTL = TTL input, ST = Schmitt Trigger input

#### TABLE 4-2: SUMMARY OF REGISTERS ASSOCIATED WITH PORTA

| Address | Name   | Bit 7 | Bit 6 | Bit 5 | Bit 4                         | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Value on:<br>POR, BOR | Value on<br>all other<br>RESETS |

|---------|--------|-------|-------|-------|-------------------------------|-------|-------|-------|-------|-----------------------|---------------------------------|

| 05h     | PORTA  |       |       | RA5   | RA4                           | RA3   | RA2   | RA1   | RA0   | 0x 0000               | 0u 0000                         |

| 85h     | TRISA  | —     | —     | PORTA | PORTA Data Direction Register |       |       |       |       | 11 1111               | 11 1111                         |

| 9Fh     | ADCON1 | ADFM  | _     | _     |                               | PCFG3 | PCFG2 | PCFG1 | PCFG0 | 0- 0000               | 0- 0000                         |

Legend: x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells are not used by PORTA.

| REGISTER 4-1: | TRISE RE                | GISTER (                                                                                                                                                                | ADDRESS        | : 89h)                 |               |             |                |       |  |  |  |

|---------------|-------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|------------------------|---------------|-------------|----------------|-------|--|--|--|

|               | R-0                     | R-0                                                                                                                                                                     | R/W-0          | R/W-0                  | U-0           | R/W-1       | R/W-1          | R/W-1 |  |  |  |

|               | IBF                     | OBF                                                                                                                                                                     | IBOV           | PSPMODE                |               | Bit2        | Bit1           | Bit0  |  |  |  |

|               | bit 7                   |                                                                                                                                                                         |                |                        |               |             |                | bit 0 |  |  |  |

|               |                         |                                                                                                                                                                         |                |                        |               |             |                |       |  |  |  |

| bit 7         |                         | lave Port Si<br>Buffer Full S                                                                                                                                           |                | ol Bits                |               |             |                |       |  |  |  |

|               | 1 = A word              | <ul> <li>IBF: Input Buffer Full Status bit</li> <li>1 = A word has been received and is waiting to be read by the CPU</li> <li>0 = No word has been received</li> </ul> |                |                        |               |             |                |       |  |  |  |

| bit 6         | OBF: Outp               | out Buffer Fu                                                                                                                                                           | ull Status bit |                        |               |             |                |       |  |  |  |

|               |                         | utput buffer s<br>utput buffer l                                                                                                                                        |                | previously writt<br>ad | en word       |             |                |       |  |  |  |

| bit 5         | IBOV: Inpu              | ut Buffer Ov                                                                                                                                                            | erflow Dete    | ct bit (in Microp      | processor m   | ode)        |                |       |  |  |  |

|               | (must                   | e occurred v<br>be cleared<br>erflow occu                                                                                                                               | in software)   | iously input wo        | ord has not l | been read   |                |       |  |  |  |

| bit 4         | PSPMODE                 | E: Parallel S                                                                                                                                                           | lave Port M    | ode Select bit         |               |             |                |       |  |  |  |

|               |                         | el Slave Por                                                                                                                                                            |                |                        |               |             |                |       |  |  |  |

|               |                         | al Purpose I                                                                                                                                                            |                |                        |               |             |                |       |  |  |  |

| bit 3         |                         | ented: Rea                                                                                                                                                              |                |                        |               |             |                |       |  |  |  |

| <b>h</b> it 0 |                         | ata Directio                                                                                                                                                            |                |                        |               |             |                |       |  |  |  |

| bit 2         | 1 = Input               | tion Control                                                                                                                                                            | bit for pin r  | RE2/CS/AN7             |               |             |                |       |  |  |  |

|               | 1 = Input 0 = Output    | t                                                                                                                                                                       |                |                        |               |             |                |       |  |  |  |

| bit 1         | -                       |                                                                                                                                                                         | bit for pin F  | RE1/WR/AN6             |               |             |                |       |  |  |  |

|               | 1 = Input<br>0 = Output | t                                                                                                                                                                       | ·              |                        |               |             |                |       |  |  |  |

| bit 0         | Bit0: Direc             | tion Contro                                                                                                                                                             | bit for pin F  | RE0/RD/AN5             |               |             |                |       |  |  |  |

|               | 1 = Input               |                                                                                                                                                                         |                |                        |               |             |                |       |  |  |  |

|               | 0 = Output              | t                                                                                                                                                                       |                |                        |               |             |                |       |  |  |  |

|               | Legend:                 |                                                                                                                                                                         |                |                        |               |             |                |       |  |  |  |

|               | R = Reada               | able bit                                                                                                                                                                | W = \          | Vritable bit           | U = Unimr     | plemented b | oit, read as ' | 0'    |  |  |  |

|               | - n = Value             |                                                                                                                                                                         |                | Bit is set             | '0' = Bit is  |             | x = Bit is u   |       |  |  |  |

|               |                         |                                                                                                                                                                         |                |                        |               |             |                |       |  |  |  |

#### **TIMER1 MODULE** 6.0

The Timer1 module is a 16-bit timer/counter consisting of two 8-bit registers (TMR1H and TMR1L), which are readable and writable. The TMR1 register pair (TMR1H:TMR1L) increments from 0000h to FFFFh and rolls over to 0000h. The TMR1 interrupt, if enabled, is generated on overflow, which is latched in interrupt flag bit, TMR1IF (PIR1<0>). This interrupt can be enabled/disabled by setting/clearing TMR1 interrupt enable bit, TMR1IE (PIE1<0>).

Timer1 can operate in one of two modes:

- As a timer

- · As a counter

The Operating mode is determined by the clock select bit, TMR1CS (T1CON<1>).

In Timer mode, Timer1 increments every instruction cycle. In Counter mode, it increments on every rising edge of the external clock input.

Timer1 can be enabled/disabled by setting/clearing control bit, TMR1ON (T1CON<0>).

Timer1 also has an internal "RESET input". This RESET can be generated by either of the two CCP modules (Section 8.0). Register 6-1 shows the Timer1 control register.

When the Timer1 oscillator is enabled (T1OSCEN is set), the RC1/T1OSI and RC0/T1OSO/T1CKI pins become inputs. That is, the TRISC<1:0> value is ignored, and these pins read as '0'.

Additional information on timer modules is available in the PIC<sup>®</sup> Mid-Range MCU Family Reference Manual (DS33023).

| ER 6-1: | I1CON: I               | IMER1 CO                     | UNIROL R        | EGISTER        | ADDRESS:                                | 10h)        |                |        |

|---------|------------------------|------------------------------|-----------------|----------------|-----------------------------------------|-------------|----------------|--------|

|         | U-0                    | U-0                          | R/W-0           | R/W-0          | R/W-0                                   | R/W-0       | R/W-0          | R/W-0  |

|         | —                      | —                            | T1CKPS1         | T1CKPS0        | T1OSCEN                                 | T1SYNC      | TMR1CS         | TMR10N |

|         | bit 7                  |                              |                 |                |                                         |             |                | bit 0  |

|         |                        |                              |                 |                |                                         |             |                |        |

| bit 7-6 | Unimplem               | ented: Rea                   | ad as '0'       |                |                                         |             |                |        |

| bit 5-4 | T1CKPS1:               | T1CKPS0:                     | Timer1 Inpu     | t Clock Pres   | cale Select bit                         | S           |                |        |

|         | -                      | rescale valu                 |                 |                |                                         |             |                |        |

|         |                        | rescale valu                 |                 |                |                                         |             |                |        |

|         |                        | rescale valı<br>rescale valı |                 |                |                                         |             |                |        |

| bit 3   |                        |                              | scillator Enal  | ole Control b  | it                                      |             |                |        |

|         |                        | tor is enabl                 |                 |                |                                         |             |                |        |

|         | 0 = Oscilla            | tor is shut-                 | off (the oscill | ator inverter  | is turned off to                        | eliminate p | ower drain     | )      |

| bit 2   | T1SYNC: 7              | Fimer1 Exte                  | ernal Clock Ir  | nput Synchro   | onization Contr                         | ol bit      |                |        |

|         | When TMF               |                              |                 |                |                                         |             |                |        |

|         |                        |                              | e external cl   |                |                                         |             |                |        |

|         | 0 = Synchr<br>When TMF |                              | nal clock inp   | out            |                                         |             |                |        |

|         |                        |                              | ner1 uses th    | e internal clo | ock when TMR                            | 1CS = 0.    |                |        |

| bit 1   |                        | •                            | ck Source Se    |                |                                         |             |                |        |

|         |                        |                              |                 |                | (I (on the rising                       | edae)       |                |        |

|         |                        | l clock (Fo                  |                 |                | (************************************** | 5           |                |        |

| bit 0   | TMR1ON:                | Timer1 On                    | bit             |                |                                         |             |                |        |

|         | 1 = Enable             | s Timer1                     |                 |                |                                         |             |                |        |

|         | 0 = Stops 7            | Timer1                       |                 |                |                                         |             |                |        |

|         |                        |                              |                 |                |                                         |             |                |        |

|         | Legend:                |                              |                 |                |                                         |             |                |        |

|         | R = Reada              | ble bit                      | W = V           | Vritable bit   | U = Unimpl                              | emented b   | it, read as '( | )'     |

|         | - n = Value            | at POR                       | '1' = E         | Bit is set     | '0' = Bit is c                          | leared      | x = Bit is ur  | nknown |

#### T1CON: TIMER1 CONTROL REGISTER (ADDRESS: 10b) **REGISTER 6-1:**

# 8.0 CAPTURE/COMPARE/PWM MODULES

Each Capture/Compare/PWM (CCP) module contains a 16-bit register which can operate as a:

- 16-bit Capture register

- 16-bit Compare register

- PWM Master/Slave Duty Cycle register

Table 8-1 shows the resources and interactions of the CCP module. In the following sections, the operation of a CCP module is described.

# 8.1 CCP1 Module

Capture/Compare/PWM Register1 (CCPR1) is comprised of two 8-bit registers: CCPR1L (low byte) and CCPR1H (high byte). The CCP1CON register controls the operation of CCP1. The special event trigger is generated by a compare match and will reset Timer1 and start an A/D conversion (if the A/D module is enabled). Additional information on CCP modules is available in the PIC<sup>®</sup> Mid-Range MCU Family Reference Manual (DS33023) and in application note AN594, "Using the CCP Modules" (DS00594).

#### TABLE 8-1: CCP MODE - TIMER RESOURCES REQUIRED

| CCP Mode | Timer Resource |

|----------|----------------|

| Capture  | Timer1         |

| Compare  | Timer1         |

| PWM      | Timer2         |

#### REGISTER 8-1: CCP1CON REGISTER REGISTER (ADDRESS: 17h/1Dh)

| U-0   | U-0 | R/W-0 | R/W-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

|-------|-----|-------|-------|--------|--------|--------|--------|

| —     | —   | CCP1X | CCP1Y | CCP1M3 | CCP1M2 | CCP1M1 | CCP1M0 |

| bit 7 |     |       |       |        |        |        | bit 0  |

| bit 7-6 | Unimplemented: Read as                                                                                                                                                                                                                                                                                                           | '0'                                                                                                                                                                                     |                                                                 |                       |

|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------|-----------------------|

| bit 5-4 | CCP1X:CCP1Y: PWM Lea                                                                                                                                                                                                                                                                                                             | st Significant bits                                                                                                                                                                     |                                                                 |                       |

|         | <u>Capture mode</u> :<br>Unused                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                         |                                                                 |                       |

|         | <u>Compare mode:</u><br>Unused                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                         |                                                                 |                       |

|         | <u>PWM mode:</u><br>These bits are the two LSb                                                                                                                                                                                                                                                                                   | s of the PWM duty cy                                                                                                                                                                    | cle. The eight MSbs a                                           | re found in CCPR1L.   |

| bit 3-0 | CCP1M3:CCP1M0: CCP1<br>0000 = Capture/Compare/<br>0100 = Capture mode, eve<br>0101 = Capture mode, eve<br>0110 = Capture mode, eve<br>0111 = Capture mode, eve<br>1000 = Compare mode, de<br>1001 = Compare mode, de<br>1010 = Compare mode, de<br>unaffected)<br>1011 = Compare mode, tri<br>CCP1resets TMR1<br>11xx = PWM mode | PWM disabled (resets<br>ery falling edge<br>ery rising edge<br>ery 4th rising edge<br>ery 16th rising edge<br>et output on match (Ce<br>ear output on match (<br>enerate software inter | CP1IF bit is set)<br>CCP1IF bit is set)<br>rupt on match (CCP1I | 1 pin is unaffected); |

|         | Legend:                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                         |                                                                 |                       |

|         | R = Readable bit                                                                                                                                                                                                                                                                                                                 | W = Writable bit                                                                                                                                                                        | U = Unimplemented                                               | bit, read as '0'      |

|         | - n = Value at POR                                                                                                                                                                                                                                                                                                               | '1' = Bit is set                                                                                                                                                                        | '0' = Bit is cleared                                            | x = Bit is unknown    |

# 9.0 ADDRESSABLE UNIVERSAL SYNCHRONOUS ASYNCHRONOUS RECEIVER TRANSMITTER (USART)

The Universal Synchronous Asynchronous Receiver Transmitter (USART) module is one of the two serial I/O modules. (USART is also known as a Serial Communications Interface or SCI.) The USART can be configured as a full duplex asynchronous system that can communicate with peripheral devices, such as CRT terminals and personal computers, or it can be configured as a half-duplex synchronous system that can communicate with peripheral devices, such as A/D or D/A integrated circuits, serial EEPROMs, etc. The USART can be configured in the following modes:

- Asynchronous (full-duplex)

- Synchronous Master (half-duplex)

- Synchronous Slave (half-duplex)

Bit SPEN (RCSTA<7>) and bits TRISC<7:6> have to be set in order to configure pins RC6/TX/CK and RC7/RX/DT as the Universal Synchronous Asynchronous Receiver Transmitter.

The USART module also has a multi-processor communication capability using 9-bit address detection.

#### **REGISTER 9-1:** TXSTA: TRANSMIT STATUS AND CONTROL REGISTER (ADDRESS: 98h)

|       | R/W-0                                              | R/W-0           | R/W-0        | R/W-0         | U-0            | <b>R</b> /W-0 | R-1           | ,<br>R/W-0 |

|-------|----------------------------------------------------|-----------------|--------------|---------------|----------------|---------------|---------------|------------|

|       | CSRC                                               | TX9             | TXEN         | SYNC          | —              | BRGH          | TRMT          | TX9D       |

|       | bit 7                                              |                 |              |               |                |               |               | bit 0      |

| bit 7 | CSRC: Cloc                                         | k Source Se     | elect bit    |               |                |               |               |            |

|       | <u>Asynchronou</u><br>Don't care                   | <u>us mode:</u> |              |               |                |               |               |            |

|       | <u>Synchronous</u><br>1 = Master n<br>0 = Slave mo | node (clock     |              |               | m BRG)         |               |               |            |

| bit 6 | <b>TX9</b> : 9-bit Tr                              | ansmit Enal     | ole bit      |               |                |               |               |            |

|       | 1 = Selects 9<br>0 = Selects 8                     |                 |              |               |                |               |               |            |

| bit 5 | TXEN: Tran                                         | smit Enable     | bit          |               |                |               |               |            |

|       | 1 = Transmit<br>0 = Transmit                       |                 |              |               |                |               |               |            |

|       | Note: S                                            | SREN/CREM       | l overrides  | TXEN in Sy    | nc mode.       |               |               |            |

| bit 4 | SYNC: USA                                          | RT Mode Se      | elect bit    |               |                |               |               |            |

|       | 1 = Synchron<br>0 = Asynchro                       |                 | 9            |               |                |               |               |            |

| bit 3 | Unimpleme                                          | nted: Read      | as '0'       |               |                |               |               |            |

| bit 2 | BRGH: High                                         | Baud Rate       | Select bit   |               |                |               |               |            |

|       | Asynchronou<br>1 = High spe<br>0 = Low spe         | ed              |              |               |                |               |               |            |

|       | Synchronous                                        |                 |              |               |                |               |               |            |

|       | Unused in th                                       |                 |              |               |                |               |               |            |

| bit 1 | TRMT: Trans                                        | smit Shift Re   | gister Statu | s bit         |                |               |               |            |

|       | 1 = TSR emp<br>0 = TSR full                        | pty             |              |               |                |               |               |            |

| bit 0 | TX9D: 9th bi                                       | it of Transm    | it Data, can | be parity bit |                |               |               |            |

|       | Legend:                                            |                 |              |               |                |               |               |            |

|       | R = Readabl                                        | le bit          | W = Wr       | itable bit    | U = Unimpl     | emented b     | it, read as ' | 0'         |

|       | - n = Value a                                      | at POR          | '1' = Bit    | is set        | '0' = Bit is c | leared        | x = Bit is ur | nknown     |

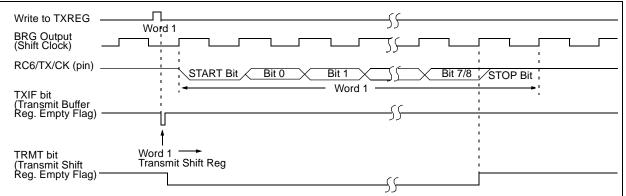

When setting up an Asynchronous Transmission, follow these steps:

- 1. Initialize the SPBRG register for the appropriate baud rate. If a high speed baud rate is desired, set bit BRGH (Section 9.1).

- 2. Enable the asynchronous serial port by clearing bit SYNC and setting bit SPEN.

- 3. If interrupts are desired, then set enable bit TXIE.

- 4. If 9-bit transmission is desired, then set transmit bit TX9.

- 5. Enable the transmission by setting bit TXEN, which will also set bit TXIF.

- 6. If 9-bit transmission is selected, the ninth bit should be loaded in bit TX9D.

- 7. Load data to the TXREG register (starts transmission).

- 8. If using interrupts, ensure that GIE and PEIE (bits 7 and 6) of the INTCON register are set.

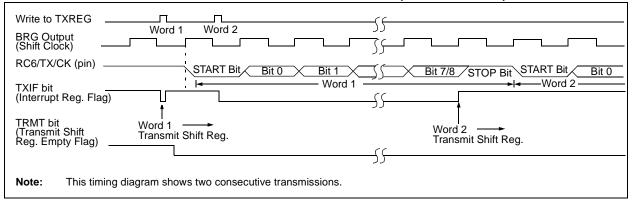

#### FIGURE 9-2: ASYNCHRONOUS MASTER TRANSMISSION

#### FIGURE 9-3: ASYNCHRONOUS MASTER TRANSMISSION (BACK TO BACK)

#### TABLE 9-5: REGISTERS ASSOCIATED WITH ASYNCHRONOUS TRANSMISSION

| Address                | Name   | Bit 7                | Bit 6    | Bit 5      | Bit 4 | Bit 3 | Bit 2  | Bit 1  | Bit 0  | Value on:<br>POR, BOR | Value on<br>all other<br>RESETS |

|------------------------|--------|----------------------|----------|------------|-------|-------|--------|--------|--------|-----------------------|---------------------------------|

| 0Bh, 8Bh,<br>10Bh,18Bh | INTCON | GIE                  | PEIE     | TOIE       | INTE  | RBIE  | TOIF   | INTF   | R0IF   | x000 0000x            | 0000 000u                       |

| 0Ch                    | PIR1   | PSPIF <sup>(1)</sup> | ADIF     | RCIF       | TXIF  | _     | CCP1IF | TMR2IF | TMR1IF | 0000 -000             | 0000 -000                       |

| 18h                    | RCSTA  | SPEN                 | RX9      | SREN       | CREN  | _     | FERR   | OERR   | RX9D   | 0000 -00x             | 0000 -00x                       |

| 19h                    | TXREG  | USART Tra            | nsmit Re | gister     |       |       |        |        |        | 0000 0000             | 0000 0000                       |

| 8Ch                    | PIE1   | PSPIE <sup>(1)</sup> | ADIE     | RCIE       | TXIE  | _     | CCP1IE | TMR2IE | TMR1IE | 0000 -000             | 0000 -000                       |

| 98h                    | TXSTA  | CSRC                 | TX9      | TXEN       | SYNC  | _     | BRGH   | TRMT   | TX9D   | 0000 -010             | 0000 -010                       |

| 99h                    | SPBRG  | Baud Rate            | Generato | r Register | •     |       |        |        |        | 0000 0000             | 0000 0000                       |

Legend: x = unknown, - = unimplemented locations read as '0'. Shaded cells are not used for asynchronous transmission.

Note 1: Bits PSPIE and PSPIF are reserved on the PIC16F870; always maintain these bits clear.

#### 9.3 USART Synchronous Master Mode

In Synchronous Master mode, the data is transmitted in a half-duplex manner (i.e., transmission and reception do not occur at the same time). When transmitting data, the reception is inhibited and vice versa. Synchronous mode is entered by setting bit SYNC (TXSTA<4>). In addition, enable bit SPEN (RCSTA<7>) is set in order to configure the RC6/TX/CK and RC7/RX/DT I/O pins to CK (clock) and DT (data) lines, respectively. The Master mode indicates that the processor transmits the master clock on the CK line. The Master mode is entered by setting bit CSRC (TXSTA<7>).

#### 9.3.1 USART SYNCHRONOUS MASTER TRANSMISSION

The USART transmitter block diagram is shown in Figure 9-6. The heart of the transmitter is the Transmit (Serial) Shift register (TSR). The Shift register obtains its data from the Read/Write Transmit Buffer register TXREG. The TXREG register is loaded with data in software. The TSR register is not loaded until the last bit has been transmitted from the previous load. As soon as the last bit is transmitted, the TSR is loaded with new data from the TXREG (if available). Once the TXREG register transfers the data to the TSR register (occurs in one TCYCLE), the TXREG is empty and interrupt bit TXIF (PIR1<4>) is set. The interrupt can be enabled/disabled by setting/clearing enable bit TXIE (PIE1<4>). Flag bit TXIF will be set, regardless of the state of enable bit TXIE and cannot be cleared in software. It will reset only when new data is loaded into the TXREG register. While flag bit TXIF indicates the status of the TXREG register, another bit TRMT (TXSTA<1>) shows the status of the TSR register. TRMT is a read only bit which is set when the TSR is empty. No interrupt logic is tied to this bit, so the user has to poll this bit in order to determine if the TSR register is empty. The TSR is not mapped in data memory, so it is not available to the user.

Transmission is enabled by setting enable bit TXEN (TXSTA<5>). The actual transmission will not occur until the TXREG register has been loaded with data. The first data bit will be shifted out on the next available rising edge of the clock on the CK line. Data out is stable around the falling edge of the synchronous clock (Figure 9-9). The transmission can also be started by first loading the TXREG register and then setting bit TXEN (Figure 9-10). This is advantageous when slow baud rates are selected, since the BRG is kept in RESET when bits TXEN, CREN and SREN are clear. Setting enable bit TXEN will start the BRG, creating a shift clock immediately. Normally, when transmission is first started, the TSR register is empty, so a transfer to the TXREG register will result in an immediate transfer to TSR, resulting in an empty TXREG. Back-to-back transfers are possible.

Clearing enable bit TXEN during a transmission will cause the transmission to be aborted and will reset the transmitter. The DT and CK pins will revert to hiimpedance. If either bit CREN or bit SREN is set during a transmission, the transmission is aborted and the DT pin reverts to a hi-impedance state (for a reception). The CK pin will remain an output if bit CSRC is set (internal clock). The transmitter logic, however, is not reset, although it is disconnected from the pins. In order to reset the transmitter, the user has to clear bit TXEN. If bit SREN is set (to interrupt an on-going transmission and receive a single word), then after the single word is received, bit SREN will be cleared and the serial port will revert back to transmitting, since bit TXEN is still set. The DT line will immediately switch from Hi-Impedance Receive mode to transmit and start driving. To avoid this, bit TXEN should be cleared.

In order to select 9-bit transmission, the TX9 (TXSTA<6>) bit should be set and the ninth bit should be written to bit TX9D (TXSTA<0>). The ninth bit must be written before writing the 8-bit data to the TXREG register. This is because a data write to the TXREG can result in an immediate transfer of the data to the TSR register (if the TSR is empty). If the TSR was empty and the TXREG was written before writing the "new" TX9D, the "present" value of bit TX9D is loaded.

Steps to follow when setting up a Synchronous Master Transmission:

- 1. Initialize the SPBRG register for the appropriate baud rate (Section 9.1).

- 2. Enable the synchronous master serial port by setting bits SYNC, SPEN and CSRC.

- 3. If interrupts are desired, set enable bit TXIE.

- 4. If 9-bit transmission is desired, set bit TX9.

- 5. Enable the transmission by setting bit TXEN.

- 6. If 9-bit transmission is selected, the ninth bit should be loaded in bit TX9D.

- 7. Start transmission by loading data to the TXREG register.

- 8. If using interrupts, ensure that GIE and PEIE (bits 7 and 6) of the INTCON register are set.

NOTES:

#### REGISTER 10-2: ADCON1 REGISTER (ADDRESS: 9Fh)

| U-0   | U-0 | R/W-0 | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|-------|-----|-------|-----|-------|-------|-------|-------|

| ADFM  | —   | —     | —   | PCFG3 | PCFG2 | PCFG1 | PCFG0 |

| bit 7 |     |       |     |       |       |       | bit 0 |

bit 7 ADFM: A/D Result Format Select bit

1 = Right justified. 6 Most Significant bits of ADRESH are read as '0'.

0 = Left justified. 6 Least Significant bits of ADRESL are read as '0'.

bit 6-4 Unimplemented: Read as '0'

bit 3-0 **PCFG3:PCFG0**: A/D Port Configuration Control bits:

| PCFG3:<br>PCFG0 | AN7 <sup>(1)</sup><br>RE2 | AN6 <sup>(1)</sup><br>RE1 | AN5 <sup>(1)</sup><br>RE0 | AN4<br>RA5 | AN3<br>RA3 | AN2<br>RA2 | AN1<br>RA1 | AN0<br>RA0 | VREF+ | VREF- | CHAN/<br>Refs <sup>(2)</sup> |

|-----------------|---------------------------|---------------------------|---------------------------|------------|------------|------------|------------|------------|-------|-------|------------------------------|

| 0000            | А                         | А                         | А                         | А          | A          | Α          | Α          | Α          | Vdd   | Vss   | 8/0                          |

| 0001            | А                         | А                         | А                         | А          | VREF+      | А          | Α          | Α          | RA3   | Vss   | 7/1                          |

| 0010            | D                         | D                         | D                         | А          | А          | А          | Α          | Α          | Vdd   | Vss   | 5/0                          |

| 0011            | D                         | D                         | D                         | А          | VREF+      | А          | Α          | Α          | RA3   | Vss   | 4/1                          |

| 0100            | D                         | D                         | D                         | D          | Α          | D          | Α          | Α          | Vdd   | Vss   | 3/0                          |

| 0101            | D                         | D                         | D                         | D          | VREF+      | D          | Α          | Α          | RA3   | Vss   | 2/1                          |

| 011x            | D                         | D                         | D                         | D          | D          | D          | D          | D          | Vdd   | Vss   | 0/0                          |

| 1000            | А                         | А                         | А                         | А          | VREF+      | VREF-      | Α          | Α          | RA3   | RA2   | 6/2                          |

| 1001            | D                         | D                         | А                         | А          | Α          | Α          | Α          | Α          | Vdd   | Vss   | 6/0                          |

| 1010            | D                         | D                         | А                         | А          | VREF+      | Α          | Α          | Α          | RA3   | Vss   | 5/1                          |

| 1011            | D                         | D                         | А                         | А          | VREF+      | VREF-      | Α          | Α          | RA3   | RA2   | 4/2                          |

| 1100            | D                         | D                         | D                         | А          | VREF+      | VREF-      | Α          | Α          | RA3   | RA2   | 3/2                          |

| 1101            | D                         | D                         | D                         | D          | VREF+      | VREF-      | Α          | А          | RA3   | RA2   | 2/2                          |

| 1110            | D                         | D                         | D                         | D          | D          | D          | D          | Α          | Vdd   | Vss   | 1/0                          |

| 1111            | D                         | D                         | D                         | D          | VREF+      | VREF-      | D          | Α          | RA3   | RA2   | 1/2                          |

A = Analog input D = Digital I/O

Note 1: These channels are not available on the PIC16F870 device.

**2:** This column indicates the number of analog channels available as A/D inputs and the number of analog channels used as voltage reference inputs.

| Legend:            |                  |                      |                    |

|--------------------|------------------|----------------------|--------------------|

| R = Readable bit   | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

| - n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

The ADRESH:ADRESL registers contain the 10-bit result of the A/D conversion. When the A/D conversion is complete, the result is loaded into this A/D result register pair, the GO/DONE bit (ADCON0<2>) is cleared and the A/D interrupt flag bit ADIF is set. The block diagram of the A/D module is shown in Figure 10-1.

After the A/D module has been configured as desired, the selected channel must be acquired before the conversion is started. The analog input channels must have their corresponding TRIS bits selected as inputs. To determine sample time, see Section 10.1. After this acquisition time has elapsed, the A/D conversion can be started.

## 10.5 A/D Operation During SLEEP

The A/D module can operate during SLEEP mode. This requires that the A/D clock source be set to RC (ADCS1:ADCS0 = 11). When the RC clock source is selected, the A/D module waits one instruction cycle before starting the conversion. This allows the SLEEP instruction to be executed, which eliminates all digital switching noise from the conversion. When the conversion is completed, the GO/DONE bit will be cleared and the result loaded into the ADRES register. If the A/D interrupt is enabled, the device will wake-up from SLEEP. If the A/D interrupt is not enabled, the ADON bit will remain set.

When the A/D clock source is another clock option (not RC), a SLEEP instruction will cause the present conversion to be aborted and the A/D module to be turned off, though the ADON bit will remain set.

Turning off the A/D places the A/D module in its lowest current consumption state.

| Note: | For the A/D module to operate in SLEEP,   |

|-------|-------------------------------------------|

|       | the A/D clock source must be set to RC    |

|       | (ADCS1:ADCS0 = 11). To allow the con-     |

|       | version to occur during SLEEP, ensure the |

|       | SLEEP instruction immediately follows the |

|       | instruction that sets the GO/DONE bit.    |

### 10.6 Effects of a RESET

A device RESET forces all registers to their RESET state. This forces the A/D module to be turned off, and any conversion is aborted. All A/D input pins are configured as analog inputs.

The value that is in the ADRESH:ADRESL registers is not modified for a Power-on Reset. The ADRESH:ADRESL registers will contain unknown data after a Power-on Reset.

| Address               | Name   | Bit 7                | Bit 6      | Rit 5   Rit 4   Rit 3   Rit 2   Rit 1   Rit 0 |                                                     |           |           | Value on<br>POR, BOR | V <u>alue o</u> n<br>MCLR,<br>WDT |           |           |

|-----------------------|--------|----------------------|------------|-----------------------------------------------|-----------------------------------------------------|-----------|-----------|----------------------|-----------------------------------|-----------|-----------|

| 0Bh,8Bh,<br>10Bh,18Bh | INTCON | GIE                  | PEIE       | TOIE                                          | INTE                                                | RBIE      | TOIF      | INTF                 | RBIF                              | 0000 000x | 0000 000u |

| 0Ch                   | PIR1   | PSPIF <sup>(1)</sup> | ADIF       | RCIF                                          | TXIF                                                | —         | CCP1IF    | TMR2IF               | TMR1IF                            | 0000 -000 | 0000 -000 |

| 8Ch                   | PIE1   | PSPIE <sup>(1)</sup> | ADIE       | RCIE                                          | RCIE TXIE — CCP1IE TMR2IE TMR1IE C                  |           |           |                      |                                   | 0000 -000 | 0000 -000 |

| 1Eh                   | ADRESH | A/D Resul            | t Register | High Byt                                      |                                                     | xxxx xxxx | uuuu uuuu |                      |                                   |           |           |

| 9Eh                   | ADRESL | A/D Resul            | t Register | Low Byte                                      |                                                     | xxxx xxxx | uuuu uuuu |                      |                                   |           |           |

| 1Fh                   | ADCON0 | ADCS1                | ADCS0      | CHS2                                          | CHS2 CHS1 CHS0 GO/DONE — ADON                       |           |           |                      |                                   |           | 0000 00-0 |

| 9Fh                   | ADCON1 | ADFM                 | —          | _                                             | PCFG3 PCFG2 PCFG1 PCFG0                             |           |           |                      | 0-0000                            | 0- 0000   |           |

| 85h                   | TRISA  | _                    | —          | PORTA                                         | Data Directio                                       | 11 1111   | 11 1111   |                      |                                   |           |           |

| 05h                   | PORTA  |                      | —          | PORTA                                         | PORTA Data Latch when written: PORTA pins when read |           |           |                      |                                   |           | Ou 0000   |

| 89h <sup>(1)</sup>    | TRISE  | IBF                  | OBF        | IBOV                                          | PSPMODE                                             | —         | PORTE Dat | ta Directior         | n bits                            | 0000 -111 | 0000 -111 |

| 09h <sup>(1)</sup>    | PORTE  |                      | _          | —                                             | _                                                   | —         | RE2       | RE1                  | RE0                               | xxx       | uuu       |

TABLE 10-2: REGISTERS/BITS ASSOCIATED WITH A/D

Legend: x = unknown, u = unchanged, - = unimplemented, read as '0'. Shaded cells are not used for A/D conversion.

**Note 1:** These registers/bits are not available on the 28-pin devices.

# REGISTER 11-1: CONFIGURATION WORD (ADDRESS 2007h)<sup>(1)</sup>

| REGIS    | STER 1 | 1-1: C               | ONFIGU     | JRATI   | ON W    | ORD      | (ADDRES                    | SS 200      | 7h) <sup>(1)</sup> |              |          |                     |       |

|----------|--------|----------------------|------------|---------|---------|----------|----------------------------|-------------|--------------------|--------------|----------|---------------------|-------|

| CP1      | CP0    | DEBUG                | —          | WRT     | CPD     | LVP      | BOREN                      | CP1         | CP0                | PWRTEN       | WDTEN    | FOSC1               | FOSC0 |

| bit 13   |        |                      |            |         |         |          |                            | •           |                    |              |          |                     | bit 0 |

| bit 13-' | 12,    | CP1:CP0              | : FLASH    | l Progr | am Me   | mory (   | Code Prote                 | ection bi   | ts <sup>(2)</sup>  |              |          |                     |       |

| bit 5-4  |        | 11 = Cod             |            |         |         |          |                            |             |                    |              |          |                     |       |

|          |        | 10 = Not             |            |         |         |          |                            |             |                    |              |          |                     |       |

|          |        | 01 = Not<br>00 = Cod |            |         |         |          |                            |             |                    |              |          |                     |       |

| bit 11   |        | DEBUG:               | •          |         |         | lode     |                            |             |                    |              |          |                     |       |

| bit II   |        |                      |            |         | 00      |          | 6 and RB7                  | are der     | neral pu           | Irpose I/O p | oins     |                     |       |

|          |        |                      |            | 00      |         |          |                            | 0           |                    | to the debu  |          |                     |       |

| bit 10   |        | Unimple              | mented:    | Read    | as '1'  |          |                            |             |                    |              |          |                     |       |

| bit 9    |        | WRT: FL              | ASH Pro    | gram N  | Nemory  | Write    | Enable                     |             |                    |              |          |                     |       |

|          |        | 1 = Unpre            | otected p  | orogran | n mem   | ory ma   | ay be writte               | n to by     | EECO               | N control    |          |                     |       |

|          |        | 0 = Unpre            | otected p  | orograr | n mem   | ory ma   | ay not be w                | ritten to   | by EE              | CON control  | ol       |                     |       |

| bit 8    |        | CPD: Da              | ta EE Me   | emory   | Code P  | rotecti  | ion                        |             |                    |              |          |                     |       |

|          |        | 1 = Code             | •          |         |         |          | 4 4I                       |             |                    |              |          |                     |       |

| L:4 7    |        | 0 = Data             |            |         | •       |          |                            | E a a la La | L 14               |              |          |                     |       |

| bit 7    |        |                      | -          |         |         |          | ogramming                  |             |                    | anablad      |          |                     |       |

|          |        |                      |            |         |         |          | low voltage<br>nust be use |             |                    |              |          |                     |       |

| bit 6    |        | BOREN:               |            |         |         |          |                            | - · · · F · | - 3                |              |          |                     |       |

|          |        | 1 = BOR              |            |         |         |          |                            |             |                    |              |          |                     |       |

|          |        | 0 <b>= BOR</b>       | disabled   | l       |         |          |                            |             |                    |              |          |                     |       |

| bit 3    |        | PWRTEN               | : Power    | -up Tin | ner Ena | able bit | t(3)                       |             |                    |              |          |                     |       |

|          |        | 1 = PWRT disabled    |            |         |         |          |                            |             |                    |              |          |                     |       |

|          |        | 0 = PWR              |            |         |         |          |                            |             |                    |              |          |                     |       |

| bit 2    |        | WDTEN:               |            | 0       | er Enat | ole bit  |                            |             |                    |              |          |                     |       |

|          |        | 1 = WDT<br>0 = WDT   |            |         |         |          |                            |             |                    |              |          |                     |       |

| bit 1-0  |        | FOSC1:F              |            |         | or Sole | oction I | hite                       |             |                    |              |          |                     |       |

| bit 1-0  |        | 11 = RC              |            |         |         | CUOIT    | 0113                       |             |                    |              |          |                     |       |

|          |        | 10 = HS              |            |         |         |          |                            |             |                    |              |          |                     |       |

|          |        | 01 = XT (            |            |         |         |          |                            |             |                    |              |          |                     |       |

|          |        | 00 = LP (            | oscillator |         |         |          |                            |             |                    |              |          |                     |       |

|          |        | Legend:              |            |         |         |          |                            |             |                    |              |          |                     | ]     |

|          |        | R = Read             | lahla hit  |         | ۱.      | <u> </u> | ritable bit                |             | – Linim            | nplemented   | hit read | as 'O'              |       |

|          |        | -n = Valu            |            | R       |         |          | t is set                   |             |                    | s cleared    |          | as u<br>it is unkno |       |

|          |        | -n = valt            | ie al PUI  | N       |         | i = Dl   | 115 561                    | 0           | = DIL I            | sciedieu     | x = B    |                     |       |

|          |        |                      |            |         |         |          |                            |             |                    |              |          |                     |       |

**Note 1:** The erased (unprogrammed) value of the configuration word is 3FFFh.

- 2: All of the CP1:CP0 pairs have to be given the same value to enable the code protection scheme listed.

- **3:** Enabling Brown-out Reset automatically enables Power-up Timer (PWRT), regardless of the value of bit PWRTEN. Ensure the Power-up Timer is enabled any time Brown-out Reset is enabled.

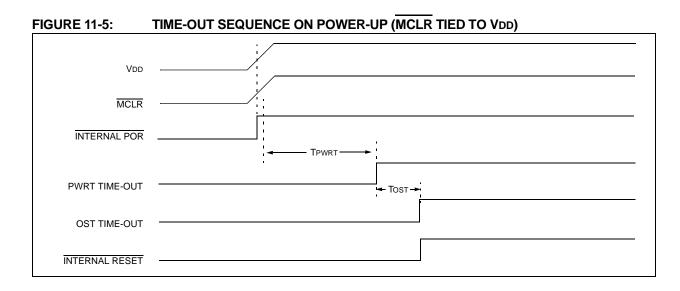

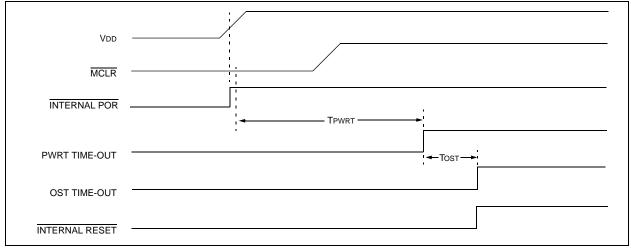

FIGURE 11-6: TIME-OUT SEQUENCE ON POWER-UP (MCLR NOT TIED TO VDD): CASE 1

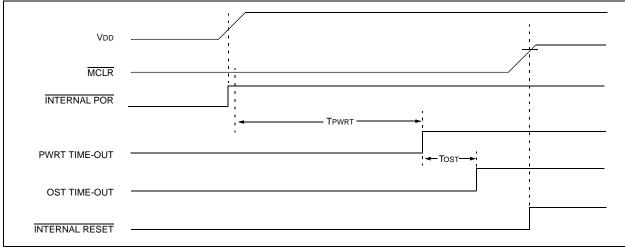

FIGURE 11-7: TIME-OUT SEQUENCE ON POWER-UP (MCLR NOT TIED TO VDD): CASE 2

| ; Q1 Q2 Q3 Q4; Q1 Q2 Q3 Q<br>OSC1 ////////////////////////////////////                                                                                                                             |                       |                   | ; Q1  Q2  Q3  Q4;<br>;/~_/~_/~_/<br>;// | 011 021 031 04;<br>    | Q1 Q2 Q3 Q4<br>\/\/\/\ |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|-------------------|-----------------------------------------|------------------------|------------------------|

| INTF Flag<br>(INTCON<1>)                                                                                                                                                                           |                       |                   | Interrupt Latency                       | 2)                     |                        |

| GIE bit<br>(INTCON<7>)                                                                                                                                                                             | Processor in<br>SLEEP | <br>              |                                         | i                      | 1<br>1<br>1            |

| INSTRUCTION FLOW                                                                                                                                                                                   |                       | l<br>l            | 1 I<br>1 I                              | 1                      | I<br>I                 |

| PC X PC X PC+1                                                                                                                                                                                     | X PC+2                | PC+2              | X PC + 2 X                              | <u>    0004h     X</u> | 0005h                  |

| $ \begin{array}{l} \text{Instruction} \\ \text{Fetched} \end{array} \Big\{ \begin{array}{l} \text{Inst}(\text{PC}) = \text{SLEEP} & \text{Inst}(\text{PC}+1) \end{array} \Big\} \\ \end{array} \\$ |                       | Inst(PC + 2)      | 1 1<br>1 1<br>1 1                       | Inst(0004h)            | Inst(0005h)            |

| Instruction<br>Executed { Inst(PC - 1) SLEEP                                                                                                                                                       |                       | Inst(PC + 1)      | Dummy cycle                             | Dummy cycle            | Inst(0004h)            |

| Note 1: XT, HS or LP Oscillator mode assume<br>2: Tost = 1024 Tosc (drawing not to sca                                                                                                             |                       | e there for RC Os | c mode.                                 |                        |                        |

3: GIE = 1 assumed. In this case, after wake-up, the processor jumps to the interrupt routine. If GIE = 0, execution will continue in-line.

4: CLKO is not available in these Osc modes, but shown here for timing reference.

### 11.14 In-Circuit Debugger

When the DEBUG bit in the configuration word is programmed to a '0', the In-Circuit Debugger functionality is enabled. This function allows simple debugging functions when used with MPLAB<sup>®</sup> ICD. When the microcontroller has this feature enabled, some of the resources are not available for general use. Table 11-8 shows which features are consumed by the background debugger.

|  | TABLE 11-8: | DEBUGGER RESOURCES |

|--|-------------|--------------------|

|--|-------------|--------------------|

| I/O pins       | RB6, RB7                    |

|----------------|-----------------------------|

| Stack          | 1 level                     |

| Program Memory | Address 0000h must be NOP   |

|                | Last 100h words             |

| Data Memory    | 0x070 (0x0F0, 0x170, 0x1F0) |

|                | 0x1EB - 0x1EF               |

To use the In-Circuit Debugger function of the microcontroller, the design must implement In-Circuit Serial Programming connections to MCLR/VPP, VDD, GND, RB7 and RB6. This will interface to the In-Circuit Debugger module available from Microchip, or one of the third party development tool companies.

## 11.15 Program Verification/Code Protection

If the code protection bit(s) have not been programmed, the on-chip program memory can be read out for verification purposes.

## 11.16 ID Locations

Four memory locations (2000h - 2003h) are designated as ID locations, where the user can store checksum or other code identification numbers. These locations are not accessible during normal execution, but are readable and writable during program/verify. It is recommended that only the 4 Least Significant bits of the ID location are used.

# APPENDIX A: REVISION HISTORY

# **Revision A (December 1999)**

Original data sheet for the PIC16F870/871 family.

# **Revision B (April 2003)**

This revision includes the DC and AC Characteristics Graphs and Tables. The Electrical Specifications in Section 14.0 have been updated and there have been minor corrections to the data sheet text.

## **Revision C (January 2013)**

Added a note to each package outline drawing.

#### TABLE B-1: DEVICE DIFFERENCES

#### APPENDIX B: DEVICE DIFFERENCES

The differences between the devices listed in this data sheet are shown in Table B-1.

| Feature                         | PIC16F870              | PIC16F871                      |

|---------------------------------|------------------------|--------------------------------|

| On-chip Program Memory (Kbytes) | 2K                     | 2K                             |

| Data Memory (bytes)             | 128                    | 128                            |

| Boot Block (bytes)              | 2048                   | 512                            |

| Timer1 Low Power Option         | Yes                    | No                             |

| I/O Ports                       | Ports A, B, C          | Ports A, B, C, D, E            |

| A/D Channels                    | 5                      | 8                              |

| External Memory Interface       | No                     | No                             |

| Package Types                   | 28-pin DIP, SOIC, SSOP | 40-pin PDIP, 44-pin PLCC, TQFP |

| Interrupts, Enable Bits                 |   |

|-----------------------------------------|---|

| Global Interrupt Enable (GIE Bit)       | 6 |

| Interrupt-on-Change (RB7:RB4) Enable    |   |

| (RBIE Bit)18, 9                         | 7 |

| Peripheral Interrupt Enable (PEIE Bit)1 | 8 |

| RB0/INT Enable (INTE Bit)1              | 8 |

| TMR0 Overflow Enable (T0IE Bit)1        | 8 |

| Interrupts, Flag Bits                   |   |

| Interrupt-on-Change (RB7:RB4)           |   |

| Flag (RBIF Bit)18, 35, 9                | 7 |

| RB0/INT Flag (INTF Bit)1                | 8 |

| TMR0 Overflow Flag (T0IF Bit)9          | 7 |

| L                                       |   |

| Loading of PC2                            | 4 |

|-------------------------------------------|---|

| Low Voltage In-Circuit Serial Programming | 2 |

### Μ

| Master Clear (MCLR)                          |        |

|----------------------------------------------|--------|

| MCLR Reset, Normal Operation                 | 91, 93 |

| MCLR Reset, SLEEP                            | 91, 93 |

| MCLR/VPP/THV Pin                             | 7, 8   |

| Memory Organization                          |        |

| Data Memory                                  | 11     |

| Program Memory                               | 11     |

| Migration from High-End to Enhanced Devices  | 159    |

| Migration from Mid-Range to Enhanced Devices | 158    |

| MPLAB ASM30 Assembler, Linker, Librarian     | 112    |

| MPLAB ICD 2 In-Circuit Debugger              | 113    |

| MPLAB ICE 2000 High Performance Universal    |        |

| In-Circuit Emulator                          | 113    |

| MPLAB ICE 4000 High Performance Universal    |        |

| In-Circuit Emulator                          | 113    |

| MPLAB Integrated Development                 |        |

| Environment Software                         | 111    |

| MPLINK Object Linker/MPLIB Object Librarian  | 112    |

|                                              |        |

# ο

| OPCODE Field Descriptions      |            |

|--------------------------------|------------|

| OPTION                         |            |

| OPTION Register                |            |

| OPTION_REG Register            |            |

| INTEDG Bit                     |            |

|                                |            |

| <u>PSA B</u> it                |            |

| RBPU Bit                       |            |

| T0CS Bit                       |            |

| T0SE Bit                       |            |

| OSC1/CLKI Pin                  |            |

| OSC2/CLKO Pin                  | 7, 8       |

| Oscillator Configuration       |            |

| HS                             |            |

| LP                             |            |

| RC                             | 89, 90, 92 |

| XT                             |            |

| Oscillator, WDT                |            |

| Oscillators                    |            |

| Capacitor Selection            |            |

| Crystal and Ceramic Resonators | 89         |

| RC                             |            |

| <b>Ν</b> Ο                     |            |

## Ρ

| 1                                    |

|--------------------------------------|

| Packaging149                         |

| Marking Information 149              |

| Parallel Slave Port (PSP)            |

| Associated Registers                 |

| RE0/RD/AN5 Pin                       |

|                                      |

| RE1/WR/AN6 Pin                       |

| RE2/CS/AN7 Pin 41, 42                |

| Select (PSPMODE Bit) 38, 39, 40, 42  |

| PCL Register 13, 14, 15, 24          |

| PCLATH Register 13, 14, 15, 24       |

| PCON Register                        |

| BOR Bit                              |

| POR Bit                              |

| PICkit 1 FLASH Starter Kit           |

| PICSTART Plus Development Programmer |

|                                      |

| PIE1 Register                        |

| PIE2 Register                        |

| Pinout Descriptions                  |

| PIC16F8707                           |

| PIC16F871 8                          |

| PIR1 Register                        |

| PIR2 Register                        |

| POP                                  |

| POR. See Power-on Reset.             |

| PORTA                                |

| Associated Registers                 |

|                                      |

| PORTA Register                       |

| RA0/AN0 Pin7, 8                      |

| RA1/AN1 Pin7, 8                      |

| RA2/AN2/VREF- Pin                    |

| RA2/AN2/VREF- Pin                    |

| RA3/AN3/VREF+ Pin7                   |

| RA3/AN3/VREF+ Pin                    |

| RA4/T0CKI Pin                        |

| RA5/AN4 Pin                          |

|                                      |

| TRISA Register                       |

| PORTA Register                       |

| PORTB 7, 8                           |

| PORTB Register                       |

| Pull-up Enable (RBPU Bit) 17         |

| RB0/INT Edge Select (INTEDG Bit) 17  |

| RB0/INT Pin7, 8                      |

| RB0/INT Pin, External97              |

| RB1 Pin                              |

|                                      |

| RB2 Pin                              |

| RB3/PGM Pin                          |

| RB4 Pin                              |

| RB5 Pin7, 8                          |

| RB6/PGC Pin7, 8                      |

| RB7/PGD Pin7, 8                      |

| RB7:RB4 Interrupt-on-Change          |

| RB7:RB4 Interrupt-on-Change          |

| Enable (RBIE Bit) 18, 97             |

| RB7:RB4 Interrupt-on-Change          |

| Flag (RBIF Bit)                      |

|                                      |

| TRISB Register                       |

| PORTB Register 13, 15                |

# THE MICROCHIP WEB SITE

Microchip provides online support via our WWW site at www.microchip.com. This web site is used as a means to make files and information easily available to customers. Accessible by using your favorite Internet browser, the web site contains the following information:

- Product Support Data sheets and errata, application notes and sample programs, design resources, user's guides and hardware support documents, latest software releases and archived software

- General Technical Support Frequently Asked Questions (FAQ), technical support requests, online discussion groups, Microchip consultant program member listing

- Business of Microchip Product selector and ordering guides, latest Microchip press releases, listing of seminars and events, listings of Microchip sales offices, distributors and factory representatives

# CUSTOMER CHANGE NOTIFICATION SERVICE

Microchip's customer notification service helps keep customers current on Microchip products. Subscribers will receive e-mail notification whenever there are changes, updates, revisions or errata related to a specified product family or development tool of interest.

To register, access the Microchip web site at www.microchip.com. Under "Support", click on "Customer Change Notification" and follow the registration instructions.

# **CUSTOMER SUPPORT**

Users of Microchip products can receive assistance through several channels:

- Distributor or Representative

- Local Sales Office

- Field Application Engineer (FAE)

- Technical Support