Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Product Status             | Active                                                                    |

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 20MHz                                                                     |

| Connectivity               | UART/USART                                                                |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                     |

| Number of I/O              | 22                                                                        |

| Program Memory Size        | 3.5KB (2K x 14)                                                           |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 64 x 8                                                                    |

| RAM Size                   | 128 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                 |

| Data Converters            | A/D 5x10b                                                                 |

| Oscillator Type            | External                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                            |

| Supplier Device Package    | 28-SOIC                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf870-i-so |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 3.0 DATA EEPROM AND FLASH PROGRAM MEMORY

The Data EEPROM and FLASH Program Memory are readable and writable during normal operation over the entire VDD range. A bulk erase operation may not be issued from user code (which includes removing code protection). The data memory is not directly mapped in the register file space. Instead, it is indirectly addressed through the Special Function Registers (SFR).

There are six SFRs used to read and write the program and data EEPROM memory. These registers are:

- EECON1

- EECON2

- EEDATA

- EEDATH

- EEADR

- EEADRH

The EEPROM data memory allows byte read and write. When interfacing to the data memory block, EEDATA holds the 8-bit data for read/write and EEADR holds the address of the EEPROM location being accessed. The registers EEDATH and EEADRH are not used for data EEPROM access. The PIC16F870/871 devices have 64 bytes of data EEPROM with an address range from 0h to 3Fh.

The EEPROM data memory is rated for high erase/ write cycles. The write time is controlled by an on-chip timer. The write time will vary with voltage and temperature, as well as from chip-to-chip. Please refer to the specifications for exact limits.

The program memory allows word reads and writes. Program memory access allows for checksum calculation and calibration table storage. A byte or word write automatically erases the location and writes the new data (erase before write). Writing to program memory will cease operation until the write is complete. The program memory cannot be accessed during the write, therefore code cannot execute. During the write operation, the oscillator continues to clock the peripherals, and therefore, they continue to operate. Interrupt events will be detected and essentially "queued" until the write is completed. When the write completes, the next instruction in the pipeline is executed and the branch to the interrupt vector address will occur.

When interfacing to the program memory block, the EEDATH:EEDATA registers form a two-byte word, which holds the 14-bit data for read/write. The EEADRH:EEADR registers form a two-byte word, which holds the 13-bit address of the FLASH location being accessed. The PIC16F870/871 devices have 2K words of program FLASH with an address range from 0h to 7FFh. The unused upper bits in both the EEDATH and EEDATA registers all read as '0's.

The value written to program memory does not need to be a valid instruction. Therefore, up to 14-bit numbers can be stored in memory for use as calibration parameters, serial numbers, packed 7-bit ASCII, etc. Executing a program memory location containing data that forms an invalid instruction results in a NOP.

## 3.1 EEADR

The address registers can address up to a maximum of 256 bytes of data EEPROM or up to a maximum of 8K words of program FLASH. However, the PIC16F870/871 have 64 bytes of data EEPROM and 2K words of program FLASH.

When selecting a program address value, the MSByte of the address is written to the EEADRH register and the LSByte is written to the EEADR register. When selecting a data address value, only the LSByte of the address is written to the EEADR register.

On the PIC16F870/871 devices, the upper two bits of the EEADR must always be cleared to prevent inadvertent access to the wrong location in data EEPROM. This also applies to the program memory. The upper five MSbits of EEADRH must always be clear during program FLASH access.

## 3.2 EECON1 and EECON2 Registers

The EECON1 register is the control register for configuring and initiating the access. The EECON2 register is not a physically implemented register, but is used exclusively in the memory write sequence to prevent inadvertent writes.

There are many bits used to control the read and write operations to EEPROM data and FLASH program memory. The EEPGD bit determines if the access will be a program or data memory access. When clear, any subsequent operations will work on the EEPROM data memory. When set, all subsequent operations will operate in the program memory.

Read operations only use one additional bit, RD, which initiates the read operation from the desired memory location. Once this bit is set, the value of the desired memory location will be available in the data registers. This bit cannot be cleared by firmware. It is automatically cleared at the end of the read operation. For EEPROM data memory reads, the data will be available in the EEDATA register in the very next instruction cycle after the RD bit is set. For program memory reads, the data will be loaded into the EEDATH:EEDATA registers, following the second instruction after the RD bit is set.

Write operations have two control bits, WR and WREN, and two status bits, WRERR and EEIF. The WREN bit is used to enable or disable the write operation. When WREN is clear, the write operation will be disabled. Therefore, the WREN bit must be set before executing a write operation. The WR bit is used to initiate the write operation. It also is automatically cleared at the end of the write operation. The interrupt flag EEIF is used to determine when the memory write completes. This flag must be cleared in software before setting the WR bit. For EEPROM data memory, once the WREN bit and the WR bit have been set, the desired memory address in EEADR will be erased, followed by a write of the data in EEDATA. This operation takes place in parallel with the microcontroller continuing to execute normally. When the write is complete, the EEIF flag bit will be set. For program memory, once the WREN bit and the WR bit have been set, the microcontroller will cease to execute instructions. The desired memory location pointed to by EEADRH:EEADR will be erased. Then, the data value in EEDATH:EEDATA will be programmed. When complete, the EEIF flag bit will be set and the microcontroller will continue to execute code.

The WRERR bit is used to indicate when the PIC16F870/871 devices have been reset during a write operation. WRERR should be cleared after Power-on Reset. Thereafter, it should be checked on any other RESET. The WRERR bit is set when a write operation is interrupted by a MCLR Reset, or a WDT Time-out Reset, during normal operation. In these situations, following a RESET, the user should check the WRERR bit and rewrite the memory location, if set. The contents of the data registers, address registers and EEPGD bit are not affected by either MCLR Reset, or WDT Time-out Reset, during normal operation.

## REGISTER 3-1: EECON1 REGISTER (ADDRESS: 18Ch)

- n = Value at POR

|         | R/W-x        | U-0                                                                                                                                      | U-0          | U-0          | R/W-x          | R/W-0       | R/S-0       | R/S-0       |  |  |  |  |  |  |

|---------|--------------|------------------------------------------------------------------------------------------------------------------------------------------|--------------|--------------|----------------|-------------|-------------|-------------|--|--|--|--|--|--|

|         | EEPGD        | _                                                                                                                                        | _            | _            | WRERR          | WREN        | WR          | RD          |  |  |  |  |  |  |

|         | bit 7        |                                                                                                                                          |              |              | •              |             |             | bit 0       |  |  |  |  |  |  |

|         |              |                                                                                                                                          |              |              |                |             |             |             |  |  |  |  |  |  |

| bit 7   | EEPGD: PI    | rogram/Data                                                                                                                              | a EEPROM     | Select bit   |                |             |             |             |  |  |  |  |  |  |

|         | 1 = Access   | 1 = Accesses program memory                                                                                                              |              |              |                |             |             |             |  |  |  |  |  |  |

|         |              | = Accesses data memory                                                                                                                   |              |              |                |             |             |             |  |  |  |  |  |  |

|         | (This bit ca | This bit cannot be changed while a read or write operation is in progress.)                                                              |              |              |                |             |             |             |  |  |  |  |  |  |

| bit 6-4 | Unimplem     | ented: Rea                                                                                                                               | d as '0'     |              |                |             |             |             |  |  |  |  |  |  |

| bit 3   | WRERR: E     | EPROM Er                                                                                                                                 | ror Flag bit |              |                |             |             |             |  |  |  |  |  |  |

|         | 1 = A write  | e operation                                                                                                                              | is prematur  | ely terminat | ed (any MCLR   | Reset or a  | ny WDT Re   | eset during |  |  |  |  |  |  |

|         |              | l operation)                                                                                                                             |              |              |                |             |             |             |  |  |  |  |  |  |

|         | 0 = The w    | rite operatio                                                                                                                            | n complete   | d            |                |             |             |             |  |  |  |  |  |  |

| bit 2   | WREN: EE     | PROM Writ                                                                                                                                | e Enable bi  | t            |                |             |             |             |  |  |  |  |  |  |

|         |              | write cycles                                                                                                                             |              |              |                |             |             |             |  |  |  |  |  |  |

|         | 0 = Inhibits | write to the                                                                                                                             | EEPROM       |              |                |             |             |             |  |  |  |  |  |  |

| bit 1   | WR: Write    | Control bit                                                                                                                              |              |              |                |             |             |             |  |  |  |  |  |  |

|         |              | -                                                                                                                                        |              |              | by hardware on | ce write is | complete.   | The WR bit  |  |  |  |  |  |  |

|         |              |                                                                                                                                          | ,            | n software.) |                |             |             |             |  |  |  |  |  |  |

|         |              | cycle to the                                                                                                                             | EEPROM IS    | s complete   |                |             |             |             |  |  |  |  |  |  |

| bit 0   | RD: Read (   |                                                                                                                                          |              |              |                |             |             |             |  |  |  |  |  |  |

|         |              | <ul> <li>1 = Initiates an EEPROM read. (RD is cleared in hardware. The RD bit can only be set (not<br/>cleared) in software.)</li> </ul> |              |              |                |             |             |             |  |  |  |  |  |  |

|         | 0 = Does r   | not initiate a                                                                                                                           | n EEPROM     | read         |                |             |             |             |  |  |  |  |  |  |

|         | Legend:      |                                                                                                                                          |              |              |                |             |             |             |  |  |  |  |  |  |

|         | •            | hla hit                                                                                                                                  | 10/ 1/       | Vritable hit |                | omontod L   | t road as f | 0,          |  |  |  |  |  |  |

|         | R = Reada    |                                                                                                                                          | vv = v       | Vritable bit | U = Unimpl     | emented b   | ii, read as | U           |  |  |  |  |  |  |

'1' = Bit is set

x = Bit is unknown

'0' = Bit is cleared

## 3.3 Reading the EEPROM Data Memory

Reading EEPROM data memory only requires that the desired address to access be written to the EEADR register and clear the EEPGD bit. After the RD bit is set, data will be available in the EEDATA register on the very next instruction cycle. EEDATA will hold this value until another read operation is initiated or until it is written by firmware.

The steps to reading the EEPROM data memory are:

- 1. Write the address to EEDATA. Make sure that the address is not larger than the memory size of the PIC16F870/871 devices.

- 2. Clear the EEPGD bit to point to EEPROM data memory.

- 3. Set the RD bit to start the read operation.

- 4. Read the data from the EEDATA register.

| EXAMP | 'LE 3-1: |      | EPROM DATA READ          |

|-------|----------|------|--------------------------|

| BSF   | STATUS,  | RP1  | ;                        |

|       | STATUS,  |      | ;Bank 2                  |

| MOVF  | ADDR, W  |      | ;Write address           |

| MOVWF | EEADR    |      | ;to read from            |

|       | STATUS,  | RP0  | ;Bank 3                  |

| BCF   | EECON1,  | EEPG | D ; Point to Data memory |

;Bank 2

;W = EEDATA

;Start read operation

EXAMPLE 3-1: EEPROM DATA READ

The steps to write to EEPROM data memory are:

- 1. If step 10 is not implemented, check the WR bit to see if a write is in progress.

- 2. Write the address to EEADR. Make sure that the address is not larger than the memory size of the PIC16F870/871 devices.

- 3. Write the 8-bit data value to be programmed in the EEDATA register.

- 4. Clear the EEPGD bit to point to EEPROM data memory.

- 5. Set the WREN bit to enable program operations.

- 6. Disable interrupts (if enabled).

- 7. Execute the special five instruction sequence:

- Write 55h to EECON2 in two steps (first to W, then to EECON2)

- Write AAh to EECON2 in two steps (first to W, then to EECON2)

- Set the WR bit

EXAMPLE 3-2:

- 8. Enable interrupts (if using interrupts).

- 9. Clear the WREN bit to disable program operations.

- At the completion of the write cycle, the WR bit is cleared and the EEIF interrupt flag bit is set. (EEIF must be cleared by firmware.) If step 1 is not implemented, then firmware should check for EEIF to be set, or WR to clear, to indicate the end of the program cycle.

**EEPROM DATA WRITE**

|       | FLE J-Z.  |       |                          |

|-------|-----------|-------|--------------------------|

| BSF   | STATUS, F | RP1   | ;                        |

| BSF   | STATUS, F | RP0   | ;Bank 3                  |

| BTFSC | EECON1, W | VR.   | ;Wait for                |

| GOTO  | \$-1      |       | ;write to finish         |

| BCF   | STATUS, F | RP0   | ;Bank 2                  |

| MOVF  | ADDR, W   |       | ;Address to              |

|       | EEADR     |       | ;write to                |

| MOVF  | VALUE, W  |       | ;Data to                 |

| MOVWF | EEDATA    |       | ;write                   |

| BSF   | STATUS, F | RP0   | ;Bank 3                  |

| BCF   | EECON1, E | EEPGD | ;Point to Data memory    |

| BSF   | EECON1, W | VREN  | ;Enable writes           |

|       |           |       | ;Only disable interrupts |

| BCF   | INTCON, C | JIE   | ; if already enabled,    |

|       |           |       | ;otherwise discard       |

| MOVLW | 0x55      |       | ;Write 55h to            |

| MOVWF | EECON2    |       | ;EECON2                  |

| MOVLW | 0xAA      |       | ;Write AAh to            |

| MOVWF | EECON2    |       | ; EECON2                 |

| BSF   | EECON1, V | VR.   | ;Start write operation   |

|       |           |       | ;Only enable interrupts  |

| BSF   | INTCON, C | GIE   | ; if using interrupts,   |

|       |           |       | ;otherwise discard       |

| BCF   | EECON1, W | VREN  | ;Disable writes          |

|       |           |       |                          |

3.4 Writing to the EEPROM Data Memory

EECON1, RD

EEDATA, W

STATUS, RPO

BSF

BCF

MOVF

There are many steps in writing to the EEPROM data memory. Both address and data values must be written to the SFRs. The EEPGD bit must be cleared, and the WREN bit must be set, to enable writes. The WREN bit should be kept clear at all times, except when writing to the EEPROM data. The WR bit can only be set if the WREN bit was set in a previous operation (i.e., they both cannot be set in the same operation). The WREN bit should then be cleared by firmware after the write. Clearing the WREN bit before the write actually completes will not terminate the write in progress.

Writes to EEPROM data memory must also be prefaced with a special sequence of instructions that prevent inadvertent write operations. This is a sequence of five instructions that must be executed without interruptions. The firmware should verify that a write is not in progress before starting another cycle.

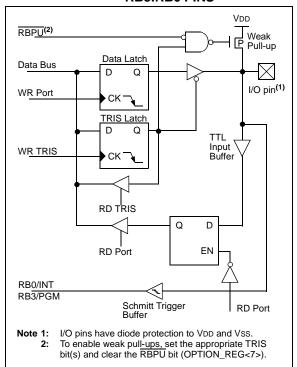

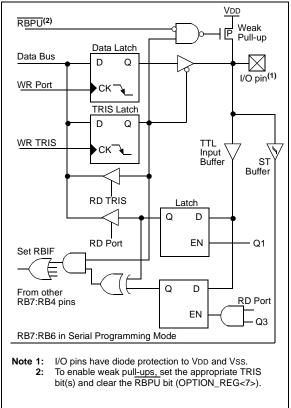

## 4.2 PORTB and the TRISB Register

PORTB is an 8-bit wide, bi-directional port. The corresponding data direction register is TRISB. Setting a TRISB bit (= 1) will make the corresponding PORTB pin an input (i.e., put the corresponding output driver in a Hi-Impedance mode). Clearing a TRISB bit (= 0) will make the corresponding PORTB pin an output (i.e., put the contents of the output latch on the selected pin).

Three pins of PORTB are multiplexed with the Low Voltage Programming function: RB3/PGM, RB6/PGC and RB7/PGD. The alternate functions of these pins are described in the Special Features Section.

Each of the PORTB pins has a weak internal pull-up. A single control bit can turn on all the pull-ups. This is performed by clearing bit RBPU (OPTION\_REG<7>). The weak pull-up is automatically turned off when the port pin is configured as an output. The pull-ups are disabled on a Power-on Reset.

Four of PORTB's pins, RB7:RB4, have an interrupt-onchange feature. Only pins configured as inputs can cause this interrupt to occur (i.e., any RB7:RB4 pin configured as an output is excluded from the interrupton-change comparison). The input pins (of RB7:RB4) are compared with the old value latched on the last read of PORTB. The "mismatch" outputs of RB7:RB4 are OR'ed together to generate the RB Port Change Interrupt with flag bit RBIF (INTCON<0>). This interrupt can wake the device from SLEEP. The user, in the Interrupt Service Routine, can clear the interrupt in the following manner:

- a) Any read or write of PORTB. This will end the mismatch condition.

- b) Clear flag bit RBIF.

A mismatch condition will continue to set flag bit RBIF. Reading PORTB will end the mismatch condition and allow flag bit RBIF to be cleared.

The interrupt-on-change feature is recommended for wake-up on key depression operation and operations where PORTB is only used for the interrupt-on-change feature. Polling of PORTB is not recommended while using the interrupt-on-change feature.

This interrupt on mismatch feature, together with software configurable pull-ups on these four pins, allow easy interface to a keypad and make it possible for wake-up on key-depression. Refer to the Embedded Control Handbook, *"Implementing Wake-up on Key Stroke"* (AN552).

RB0/INT is an external interrupt input pin and is configured using the INTEDG bit (OPTION\_REG<6>).

RB0/INT is discussed in detail in Section 11.10.1.

## FIGURE 4-4: BLO

BLOCK DIAGRAM OF RB7:RB4 PINS

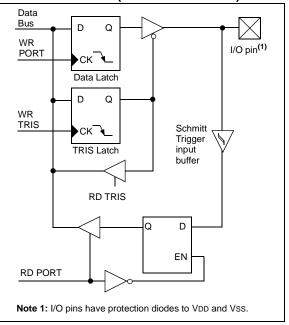

### 4.5 **PORTE and TRISE Register**

This section is not applicable to the PIC16F870.

PORTE has three pins, RE0/RD/AN5, RE1/WR/AN6 and RE2/CS/AN7, which are individually configurable as inputs or outputs. These pins have Schmitt Trigger input buffers.

I/O PORTE becomes control inputs for the microprocessor port when bit PSPMODE (TRISE<4>) is set. In this mode, the user must make sure that the TRISE<2:0> bits are set (pins are configured as digital inputs). Ensure ADCON1 is configured for digital I/O. In this mode, the input buffers are TTL.

Register 4-1 shows the TRISE register, which also controls the parallel slave port operation.

PORTE pins are multiplexed with analog inputs. When selected as an analog input, these pins will read as '0's.

TRISE controls the direction of the RE pins, even when they are being used as analog inputs. The user must make sure to keep the pins configured as inputs when using them as analog inputs.

**Note:** On a Power-on Reset, these pins are configured as analog inputs.

#### FIGURE 4-7: POR

#### PORTE BLOCK DIAGRAM (IN I/O PORT MODE)

NOTES:

## 6.4 Timer1 Operation in Asynchronous Counter Mode

If control bit  $\overline{T1SYNC}$  (T1CON<2>) is set, the external clock input is not synchronized. The timer continues to increment asynchronous to the internal phase clocks. The timer will continue to run during SLEEP and can generate an interrupt-on-overflow, which will wake-up the processor. However, special precautions in software are needed to read/write the timer (Section 6.4.1).

In Asynchronous Counter mode, Timer1 cannot be used as a time base for capture or compare operations.

#### 6.4.1 READING AND WRITING TIMER1 IN ASYNCHRONOUS COUNTER MODE

Reading TMR1H or TMR1L while the timer is running from an external asynchronous clock, will ensure a valid read (taken care of in hardware). However, the user should keep in mind that reading the 16-bit timer in two 8-bit values itself, poses certain problems, since the timer may overflow between the reads.

For writes, it is recommended that the user simply stop the timer and write the desired values. A write contention may occur by writing to the timer registers, while the register is incrementing. This may produce an unpredictable value in the timer register.

Reading the 16-bit value requires some care. Examples 12-2 and 12-3 in the PIC<sup>®</sup> Mid-Range MCU Family Reference Manual (DS33023) show how to read and write Timer1 when it is running in Asynchronous mode.

## 6.5 Timer1 Oscillator

A crystal oscillator circuit is built-in between pins T1OSI (input) and T1OSO (amplifier output). It is enabled by setting control bit, T1OSCEN (T1CON<3>). The oscillator is a low power oscillator, rated up to 200 kHz. It will continue to run during SLEEP. It is primarily intended for use with a 32 kHz crystal. Table 6-1 shows the capacitor selection for the Timer1 oscillator.

The Timer1 oscillator is identical to the LP oscillator. The user must provide a software time delay to ensure proper oscillator start-up.

## TABLE 6-1:CAPACITOR SELECTION FOR<br/>THE TIMER1 OSCILLATOR

| Osc Typ                                    | е                                                                                                       | Freq.                          | C1                  | C2       |  |  |  |  |  |  |

|--------------------------------------------|---------------------------------------------------------------------------------------------------------|--------------------------------|---------------------|----------|--|--|--|--|--|--|

| LP                                         |                                                                                                         | 32 kHz                         | 33 pF               | 33 pF    |  |  |  |  |  |  |

|                                            |                                                                                                         | 100 kHz                        | 100 kHz 15 pF       |          |  |  |  |  |  |  |

|                                            |                                                                                                         | 200 kHz                        | 15 pF               |          |  |  |  |  |  |  |

| These values are for design guidance only. |                                                                                                         |                                |                     |          |  |  |  |  |  |  |

| Crystals Tested:                           |                                                                                                         |                                |                     |          |  |  |  |  |  |  |

| 32.768 kl                                  | Ηz                                                                                                      | Epson C-00                     | 1R32.768K-A         | ± 20 PPM |  |  |  |  |  |  |

| 100 kH:                                    | Z                                                                                                       | Epson C-2 100.00 KC-P ± 20 PPM |                     |          |  |  |  |  |  |  |

| 200 kH:                                    | Z                                                                                                       | STD XTL                        | STD XTL 200.000 kHz |          |  |  |  |  |  |  |

| Note 1:<br>2:                              | Note 1: Higher capacitance increases the stability of oscillator, but also increases the start-up time. |                                |                     |          |  |  |  |  |  |  |

## 6.6 Resetting Timer1 Using a CCP Trigger Output

If the CCP1 module is configured in Compare mode to generate a "special event trigger" (CCP1M3:CCP1M0 = 1011), this signal will reset Timer1.

| Note: | The special event triggers from the CCP | י1  |

|-------|-----------------------------------------|-----|

|       | module will not set interrupt flag b    | oit |

|       | TMR1IF (PIR1<0>).                       |     |

Timer1 must be configured for either Timer or Synchronized Counter mode to take advantage of this feature. If Timer1 is running in Asynchronous Counter mode, this RESET operation may not work.

In the event that a write to Timer1 coincides with a special event trigger from CCP1, the write will take precedence.

In this mode of operation, the CCPRH:CCPRL register pair effectively becomes the period register for Timer1.

## 7.1 Timer2 Prescaler and Postscaler

The prescaler and postscaler counters are cleared when any of the following occurs:

- a write to the TMR2 register

- a write to the T2CON register

- any device RESET (POR, MCLR Reset, WDT Reset, or BOR)

TMR2 is not cleared when T2CON is written.

## 7.2 Output of TMR2

The output of TMR2 (before the postscaler) is fed to the SSP module, which optionally uses it to generate shift clock.

| TABLE 7-1: | <b>REGISTERS ASSOCIATED WITH TIMER2 AS A TIMER/COUNTER</b> |

|------------|------------------------------------------------------------|

|            |                                                            |

| Address               | Name   | Bit 7                | Bit 6                                                 | Bit 5  | Bit 4 | Bit 3 | Bit 2  | Bit 1  | Bit 0  | Value<br>POR, |      | Valu<br>all c<br>RES | other |

|-----------------------|--------|----------------------|-------------------------------------------------------|--------|-------|-------|--------|--------|--------|---------------|------|----------------------|-------|

| 0Bh,8Bh,<br>10Bh,18Bh | INTCON | GIE                  | PEIE                                                  | TOIE   | INTE  | RBIE  | TOIF   | INTF   | RBIF   | 0000          | 000x | 0000                 | 000u  |

| 0Ch                   | PIR1   | PSPIF <sup>(1)</sup> | ADIF                                                  | RCIF   | TXIF  | _     | CCP1IF | TMR2IF | TMR1IF | 0000          | -000 | 0000                 | -000  |

| 8Ch                   | PIE1   | PSPIE <sup>(1)</sup> | ADIE                                                  | RCIE   | TXIE  | -     | CCP1IE | TMR2IE | TMR1IE | 0000          | -000 | 0000                 | -000  |

| 11h                   | TMR2   | Timer2 M             | lodule's Re                                           | gister |       |       |        |        |        | 0000          | 0000 | 0000                 | 0000  |

| 12h                   | T2CON  |                      | - TOUTPS3 TOUTPS2 TOUTPS1 TOUTPS0 TMR2ON T2CKPS1 T2Ck |        |       |       |        |        |        | -000          | 0000 | -000                 | 0000  |

| 92h                   | PR2    | Timer2 P             | eriod Regis                                           | ter    |       |       |        |        |        | 1111          | 1111 | 1111                 | 1111  |

Legend: x = unknown, u = unchanged, - = unimplemented, read as '0'. Shaded cells are not used by the Timer2 module.

Note 1: Bits PSPIE and PSPIF are reserved on the PIC16F870; always maintain these bits clear.

When setting up an Asynchronous Reception, follow these steps:

- 1. Initialize the SPBRG register for the appropriate baud rate. If a high speed baud rate is desired, set bit BRGH (Section 9.1).

- 2. Enable the asynchronous serial port by clearing bit SYNC and setting bit SPEN.

- 3. If interrupts are desired, then set enable bit RCIE.

- 4. If 9-bit reception is desired, then set bit RX9.

- 5. Enable the reception by setting bit CREN.

- Flag bit RCIF will be set when reception is complete and an interrupt will be generated if enable bit RCIE is set.

- 7. Read the RCSTA register to get the ninth bit (if enabled) and determine if any error occurred during reception.

- 8. Read the 8-bit received data by reading the RCREG register.

- 9. If any error occurred, clear the error by clearing enable bit CREN.

- 10. If using interrupts, ensure that GIE and PEIE (bits 7 and 6) of the INTCON register are set.

| TABLE 9-               | ABLE 9-6: REGISTERS ASSOCIATED WITH ASTNCHRONOUS RECEPTION |                      |            |        |           |           |        |        |        |                       |                                 |  |  |

|------------------------|------------------------------------------------------------|----------------------|------------|--------|-----------|-----------|--------|--------|--------|-----------------------|---------------------------------|--|--|

| Address                | Name                                                       | Bit 7                | Bit 6      | Bit 5  | Bit 4     | Bit 3     | Bit 2  | Bit 1  | Bit 0  | Value on:<br>POR, BOR | Value on<br>all other<br>RESETS |  |  |

| 0Bh, 8Bh,<br>10Bh,18Bh | INTCON                                                     | GIE                  | PEIE       | TOIE   | INTE      | RBIE      | TOIF   | INTF   | R0IF   | 0000 000x             | 0000 000u                       |  |  |

| 0Ch                    | PIR1                                                       | PSPIF <sup>(1)</sup> | ADIF       | RCIF   | TXIF      | _         | CCP1IF | TMR2IF | TMR1IF | -000 0000             | -000 0000                       |  |  |

| 18h                    | RCSTA                                                      | SPEN                 | RX9        | SREN   | CREN      | —         | FERR   | OERR   | RX9D   | 0000 -00x             | 0000 -00x                       |  |  |

| 1Ah                    | RCREG                                                      | USART R              | eceive Reg | gister |           |           |        |        |        | 0000 0000             | 0000 0000                       |  |  |

| 8Ch                    | PIE1                                                       | PSPIE <sup>(1)</sup> | ADIE       | RCIE   | TXIE      | —         | CCP1IE | TMR2IE | TMR1IE | 0000 -000             | 0000 -000                       |  |  |

| 98h                    | TXSTA                                                      | CSRC                 | TX9        | TXEN   | SYNC      | _         | BRGH   | TRMT   | TX9D   | 0000 -010             | 0000 -010                       |  |  |

| 99h                    | SPBRG                                                      | Baud Rate            | e Generato |        | 0000 0000 | 0000 0000 |        |        |        |                       |                                 |  |  |

TABLE 9-6:

REGISTERS ASSOCIATED WITH ASYNCHRONOUS RECEPTION

Legend: x = unknown, - = unimplemented locations read as '0'. Shaded cells are not used for asynchronous reception.

Note 1: Bits PSPIE and PSPIF are reserved on the PIC16F870; always maintain these bits clear.

## 9.4 USART Synchronous Slave Mode

Synchronous Slave mode differs from the Master mode in the fact that the shift clock is supplied externally at the RC6/TX/CK pin (instead of being supplied internally in Master mode). This allows the device to transfer or receive data while in SLEEP mode. Slave mode is entered by clearing bit CSRC (TXSTA<7>).

#### 9.4.1 USART SYNCHRONOUS SLAVE TRANSMIT

The operation of the Synchronous Master and Slave modes is identical, except in the case of the SLEEP mode.

If two words are written to the TXREG and then the SLEEP instruction is executed, the following will occur:

- a) The first word will immediately transfer to the TSR register and transmit.

- b) The second word will remain in TXREG register.

- c) Flag bit TXIF will not be set.

- When the first word has been shifted out of TSR, the TXREG register will transfer the second word to the TSR and flag bit TXIF will now be set.

- e) If enable bit TXIE is set, the interrupt will wake the chip from SLEEP and if the global interrupt is enabled, the program will branch to the interrupt vector (0004h).

When setting up a Synchronous Slave Transmission, follow these steps:

- 1. Enable the synchronous slave serial port by setting bits SYNC and SPEN and clearing bit CSRC.

- 2. Clear bits CREN and SREN.

- 3. If interrupts are desired, then set enable bit TXIE.

- 4. If 9-bit transmission is desired, then set bit TX9.

- 5. Enable the transmission by setting enable bit TXEN.

- 6. If 9-bit transmission is selected, the ninth bit should be loaded in bit TX9D.

- 7. Start transmission by loading data to the TXREG register.

- 8. If using interrupts, ensure that GIE and PEIE (bits 7 and 6) of the INTCON register are set.

| Address                | Name   | Bit 7                | Bit 6                                                      | Bit 5     | Bit 4 | Bit 3 | Bit 2  | Bit 1  | Bit 0  | Value on:<br>POR, BOR | Value on<br>all other<br>RESETS |

|------------------------|--------|----------------------|------------------------------------------------------------|-----------|-------|-------|--------|--------|--------|-----------------------|---------------------------------|

| 0Bh, 8Bh,<br>10Bh,18Bh | INTCON | GIE                  | PEIE                                                       | TOIE      | INTE  | RBIE  | TOIF   | INTF   | R0IF   | 0000 000x             | 0000 000u                       |

| 0Ch                    | PIR1   | PSPIF <sup>(1)</sup> | ADIF                                                       | RCIF      | TXIF  | —     | CCP1IF | TMR2IF | TMR1IF | 0000 -000             | 0000 -000                       |

| 18h                    | RCSTA  | SPEN                 | RX9                                                        | SREN      | CREN  | ADDEN | FERR   | OERR   | RX9D   | x000 000x             | x000 000x                       |

| 19h                    | TXREG  | USART Tr             | ansmit Re                                                  | egister   |       |       |        |        |        | 0000 0000             | 0000 0000                       |

| 8Ch                    | PIE1   | PSPIE <sup>(1)</sup> | PSPIE <sup>(1)</sup> ADIE RCIE TXIE — CCP1IE TMR2IE TMR1IE |           |       |       |        |        |        | 0000 -000             | 0000 -000                       |

| 98h                    | TXSTA  | CSRC                 | TX9                                                        | TXEN      | SYNC  | _     | BRGH   | TRMT   | TX9D   | 0000 -010             | 0000 -010                       |

| 99h                    | SPBRG  | Baud Rate            | Generat                                                    | or Regist | ter   |       |        |        |        | 0000 0000             | 0000 0000                       |

#### TABLE 9-10: REGISTERS ASSOCIATED WITH SYNCHRONOUS SLAVE TRANSMISSION

Legend: x = unknown, - = unimplemented, read as '0'. Shaded cells are not used for synchronous slave transmission.

Note 1: Bits PSPIE and PSPIF are reserved on the PIC16F870; always maintain these bits clear.

NOTES:

#### REGISTER 10-2: ADCON1 REGISTER (ADDRESS: 9Fh)

| U-0   | U-0 | R/W-0 | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|-------|-----|-------|-----|-------|-------|-------|-------|

| ADFM  | —   | —     | —   | PCFG3 | PCFG2 | PCFG1 | PCFG0 |

| bit 7 |     |       |     |       |       |       | bit 0 |

bit 7 ADFM: A/D Result Format Select bit

1 = Right justified. 6 Most Significant bits of ADRESH are read as '0'.

0 = Left justified. 6 Least Significant bits of ADRESL are read as '0'.

bit 6-4 Unimplemented: Read as '0'

bit 3-0 **PCFG3:PCFG0**: A/D Port Configuration Control bits:

| PCFG3:<br>PCFG0 | AN7 <sup>(1)</sup><br>RE2 | AN6 <sup>(1)</sup><br>RE1 | AN5 <sup>(1)</sup><br>RE0 | AN4<br>RA5 | AN3<br>RA3 | AN2<br>RA2 | AN1<br>RA1 | AN0<br>RA0 | VREF+ | VREF- | CHAN/<br>Refs <sup>(2)</sup> |

|-----------------|---------------------------|---------------------------|---------------------------|------------|------------|------------|------------|------------|-------|-------|------------------------------|

| 0000            | А                         | А                         | А                         | А          | Α          | Α          | Α          | Α          | Vdd   | Vss   | 8/0                          |

| 0001            | А                         | А                         | А                         | А          | VREF+      | Α          | Α          | Α          | RA3   | Vss   | 7/1                          |

| 0010            | D                         | D                         | D                         | А          | Α          | Α          | Α          | Α          | Vdd   | Vss   | 5/0                          |

| 0011            | D                         | D                         | D                         | А          | VREF+      | Α          | Α          | Α          | RA3   | Vss   | 4/1                          |

| 0100            | D                         | D                         | D                         | D          | Α          | D          | Α          | Α          | Vdd   | Vss   | 3/0                          |

| 0101            | D                         | D                         | D                         | D          | VREF+      | D          | Α          | Α          | RA3   | Vss   | 2/1                          |

| 011x            | D                         | D                         | D                         | D          | D          | D          | D          | D          | Vdd   | Vss   | 0/0                          |

| 1000            | А                         | А                         | А                         | А          | VREF+      | VREF-      | А          | А          | RA3   | RA2   | 6/2                          |

| 1001            | D                         | D                         | А                         | А          | Α          | А          | Α          | Α          | Vdd   | Vss   | 6/0                          |

| 1010            | D                         | D                         | А                         | А          | VREF+      | А          | Α          | Α          | RA3   | Vss   | 5/1                          |

| 1011            | D                         | D                         | А                         | А          | VREF+      | VREF-      | А          | Α          | RA3   | RA2   | 4/2                          |

| 1100            | D                         | D                         | D                         | А          | VREF+      | Vref-      | А          | А          | RA3   | RA2   | 3/2                          |

| 1101            | D                         | D                         | D                         | D          | VREF+      | VREF-      | Α          | Α          | RA3   | RA2   | 2/2                          |

| 1110            | D                         | D                         | D                         | D          | D          | D          | D          | А          | Vdd   | Vss   | 1/0                          |

| 1111            | D                         | D                         | D                         | D          | VREF+      | VREF-      | D          | Α          | RA3   | RA2   | 1/2                          |

A = Analog input D = Digital I/O

Note 1: These channels are not available on the PIC16F870 device.

**2:** This column indicates the number of analog channels available as A/D inputs and the number of analog channels used as voltage reference inputs.

| Legend:            |                  |                      |                    |

|--------------------|------------------|----------------------|--------------------|

| R = Readable bit   | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

| - n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

The ADRESH:ADRESL registers contain the 10-bit result of the A/D conversion. When the A/D conversion is complete, the result is loaded into this A/D result register pair, the GO/DONE bit (ADCON0<2>) is cleared and the A/D interrupt flag bit ADIF is set. The block diagram of the A/D module is shown in Figure 10-1.

After the A/D module has been configured as desired, the selected channel must be acquired before the conversion is started. The analog input channels must have their corresponding TRIS bits selected as inputs. To determine sample time, see Section 10.1. After this acquisition time has elapsed, the A/D conversion can be started.

## 11.2 Oscillator Configurations

#### 11.2.1 OSCILLATOR TYPES

The PIC16F870/871 can be operated in four different Oscillator modes. The user can program two configuration bits (FOSC1 and FOSC0) to select one of these four modes:

- LP Low Power Crystal

- XT Crystal/Resonator

- HS High Speed Crystal/Resonator

- RC Resistor/Capacitor

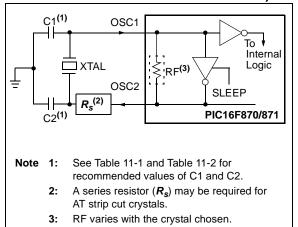

## 11.2.2 CRYSTAL OSCILLATOR/CERAMIC RESONATORS

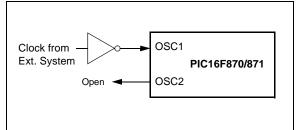

In XT, LP or HS modes, a crystal or ceramic resonator is connected to the OSC1/CLKI and OSC2/CLKO pins to establish oscillation (Figure 11-1). The PIC16F870/ 871 oscillator design requires the use of a parallel cut crystal. Use of a series cut crystal may give a frequency out of the crystal manufacturers specifications. When in XT, LP or HS modes, the device can have an external clock source to drive the OSC1/CLKI pin (Figure 11-2).

#### FIGURE 11-1: CRYSTAL/CERAMIC RESONATOR OPERATION (HS, XT OR LP OSC CONFIGURATION)

FIGURE 11-2:

#### EXTERNAL CLOCK INPUT OPERATION (HS, XT OR LP OSC CONFIGURATION)

#### TABLE 11-1: CERAMIC RESONATORS

| Ranges Tested: |          |             |             |  |  |  |

|----------------|----------|-------------|-------------|--|--|--|

| Mode           | OSC1     | OSC2        |             |  |  |  |

| XT             | 455 kHz  | 68 - 100 pF | 68 - 100 pF |  |  |  |

|                | 2.0 MHz  | 15 - 68 pF  | 15 - 68 pF  |  |  |  |

|                | 4.0 MHz  | 15 - 68 pF  | 15 - 68 pF  |  |  |  |

| HS             | 8.0 MHz  | 10 - 68 pF  | 10 - 68 pF  |  |  |  |

|                | 16.0 MHz | 10 - 22 pF  | 10 - 22 pF  |  |  |  |

**These values are for design guidance only.** See notes following Table 11-2.

| Resonators Used:                                      |                        |             |  |  |

|-------------------------------------------------------|------------------------|-------------|--|--|

| 455 kHz                                               | Panasonic EFO-A455K04B | ± 0.3%      |  |  |

| 2.0 MHz                                               | Murata Erie CSA2.00MG  | $\pm 0.5\%$ |  |  |

| 4.0 MHz                                               | Murata Erie CSA4.00MG  | $\pm 0.5\%$ |  |  |

| 8.0 MHz                                               | Murata Erie CSA8.00MT  | $\pm 0.5\%$ |  |  |

| 16.0 MHz                                              | Murata Erie CSA16.00MX | $\pm 0.5\%$ |  |  |

| All resonators used did not have built-in capacitors. |                        |             |  |  |

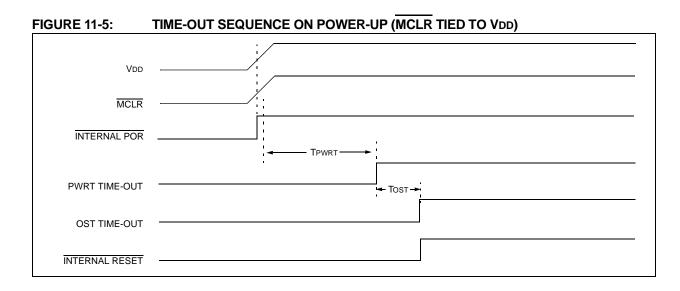

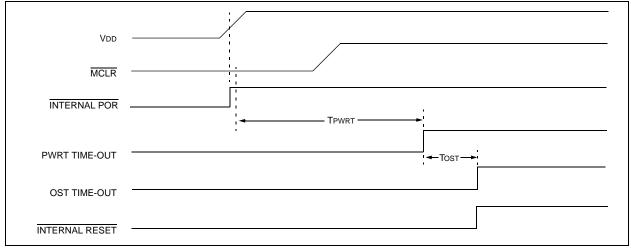

FIGURE 11-6: TIME-OUT SEQUENCE ON POWER-UP (MCLR NOT TIED TO VDD): CASE 1

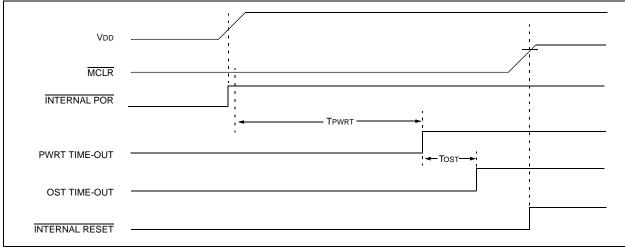

FIGURE 11-7: TIME-OUT SEQUENCE ON POWER-UP (MCLR NOT TIED TO VDD): CASE 2

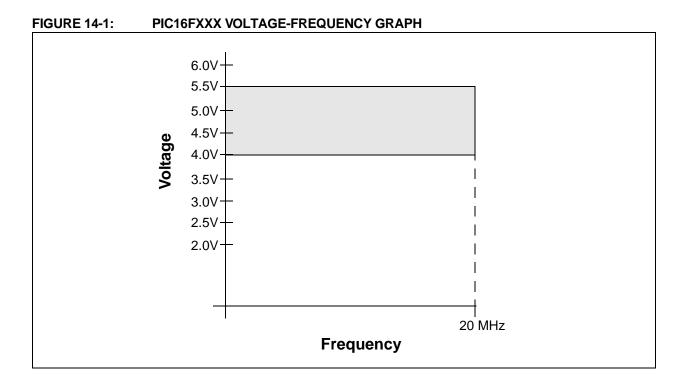

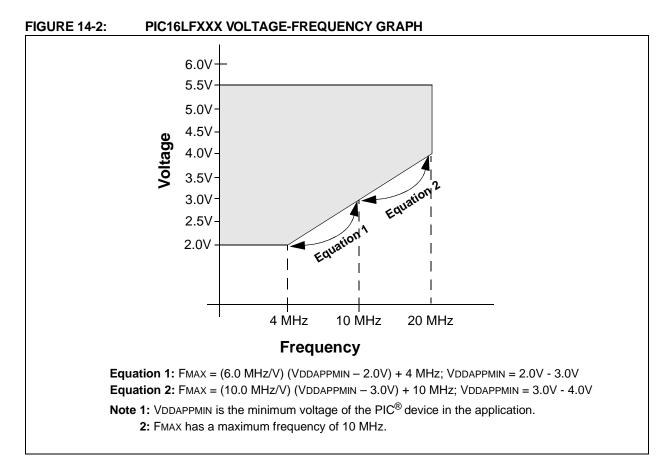

## 14.0 ELECTRICAL CHARACTERISTICS

## Absolute Maximum Ratings †

| Ambient temperature under bias                                                                                     | 55 to +125°C                       |

|--------------------------------------------------------------------------------------------------------------------|------------------------------------|

| Storage temperature                                                                                                | 65°C to +150°C                     |

| Voltage on any pin with respect to Vss (except VDD, MCLR. and RA4)                                                 | 0.3V to (VDD + 0.3V)               |

| Voltage on VDD with respect to Vss                                                                                 | 0.3 to +7.5V                       |

| Voltage on MCLR with respect to Vss (Note 2)                                                                       |                                    |

| Voltage on RA4 with respect to Vss                                                                                 | 0 to +8.5V                         |

| Total power dissipation (Note 1)                                                                                   | 1.0W                               |

| Maximum current out of Vss pin                                                                                     | 300 mA                             |

| Maximum current into VDD pin                                                                                       | 250 mA                             |

| Input clamp current, IiK (Vi < 0 or Vi > VDD)                                                                      | ± 20 mA                            |

| Output clamp current, Iok (Vo < 0 or Vo > VDD)                                                                     | ± 20 mA                            |

| Maximum output current sunk by any I/O pin                                                                         | 25 mA                              |

| Maximum output current sourced by any I/O pin                                                                      | 25 mA                              |

| Maximum current sunk by PORTA, PORTB, and PORTE (combined) (Note 3)                                                | 200 mA                             |

| Maximum current sourced by PORTA, PORTB, and PORTE (combined) (Note 3)                                             | 200 mA                             |

| Maximum current sunk by PORTC and PORTD (combined) (Note 3)                                                        | 200 mA                             |

| Maximum current sourced by PORTC and PORTD (combined) (Note 3)                                                     | 200 mA                             |

| <b>Note 1:</b> Power dissipation is calculated as follows: Pdis = VDD x {IDD - $\sum$ IOH} + $\sum$ {(VDD - $\sum$ | /OH) x IOH} + $\Sigma$ (VOI x IOL) |

| 2: Voltage spikes below Vss at the $\overline{\text{MCLR}}$ pin, inducing currents greater than 80 r               | nA <u>, may cause latch-up</u> .   |

- 2: Voltage spikes below VSS at the MCLR pin, inducing currents greater than 80 mA, may cause latch-up. Thus, a series resistor of 50-100Ω should be used when applying a "low" level to the MCLR pin, rather than pulling this pin directly to VSS.

- 3: PORTD and PORTE are not implemented on the 28-pin devices.

† NOTICE: Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at those or any other conditions above those indicated in the operation listings of this specification is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

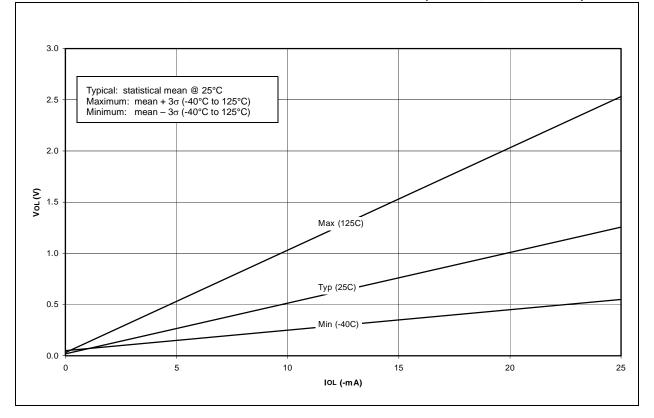

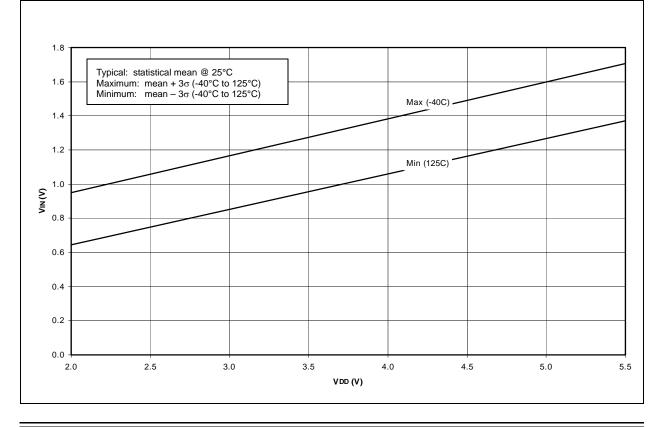

| DC CHA       | RACTI | ERISTICS                                      | Standard Operating Conditions (unless otherwise stated)<br>Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial<br>Operating voltage VDD range as described in DC spec Section 14.1<br>and Section 14.2. |     |          |                                                             |                                                |  |  |

|--------------|-------|-----------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|----------|-------------------------------------------------------------|------------------------------------------------|--|--|

| Param<br>No. | Sym   | Characteristic                                | Min Typ†                                                                                                                                                                                                                        |     | Мах      | Units                                                       | Conditions                                     |  |  |

|              | VIL   | Input Low Voltage                             |                                                                                                                                                                                                                                 |     |          |                                                             |                                                |  |  |

|              |       | I/O ports:                                    |                                                                                                                                                                                                                                 |     |          |                                                             |                                                |  |  |

| D030         |       | with TTL buffer                               | Vss                                                                                                                                                                                                                             |     | 0.15 Vdd | V                                                           | For entire VDD range                           |  |  |

| D030A        |       |                                               | Vss                                                                                                                                                                                                                             |     | 0.8V     | V                                                           | $4.5V \leq VDD \leq 5.5V$                      |  |  |

| D031         |       | with Schmitt Trigger buffer                   | Vss                                                                                                                                                                                                                             |     | 0.2 Vdd  | V                                                           |                                                |  |  |

| D032         |       | MCLR, OSC1 (in RC mode)                       | Vss                                                                                                                                                                                                                             | —   | 0.2 Vdd  | V                                                           |                                                |  |  |

| D033         |       | OSC1 (in XT, HS and LP)<br>Ports RC3 and RC4: | Vss                                                                                                                                                                                                                             | —   | 0.3 Vdd  | V                                                           | (Note 1)                                       |  |  |

| D034         |       | with Schmitt Trigger buffer                   | Vss                                                                                                                                                                                                                             |     | 0.3 Vdd  | V                                                           | For entire VDD range                           |  |  |

| D034A        |       | with SMBus                                    | -0.5                                                                                                                                                                                                                            | —   | 0.6      | V                                                           | For $VDD = 4.5$ to $5.5V$                      |  |  |

|              | Vih   | Input High Voltage                            |                                                                                                                                                                                                                                 |     |          |                                                             |                                                |  |  |

|              |       | I/O ports:                                    |                                                                                                                                                                                                                                 | —   |          |                                                             |                                                |  |  |

| D040         |       | with TTL buffer                               | 2.0                                                                                                                                                                                                                             |     | Vdd      | V                                                           | $4.5V \leq VDD \leq 5.5V$                      |  |  |

| D040A        |       |                                               | 0.25 Vdd +<br>0.8V                                                                                                                                                                                                              | —   | Vdd      | V                                                           | For entire VDD range                           |  |  |

| D041         |       | with Schmitt Trigger buffer                   | 0.8 Vdd                                                                                                                                                                                                                         | —   | Vdd      | V                                                           | For entire VDD range                           |  |  |

| D042         |       | MCLR                                          | 0.8 Vdd                                                                                                                                                                                                                         |     | Vdd      | V                                                           |                                                |  |  |

| D042A        |       | OSC1 (XT, HS and LP)                          | 0.7 Vdd                                                                                                                                                                                                                         |     | Vdd      | V                                                           | (Note 1)                                       |  |  |

| D043         |       | OSC1 (in RC mode)                             | 0.9 Vdd                                                                                                                                                                                                                         | —   | Vdd      | V                                                           |                                                |  |  |

|              |       | Ports RC3 and RC4:                            |                                                                                                                                                                                                                                 |     |          |                                                             |                                                |  |  |

| D044         |       | with Schmitt Trigger buffer                   | 0.7 Vdd                                                                                                                                                                                                                         | —   | Vdd      | V                                                           | For entire VDD range                           |  |  |

| D044A        |       | with SMBus                                    | 1.4                                                                                                                                                                                                                             |     | 5.5      | V                                                           | for VDD = 4.5 to 5.5V                          |  |  |

| D070         | Ipurb | PORTB Weak Pull-up<br>Current                 | 50                                                                                                                                                                                                                              | 250 | 400      | μA                                                          | VDD = 5V, VPIN = VSS                           |  |  |

|              | lı∟   | Input Leakage Current<br>(Notes 2, 3)         |                                                                                                                                                                                                                                 |     |          |                                                             |                                                |  |  |

| D060         |       | I/O ports                                     | —                                                                                                                                                                                                                               | _   | ±1       | μA                                                          | $Vss \le VPIN \le VDD,$<br>Pin at hi-impedance |  |  |

| D061         |       | MCLR, RA4/T0CKI                               | —                                                                                                                                                                                                                               | —   | ±5       | μΑ                                                          | $Vss \leq VPIN \leq VDD$                       |  |  |

| D063 OSC1    |       | —                                             | —                                                                                                                                                                                                                               | ±5  | μA       | Vss $\leq$ VPIN $\leq$ VDD, XT, HS and LP osc configuration |                                                |  |  |

## 14.2 DC Characteristics: PIC16F870/871 (Industrial)

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

**Note 1:** In RC oscillator configuration, the OSC1/CLKI pin is a Schmitt Trigger input. It is not recommended that the PIC16F870/871 be driven with external clock in RC mode.

2: The leakage current on the MCLR pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages.

3: Negative current is defined as current sourced by the pin.

# TABLE 14-9:PIC16F870/871 (INDUSTRIAL)PIC16LF870/871 (INDUSTRIAL)

| Param<br>No. | Sym   | Character                                  | istic         | Min        | Тур†       | Мах        | Units | Conditions                                                                                                  |

|--------------|-------|--------------------------------------------|---------------|------------|------------|------------|-------|-------------------------------------------------------------------------------------------------------------|

| A01          | Nr    | Resolution                                 |               |            | _          | 10-bits    | bit   | $\label{eq:VREF} \begin{array}{l} VREF = VDD = 5.12V,\\ VSS \leq VAIN \leq VREF \end{array}$                |

| A03          | EIL   | Integral linearity error                   |               | —          | —          | < ± 1      | LSb   | $\label{eq:VREF} \begin{array}{l} VREF = VDD = 5.12V,\\ VSS \leq VAIN \leq VREF \end{array}$                |

| A04          | Edl   | Differential linearity error               |               | —          | _          | < ± 1      | LSb   | $\label{eq:VREF} \begin{array}{l} VREF = VDD = 5.12V,\\ VSS \leq VAIN \leq VREF \end{array}$                |

| A06          | Eoff  | Offset error                               |               | —          | —          | < ± 1      | LSb   | $\begin{array}{l} VREF=VDD=5.12V,\\ VSS\leqVAIN\leqVREF \end{array}$                                        |

| A07          | Egn   | Gain error                                 |               | —          | _          | < ± 1      | LSb   | $\begin{array}{l} VREF=VDD=5.12V,\\ VSS\leqVAIN\leqVREF \end{array}$                                        |

| A10          | -     | Monotonicity <sup>(3)</sup>                |               | —          | guaranteed | —          | —     | $VSS \leq VAIN \leq VREF$                                                                                   |

| A20          | Vref  | Reference voltage (V                       | ref+ – Vref-) | 2.0V       | _          | Vdd + 0.3  | V     |                                                                                                             |

| A21          | Vref+ | Reference voltage Hi                       | gh            | Vdd - 2.5V |            | VDD + 0.3V | V     | Must meet spec. A20                                                                                         |

| A22          | Vref- | Reference voltage Low                      |               | Vss-0.3V   |            | VREF+-2.0V | V     | Must meet spec. A20                                                                                         |

| A25          | Vain  | Analog input voltage                       |               | Vss – 0.3  | _          | VREF + 0.3 | V     |                                                                                                             |

| A30          | ZAIN  | Recommended imper<br>analog voltage source |               | —          | _          | 10.0       | kΩ    |                                                                                                             |

| A40          | IAD   |                                            | Standard(F)   | —          | 220        | —          | μΑ    | Average current consumption                                                                                 |

|              |       |                                            | Extended(LF)  | —          | 90         | —          | μΑ    | when A/D is on (Note 1).                                                                                    |

| A50          | IREF  | VREF input current <b>(N</b>               | ote 2)        | 10         | _          | 1000       | μΑ    | During VAIN acquisition.<br>Based on differential of VHOLD<br>to VAIN to charge CHOLD, see<br>Section 10.1. |

|              |       |                                            |               | _          | —          | 10         | μΑ    | During A/D Conversion cycle                                                                                 |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

**Note 1:** When A/D is off, it will not consume any current other than minor leakage current. The power-down current spec includes any such leakage from the A/D module.

2: VREF current is from RA3 pin or VDD pin, whichever is selected as reference input.

3: The A/D conversion result never decreases with an increase in the input voltage, and has no missing codes.

## U

| Universal Synchronous Asynchronous Receiver Transmitter.<br>See USART |

|-----------------------------------------------------------------------|

| USART                                                                 |

| Address Detect Enable (ADDEN Bit)                                     |

| Asynchronous Mode                                                     |

| Asynchronous Receive                                                  |

| Asynchronous Receive (9-bit Mode)70                                   |

| Asynchronous Receive with Address Detect.                             |

| See Asynchronous Receive (9-bit Mode).                                |

| Asynchronous Reception                                                |

| Asynchronous Transmitter                                              |

| Baud Rate Generator (BRG)63                                           |

| Baud Rate Formula                                                     |

| Baud Rates, Asynchronous Mode                                         |

| (BRGH = 0)64                                                          |

| Baud Rates, Asynchronous Mode                                         |

| (BRGH = 1)65                                                          |

| High Baud Rate Select (BRGH Bit)61                                    |

| Sampling63                                                            |

| Clock Source Select (CSRC Bit)61                                      |

| Continuous Receive Enable (CREN Bit) 62                               |

| Framing Error (FERR Bit)62                                            |

| Overrun Error (OERR Bit)62                                            |

| Receive Data, 9th bit (RX9D Bit)62                                    |

| Receive Enable, 9-bit (RX9 Bit)62                                     |

| Serial Port Enable (SPEN Bit)61, 62                                   |

| Single Receive Enable (SREN Bit)62                                    |

| Synchronous Master Mode72                                             |

| Synchronous Master Reception74                                        |

| Synchronous Master Transmission72                                     |

| Synchronous Slave Mode76                                              |

| Synchronous Slave Reception77                                         |

| Synchronous Slave Transmit76                                          |

| Transmit Data, 9th Bit (TX9D)61                                       |

| Transmit Enable (TXEN Bit)61                                          |

| Transmit Enable, Nine-bit (TX9 Bit)61                                 |

| Transmit Shift Register Status (TRMT Bit)61                           |

#### W

| Wake-up from SLEEP                   | . 87, 100 |

|--------------------------------------|-----------|

| Interrupts                           | 93        |

| MCLR Reset                           | 93        |

| Timing Diagram                       | 101       |

| WDT Reset                            | 93        |

| Watchdog Timer                       |           |

| Register Summary                     |           |

| Watchdog Timer (WDT)                 | 87, 99    |

| Enable (WDTEN Bit)                   |           |

| Postscaler. See Postscaler, WDT.     |           |

| Programming Considerations           |           |

| RC Oscillator                        |           |

| Time-out Period                      |           |

| WDT Reset, Normal Operation          | 91, 93    |

| WDT Reset, SLEEP                     | 91, 93    |

| Write Verify                         |           |

| Data EEPROM and FLASH Program Memory | 31        |

| WWW, On-Line Support                 | 4         |