#### Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

| Betano                     |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Product Status             | Active                                                                    |

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

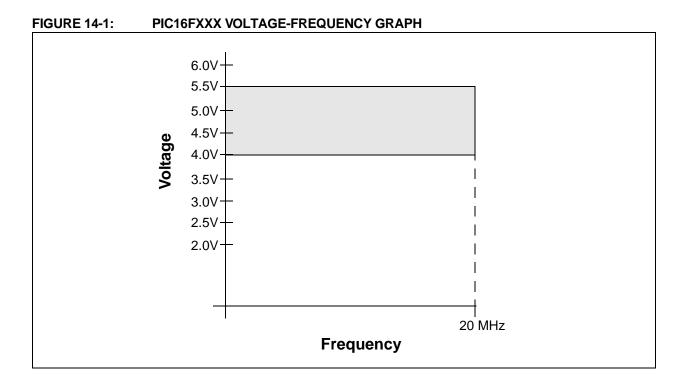

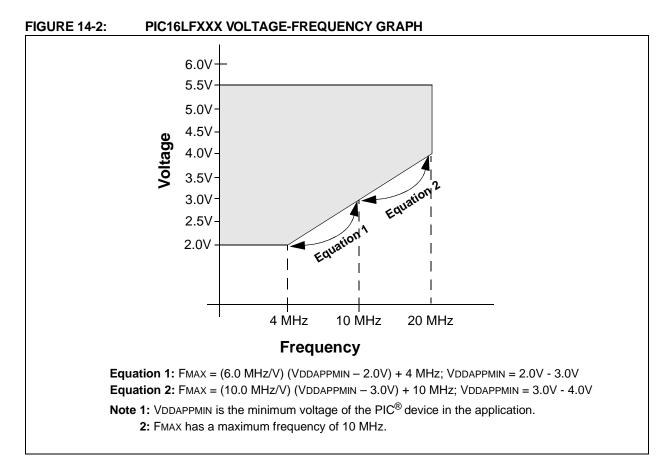

| Speed                      | 20MHz                                                                     |

| Connectivity               | UART/USART                                                                |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                     |

| Number of I/O              | 22                                                                        |

| Program Memory Size        | 3.5KB (2K x 14)                                                           |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 64 x 8                                                                    |

| RAM Size                   | 128 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                 |

| Data Converters            | A/D 5x10b                                                                 |

| Oscillator Type            | External                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Through Hole                                                              |

| Package / Case             | 28-DIP (0.300", 7.62mm)                                                   |

| Supplier Device Package    | 28-SPDIP                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf870-i-sp |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

NOTES:

# 2.0 MEMORY ORGANIZATION

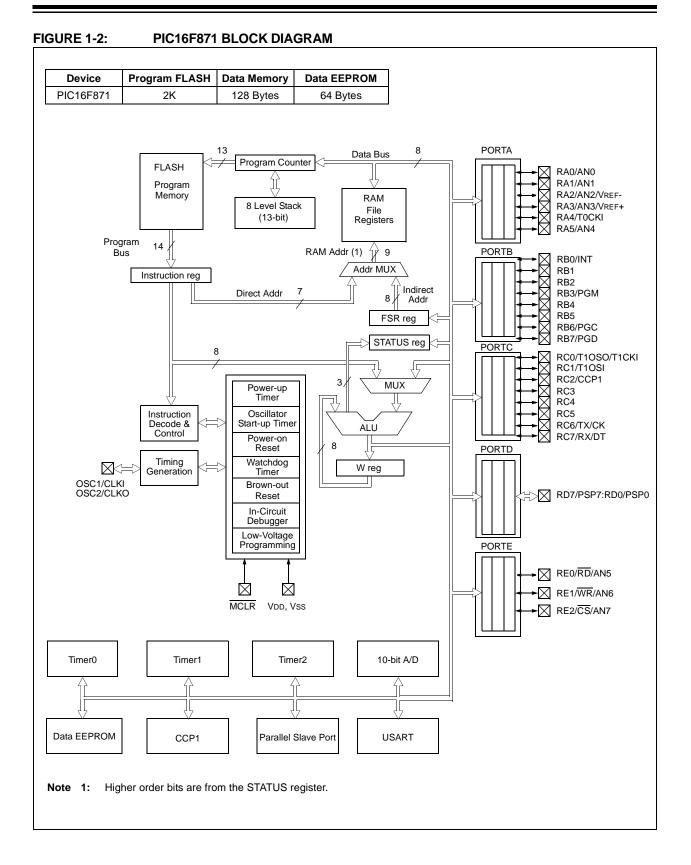

The PIC16F870/871 devices have three memory blocks. The Program Memory and Data Memory have separate buses, so that concurrent access can occur, and is detailed in this section. The EEPROM data memory block is detailed in Section 3.0.

Additional information on device memory may be found in the PICmicro<sup>™</sup> Mid-Range MCU Family Reference Manual (DS33023).

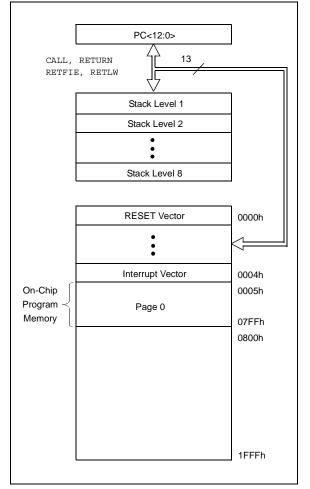

### 2.1 Program Memory Organization

The PIC16F870/871 devices have a 13-bit program counter capable of addressing an 8K x 14 program memory space. The PIC16F870/871 devices have 2K x 14 words of FLASH program memory. Accessing a location above the physically implemented address will cause a wraparound.

The RESET vector is at 0000h and the interrupt vector is at 0004h.

## 2.2 Data Memory Organization

The data memory is partitioned into multiple banks which contain the General Purpose Registers and the Special Function Registers. Bits RP1 (STATUS<6>) and RP0 (STATUS<5>) are the bank select bits.

| RP<1:0> | Bank |

|---------|------|

| 00      | 0    |

| 01      | 1    |

| 10      | 2    |

| 11      | 3    |

Each bank extends up to 7Fh (128 bytes). The lower locations of each bank are reserved for the Special Function Registers. Above the Special Function Registers are General Purpose Registers, implemented as static RAM. All implemented banks contain Special Function Registers. Some "high use" Special Function Registers from one bank may be mirrored in another bank for code reduction and quicker access.

| Note: | EEPROM Data Memory description can          |

|-------|---------------------------------------------|

|       | be found in Section 3.0 of this Data Sheet. |

|       |                                             |

### 2.2.1 GENERAL PURPOSE REGISTER FILE

The register file can be accessed either directly, or indirectly through the File Select Register FSR.

### PIC16F870/871 REGISTER FILE MAP

|                      | File<br>Address |                      | File<br>Address |                     | File<br>Address |                         | File<br>Addres |

|----------------------|-----------------|----------------------|-----------------|---------------------|-----------------|-------------------------|----------------|

| ndirect addr.(*)     | 00h             | Indirect addr.(*)    | 80h             | Indirect addr.(*)   | 100h            | Indirect addr.(*)       | 180ŀ           |

| TMR0                 | 01h             | OPTION_REG           | 81h             | TMR0                | 101h            | OPTION_REG              | 181ŀ           |

| PCL                  | 02h             | PCL                  | 82h             | PCL                 | 102h            | PCL                     | 182ł           |

| STATUS               | 03h             | STATUS               | 83h             | STATUS              | 103h            | STATUS                  | 183ł           |

| FSR                  | 04h             | FSR                  | 84h             | FSR                 | 104h            | FSR                     | 184ł           |

| PORTA                | 05h             | TRISA                | 85h             |                     | 105h            |                         | 185ł           |

| PORTB                | 06h             | TRISB                | 86h             | PORTB               | 106h            | TRISB                   | 186ł           |

| PORTC                | 07h             | TRISC                | 87h             |                     | 107h            |                         | 187ł           |

| PORTD <sup>(2)</sup> | 08h             | TRISD <sup>(2)</sup> | 88h             |                     | 108h            |                         | 188ł           |

| PORTE <sup>(2)</sup> | 09h             | TRISE <sup>(2)</sup> | 89h             |                     | 109h            |                         | 189            |

| PCLATH               | 0Ah             | PCLATH               | 8Ah             | PCLATH              | 10Ah            | PCLATH                  | 18A            |

| INTCON               | 0Bh             | INTCON               | 8Bh             | INTCON              | 10Bh            | INTCON                  | 18B            |

| PIR1                 | 0Ch             | PIE1                 | 8Ch             | EEDATA              | 10Ch            | EECON1                  | 18C            |

| PIR2                 | 0Dh             | PIE2                 | 8Dh             | EEADR               | 10Dh            | EECON2                  | 18D            |

| TMR1L                | 0Eh             | PCON                 | 8Eh             | EEDATH              | 10Eh            | Reserved <sup>(1)</sup> | 18E            |

| TMR1H                | 0Fh             |                      | 8Fh             | EEADRH              | 10Fh            | Reserved <sup>(1)</sup> | 18F            |

| T1CON                | 10h             |                      | 90h             |                     | 110h            |                         | 190            |

| TMR2                 | 11h             |                      | 91h             |                     |                 |                         |                |

| T2CON                | 12h             | PR2                  | 92h             |                     |                 |                         |                |

|                      | 13h             |                      | 93h             |                     |                 |                         |                |

|                      | 14h             |                      | 94h             |                     |                 |                         |                |

| CCPR1L               | 15h             |                      | 95h             |                     |                 |                         |                |

| CCPR1H               | 16h             |                      | 96h             |                     |                 |                         |                |

| CCP1CON              | 17h             |                      | 97h             |                     |                 |                         |                |

| RCSTA                | 18h             | TXSTA                | 98h             |                     |                 |                         |                |

| TXREG                | 19h             | SPBRG                | 99h             |                     |                 |                         |                |

| RCREG                | 1Ah             |                      | 9Ah             |                     |                 |                         |                |

|                      | 1Bh             |                      | 9Bh             |                     |                 |                         |                |

|                      | 1Ch             |                      | 9Ch             |                     |                 |                         |                |

|                      | 1Dh             |                      | 9Dh             |                     |                 |                         |                |

| ADRESH               | 1Eh             | ADRESL               | 9Eh             |                     |                 |                         |                |

| ADCON0               | 1Fh             | ADCON1               | 9Fh             |                     | 1005            |                         | 1 4 01         |

|                      | 20h             | General<br>Purpose   | A0h             | accesses            | 120h            | accesses                | 1A0            |

| General              |                 | Register             |                 | 20h-7Fh             |                 | A0h - BFh               |                |

| Purpose<br>Register  |                 | 32 Bytes             | BFh<br>C0h      |                     |                 |                         | 1BF<br>1C0     |

| 96 Bytes             |                 |                      | EFh<br>F0h      |                     | 16Fh<br>170h    |                         | 1EF            |

|                      | 7Fh             | accesses<br>70h-7Fh  | FFh             | accesses<br>70h-7Fh | 17Fh            | accesses<br>70h-7Fh     | 1F0I<br>1FF    |

| Bank 0               |                 | Bank 1               |                 | Bank 2              |                 | Bank 3                  |                |

\* Not a physical register.

Note 1: These registers are reserved; maintain these registers clear.

2: These registers are not implemented on the PIC16F870.

### 6.7 Resetting of Timer1 Register Pair (TMR1H, TMR1L)

TMR1H and TMR1L registers are not reset to 00h on a POR, or any other RESET, except by the CCP1 special event trigger.

T1CON register is reset to 00h on a Power-on Reset, or a Brown-out Reset, which shuts off the timer and leaves a 1:1 prescale. In all other RESETS, the register is unaffected.

### 6.8 Timer1 Prescaler

The prescaler counter is cleared on writes to the TMR1H or TMR1L registers.

### TABLE 6-2: REGISTERS ASSOCIATED WITH TIMER1 AS A TIMER/COUNTER

| Address                | Name   | Bit 7                | Bit 6                                                                      | Bit 5       | Bit 4       | Bit 3       | Bit 2     | Bit 1      | Bit 0  | Value<br>POR, |      | all c | e on<br>other<br>SETS |

|------------------------|--------|----------------------|----------------------------------------------------------------------------|-------------|-------------|-------------|-----------|------------|--------|---------------|------|-------|-----------------------|

| 0Bh,8Bh,<br>10Bh, 18Bh | INTCON | GIE                  | PEIE                                                                       | TOIE        | INTE        | RBIE        | TOIF      | INTF       | RBIF   | 0000          | 000x | 0000  | 000u                  |

| 0Ch                    | PIR1   | PSPIF <sup>(1)</sup> | ADIF                                                                       | RCIF        | TXIF        | _           | CCP1IF    | TMR2IF     | TMR1IF | 0000          | -000 | 0000  | -000                  |

| 8Ch                    | PIE1   | PSPIE <sup>(1)</sup> | ADIE                                                                       | RCIE        | TXIE        | _           | CCP1IE    | TMR2IE     | TMR1IE | 0000          | -000 | 0000  | -000                  |

| 0Eh                    | TMR1L  | Holding R            | egister fo                                                                 | r the Least | Significant | Byte of the | 16-bit TM | R1 Registe | er     | xxxx          | xxxx | uuuu  | uuuu                  |

| 0Fh                    | TMR1H  | Holding R            | lolding Register for the Most Significant Byte of the 16-bit TMR1 Register |             |             |             |           |            |        |               | xxxx | uuuu  | uuuu                  |

| 10h                    | T1CON  | _                    | _                                                                          | T1CKPS1     | T1CKPS0     | T1OSCEN     | T1SYNC    | TMR1CS     | TMR10N | 00            | 0000 | uu    | uuuu                  |

Legend: x = unknown, u = unchanged, - = unimplemented, read as '0'. Shaded cells are not used by the Timer1 module.

Note 1: Bits PSPIE and PSPIF are reserved on the PIC16F870; always maintain these bits clear.

| Address                | Name                                  | Bit 7                | Bit 6     | Bit 5   | Bit 4 | Bit 3 | Bit 2  | Bit 1  | Bit 0  | Value on:<br>POR, BOR | Value on<br>all other<br>RESETS |

|------------------------|---------------------------------------|----------------------|-----------|---------|-------|-------|--------|--------|--------|-----------------------|---------------------------------|

| 0Bh, 8Bh,<br>10Bh,18Bh | INTCON                                | GIE                  | PEIE      | TOIE    | INTE  | RBIE  | TOIF   | INTF   | R0IF   | 0000 000x             | 0000 000u                       |

| 0Ch                    | PIR1                                  | PSPIF <sup>(1)</sup> | ADIF      | RCIF    | TXIF  | _     | CCP1IF | TMR2IF | TMR1IF | 0000 -000             | 0000 -000                       |

| 18h                    | RCSTA                                 | SPEN                 | RX9       | SREN    | CREN  | _     | FERR   | OERR   | RX9D   | 0000 -00x             | 0000 -00x                       |

| 19h                    | TXREG                                 | USART Tr             | ansmit Re | egister |       |       |        |        |        | 0000 0000             | 0000 0000                       |

| 8Ch                    | PIE1                                  | PSPIE <sup>(1)</sup> | ADIE      | RCIE    | TXIE  | _     | CCP1IE | TMR2IE | TMR1IE | 0000 -000             | 0000 -000                       |

| 98h                    | TXSTA                                 | CSRC                 | TX9       | TXEN    | SYNC  | _     | BRGH   | TRMT   | TX9D   | 0000 -010             | 0000 -010                       |

| 99h                    | 9h SPBRG Baud Rate Generator Register |                      |           |         |       |       |        |        |        |                       | 0000 0000                       |

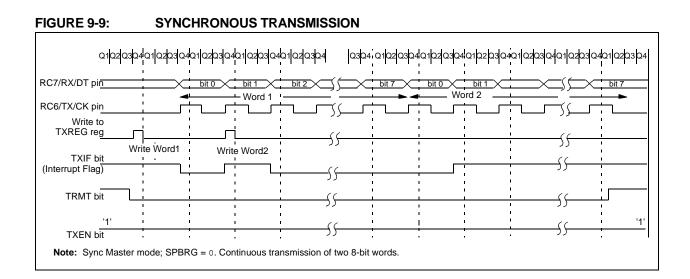

TABLE 9-8:

REGISTERS ASSOCIATED WITH SYNCHRONOUS MASTER TRANSMISSION

Legend: x = unknown, - = unimplemented, read as '0'. Shaded cells are not used for synchronous master transmission.

Note 1: Bits PSPIE and PSPIF are reserved on the PIC16F870; always maintain these bits clear.

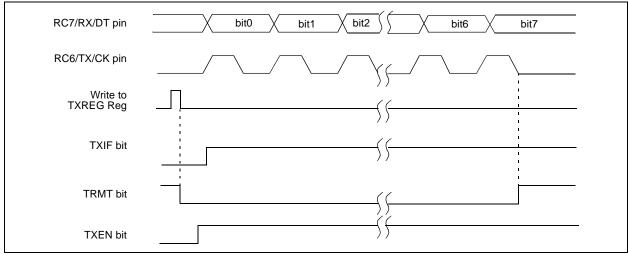

### FIGURE 9-10: SYNCHRONOUS TRANSMISSION (THROUGH TXEN)

| Address                | Name   | Bit 7                | Bit 6     | Bit 5     | Bit 4     | Bit 3   | Bit 2       | Bit 1       | Bit 0     | Value on:<br>POR, BOR | Value on<br>all other<br>RESETS |

|------------------------|--------|----------------------|-----------|-----------|-----------|---------|-------------|-------------|-----------|-----------------------|---------------------------------|

| 0Bh, 8Bh,<br>10Bh,18Bh | INTCON | GIE                  | PEIE      | TOIE      | INTE      | RBIE    | TOIF        | INTF        | R0IF      | 0000 000x             | 0000 000u                       |

| 0Ch                    | PIR1   | PSPIF <sup>(1)</sup> | ADIF      | RCIF      | TXIF      | _       | CCP1IF      | TMR2IF      | TMR1IF    | 0000 -000             | 0000 -000                       |

| 18h                    | RCSTA  | SPEN                 | RX9       | SREN      | CREN      | _       | FERR        | OERR        | RX9D      | 0000 -00x             | 0000 -00x                       |

| 1Ah                    | RCREG  | USART R              | eceive Re | gister    |           |         |             |             |           | 0000 0000             | 0000 0000                       |

| 8Ch                    | PIE1   | PSPIE <sup>(1)</sup> | ADIE      | RCIE      | TXIE      | _       | CCP1IE      | TMR2IE      | TMR1IE    | 0000 -000             | 0000 -000                       |

| 98h                    | TXSTA  | CSRC                 | TX9       | TXEN      | SYNC      | _       | BRGH        | TRMT        | TX9D      | 0000 -010             | 0000 -010                       |

| 99h                    | SPBRG  |                      | 0000 0000 | 0000 0000 |           |         |             |             |           |                       |                                 |

| Logond                 | unkno  |                      | malamant  | od rood   | 20 '0' SH | adad ca | lle ara not | upped for a | nchronour | montor recent         | ion                             |

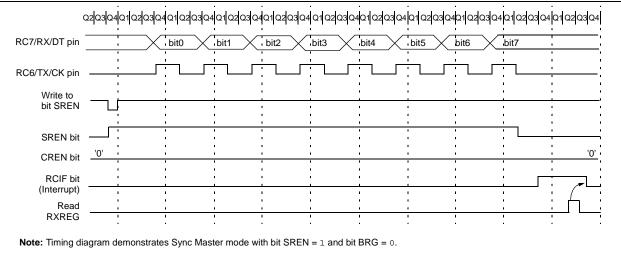

TABLE 9-9:

REGISTERS ASSOCIATED WITH SYNCHRONOUS MASTER RECEPTION

Legend: x = unknown, - = unimplemented, read as '0'. Shaded cells are not used for synchronous master reception.

Note 1: Bits PSPIE and PSPIF are reserved on the PIC16F870; always maintain these bits clear.

### 9.4.2 USART SYNCHRONOUS SLAVE RECEPTION

The operation of the Synchronous Master and Slave modes is identical, except in the case of the SLEEP mode. Bit SREN is a "don't care" in Slave mode.

If receive is enabled by setting bit CREN prior to the SLEEP instruction, then a word may be received during SLEEP. On completely receiving the word, the RSR register will transfer the data to the RCREG register and if enable bit RCIE bit is set, the interrupt generated will wake the chip from SLEEP. If the global interrupt is enabled, the program will branch to the interrupt vector (0004h).

When setting up a Synchronous Slave Reception, follow these steps:

- 1. Enable the synchronous master serial port by setting bits SYNC and SPEN and clearing bit CSRC.

- 2. If interrupts are desired, set enable bit RCIE.

- 3. If 9-bit reception is desired, set bit RX9.

- 4. To enable reception, set enable bit CREN.

- 5. Flag bit RCIF will be set when reception is complete and an interrupt will be generated, if enable bit RCIE was set.

- Read the RCSTA register to get the ninth bit (if enabled) and determine if any error occurred during reception.

- 7. Read the 8-bit received data by reading the RCREG register.

- 8. If any error occurred, clear the error by clearing bit CREN.

- 9. If using interrupts, ensure that GIE and PEIE (bits 7 and 6) of the INTCON register are set.

### TABLE 9-11: REGISTERS ASSOCIATED WITH SYNCHRONOUS SLAVE RECEPTION

| Address                | Name   | Bit 7                | Bit 6    | Bit 5   | Bit 4     | Bit 3     | Bit 2  | Bit 1  | Bit 0  | Value on:<br>POR, BOR | Value on<br>all other<br>RESETS |

|------------------------|--------|----------------------|----------|---------|-----------|-----------|--------|--------|--------|-----------------------|---------------------------------|

| 0Bh, 8Bh,<br>10Bh,18Bh | INTCON | GIE                  | PEIE     | TOIE    | INTE      | RBIE      | T0IF   | INTF   | R0IF   | 0000 000x             | 0000 000u                       |

| 0Ch                    | PIR1   | PSPIF <sup>(1)</sup> | ADIF     | RCIF    | TXIF      | —         | CCP1IF | TMR2IF | TMR1IF | 0000 -000             | 0000 -000                       |

| 18h                    | RCSTA  | SPEN                 | RX9      | SREN    | CREN      | ADDEN     | FERR   | OERR   | RX9D   | 0000 000x             | 0000 000x                       |

| 1Ah                    | RCREG  | USART R              | eceive R | egister |           |           |        |        |        | 0000 0000             | 0000 0000                       |

| 8Ch                    | PIE1   | PSPIE <sup>(1)</sup> | ADIE     | RCIE    | TXIE      | _         | CCP1IE | TMR2IE | TMR1IE | 0000 -000             | 0000 -000                       |

| 98h                    | TXSTA  | CSRC                 | TX9      | TXEN    | SYNC      | —         | BRGH   | TRMT   | TX9D   | 0000 -010             | 0000 -010                       |

| 99h                    | SPBRG  | Baud Rate            | e Genera |         | 0000 0000 | 0000 0000 |        |        |        |                       |                                 |

Legend: x = unknown, - = unimplemented, read as '0'. Shaded cells are not used for synchronous slave reception.

Note 1: Bits PSPIE and PSPIF are reserved on the PIC16F870, always maintain these bits clear.

## 10.5 A/D Operation During SLEEP

The A/D module can operate during SLEEP mode. This requires that the A/D clock source be set to RC (ADCS1:ADCS0 = 11). When the RC clock source is selected, the A/D module waits one instruction cycle before starting the conversion. This allows the SLEEP instruction to be executed, which eliminates all digital switching noise from the conversion. When the conversion is completed, the GO/DONE bit will be cleared and the result loaded into the ADRES register. If the A/D interrupt is enabled, the device will wake-up from SLEEP. If the A/D interrupt is not enabled, the ADON bit will remain set.

When the A/D clock source is another clock option (not RC), a SLEEP instruction will cause the present conversion to be aborted and the A/D module to be turned off, though the ADON bit will remain set.

Turning off the A/D places the A/D module in its lowest current consumption state.

| Note: | For the A/D module to operate in SLEEP,   |

|-------|-------------------------------------------|

|       | the A/D clock source must be set to RC    |

|       | (ADCS1:ADCS0 = 11). To allow the con-     |

|       | version to occur during SLEEP, ensure the |

|       | SLEEP instruction immediately follows the |

|       | instruction that sets the GO/DONE bit.    |

### 10.6 Effects of a RESET

A device RESET forces all registers to their RESET state. This forces the A/D module to be turned off, and any conversion is aborted. All A/D input pins are configured as analog inputs.

The value that is in the ADRESH:ADRESL registers is not modified for a Power-on Reset. The ADRESH:ADRESL registers will contain unknown data after a Power-on Reset.

| Address               | Name   | Bit 7                | Bit 6      | Bit 5    | Bit 4         | Bit 3      | Bit 2   | Bit 1     | Bit 0     | Value on<br>POR, BOR | V <u>alue o</u> n<br>MCLR,<br>WDT |

|-----------------------|--------|----------------------|------------|----------|---------------|------------|---------|-----------|-----------|----------------------|-----------------------------------|

| 0Bh,8Bh,<br>10Bh,18Bh | INTCON | GIE                  | PEIE       | TOIE     | INTE          | RBIE       | TOIF    | INTF      | RBIF      | 0000 000x            | 0000 000u                         |

| 0Ch                   | PIR1   | PSPIF <sup>(1)</sup> | ADIF       | RCIF     | TXIF          | —          | CCP1IF  | TMR2IF    | TMR1IF    | 0000 -000            | 0000 -000                         |

| 8Ch                   | PIE1   | PSPIE <sup>(1)</sup> | ADIE       | RCIE     | TXIE          | —          | CCP1IE  | TMR2IE    | TMR1IE    | 0000 -000            | 0000 -000                         |

| 1Eh                   | ADRESH | A/D Resul            | t Register |          | xxxx xxxx     | uuuu uuuu  |         |           |           |                      |                                   |

| 9Eh                   | ADRESL | A/D Resul            | t Register | Low Byte | e             |            |         |           |           | xxxx xxxx            | uuuu uuuu                         |

| 1Fh                   | ADCON0 | ADCS1                | ADCS0      | CHS2     | CHS1          | CHS0       | GO/DONE | _         | ADON      | 0000 00-0            | 0000 00-0                         |

| 9Fh                   | ADCON1 | ADFM                 | —          | _        | —             | PCFG3      | PCFG2   | PCFG1     | PCFG0     | 0-0000               | 0- 0000                           |

| 85h                   | TRISA  | —                    | _          | PORTA    | Data Directio | n Register |         |           |           | 11 1111              | 11 1111                           |

| 05h                   | PORTA  | _                    | _          | PORTA    | Data Latch w  | ad         | 0x 0000 | Ou 0000   |           |                      |                                   |

| 89h <sup>(1)</sup>    | TRISE  | IBF                  | OBF        | IBOV     | PSPMODE       | —          | n bits  | 0000 -111 | 0000 -111 |                      |                                   |

| 09h <sup>(1)</sup>    | PORTE  | —                    | _          | _        | —             | _          | RE2     | RE1       | RE0       | xxx                  | uuu                               |

TABLE 10-2: REGISTERS/BITS ASSOCIATED WITH A/D

Legend: x = unknown, u = unchanged, - = unimplemented, read as '0'. Shaded cells are not used for A/D conversion.

**Note 1:** These registers/bits are not available on the 28-pin devices.

| POR | BOR | то | PD |                                                         |  |  |  |  |  |

|-----|-----|----|----|---------------------------------------------------------|--|--|--|--|--|

| 0   | x   | 1  | 1  | Power-on Reset                                          |  |  |  |  |  |

| 0   | х   | 0  | x  | egal, TO is set on POR                                  |  |  |  |  |  |

| 0   | x   | x  | 0  | egal, PD is set on POR                                  |  |  |  |  |  |

| 1   | 0   | 1  | 1  | Brown-out Reset                                         |  |  |  |  |  |

| 1   | 1   | 0  | 1  | WDT Reset                                               |  |  |  |  |  |

| 1   | 1   | 0  | 0  | WDT Wake-up                                             |  |  |  |  |  |

| 1   | 1   | u  | u  | MCLR Reset during normal operation                      |  |  |  |  |  |

| 1   | 1   | 1  | 0  | MCLR Reset during SLEEP or interrupt wake-up from SLEEP |  |  |  |  |  |

### TABLE 11-4: STATUS BITS AND THEIR SIGNIFICANCE

Legend: x = don't care, u = unchanged

### TABLE 11-5: RESET CONDITION FOR SPECIAL REGISTERS

| Condition                          | Program<br>Counter    | STATUS<br>Register | PCON<br>Register |

|------------------------------------|-----------------------|--------------------|------------------|

| Power-on Reset                     | 000h                  | 0001 1xxx          | 0x               |

| MCLR Reset during normal operation | 000h                  | 000u uuuu          | uu               |

| MCLR Reset during SLEEP            | 000h                  | 0001 0uuu          | uu               |

| WDT Reset                          | 000h                  | 0000 luuu          | uu               |

| WDT Wake-up                        | PC + 1                | uuu0 Ouuu          | uu               |

| Brown-out Reset                    | 000h                  | 0001 luuu          | u0               |

| Interrupt wake-up from SLEEP       | PC + 1 <sup>(1)</sup> | uuul Ouuu          | uu               |

Legend: u = unchanged, x = unknown, - = unimplemented bit, read as '0'

Note 1: When the wake-up is due to an interrupt and the GIE bit is set, the PC is loaded with the interrupt vector (0004h).

### TABLE 11-6: INITIALIZATION CONDITIONS FOR ALL REGISTERS

| Register | Devices   |           | Power-on Reset,<br>Brown-out Reset | MCLR Resets<br>WDT Reset | Wake-up via WDT or<br>Interrupt |  |

|----------|-----------|-----------|------------------------------------|--------------------------|---------------------------------|--|

| W        | PIC16F870 | PIC16F871 | XXXX XXXX                          | uuuu uuuu                | սսսս սսսս                       |  |

| INDF     | PIC16F870 | PIC16F871 | N/A                                | N/A                      | N/A                             |  |

| TMR0     | PIC16F870 | PIC16F871 | xxxx xxxx                          | uuuu uuuu                | սսսս սսսս                       |  |

| PCL      | PIC16F870 | PIC16F871 | 0000h                              | 0000h                    | PC + 1 <sup>(2)</sup>           |  |

| STATUS   | PIC16F870 | PIC16F871 | 0001 1xxx                          | 000q quuu <b>(3)</b>     | uuuq quuu <sup>(3)</sup>        |  |

| FSR      | PIC16F870 | PIC16F871 | xxxx xxxx                          | uuuu uuuu                | uuuu uuuu                       |  |

| PORTA    | PIC16F870 | PIC16F871 | 0x 0000                            | 0u 0000                  | uu uuuu                         |  |

| PORTB    | PIC16F870 | PIC16F871 | xxxx xxxx                          | uuuu uuuu                | uuuu uuuu                       |  |

| PORTC    | PIC16F870 | PIC16F871 | xxxx xxxx                          | uuuu uuuu                | uuuu uuuu                       |  |

| PORTD    | PIC16F870 | PIC16F871 | xxxx xxxx                          | uuuu uuuu                | uuuu uuuu                       |  |

| PORTE    | PIC16F870 | PIC16F871 | xxx                                | uuu                      | uuu                             |  |

| PCLATH   | PIC16F870 | PIC16F871 | 0 0000                             | 0 0000                   | u uuuu                          |  |

| INTCON   | PIC16F870 | PIC16F871 | 0000 000x                          | 0000 000u                | uuuu uuuu <b>(1)</b>            |  |

Legend: u = unchanged, x = unknown, - = unimplemented bit, read as '0', q = value depends on condition, r = reserved, maintain clear

Note 1: One or more bits in INTCON, PIR1 and/or PIR2 will be affected (to cause wake-up).

- **2:** When the wake-up is due to an interrupt and the GIE bit is set, the PC is loaded with the interrupt vector (0004h).

- **3:** See Table 11-5 for RESET value for specific condition.

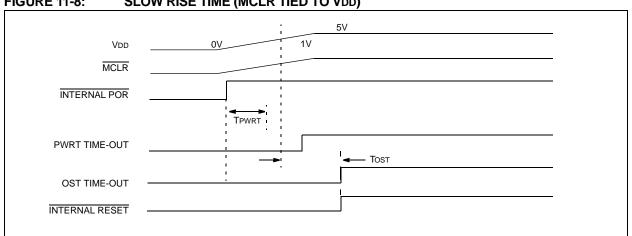

#### SLOW RISE TIME (MCLR TIED TO VDD) **FIGURE 11-8:**

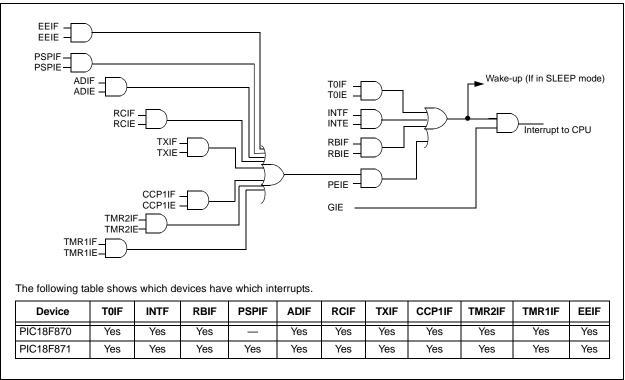

### 11.10 Interrupts

The PIC16F870/871 family has up to 14 sources of interrupt. The Interrupt Control register (INTCON) records individual interrupt requests in flag bits. It also has individual and global interrupt enable bits.

| Note: | Individual | interru | pt fla | ag    | bits  | are   | set,  |

|-------|------------|---------|--------|-------|-------|-------|-------|

|       | regardless | of      | the    | stat  | tus   | of    | their |

|       | correspond | ling ma | sk bit | t, or | the G | SIE b | it.   |

A global interrupt enable bit, GIE (INTCON<7>), enables (if set) all unmasked interrupts, or disables (if cleared) all interrupts. When bit GIE is enabled, and an interrupt's flag bit and mask bit are set, the interrupt will vector immediately. Individual interrupts can be disabled through their corresponding enable bits in various registers. Individual interrupt bits are set, regardless of the status of the GIE bit. The GIE bit is cleared on RESET.

The "return from interrupt" instruction, RETFIE, exits the interrupt routine as well as sets the GIE bit, which re-enables interrupts.

The RB0/INT pin interrupt, the RB port change interrupt, and the TMR0 overflow interrupt flags are contained in the INTCON register.

The peripheral interrupt flags are contained in the special function registers, PIR1 and PIR2. The corresponding interrupt enable bits are contained in special function registers, PIE1 and PIE2, and the peripheral interrupt enable bit is contained in special function register, INTCON.

When an interrupt is responded to, the GIE bit is cleared to disable any further interrupt, the return address is pushed onto the stack and the PC is loaded with 0004h. Once in the Interrupt Service Routine, the source(s) of the interrupt can be determined by polling the interrupt flag bits. The interrupt flag bit(s) must be cleared in software before re-enabling interrupts to avoid recursive interrupts.

For external interrupt events, such as the INT pin or PORTB change interrupt, the interrupt latency will be three or four instruction cycles. The exact latency depends when the interrupt event occurs. The latency is the same for one or two-cycle instructions. Individual interrupt flag bits are set, regardless of the status of their corresponding mask bit, PEIE bit, or GIE bit.

FIGURE 11-9: INTERRUPT LOGIC

### 11.10.1 INT INTERRUPT

External interrupt on the RB0/INT pin is edge triggered, either rising, if bit INTEDG (OPTION\_REG<6>) is set, or falling, if the INTEDG bit is clear. When a valid edge appears on the RB0/INT pin, flag bit INTF (INTCON<1>) is set. This interrupt can be disabled by clearing enable bit INTE (INTCON<4>). Flag bit INTF must be cleared in software in the Interrupt Service Routine before re-enabling this interrupt. The INT interrupt can wake-up the processor from SLEEP, if bit INTE was set prior to going into SLEEP. The status of global interrupt enable bit, GIE, decides whether or not the processor branches to the interrupt vector following wake-up. See Section 11.13 for details on SLEEP mode.

### 11.10.2 TMR0 INTERRUPT

An overflow (FFh  $\rightarrow$  00h) in the TMR0 register will set flag bit T0IF (INTCON<2>). The interrupt can be enabled/disabled by setting/clearing enable bit T0IE (INTCON<5>) (Section 5.0).

### 11.10.3 PORTB INTCON CHANGE

An input change on PORTB<7:4> sets flag bit RBIF (INTCON<0>). The interrupt can be enabled/disabled by setting/clearing enable bit RBIE (INTCON<4>) (Section 4.2).

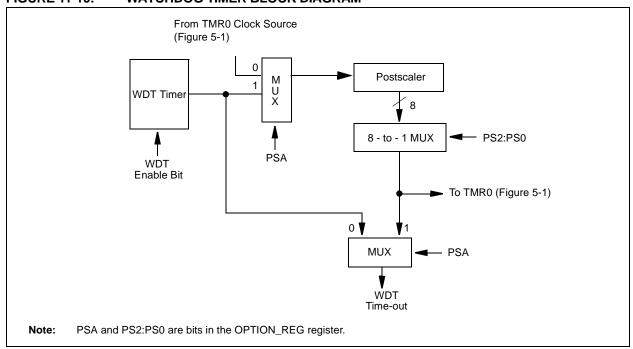

## 11.12 Watchdog Timer (WDT)

The Watchdog Timer is a free running on-chip RC oscillator which does not require any external components. This RC oscillator is separate from the RC oscillator of the OSC1/CLKI pin. That means that the WDT will run, even if the clock on the OSC1/CLKI and OSC2/CLKO pins of the device has been stopped, for example, by execution of a SLEEP instruction.

During normal operation, a WDT time-out generates a device RESET (Watchdog Timer Reset). If the device is in SLEEP mode, a WDT time-out causes the device to wake-up and continue with normal operation (Watchdog Timer Wake-up). The TO bit in the STATUS register will be cleared upon a Watchdog Timer time-out.

The WDT can be permanently disabled by clearing configuration bit WDTEN (Section 11.1).

WDT time-out period values may be found in the Electrical Specifications section under parameter #31. Values for the WDT prescaler (actually a postscaler, but shared with the Timer0 prescaler) may be assigned using the OPTION\_REG register.

- Note 1: The CLRWDT and SLEEP instructions clear the WDT and the postscaler, if assigned to the WDT, and prevent it from timing out and generating a device RESET condition.

- 2: When a CLRWDT instruction is executed and the prescaler is assigned to the WDT, the prescaler count will be cleared, but the prescaler assignment is not changed.

### FIGURE 11-10: WATCHDOG TIMER BLOCK DIAGRAM

### TABLE 11-7: SUMMARY OF WATCHDOG TIMER REGISTERS

| Address  | Name         | Bit 7 | Bit 6                | Bit 5 | Bit 4 | Bit 3                 | Bit 2 | Bit 1 | Bit 0 |

|----------|--------------|-------|----------------------|-------|-------|-----------------------|-------|-------|-------|

| 2007h    | Config. bits | (1)   | BOREN <sup>(1)</sup> | CP1   | CP0   | PWRTEN <sup>(1)</sup> | WDTEN | FOSC1 | FOSC0 |

| 81h,181h | OPTION_REG   | RBPU  | INTEDG               | TOCS  | T0SE  | PSA                   | PS2   | PS1   | PS0   |

Legend: Shaded cells are not used by the Watchdog Timer.

Note 1: See Register 11-1 for operation of these bits.

| ADDLW            | Add Literal and W                                                                                                          |

|------------------|----------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] ADDLW k                                                                                                   |

| Operands:        | $0 \le k \le 255$                                                                                                          |

| Operation:       | $(W) + k \to (W)$                                                                                                          |

| Status Affected: | C, DC, Z                                                                                                                   |

| Description:     | The contents of the W register<br>are added to the eight-bit literal 'k'<br>and the result is placed in the W<br>register. |

| ADDWF            | Add W and f                                                                                                                                                                    |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] ADDWF f,d                                                                                                                                                              |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \end{array}$                                                                                                                |

| Operation:       | (W) + (f) $\rightarrow$ (destination)                                                                                                                                          |

| Status Affected: | C, DC, Z                                                                                                                                                                       |

| Description:     | Add the contents of the W register<br>with register 'f'. If 'd' is 0, the result<br>is stored in the W register. If 'd' is<br>1, the result is stored back in<br>register 'f'. |

| BCF              | Bit Clear f                                                         |

|------------------|---------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ]BCF f,b                                             |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ 0 \leq b \leq 7 \end{array}$ |

| Operation:       | $0 \rightarrow (f < b >)$                                           |

| Status Affected: | None                                                                |

| Description:     | Bit 'b' in register 'f' is cleared.                                 |

| BSF              | Bit Set f                                                           |

|------------------|---------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] BSF f,b                                            |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ 0 \leq b \leq 7 \end{array}$ |

| Operation:       | $1 \rightarrow (f < b >)$                                           |

| Status Affected: | None                                                                |

| Description:     | Bit 'b' in register 'f' is set.                                     |

| ANDLW            | AND Literal with W                                                                                                     |  |  |

|------------------|------------------------------------------------------------------------------------------------------------------------|--|--|

| Syntax:          | [ <i>label</i> ] ANDLW k                                                                                               |  |  |

| Operands:        | $0 \leq k \leq 255$                                                                                                    |  |  |

| Operation:       | (W) .AND. (k) $\rightarrow$ (W)                                                                                        |  |  |

| Status Affected: | Z                                                                                                                      |  |  |

| Description:     | The contents of W register are<br>AND'ed with the eight-bit literal<br>'k'. The result is placed in the W<br>register. |  |  |

| BTFSS            | Bit Test f, Skip if Set                                                                                                                                                                           |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ label ] BTFSS f,b                                                                                                                                                                               |

| Operands:        | $0 \le f \le 127$<br>$0 \le b < 7$                                                                                                                                                                |

| Operation:       | skip if (f <b>) = 1</b>                                                                                                                                                                           |

| Status Affected: | None                                                                                                                                                                                              |

| Description:     | If bit 'b' in register 'f' is '0', the next instruction is executed.<br>If bit 'b' is '1', then the next instruction is discarded and a NOP is executed instead, making this a 2 TCY instruction. |

| ANDWF            | AND W with f                                                                                                                                                |  |  |  |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Syntax:          | [label] ANDWF f,d                                                                                                                                           |  |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \end{array}$                                                                                             |  |  |  |

| Operation:       | (W) .AND. (f) $\rightarrow$ (destination)                                                                                                                   |  |  |  |

| Status Affected: | Z                                                                                                                                                           |  |  |  |

| Description:     | AND the W register with register<br>'f'. If 'd' is 0, the result is stored in<br>the W register. If 'd' is 1, the result<br>is stored back in register 'f'. |  |  |  |

| BTFSC            | Bit Test, Skip if Clear                                                                                                                                                                                         |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ label ] BTFSC f,b                                                                                                                                                                                             |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ 0 \leq b \leq 7 \end{array}$                                                                                                                                             |

| Operation:       | skip if (f <b>) = <math>0</math></b>                                                                                                                                                                            |

| Status Affected: | None                                                                                                                                                                                                            |

| Description:     | If bit 'b' in register 'f' is '1', the next instruction is executed.<br>If bit 'b', in register 'f', is '0', the next instruction is discarded, and a NOP is executed instead, making this a 2 TCY instruction. |

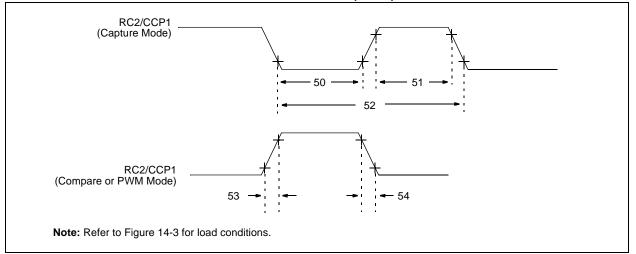

TABLE 14-5: CAPTURE/COMPARE/PWM REQUIREMENTS (CCP1)

| Param<br>No. | Sym  | Characteristic              |                |              | Min                    | Тур† | Max | Units | Conditions                        |

|--------------|------|-----------------------------|----------------|--------------|------------------------|------|-----|-------|-----------------------------------|

| 50*          | TccL | * CCP1<br>input low<br>time | No Prescaler   |              | 0.5 TCY + 20           | _    |     | ns    |                                   |

|              |      |                             | With Prescaler | Standard(F)  | 10                     |      | _   | ns    |                                   |

|              |      |                             |                | Extended(LF) | 20                     | _    | _   | ns    |                                   |

| 51*          | TccH | CCP1 input high time        | No Prescaler   |              | 0.5 TCY + 20           | _    | _   | ns    |                                   |

|              |      |                             | With Prescaler | Standard(F)  | 10                     |      | _   | ns    |                                   |

|              |      |                             |                | Extended(LF) | 20                     | _    | _   | ns    |                                   |

| 52*          | TccP | CCP1 input period           |                |              | <u>3 Tcy + 40</u><br>N | —    | _   | ns    | N = prescale value<br>(1,4 or 16) |

| 53*          | TccR | CCP1 output rise time       |                | Standard(F)  | —                      | 10   | 25  | ns    |                                   |

|              |      |                             |                | Extended(LF) | —                      | 25   | 50  | ns    |                                   |

| 54*          | TccF | CCP1 output fall time       |                | Standard(F)  | —                      | 10   | 25  | ns    |                                   |

|              |      |                             |                | Extended(LF) | _                      | 25   | 45  | ns    |                                   |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

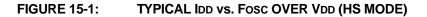

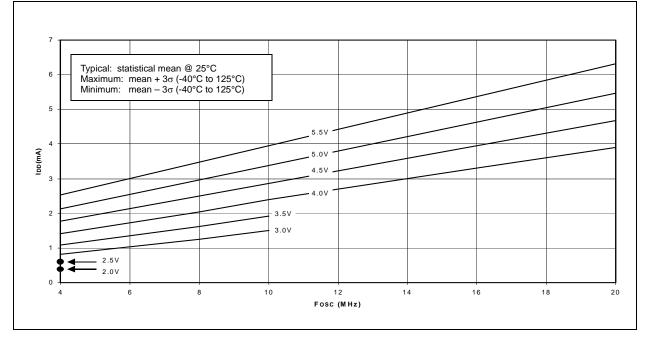

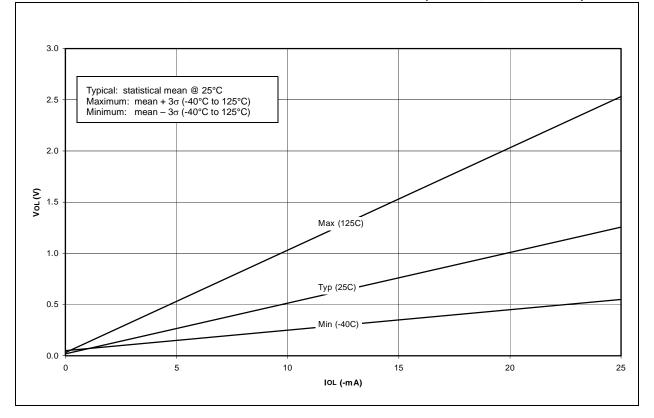

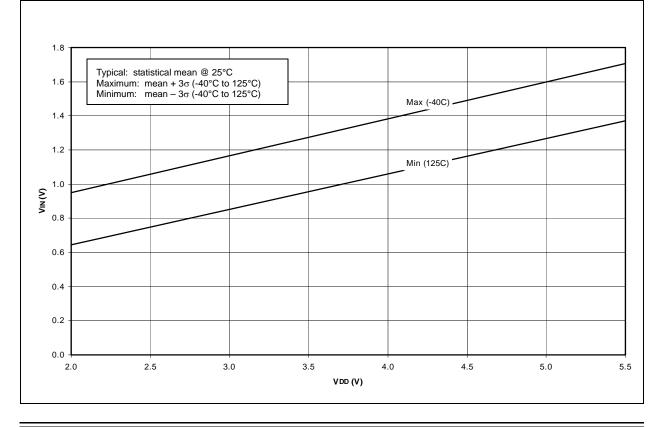

# 15.0 DC AND AC CHARACTERISTICS GRAPHS AND TABLES

**Note:** The graphs and tables provided following this note are a statistical summary based on a limited number of samples and are provided for informational purposes only. The performance characteristics listed herein are not tested or guaranteed. In some graphs or tables, the data presented may be outside the specified operating range (e.g., outside specified power supply range) and therefore, outside the warranted range.

"Typical" represents the mean of the distribution at 25°C. "Maximum" or "minimum" represents (mean +  $3\sigma$ ) or (mean -  $3\sigma$ ) respectively, where  $\sigma$  is a standard deviation, over the whole temperature range.

FIGURE 15-2: MAXIMUM IDD vs. Fosc OVER VDD (HS MODE)

© 2000-2013 Microchip Technology Inc.

# APPENDIX A: REVISION HISTORY

## **Revision A (December 1999)**

Original data sheet for the PIC16F870/871 family.

## **Revision B (April 2003)**

This revision includes the DC and AC Characteristics Graphs and Tables. The Electrical Specifications in Section 14.0 have been updated and there have been minor corrections to the data sheet text.

## **Revision C (January 2013)**

Added a note to each package outline drawing.

### TABLE B-1: DEVICE DIFFERENCES

### APPENDIX B: DEVICE DIFFERENCES

The differences between the devices listed in this data sheet are shown in Table B-1.

| Feature                         | PIC16F870              | PIC16F871                      |  |  |

|---------------------------------|------------------------|--------------------------------|--|--|

| On-chip Program Memory (Kbytes) | 2K                     | 2K                             |  |  |

| Data Memory (bytes)             | 128                    | 128                            |  |  |

| Boot Block (bytes)              | 2048                   | 512                            |  |  |

| Timer1 Low Power Option         | Yes                    | No                             |  |  |

| I/O Ports                       | Ports A, B, C          | Ports A, B, C, D, E            |  |  |

| A/D Channels                    | 5                      | 8                              |  |  |

| External Memory Interface       | No                     | No                             |  |  |

| Package Types                   | 28-pin DIP, SOIC, SSOP | 40-pin PDIP, 44-pin PLCC, TQFP |  |  |

# APPENDIX C: CONVERSION CONSIDERATIONS

This appendix discusses the considerations for converting from previous versions of a device to the ones listed in this data sheet. Typically, these changes are due to the differences in the process technology used. An example of this type of conversion is from a PIC17C756 to a PIC18F8720.

### **Not Applicable**

# APPENDIX D: MIGRATION FROM MID-RANGE TO ENHANCED DEVICES

A detailed discussion of the differences between the mid-range MCU devices (i.e., PIC16CXXX) and the enhanced devices (i.e., PIC18FXXX) is provided in AN716, "Migrating Designs from PIC16C74A/74B to PIC18C442." The changes discussed, while device specific, are generally applicable to all mid-range to enhanced device migrations.

This Application Note is available as Literature Number DS00716.